20160629SP_DDR3硬件设计和Layout设计

- 格式:pdf

- 大小:2.49 MB

- 文档页数:13

DDR3硬件设计和Layout设计译自飞思卡尔官方文档Hardware and Layout Design Considerations for DDR3 SDRAMMemory Interfaces目录1 设计检查表 (3)2 终端匹配电阻功耗计算 (8)3 VREF (8)4 VTT电压轨 (8)5 DDR布线 (9)5.1 数据线— MDQ[0:63], MDQS[0:8], MDM[0:8], MECC[0:7] (9)5.2 Layout建议 (10)6 仿真 (12)7 扩展阅读 (13)8 历史版本 (13)9 声明 (13)这是一篇关于DDR3 SDRAM IP core的设计向导,出自飞思卡尔,为了实现PCB的灵活设计,我们可以采用合适的拓扑结构简化设计时的板级关联性。

飞思卡尔强烈推荐系统/板级工程师在PCB制板前进行设计验证,包括信号完整性、时序等等。

1 设计检查表如表1,罗列了DDR设计检查清单,推荐逐一检查,并在最右侧作出决策。

MDQSx/x。

DDR3数据线在做蛇形走线等长匹配时,应该保证蛇形走线间至少有25mil 的间距。

2 终端匹配电阻功耗计算DDR的地址线和控制线会有灌电流和拉电流经终端电阻R T流过,那么该电阻的功耗计算如下:Power = x R T = x (47Ω) = 7.5mW根据上述,我们需要选择高达1/16W的电阻。

另外,V TT电流的计算请参看第4节。

3 V REFV REF电流需求相对较小,低于3mA。

V REF是为控制器和DDR芯片的差分接收器提供0.75V 的直流偏置(V DD/2),V REF的误差或噪声可能会在总线上引起时序错误、不期望的抖动和误动作等。

为避免上述问题,V REF噪声必须控制在JEDEC要求范围内,因此,V REF和V TT不能在同一平面,因为DRAM的V REF对V TT的噪声很敏感。

但是,VREF和VTT的产生必须经由同一个电源产生,以保证高度统一,所以每一个VREF要放置合适的去耦电容(包括控制器、每一个DIMM/DDR芯片、V REF电源),并且做到布局布线简单,预防潜在问题。

PC1600 and PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationRevision 1.1June 29, 2001Table of Contents PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification Table of ContentsTable of Contents (2)Product Description (3)Product Family Attributes (3)Environmental Requirements (5)Architecture (5)Absolute Maximum Ratings (5)Pin Description (5)Input/Output Functional Description (6)184-Pin DDR SDRAM DIMM Pin Assignments (7)Block Diagram: Raw Card Version A, x72 (8)Block Diagram: Raw Card Version A, x64 (9)Block Diagram: Raw Card Version B, x64 (10)Block Diagram: Raw Card Version B, x72 (11)Block Diagram: Raw Card Version C, x64 (12)Block Diagram: Raw Card Version C, x72 (13)Logical Clock Net Structures (14)Component Details (15)Pin Assignments for 64Mb, 128Mb, 256Mb and 512Mb DDR SDRAM Planar Components (15)DDR SDRAM Component Specifications (16)Unbuffered DIMM Details (16)SDRAM Module Configurations (Reference Designs) (16)DDR Unbuffered Design File Releases (17)Input Loading Matrix (17)Component Types and Placement (18)Example Raw Card A Component Placement (18)Example Raw Card B Component Placement (19)Example Raw Card C Component Placement (19)DIMM Wiring Details (20)Signal Groups (20)General Net Structure Routing Guidelines (20)Explanation of Net Structure Diagrams (21)Net Structure Example (21)Clock Net Structures (22)Signal Net Structures (23)Cross Section Recommendations (34)Decoupling (34)Page 2Revision 1.1PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification Table of ContentsDesign Target (35)Address setup/hold flight times (35)Clock Skew Contributions (tSKEW) (35)Serial PD Definition (36)Serial Presence Detect Example Raw Card Version ’B’ (36)Serial Presence Detect Component Specification (37)Product Label (38)DIMM Mechanical Specifications (39)Simplified Mechanical Drawing with Keying Positions (39)Clocking Timing Methodology (40)Unbuffered DIMM Differential Clock Reference Net (40)Revision Log (41)Revision 1.1Page 31. Product Description PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification 1. Product DescriptionThis specification defines the electrical and mechanical requirements for 184-pin, 2.5 Volt (V DD)/ 2.5 Volt (V DDQ), Unbuffered, Double Data Rate, Synchronous DRAM Dual In-Line Memory Modules (DDR SDRAM DIMMs).These DDR DIMMs are intended for use as main memory when installed in PCs. The DDR DIMMs must permit operation with a new address every clock cycle in PC1600 and PC2100 environments.Reference design examples are included which provide an initial basis for Unbuffered DDR DIMM designs. Modifica-tions to these reference designs may be required to meet all system timing, signal integrity and thermal requirements for PC1600 and PC2100 support. All Unbuffered DIMM implementations must use simulations and lab verification to ensure proper timing requirements and signal integrity in the design.This specification largely follows the JEDEC defined 184-pin Unbuffered DDR SDRAM DIMM product. (Refer to JEDEC standard JESD21-C, Section 4.5.10, at ).Product Family AttributesDIMM Organization x64, x72 ECC NotesDIMM Dimensions (max) 5.256" x 1.256" x 0.157"Pin Count184DDR SDRAMs Supported64Mb, 128Mb, 256Mb, 512MbCapacity32MB - 1GBSerial PD Consistent with JEDEC JC 42.5 Item 849AVoltage Options 2.5 Volt V DD/V DDQ2.3 Volt to3.6 Volt V DD SPDAll DDR modules use a common V DD-V DDQ power plane. They are tied togetheron the DIMM, but by standard definitionare supported on the pinout to accommodatefuture enhancements.Interface SSTL_2Note 1: V DD SPD is not tied to V DD or V DDQ on the DDR DIMM.Page 4Revision 1.1PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification2. Environmental RequirementsRevision 1.1Page 52. Environmental Requirements184-pin Unbuffered DDR SDRAM DIMMs are intended for use in standard office environments that have limited capacity for heating and air conditioning.3. Architecture*The V DD and V DDQ pins are tied to the single power-plane on these designs. See page 35.Absolute Maximum RatingsSymbol ParameterRating Units Notes T OPR Operating Temperature (ambient) 0 to +55°C 1H OPR Operating Humidity (relative) 10 to 90%1T STG Storage Temperature-50 to +100°C 1H STGStorage Humidity (without condensation) 5 to 95%1Barometric Pressure (operating & storage)105 to 69K Pascal1, 21.Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and device functional operation at or above the conditions indicated is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2.Up to 9850 ft.Pin DescriptionPin Name DescriptionPin Name DescriptionA0 - A13SDRAM address bus CK0 - CK2SDRAM clock (positive lines of 3 differ-ential pairs)BA0 - BA1SDRAM bank select CK0 - CK2SDRAM clock (negative lines of these three pairs)DQ0 - DQ63DIMM memory data bus SCL IIC serial bus clock for EEPROM CB0 - CB7DIMM ECC check bits SDA IIC serial bus data line for EEPROM /RAS SDRAM row address strobe SA0 - SA2IIC slave address select for EEPROM /CAS SDRAM column address strobe V DD *SDRAM positive power supply /WE SDRAM write strobeV DDQ *SDRAM I/O Driver positive power sup-ply/S0 - /S1SDRAM chip select lines (Phys. banks 0 and 1)VREF SDRAM I/O reference supply CKE0 - CKE1SDRAM clock enable lines V SS Power supply return (ground)DQS0 - DQS8SDRAM low data strobesV DD SPD Serial EEPROM positive power supply (2.3 Volts to 3.6 Volts)--V DD SPD is not connected to V DD or V DDQ DM(0-8)/DQS(9-17)SDRAM low data masks/high data strobes (x4, 2 Phys. banks)NCSpare pins (no connect)V DD IDV DD identification flag3. Architecture PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationInput/Output Functional DescriptionSymbol Type Polarity FunctionCK0 - CK2(SSTL)PositiveEdgeThe positive line of the differential pair of system clock inputs. All the DDR SDRAM addr/cntl inputs are sampled on the rising edge of their associated clocks.CK0 - CK2(SSTL)NegativeEdgeThe negative line of the differential pair of system clock inputs.CKE0, CKE1(SSTL)ActiveHighActivates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low initiates the Power Down mode, or the Self Refresh mode.S0, S1(SSTL)Active Low Enables the associated SDRAM command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations con-tinue.RAS, CAS, WE(SSTL)Active Low When sampled at the positive rising edge of the clock, CAS, RAS, and WE define the operation to be executed by the SDRAM.V REF Supply Reference voltage for SSTL2 inputs.V DDQ Supply Power supply for the DDR SDRAM output buffers to provide improved noise immunity. For all current DDR unbuffered DIMM designs, V DDQ shares the same power plane as V DD pins.BA0,1(SSTL)—Selects which SDRAM bank of four is activated. A0 - A9A10/AP, A11-A13(SSTL)—During a Bank Activate command cycle, A0-A13 defines the row address (RA0-RA13) when sampledat the rising clock edge.During a Read or Write command cycle, A0-12 defines the column address (CA0-CA12) when sampledat the rising clock edge. In addition to the column address, AP is used to invoke autoprecharge operationat the end of the burst read or write cycle. If AP is high, autoprecharge is selected and BA0, BA1 definesthe bank to be precharged. If AP is low, autoprecharge is disabled.During a Precharge command cycle, AP is used in conjunction with BA0, BA1 to control which bank(s)to precharge. If AP is high, all banks will be precharged regardless of the state of BA0 or BA1. If AP islow, BA0 and BA1 are used to define which bank to precharge.DQ0 - DQ63,CB0 - CB7(SSTL)—Data and Check Bit Input/Output pins.DM0-DM8(SSTL)ActiveHighMasks write data when high, issued concurrently with input data. Both DM and DQ have a write latency of one clock once the write command is registered into the SDRAM.V DD, V SS Supply Power and ground for the DDR SDRAM input buffers, and core logic. V DD and V DDQ pins are tied to a single combined V DD/V DDQ plane on these modules.DQS0-DQS8(SSTL)Negativeand Posi-tive EdgeData strobe for input and output data. For the x16, LDQS corresponds to the data on DQ0-7, VDQs cor-responds to the data on DQ8-15.SA0 - 2—These signals are tied at the system planar to either V SS or V DD to configure the serial SPD EEPROM address range.SDA—This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be con-nected from the SDA bus line to V DD to act as a pullup.SCL—This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected from the SCL bus time to V DD to act as a pullup.V DD SPD Supply Power supply for SPD EEPROM. This supply is separate from the V DD/V DDQ power plane. EEPROM supply is operable from 2.3V to 3.6V.Page 6Revision 1.1PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification3. ArchitectureRevision 1.1Page 7184-Pin DDR SDRAM DIMM Pin AssignmentsFront Side (left side 1 - 52, right side 53 - 92)Back Side (left side 93 -144, right side 145 -184)Front Side (left side 1 - 52, right side 53 - 92)Back Side (left side 93 -144, right side145 -184)Pin #x64Non-Parity x72 ECC Pin #x64Non-Parity x72ECC Pin #x64Non-Parity x72 ECC Pin #x64Non-Parity x72ECC1VREF VREF 93V SS V SS 48A0A0140NC DM8/DQS172DQ0DQ094DQ4DQ449NC CB2141A10A103V SS V SS 95DQ5DQ550V SS V SS 142NC CB64DQ1DQ196V DDQ V DDQ 51NC CB3143V DDQV DDQ 5DQS0DQS097DM0/DQS9DM0/DQS952BA1BA1144NC CB76DQ2DQ298DQ6DQ6KEY KEY 7V DD V DD 99DQ7DQ753DQ32DQ32145V SS V SS 8DQ3DQ3100V SS V SS 54V DDQ V DDQ 146DQ36DQ369NC NC 101NC NC 55DQ33DQ33147DQ37DQ3710NC NC 102NCNC56DQS4DQS4148V DD V DD 11V SS V SS 103NC (FETEN)NC (FENTEN)57DQ34DQ34149DM4/DQS13DM4/DQS1312DQ8DQ8104V DDQ V DDQ 58V SS V SS 150DQ38DQ3813DQ9DQ9105DQ12DQ1259BA0BA0151DQ39DQ3914DQS1DQS1106DQ13DQ1360DQ35DQ35152V SS V SS 15V DDQ V DDQ 107DM1/DQS10DM1/DQS1061DQ40DQ40153DQ44DQ4416CK1CK1108V DD V DD 62V DDQ V DDQ 154/RAS /RAS 17/CK1/CK1109DQ14DQ1463/WE /WE 155DQ45DQ4518V SS V SS 110DQ15DQ1564DQ41DQ41156V DDQ V DDQ 19DQ10DQ10111CKE1CKE165/CAS /CAS 157/S0/S020DQ11DQ11112V DDQ V DDQ 66V SS V SS 158/S1/S121CKE0CKE0 113BA2BA267DQS5DQS5159DM5/DQS14DM5/DQS1422V DDQ V DDQ 114DQ20DQ2068DQ42DQ42160V SS V SS 23DQ16DQ16115A12A1269DQ43DQ43 161DQ46DQ4624DQ17DQ17116V SS V SS 70V DD V DD 162DQ47DQ4725DQS2DQS2117DQ21DQ2171NC, /S2NC, /S2163NC, /S3NC, /S326V SS V SS 118A11A1172DQ48DQ48164V DDQ V DDQ 27A9A9119DM2/DQS11DM2/DQS1173DQ49DQ49165DQ52DQ5228DQ18DQ18120V DD V DD 74V SS V SS 166DQ53DQ5329A7A7121DQ22DQ2275/CK2/CK2167A13A1330V DDQ V DDQ 122A8A876CK2CK2168V DD V DD 31DQ19DQ19123DQ23DQ2377V DDQ V DDQ 169DM6/DQS15DM6/DQS1532A5A5124V SS V SS 78DQS6DQS6170DQ54DQ5433DQ24DQ24125A6A679DQ50DQ50171DQ55DQ5534V SS V SS 126DQ28DQ2880DQ51DQ51172V DDQ V DDQ 35DQ25DQ25127DQ29DQ2981V SS V SS 173NC NC 36DQS3DQS3128V DDQ V DDQ 82V DDID V DDID 174DQ60DQ6037A4A4129DM3/DQS12DM3/DQS1283DQ56DQ56175DQ61DQ6138V DD V DD 130A3A384DQ57DQ57176V SS V SS 39DQ26DQ26131DQ30DQ3085V DD V DD 177DM7/DQS16DM7/DQS1640DQ27DQ27132V SS V SS 86DQS7DQS7178DQ62DQ6241A2A2133DQ31DQ3187DQ58DQ58179DQ63DQ6342V SS V SS 134NC CB488DQ59DQ59180V DDQ V DDQ 43A1A1135NC CB589V SS V SS 181SA0SA044NC CB0136V DDQ V DDQ 90NC NC 182SA1SA145NC CB1137CK0CK091SDA SDA 183SA2SA246V DDV DD138/CK0/CK092SCLSCL184V DDSPDV DDSPD47NC DQS8139V SSV SSNC = No Connect NU = Not UseablePage 8Revision 1.13. ArchitecturePC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationBlock Diagram: Raw Card Version A, x72 (Populated as 1 physical bank of x8 DDR SDRAMs)A0 - A13A0-A13: SDRAMs D0 - D8RAS RAS: SDRAMs D0 - D8CAS CAS: SDRAMs D0 - D8CKE0CKE: SDRAMs D0 - D8WEWE: SDRAMs D0 - D8S0BA0 - BA1BA0-BA1: SDRAMs D0 - D8DQS8V SS D0 - D8V DD /V DDQD0 - D8V REF V but may be changed.2.DQ/DQS/DM/CKE/S relationships must be maintained as shown.3.DQ, DQS, DM/DQS resistors: 22 Ohms ± 5%.4.V DDID strap connections (for memory device V DD , V DDQ ):STRAP OUT (OPEN): V DD = V DDQ STRAP IN (V SS ): V DD ≠ V DDQ .V DDPC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification3. ArchitectureRevision 1.1Page 9Block Diagram: Raw Card Version A, x64 (Populated as 1 physical bank of x8 DDR SDRAMs)A0 - A13A0-A13: SDRAMs D0 - D7A0Serial PDA1A2SA2SDARAS RAS: SDRAMs D0 - D7CAS CAS: SDRAMs D0 - D7CKE0CKE: SDRAMs D0 - D7WEWE: SDRAMs D0 - D7BA0 - BA1BA0-BA1: SDRAMs D0 - D7DQS1DQS2DQS3SCL* Clock Wiring *CK0/CK0ClockInput SDRAMs *CK1/CK1 2 SDRAMs 3 SDRAMs 3 SDRAMs* Wire per Clock Loading Table/Wiring Diagrams*CK2/CK2Notes:1.DQ-to-I/O wiring is shown as recommended but may be changed.2.DQ/DQS/DM/CKE/S relationships must be maintained as shown.3.DQ, DQS, DM/DQS resistors: 22 Ohms ± 5%.4.V DDID strap connections(for memory device V DD , V DDQ ):STRAP OUT (OPEN): V DD = V DDQ STRAP IN (V SS ): V DD ≠ V DDQ .V SS D0 - D7V DD /V D0 - D7D0 - D7V V DDIDWP SPD V DDPage 10Revision 1.13. ArchitecturePC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationBlock Diagram: Raw Card Version B, x64 (Populated as 2 physical banks of x8 DDR SDRAMs)A0 - A13A0-A13: SDRAMs D0 - D15A0Serial PDA1A2SA2SDARAS RAS: SDRAMs D0 - D15CAS CAS: SDRAMs D0 - D15CKE0CKE: SDRAMs D0 - D7WEWE: SDRAMs D0 - D15S1CKE1CKE: SDRAMs D8 - D15BA0 - BA1BA0-BA1: SDRAMs D0 - D15DQS0DQS1DQS2DQS3* Clock Wiring *CK0/CK0ClockInput SDRAMs *CK1/CK1 4 SDRAMs 6 SDRAMs 6 SDRAMs* Wire per Clock Loading Table/Wiring Diagrams*CK2/CK2V SS D0 - D15V DD /V DDQD0 - D15D0 - D15V REF V DDIDStrap: see Note 4Notes:1.DQ-to-I/O wiring is shown as recommended but may be changed.2.DQ/DQS/DM/CKE/S relationships must be maintained as shown.3.DQ, DQS, DM/DQS resistors: 22 Ohms ± 5%.4.V DDID strap connections(for memory device V DD , V DDQ ):STRAP OUT (OPEN): V DD = V DDQ STRAP IN (V SS ): V DD ≠ V DDQSCLWP SPD V DD SPDBlock Diagram: Raw Card Version B, x72 (Populated as 2 physical banks of x8 DDR SDRAMs)A0 - A13A0-A13: SDRAMs D0 - D17RAS RAS: SDRAMs D0 - D17CAS CAS: SDRAMs D0 - D17CKE0CKE: SDRAMs D0 - D8WEWE: SDRAMs D0 - D17CKE1CKE: SDRAMs D9 - D17DQS8but may be changed.2.DQ/DQS/DM/CKE/S relationships must be maintained as shown.3.DQ, DQS, DM/DQS resistors: 22 Ohms ± 5%.4.V DDID strap connections(for memory device V DD , V DDQ ):STRAP OUT (OPEN): V DD = V DDQ STRAP IN (V SS ): V DD ≠ V DDQA0Serial PDA1A2SA0SA1SA2SDASCLWP3. ArchitecturePC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationBlock Diagram: Raw Card Version C, x64 (Populated as 1 physical bank of x16 DDR SDRAMs)S0DQS1DQS0DQS3DQS2A0 - A13A0-A13: SDRAMs D0 - D3BA0 - BA1BA0-BA1: SDRAMs D0 - D3A0Serial PDA1A2SDASCLRAS RAS: SDRAMs D0 - D3CAS CAS: SDRAMs D0 - D3CKE0CKE: SDRAMs D0 - D3WEWE: SDRAMs D0 - D3* Clock Wiring *CK0/CK0ClockInput SDRAMs *CK1/CK1NC2 SDRAMs 2 SDRAMs* Wire per Clock Loading Table/Wiring Diagrams*CK2/CK2V SS D0 - D3V DD /V DDQD0 - D3D0 - D3V REF V DDID Notes:1.DQ-to-I/O wiring is shown as recommended but may be changed.2.DQ/DQS/DM/CKE/S relationships must be main-tained as shown.3.DQ, DQS, DM/DQS resistors: 22 Ohms ± 5%.4.V DDID strap connections(for memory device V DD , V DDQ ):STRAP OUT (OPEN): V DD = V DDQ STRAP IN (V SS ): V DD ≠ V DDQ5.BA, Ax, RAS, CAS, WE resistors: 7.5 Ohms ± 5%WP SPD V DD SPDBlock Diagram: Raw Card Version C, x72 (Populated as 1 physical bank of x16 DDR SDRAMs)S0A0 - A13A0-A13: SDRAMs D0 - D4BA0 - BA1BA0-BA1: SDRAMs D0 - D4RAS RAS: SDRAMs D0 - D4CAS CAS: SDRAMs D0 - D4CKE0CKE: SDRAMs D0 - D4WEWE: SDRAMs D0 - D4V D0 - D4V DD /V DDQ D0 - D4V V DDID2.DQ/DQS/DM/CKE/S relationships must be maintained as shown.3.DQ, DQS, DM/DQS resistors: 22 Ohms ± 5%.4.V DDID strap connections(for memory device V DD , V DDQ ):STRAP OUT (OPEN): V DD = V DDQ STRAP IN (V SS ): V DD ≠ V DDQ5.BA, Ax, RAS, CAS, WE resistors: 7.5 Ohms ± 5%SPD V DDSPD3. Architecture PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification Logical Clock Net Structures4. Component DetailsPin Assignments for 64Mb, 128Mb, 256Mb and 512Mb DDR SDRAM Planar Components(Top View)123456910111213147815161718192021226665646362615857565554536059525150494847464523242544434226274140282930313233393837363534V DD DQ0V DDQ NC DQ1V SSQ V DDQ NC DQ3V SSQ NC NC NC DQ2V DDQ NC NC V DD NC NC WE CAS RAS CS NC BA0BA1V SS DQ7V SSQ NC DQ6V DDQ V SSQ NC DQ4V DDQ NC NC NC DQ5V SSQ DQS NC V REF V SS DM CLK CLK CKENCNC/A121A11A9A10/APA0A1A2A3V DDA8A7A6A5A4V SSV DD DQ0V DDQ DQ1DQ2V SSQ V DDQ DQ5DQ6V SSQ DQ7NC DQ3DQ4V DDQ LDQS NC V DD NC LDM WE CAS RAS CS NC BA0BA1A10/APA0A1A2A3V DDV SS DQ15V SSQ DQ14DQ13V DDQ V SSQ DQ10DQ9V DDQ DQ8NC DQ12DQ11V SSQ UDQS NC V REF V SS UDM CLK CLK CKENC NC/A121A11A9A8A7A6A5A4V SS4Mb x 16, 8Mb x 16, 16Mb x 16, 32Mb x 168Mb x 8, 16Mb x 8, 32Mb x 8, 64Mb x 8Notes:1. A12 is utilized on the 256Mbit and 512Mbit DDR SDRAM devices.5. Unbuffered DIMM Details PC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationDDR SDRAM Component SpecificationsThe DDR SDRAM components used with this DIMM design specification are intended to be consistent with JEDEC ballots JC-42.3-98-227A. DDR SDRAM component specification violations also violate the DDR SDRAM Unbuffered DIMM specifications.5. Unbuffered DIMM DetailsSDRAM Module Configurations (Reference Designs)Raw Card Version DIMMCapacityDIMMOrganizationSDRAMDensitySDRAMOrganization# ofSDRAMsSDRAMPackage Type# ofPhysicalBanks# of Banksin SDRAM# Address bitsrow/colA 64 MB8Mx6464Mbit8Mx8866 lead TSOP1412/98Mx7264Mbit8Mx8966 lead TSOP1412/9 128MB16Mx64128Mbit16Mx8866 lead TSOP1412/1016Mx72128Mbit16Mx8966 lead TSOP1412/10 256MB32Mx64256Mbit32Mx8866 lead TSOP1413/1032Mx72256Mbit32Mx8966 lead TSOP1413/10 512MB64Mx64512Mbit64Mx8866 lead TSOP1413/1164Mx72512Mbit64Mx8966 lead TSOP1413/11B 128MB16Mx6464Mbit8Mx81666 lead TSOP2412/1016Mx7264Mbit8Mx81866 lead TSOP2412/10 256MB32Mx64128Mbit16Mx81666 lead TSOP2412/1032Mx72128Mbit16Mx81866 lead TSOP2412/10 512MB64Mx64256Mbit32Mx81666 lead TSOP2413/1064Mx72256Mbit32Mx81866 lead TSOP2413/10 1GB128Mx64512Mbit64Mx81666 lead TSOP2413/11128Mx72512Mbit64Mx81866 lead TSOP2413/11C 32MB4Mx6464Mbit4Mx16466 lead TSOP1412/84Mx7264Mbit4Mx16566 lead TSOP1412/8 64MB8Mx64128Mbit8Mx16466 lead TSOP1412/98Mx72128Mbit8Mx16566 lead TSOP1412/9 128MB16Mx64256Mbit16Mx16466 lead TSOP1412/1016Mx72256Mbit16Mx16566 lead TSOP1412/10 256MB32Mx64512Mbit32Mx16466 lead TSOP1413/1032Mx72512Mbit32Mx16566 lead TSOP1413/10DDR Unbuffered Design File Releases‘Reference’ design file updates will be released as needed. This DDR Unbuffered DIMM specification will reflect the most recent design files, but may also be updated to reflect clarifications to the specification only; in these cases the design files will not be updated. The following table outlines the most recent design file releases.Note: Future design file releases will include both a date and a revision label. All changes to the design file are also doc-umented within the ‘read-me’ file.Input Loading MatrixSignal NamesInput Device R/C A R/C B R/C C Clock (CK0 - CK2)SDRAM 1666CKE0/CKE1/Chipselects SDRAM 8-98-94-5Addr/RAS/CAS/BA/WE SDRAM 8-916-184-5DQ/CB/DQS/DM SDRAM 121SCL/SDA/SAEEPROM1111. 6 SDRAMs or equivalent using padding capacitorsRaw Card VersionSpecification RevisionApplicable Gerber FileNotes A1.0A0Production ready 1.1A0Production ready B1.0B1Production ready 1.1B1Production ready C1.0C1Production ready 1.1C2Production ready5. Unbuffered DIMM DetailsPC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationComponent Types and PlacementComponents shall be positioned on the PCB to meet the minimum and maximum trace lengths required for DDR SDRAM signals. Bypass capacitors for DDR SDRAM devices must be located near the device power pins. The following layouts suggest placement for the Raw Card Versions A, B and C. Exact spacing is not provided, but should be based on manufacturing contraints and signal routing constraints imposed by this design guide.Example Raw Card A Component Placement31.751.250+N/A for x645.077128.955.171133.355.250SPD(2X ) 4.000.1572.300.9117.800.700(2)2.500.09810.000.394FRONT131.35SIDE3.180.125 MAX1.27 +/- 0.100.050 +/-0 .004Example Raw Card B Component PlacementExample Raw Card C Component Placement31.751.250+N/A for x64+N/A for x645.077128.955.171133.355.250SPD(2X ) 4.000.1572.300.9117.800.700(2)2.500.09810.000.394FRONTBACKSIDE(Front)4.000.157 MAX1.27 +/- 0.100.050 +/-0 .004131.35Note: All dimensions are typical unless otherwise statedmillimeters inches+N/A for x645.077128.95131.355.171133.355.250SPD31.751.250(2X ) 4.000.1572.300.9117.800.700(2)2.500.09810.000.394FRONTSIDE3.180.125 MAX1.27 +/- 0.100.050 +/- .0046. DIMM Wiring DetailsPC1600/PC2100 DDR SDRAM Unbuffered DIMM Design Specification6. DIMM Wiring DetailsSignal GroupsThis specification categorizes DDR SDRAM timing-critical signals into five groups. The following table summarizes the signals contained in each group..General Net Structure Routing GuidelinesNet structures and lengths must satisfy signal quality and setup/hold time requirements for the memory interface. Net structure diagrams for each signal group are shown in the following sections. Each diagram is accompanied by a trace length table that lists the minimum and maximum allowable lengths for each trace segment and/or net.The general routing requirements are as follows•Route all signal traces including differential clocks using 4/6 rules, i.e., 4 mil traces and 6 mil minimum spacing between adjacent traces.•No test points are required.Signal GroupSignals In Group Raw Card VersionPage Clock CK [3:0]A, B, C 22Data DQ [63:0]; CB [7:0]; DQS [8:0], DM [8:0]A, B, C 23Chip SelectS [0,1]A, B 26S [0,1]C 27Clock EnableCKE [0,1]A, B 27CKE [0,1]C 30Address/ControlAx, BAx, RAS, CAS, WE A,B 29Ax, BAx, RAS, CAS, WEC33Explanation of Net Structure DiagramsThe net structure routing diagrams provide a reference design example for each raw card version. These designs provide an initial basis for registered DIMM designs. The diagrams should be used to determine individual signal wiring on a DIMM for any supported configuration. Only transmission lines (represented as cylinders and labeled with trace length designators “TL”) represent physical trace segments. All other lines are zero in length. To verify DIMM functionality, a full simulation of all signal integrity and timing is required. The given net structures and trace lengths are not inclusive for all solutions.Once the net structure has been determined, the permitted trace lengths for the net structure can be read from the table below each net structure routing diagram. Some configurations require the use of multiple net structure routing diagrams to account for varying load quantities on the same signal. All diagrams define one load as one SDRAM input.Net Structure ExampleA 128MB double-sided ECC DIMM using 64Mbit 8Mx8 DDR SDRAM devices would have a data net structure as shown in the following diagram.TL0 DIMMConnector 22 ohms ± 5%TL1TL2TL2SDRAM PinSDRAM Pin6. DIMM Wiring DetailsPC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationClock Net StructuresCK[3:0]SDRAM clock signals must be carefully routed to meet the following requirements:•Signal quality •Rise/fall time•SDRAM component edge skew•Motherboard chipset clock edge skew.Net Structure Routing for ClocksTrace Lengths for Clock Net StructuresRaw Card TL0 TL1TL2TL3R1 Ohms Notes Min Max Min Max Min Max Min Max A,B .15.16.04.05 1.13 1.14.36.371201,2C.15.16.04.051.131.14.36.371201,21.All distances are given in inches and must be kept within a tolerance of ± 0.01 inch2.Logical clock structures on page 15 must be followed. In some cases the loads will be equivalent capacitors.TL0TL1TL2TL2TL2TL3TL3TL3TL3TL3TL3R1 ± 5%SDRAM PinSDRAM PinSDRAM PinSDRAM PinSDRAM PinSDRAM PinDIMM ConectorCLK CLKSignal Net StructuresDQ[63:0], CB[7:0], DQS [8:0] and DM [8:0]Net Structure Routing for Data (Raw Card Versions A and C)Trace Lengths for DQ, CB and DQS Net Structures (Raw Card Versions A and C)Raw CardTL0 TL1TotalR1 Ohms Notes Min Max Min Max Min Max A .14.21.52.58.72.73221,2C.14.18.55.58.72.73221,21.All distances are given in inches and must be kept within a tolerance of ± 0.01 inch.2.Total Min and Total Max refer to the min and max respectively of TL0 + TL1.Trace Lengths for DM Net Structures (Raw Card Versions A and C)Raw CardTL0 TL1TotalR1 Ohms Notes Min Max Min Max Min Max A .15.16.67.68.83.84221,2C.14.16.67.69.83.84221,21.All distances are given in inches and must be kept within a tolerance of ± 0.01 inch.2.Total Min and Total Max refer to the min and max respectively of TL0 + TL1.TL0DIMM ConnectorR1 ± 5%TL1SDRAM Pin6. DIMM Wiring DetailsPC1600/PC2100 DDR SDRAM Unbuffered DIMM Design SpecificationNet Structure Routing for Data (Raw Card Version B)Trace Lengths for DQ, CB, and DQS Net Structures (Raw Card Version B)Raw CardTL0 TL1TL2TotalR1 Ohms Notes Min Max Min Max Min Max Min Max B.14.24.19.43.13.37.72.73221,21.All distances are given in inches and must be kept within a tolerance of ± 0.01 inch.2.Total Min and Total Max refer to the min and max respectively of TL0 + TL1 + TL2.Trace Lengths for DM Net Structures (Raw Card Version B)Raw CardTL0 TL1TL2TotalR1 Ohms Notes Min Max Min Max Min Max Min Max B.15.17.25.28.42.43.82.86221,21.All distances are given in inches and must be kept within a tolerance of ± 0.01 inch.2.Total Min and Total Max refer to the min and max respectively of TL0 + TL1 + TL2.TL0DIMM ConnectorR1 ± 5%TL1TL2TL2SDRAM PinSDRAM PinNet Structure Routing for Chip Select (Raw Card Version A)Trace Lengths for Chip Select Net Structures (S0)Raw Card TL0 TL1TL2 TL3TL4 TL5TL6NotesMin Max Min Max Min Max Min Max Min Max Min Max Min Max A2.412.421.571.581.261.27.58.60.29.30.15.16.32.3311.All distances are given in inches and should be kept within a tolerance of ± 0.01 inches.DIMM ConnectorTL4TL5TL3TL0SDRAM PinTL5SDRAM PinTL4TL3SDRAM PinTL5TL5SDRAM PinTL3TL5TL3SDRAM Pin TL5SDRAM PinTL3TL3SDRAM PinTL5TL5SDRAM PinTL1TL2TL6SDRAM Pin(ECC)。

DDR3内存的PCB仿真与设计

一、DDR3内存的PCB仿真

PCB(Printed Circuit Board,印制电路板)的设计是DDR3内存中非常重要的一步。

在进行实际制作之前,通过仿真来验证设计的正确性,可以帮助找出潜在的问题并进行优化。

1.电源噪声仿真

2.信号完整性仿真

3.时钟分布仿真

4.排布规则仿真

二、DDR3内存的PCB设计

在进行DDR3内存的PCB设计时,需要考虑以下几个方面。

1.布局设计

2.分层设计

3.时钟优化

4.信号完整性优化

5.地平面设计

良好的地平面设计可以提供稳定的地连接,减小噪声干扰。

需要合理规划地平面的宽度和连接方式,并与信号平面分层设计相结合。

总之,DDR3内存的PCB仿真和设计是提高DDR3内存性能和稳定性的重要手段。

通过仿真和设计的过程,可以找出潜在的问题并进行优化,提

高DDR3内存的性能和可靠性。

对DDR3内存的PCB设计要仔细考虑布局、分层、时钟优化、信号完整性优化和地平面设计等方面,以确保DDR3内存的正常运行。

fpga ddr3电路设计FPGA(Field-Programmable Gate Array)是一种集成电路,可以通过编程重新配置其内部逻辑电路,以实现特定的功能。

DDR3(Double Data Rate 3)是一种动态随机存取存储器(DRAM)技术,广泛用于计算机系统中。

在设计FPGA与DDR3之间的电路时,需要考虑以下几个方面:1. 时序和时钟分配,在设计FPGA与DDR3之间的电路时,需要仔细考虑时序和时钟分配。

DDR3存储器需要严格的时序控制,以确保数据能够正确地被读取和写入。

因此,需要合理地分配时钟信号,并确保时序满足DDR3存储器的要求。

2. 信号完整性,DDR3存储器的工作频率较高,因此在设计FPGA与DDR3之间的电路时,需要考虑信号完整性的问题。

这包括地线设计、阻抗匹配、信号线长度匹配等方面的考虑,以确保信号传输的稳定性和可靠性。

3. 控制信号和数据信号的处理,DDR3存储器的接口复杂,需要处理大量的控制信号和数据信号。

在设计FPGA与DDR3之间的电路时,需要合理地处理这些信号,确保它们能够准确地传输和处理。

4. 电源和地线设计,DDR3存储器对电源和地线的要求较高,需要提供稳定的电源和地线。

在设计FPGA与DDR3之间的电路时,需要考虑电源和地线的布局和连接,以确保它们能够满足DDR3存储器的要求。

5. 错误检测和纠正,DDR3存储器通常具有错误检测和纠正的功能,可以检测和纠正存储器中的错误。

在设计FPGA与DDR3之间的电路时,需要考虑如何利用这些功能,以提高系统的可靠性和稳定性。

总的来说,设计FPGA与DDR3之间的电路需要综合考虑时序、信号完整性、控制信号和数据信号处理、电源和地线设计以及错误检测和纠正等方面的因素,以确保系统能够稳定可靠地工作。

同时,还需要遵循DDR3存储器厂商的规格和建议,以确保设计的合理性和可靠性。

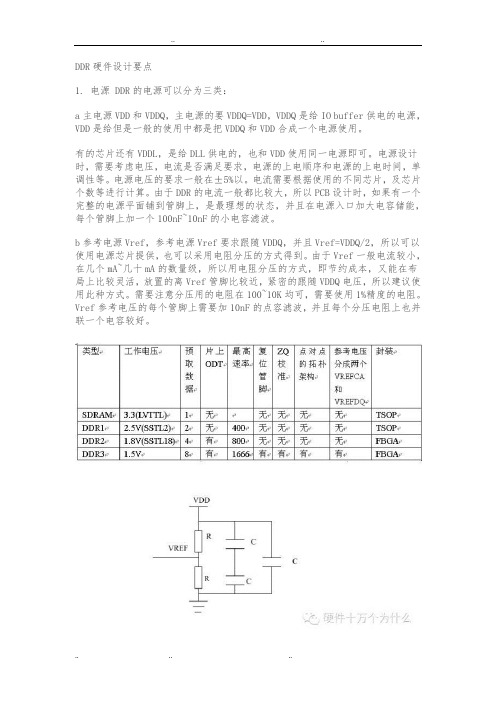

DDR硬件设计要点1. 电源 DDR的电源可以分为三类:a主电源VDD和VDDQ,主电源的要VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以。

电流需要根据使用的不同芯片,及芯片个数等进行计算。

由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。

b参考电源Vref,参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。

由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。

需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。

Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。

C、用于匹配的电压VTT(Tracking Termination Voltage)VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。

如果使用VTT,则VTT的电流要比较大的,所以需要走线使用铜皮铺过去。

并且VTT要求电源即可以吸电流,又可以灌电流才可以。

一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求。

而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

layout硬件设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 系统规划确定硬件系统的功能和性能要求。

制定设计规格和技术指标。

DDR3布局的那些事儿前面高速先生团队已经讲解过众多的DDR3理论和仿真知识,下面就开始谈谈我们LATOUT攻城狮对DDR3设计那些事情了,那么布局自然是首当其冲了。

对于DDR3的布局我们首先需要确认芯片是否支持FLY-BY走线拓扑结构,来确定我们是使用T拓扑结构还是FLY-BY拓扑结构.常规我们DDR3的布局满足以下基本设计要求即可:1.考虑BGA可维修性:BGA周边器件5MM禁布,最小3MM。

2.DFM 可靠性:按照相关的工艺要求,布局时器件与器件间满足DFM的间距要求;且考虑元件摆放的美观性。

3.绝对等长是否满足要求,相对长度是否容易实现:布局时需要确认长度限制,及时序要求,留有足够的绕等长空间。

4.滤波电容、上拉电阻的位置等:滤波电容靠近各个PIN放置,储能电容均匀放置在芯片周边(在电源平面路径上);上拉电阻按要求放置(布线长度小于500mil)。

注意:如有提供DEMO板或是芯片手册,请按照DEMO板或是芯片手册的要求来做。

1.滤波电容的布局要求电源设计是PCB设计的核心部分,电源是否稳定,纹波是否达到要求,都关系到CPU系统是否能正常工作。

滤波电容的布局是电源的重要部分,遵循以下原则:CPU端和DDR3颗粒端,每个引脚对应一个滤波电容,滤波电容尽可能靠近引脚放置。

线短而粗,回路尽量短;CPU和颗粒周边均匀摆放一些储能电容,DDR3颗粒每片至少有一个储能电容。

图1:VDD电容的布局(DDR颗粒单面放)如图2所示:VDD电容的布局(DDR颗粒正反贴)DDR 正反贴的情况,电容离BGA 1MM,就近打孔;如可以跟PIN就近连接就连接在一起。

2.VREF电路布局在DDR3中,VREF分成两部分:一个是为命令与地址信号服务的VREFCA;另一个是为数据总线服务的VREFDQ。

在布局时,VREFCA、VREFDQ的滤波电容及分压电阻要分别靠近芯片的电源引脚,如图3所示。

图3:VREF电路布局3.匹配电阻的布局为了提高信号质量,地址、控制信号一般要求在源端或终端增加匹配电阻;数据可以通过调节ODT 来实现,所以一般建议不用加电阻。

DDR3 布局布线译自飞思卡尔官方文档Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications ProcessorsIMX6 Serial Layout Recommendations目录1.DDR 原理性连接框图 (3)2。

DDR 布局布线规则 (4)3。

DDR 布线细节 (5)3.1 数据线的交换 (6)3.2 DDR3(64bits)T 型拓扑介绍 (6)3。

3 DDR3(64bits)Fly‐by 型拓扑介绍 (6)3.4 2GB DDR 布局布线建议 (6)3.5 4GB DDR 布局布线建议 (7)4.DDR 布局布线实例 (8)4.1 4 片DDR T 型拓扑实例 (9)4.2 8 片DDR Fly‐by 型拓扑实例 (13)5。

高速信号布线建议 (20)6.地平面设计建议 (20)7。

DDR POWER 布线建议 (23)8.参考 (24)9。

声明............................................................................................. 错误!未定义书签。

1.DDR 原理性连接框图图 1、图 2 为 I.MX6DQ/SDL 与 DDR 连接框图,连接示意一目了然。

图 1 DDR3 与 i.MX6DQ/SDL 连接示意图图 2 LPDDR2 与 i.MX6DQ/SDL 连接示意图2.DDR 布局布线规则DDR3 在布线中十分重要,它必须考虑阻抗匹配问题,通常单端为50Ω,差分100Ω. 图 3 给出了 DDR 及其去耦电容的最终布局,其中左图是顶层布局,右图为底层布局,共计 4 片 DDR3 芯片,顶层、底层各两片。

DDR 应该尽量靠近 CPU,这样可以减小寄生参数和传播延时。

ddr3电路设计DDR3是一种流行的内存标准,广泛应用于计算机的内存子系统中。

DDR3电路设计的关键在于确保数据传输的精确性和速度。

本文将讨论DDR3电路设计的主要方面。

首先,DDR3的电路设计必须考虑时序。

DDR3采用双倍速时钟,并使用复杂的电路实现内部时序要求。

因此,在设计DDR3电路时,需要掌握时钟源和时序分析工具,以确保电路能够在正确的时序下运行。

同时,要特别注意时序与接口匹配,特别注意输入和输出以及速度的匹配。

其次,电源稳定性也是DDR3电路设计的一个重要方面。

DDR3的工作电压为1.5V,内部时序比较严格。

如果电源不稳定,会导致内部时序失调和数据传输的不稳定。

因此,在设计DDR3电路时,需要考虑使用高品质的电源和稳压控制电路,以确保系统的电源稳定性。

第三,DDR3电路设计必须考虑阻抗匹配。

DDR3内部线路的阻抗要求非常高,以确保数据信号传输的正确性。

因此,在DDR3电路设计中,设计师必须确保阻抗匹配,包括内部线路阻抗和外部元件阻抗匹配。

通过使用高品质的PCB材料和布线方式,可以实现更好的阻抗匹配。

最后,DDR3电路设计必须考虑EMI(电磁干扰)和ESD(静电放电)等问题。

DDR3的高速数据传输和内部时序要求使其在EMI和ESD方面非常敏感。

在DDR3电路设计中,需要考虑EMI和ESD的电磁干扰特性,采用合适的滤波和抑制措施,例如使用布局合理的地和电源平面,以及使用EMI滤波器等。

总之,DDR3电路设计是一项复杂的工作,需要掌握时序、电源、阻抗、EMI和ESD等方面的知识。

采用高品质的元件、PCB材料和布线方式,可以最大限度地提高DDR3电路的精确性和速度。

DDR硬件设计要点1.电源 DDR的电源可以分为三类:a 主电源 VDD和 VDDQ,主电源的要求是 VDDQ=VDD,VDDQ是给 IO buffer 供电的电源, VDD是给但是一般的使用中都是把 VDDQ和 VDD合成一个电源使用。

有的芯片还有 VDDL,是给 DLL供电的,也和 VDD使用同一电源即可。

电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。

电流需要根据使用的不同芯片,及芯片个数等进行计算。

由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个 100nF~10nF的小电容滤波。

b 参考电源Vref ,参考电源Vref 要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。

由于Vref 一般电流较小,在几个 mA~几十 mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离 Vref 管脚比较近,紧密的跟随 VDDQ电压,所以建议使用此种方式。

需要注意分压用的电阻在 100~10K均可,需要使用 1%精度的电阻。

Vref 参考电压的每个管脚上需要加 10nF 的点容滤波,并且每个分压电阻上也并联一个电容较好。

C、用于匹配的电压VTT(Tracking Termination Voltage)VTT为匹配电阻上拉到的电源, VTT=VDDQ/2。

DDR的设计中,根据拓扑结构的不同,有的设计使用不到 VTT,如控制器带的 DDR器件比较少的情况下。

如果使用VTT,则 VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。

并且VTT 要求电源即可以吸电流,又可以灌电流才可以。

一般情况下可以使用专门为 DDR 设计的产生 VTT的电源芯片来满足要求。