第21章 触发器和时序逻辑电路2

- 格式:pps

- 大小:1.07 MB

- 文档页数:33

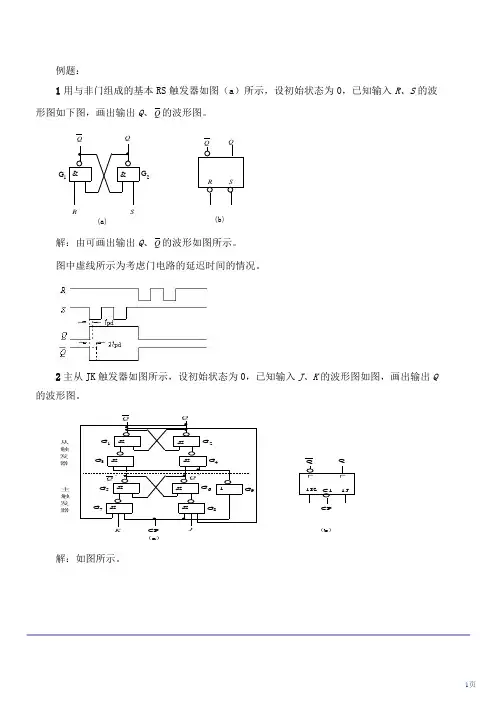

例题:1用与非门组成的基本RS 触发器如图(a )所示,设初始状态为0,已知输入R 、S 的波形图如下图,画出输出Q 、Q 的波形图。

&&G G 12(a)(b)R RS SQQQ Q解:由可画出输出Q 、Q 的波形如图所示。

图中虚线所示为考虑门电路的延迟时间的情况。

2主从JK 触发器如图所示,设初始状态为0,已知输入J 、K 的波形图如图,画出输出Q 的波形图。

CP G 4G Q 1J 1K Q(b)3C1&G &G 2&1&&7G &56&CP8&G G G 19G ''┌┌(a)触从器发主触发器QQ Q Q J K解:如图所示。

3维持—阻塞D触发器如图所示,设初始状态为0,已知输入D的波形图如图所示,画出输出Q的波形图。

解:由于是边沿触发器,在波形图时,应注意以下两点:(1)触发器的触发翻转发生在时钟脉冲的触发沿(这里是上升沿)。

(2)判断触发器次态的依据是时钟脉冲触发沿前一瞬间(这里是上升沿前一瞬间)输入端的状态。

根据D触发器的功能表或特性方程或状态转换图可画出输出端Q的波形图如图所示。

12345CPDQ图波形图第22章时序逻辑电路大纲要求:掌握时序逻辑电路的特点及组成了解时序逻辑电路的分析步骤和方法,计数器的状态转换表、状态转换图和时序图的画法;触发器触发方式不同时对不同功能计数器的应用连接掌握计数器的基本概念、功能及分类了解二进制计数器(同步和异步)逻辑电路的分析了解寄存器和移位寄存器的结构、功能和简单应用了解计数型和移位寄存器型顺序脉冲发生器的结构、功能和分析应用计数器是数字电路和计算机中广泛应用的一种逻辑部件,可累计输入脉冲的个数,可用于定时、分频、时序控制等。

按计数功能:加法计数器、减法计数器、可逆计数器按计数脉冲引入方式:异步计数器、同步计数器按计数制:二进制计数器、十进制计数器、N 进制计数器22.1 二进制计数器按二进制的规律累计脉冲个数,它也是构成其它进制计数器的基础。

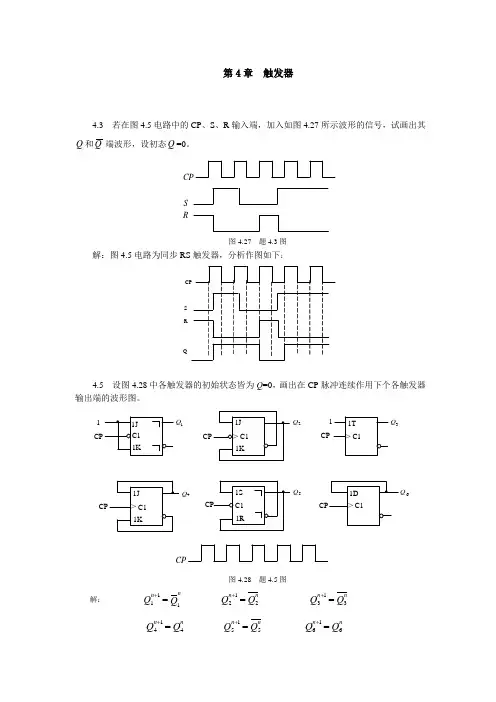

第4章 触发器4.3 若在图4.5电路中的CP 、S 、R 输入端,加入如图4.27所示波形的信号,试画出其Q 和Q 端波形,设初态Q =0。

SRCP图4.27 题4.3图解:图4.5电路为同步RS 触发器,分析作图如下:S RQ4.5 设图4.28中各触发器的初始状态皆为Q =0,画出在CP 脉冲连续作用下个各触发器输出端的波形图。

Q 11CPQ 3CPCPQ 2Q 6Q 4Q 5CP图4.28 题4.5图解:Q Q nn 111=+ Q Q n n 212=+ Q Q nn 313=+Q Q n n 414=+ Q Q n n 515=+ Q Q nn 616=+Q 1CP Q 2Q 3Q 4Q 5Q64.6 试写出 图4.29(a)中各触发器的次态函数(即Q 1 n+1 、 Q 2 n+1与现态和输入变量之间的函数式),并画出在图4.29(b )给定信号的作用下Q 1 、Q 2的波形。

假定各触发器的初始状态均为Q =0。

1A BCP>1D C1=1A BQ 1Q 2Q 2(a)BA(b)图4.29题4.6图解:由图可见:Q B A AB Q n n 111)(++=+ B A Q n ⊕=+12B A Q 2Q 14.7 图4.30(a )、(b )分别示出了触发器和逻辑门构成的脉冲分频电路,CP 脉冲如图4.30(c )所示,设各触发器的初始状态均为0。

(1)试画出图(a )中的Q 1、Q 2和F 的波形。

(2)试画出图(b )中的Q 3、Q 4和Y 的波形。

Y(b )(c )CPQ 1Q 2(a )图4.30 题4.7图解: (a )Q Q nn 211=+ QQ nn 112=+ Q F 1CP ⊕= R 2 = Q 1 低电平有效CPQ 1Q 2F(b )Q Q Q n n n 4313=+ Q Q Q n n n 4314=+ Q Q Y nn43=CP 3= CP 上降沿触发 CP 4= CP 下降沿触发CPQ 3Q 4Y4.8 电路如图4.31所示,设各触发器的初始状态均为0。

《时序逻辑电路》知识要点复习一、时序逻辑电路1、时序逻辑电路:电路的输出状态不仅与同一时刻的输入状态有关,也与电路原状态有关。

时序逻辑电路具有记忆功能。

2、时序逻辑电路分类:可分为两大类:同步时序电路与异步时序电路。

(1)同步时序电路:各触发器都受到同一时钟脉冲控制,所有触发器的状态变化都在同一时刻发生。

(2)异步时序电路:各触发器没有统一的时钟脉冲(或者没有时钟脉冲),各触发器状态变化不在同一时刻发生。

计数器、寄存器都属于时序逻辑电路。

3、时序逻辑电路由门电路和触发器组成,触发器是构成时序逻辑电路的基本单元。

二、计数器1、计数器概述:(1)计数器:能完成计数,具有分频、定时和测量等功能的电路。

(2)计数器的组成:由触发器和门电路组成。

2、计数器的分类:按数制分:二进制计数器、十进制计数器、N 进制(任意进制)计数器;按计数方式分:加法计数器、减法计数器、可逆计数器;按时钟控制分:同步计数器、异步计数器。

3、计数器计数容量(长度或模):计数器能够记忆输入脉冲的数目,就称为计数器的计数容量(或计数长度或计数模),用 M 表示。

3 位二进制同步加法计数器:M=23=8,n 位二进制同步加法计数器:M=2n,n 位二进制计数器需要用n个触发器。

4、二进制计数器(1)异步二进制加法计数器:如下图电路中,四个JK触发器顺次连接起来,把上一触发器的Q 端输出作为下一个触发器的时钟信号,CP0=CP CP1=QCP2=Q1CP3=Q2,J=K=1J1=K1=1 J2=K2=1 J3=K3=1Q3Q2Q1Q为计数输出,Q3为进位输出,Rd 为异步复位(清0)这样构成了四位异步二进制加计数器。

在计数前清零,Q3Q2Q1Q=0000;第一个脉冲输入后,Q3Q2Q1Q=0001;第二个脉冲输入后,Q3Q2Q1Q=0010;第三个脉冲输入后,Q3Q2Q1Q=0011,……,第15个脉冲输入后,Q3Q2Q1Q=1111,第16个脉冲输入后,Q3Q2Q1Q=0000,并向高位输出一个进位信号,当下一个脉冲来时,进入新的计数周期。

【电⼯基础知识】时序逻辑电路时序逻辑电路定义时序逻辑电路主要由触发器构成。

在理论中,时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输⼊,还与前⼀时刻输⼊形成的状态有关。

这跟相反,组合逻辑的输出只会跟⽬前的输⼊成⼀种函数关系。

换句话说,时序逻辑拥有储存器件()来存储信息,⽽组合逻辑则没有。

从时序逻辑电路中,可以建出两种形式的::输出只跟内部的状态有关。

(因为内部的状态只会在时脉触发边缘的时候改变,输出的值只会在时脉边缘有改变):输出不只跟⽬前内部状态有关,也跟现在的输⼊有关系。

时序逻辑因此被⽤来建构某些形式的的,延迟跟储存单元,以及有限状态⾃动机。

⼤部分现实的电脑电路都是混⽤组合逻辑跟时序逻辑。

按“功能、⽤途”分为:1. 寄存器;2. 计数(分频)器;3. 顺序(序列)脉冲发⽣器;4. 顺序脉冲检测器;5. 码组变换器;寄存器定义寄存器:能够暂时存放数码、指令、运算结果的数字逻辑部件,称为寄存器。

寄存器的功能是存储,它是由具有存储功能的组合起来构成的。

⼀个触发器可以存储1位⼆进制代码,故存放n位⼆进制代码的寄存器,需⽤n个触发器来构成。

[1]按照功能的不同,可将寄存器分为基本寄存器和两⼤类。

基本寄存器只能并⾏送⼊数据,也只能并⾏输出。

移位寄存器中的数据可以在移位脉冲作⽤下依次逐位右移或左移,数据既可以并⾏输⼊、并⾏输出,也可以串⾏输⼊、串⾏输出,还可以并⾏输⼊、串⾏输出,或串⾏输⼊、并⾏输出,⼗分灵活,⽤途也很⼴。

[1]知识点概述:1、寄存器,就是能够记忆或存储0和1数码的基本部件。

通常都是由各种触发器和门电路来构成的。

2、寄存器分为仅能存储0和1数码的数码寄存器,和既能存储数码同时也能实现数码的左移或右移的寄位移寄存器。

3、在实际中,通常使⽤集成寄存器。

本节讲解了寄存器的电路构成、⼯作原理、对74LS194双向移位寄存器的使⽤进⾏了介绍。

4、有点寄存器具有左移右移的功能寄存器电路如下:(1)由四个D触发器构成,因为每⼀个D触发器可以存放1位⼆进制信息,所以上述电路的寄存器可存放⼀个4位⼆进制数码,⼀般也把这种寄存器称为数码寄存器。

第21章 触发器和时序逻辑电路一、填空题1、JK 触发器的特性方程为:=+1n Q ________________________。

2、时钟触发器按照结构和触发方式不同可分为:_________、__________、_________和主从式触发器四种。

3、T 触发器的特性方程为=+1n Q _________________。

4、4个触发器组成的寄存器可以存储__________位二进制数。

5、将JK 触发器的J 端连在Q 端上,K 端接高电平。

假设)(t Q =0,则经过50个CP 脉冲作用后,它的状态)50(+t Q =_____。

6、对于时钟RS 触发器,若要求其输出“0”状态保持不变,则输入的RS 信号应为________。

7、组成计数器的各个触发器的状态能在时钟信号到达时同时翻转,它属于__________ 计数器。

(填“同步”或“异步”)8、当JK 触发器的输入J=1,K=0时,触发器的次态Q n+1=____________。

9、若要构成十二进制计数器,最少要用__________个触发器。

10、构成一个模6的同步计数器最少要________个触发器。

11、一个 JK 触发器有____个稳态,它可存储____位二进制数。

二、选择题1、下列触发器中有空翻现象的是_________。

A 、同步式触发器B 、维持阻塞式触发器C 、主从式触发器D 、边沿式触发器 2、在以下各种电路中,属于时序电路的有__________。

A 、译码器B 、计数器C 、数据选择器D 、编码器 3、JK 触发器当J=K=1时,Q n+1=__________。

A 、0B 、1C 、Q nD 、 Q n4、下列触发器中逻辑功能最多是_______。

A 、J-K 触发器B 、D 触发器C 、T 触发器D 、T ′触发器 5、在CP 有效的情况下,当输入端D=0时,则D 触发器的输出端=+1n Q ________。

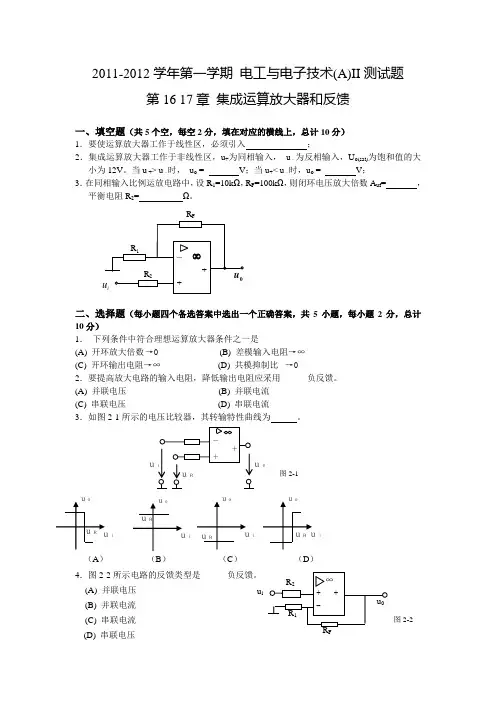

2011-2012学年第一学期 电工与电子技术(A)II 测试题第16 17章 集成运算放大器和反馈一、填空题(共5个空,每空2分,填在对应的横线上,总计10分)1.要使运算放大器工作于线性区,必须引入 ;2.集成运算放大器工作于非线性区,u +为同相输入, u –为反相输入,U o(sat)为饱和值的大小为12V 。

当u +> u –时, u o = V ;当u +< u –时,u o = V ; 3.在同相输入比例运放电路中,设R 1=10k Ω,R F =100k Ω,则闭环电压放大倍数A u f = ,平衡电阻R 2= Ω。

二、选择题(每小题四个备选答案中选出一个正确答案,共5小题,每小题2分,总计10分)1. 下列条件中符合理想运算放大器条件之一是 (A) 开环放大倍数 →0 (B) 差模输入电阻→∞ (C) 开环输出电阻→∞ (D) 共模抑制比 →02.要提高放大电路的输入电阻,降低输出电阻应采用______负反馈。

(A) 并联电压 (B) 并联电流 (C) 串联电压 (D) 串联电流3.如图2-1所示的电压比较器,其转输特性曲线为 。

(A )(B ) (C) (D )4.图2-2所示电路的反馈类型是______负反馈。

(A) 并联电压 (B) 并联电流 (C) 串联电流 (D) 串联电压u iiii i0图2-15.运算放大器电路如图2-3所示,其最大输出电压为±12V ,已知1-=i u V ,则输出电压0u 为( )。

(A) 12V (B) -12V (C) 1V (D) -1Vi u三、计算下列各题(共3小题,总计30分)1.如图3-1所示是一个电压电流变换电路,R L 是负载电阻,试求负载电流i o 与输入电压u i 的关系,并说明它是何种类型的负反馈电路。

(10分)2.电路如图3-2所示,Ω=k 101R ,Ω=k 202R ,Ω=k 100F R ,V 2.01=i u ,V 5.02-=i u ,求输出电压 。

第六章时序逻辑电路时序逻辑电路简称时序电路,与组合逻辑电路并驾齐驱,是数字电路两大重要分支之一。

本章首先介绍时序逻辑电路的基本概念、特点及时序逻辑电路的一般分析方法。

然后重点讨论典型时序逻辑部件计数器和寄存器的工作原理、逻辑功能、集成芯片及其使用方法及典型应用。

最后简要介绍同步时序逻辑电路的设计方法。

6.1 时序逻辑电路的基本概念一.时序逻辑电路的结构及特点时序逻辑电路——电路任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。

时序电路中必须含有具有记忆能力的存储器件。

存储器件的种类很多,如触发器、延迟线、磁性器件等,但最常用的是触发器。

由触发器作存储器件的时序电路的基本结构框图如图6.1.1所示,一般来说,它由组和电路和触发器两部分组成。

1 X i X Z1 Z jÊäÈëÐźÅÐźÅÊä³ö·¢Æ÷´¥·¢ÆÐźÅÊä³öÐźÅͼ6.1.1 ʱÐòÂß¼µç·¿òͼ二.时序逻辑电路的分类按照电路状态转换情况不同,时序电路分为同步时序电路和异步时序电路两大类。

按照电路中输出变量是否和输入变量直接相关,时序电路又分为米里(Mealy)型电路和莫尔(Moore)型电路。

米里型电路的外部输出Z既与触发器的状态Q n有关,又与外部输入X有关。

2011-2012学年第一学期电工与电子技术(A)II测试题第16 17章集成运算放大器和反馈一、填空题(共5个空,每空2分,填在对应的横线上,总计10分)1.要使运算放大器工作于线性区,必须引入深度电压负反馈;2.集成运算放大器工作于非线性区,u+为同相输入, u–为反相输入,U o(sat)为饱和值的大小为12V。

当u +> u–时, u o = 12 V;当u+< u–时,u o = -12 V;3.在同相输入比例运放电路中,设R1=10kΩ,R F=100kΩ,则闭环电压放大倍数A uf= 11 ,平衡电阻R2= 100/11 Ω。

二、选择题(每小题四个备选答案中选出一个正确答案,共5小题,每小题2分,总计10分)1.下列条件中符合理想运算放大器条件之一是B(A) 开环放大倍数→0 (B) 差模输入电阻→∞(C) 开环输出电阻→∞ (D) 共模抑制比→02.要提高放大电路的输入电阻,降低输出电阻应采用___C___负反馈。

(A) 并联电压 (B) 并联电流(C) 串联电压 (D) 串联电流A 。

3.如图2-1所示的电压比较器,其转输特性曲线为(A)(B)(C)(D)4.图2-2所示电路的反馈类型是___D___(A) 并联电压(B) 并联电流(C) 串联电流(D) 串联电压反馈在-,即负反馈/直接从输出端反馈,为电压反馈。

5.运算放大器电路如图2-3所示,其最大输出电压为±12V,已知1-=iu V,则输出电压u 为( A )。

(A) 12V (B) -12V (C) 1V (D) -1Viu三、计算下列各题(共3小题,总计30分)1.如图3-1所示是一个电压电流变换电路,R L是负载电阻,试求负载电流i o与输入电压u i 的关系,并说明它是何种类型的负反馈电路。

(10分)*******2.电路如图3-2所示,Ω=k101R,Ω=k202R,Ω=k100FR,V2.01=iu,V5.02-=iu,求输出电压。

第21章 触发器和时序逻辑电路191、触发器按其工作状态是否稳定可分为( b )。

(a)RS 触发器,JK 触发器,D 触发器,T 触发器;(b)双稳态触发器,单稳态触发器,无稳态触发器;(c)主从型触发器,维持阻塞型触发器。

192、逻辑电路如图所示,当A=“1”时,基本RS 触发器( c )。

(a)置“1”; (b)置“0”; (c)保持原状态。

A193、 逻辑电路如图所示,分析C ,S ,R 的波形,当初始状态为“0”时,输出Q 是“0”的瞬间为( c )。

(a)1t ; (b)2t ; (c)3t 。

C S Rt 1t 2t3194、 某主从型JK 触发器,当J=K=“1”时,C 端的频率f=200Hz ,则Q 的频率为( c )。

(a)200Hz ; (b)400Hz ; (c)100Hz 。

195、逻辑电路如图所示,当A=“1”时,C 脉冲来到后JK 触发器( a )。

(a)具有计数功能; (b)置“0”; (c)置“1”。

A196、 逻辑电路如图所示,A=“0”时,C 脉冲来到后D 触发器( b )。

(a)具有计数器功能; (b)置“0”; (c)置“1”。

A 197、逻辑电路如图所示,分析C 的波形,当初始状态为“0”时,输出Q是“0”的瞬间为( a )。

(a) 1t ; (b)2t ; (c)3t 。

C t 1t 2t 3198、逻辑电路如图所示,它具有( a )。

(a)D 触发器功能; (b)T 触发器功能; (c)T'触发器功能。

199、逻辑电路如图所示,它具有( b )。

(a)D 触发器功能; (b)T 触发器功能;(c)T'触发器功能。

200、时序逻辑电路与组合逻辑电路的主要区别是( c )。

(a)时序电路只能计数,而组合电路只能寄存;(b)时序电路没有记忆功能,组合电路则有;(c)时序电路具有记忆功能,组合电路则没有。

201、寄存器与计数器的主要区别是( b )。

常用时序组合逻辑电路及其应用寄存器计数器通过学习理解寄存器及计数器的概念和工作原理,掌握时序电路的分析方法。

21.2 寄存器◆按功能分数码寄存器移位寄存器串行并行◆按存取数码的方式在数字电路中,用来存放二进制数据或代码的电路称为寄存器。

用来暂时存放数据或指令,然后根据需要取出数码。

寄存器分类:一个触发器组成1位的数码寄存器CP上升沿,Q =DCP高电平、低电平、下降沿,Q 均不变R SD CPQQ21.2.1 数码寄存器寄存器是由具有存储功能的触发器组合起来构成的。

一个触发器可以存储1位二进制代码,存放n 位二进制代码的寄存器,需用n个触发器来构成。

通常由D触发器或R-S触发器组成D CPQ 4Q 3Q 2Q 1&&&&Q QDQ QDQ QDQ QDA 1A 2A 3A 4CLR取数脉冲接收脉冲( CP )四位数码寄存器:1111111110特点:数码从四个输入端同时输入,从四个输出端同时输出。

又称并行输入并行输出寄存器。

待存数码为11010000寄存指令取出指令1、预先清零2、存入数码3、取出数码数码寄存器由8D 集成电路74LS273组成8位二进制数寄存器D 3D 2D 1D 03210R+5V74LS2731D8D1Q8Q 8D 寄存器4567D 4D 5D 6D 7 CP 8位二进制数D 7~D 0移位寄存器除具寄存器的功能外,还可将数码移位。

所谓“移位”,就是将寄存器所存各位数据,在每个移位脉冲的作用下,向左或向右移动一位。

根据移位方向,常把它分成三种:寄存器左移寄存器右移寄存器双向移位左移寄存器:在时钟脉冲的作用下,低位寄存器的数码送给高位寄存器,作为高位寄存器的次态输出;右移寄存器:在时钟脉冲的作用下,高位寄存器的数码送给低位寄存器,作为低位寄存器的次态输出;21.2.2 移位寄存器数码存入端数码取出端D 触发器组成的四位右移寄存器清零11010110 0 0 00 0 000 0101101CPQ 4 Q 3 Q 2 Q 1D 4DC R DR DDC DC DCR DR DD 3D 2D 1移位脉冲CP1234高1、单向移位寄存器移位清零D CDCDCDCR DR DR DR DQ 4 Q 3 Q 2 Q 1D 4CP1 0 0 00 1 0 0 1 1 01◆取数:令D 4= 0,再输入4 个移位CP 脉冲,1101 将从低位到高位按CP 节拍由Q 1 端输出◆串行输入,串行输出。

Q 4 Q 3 Q 2 Q 1CP12341 1 01→ D 40 0 0 010 1 0 D 4→D 4→D 4→D 4→右移寄存器波形图12345678C 1011DQ 0Q 3Q 2Q 11110待存数据1101存入寄存器111从Q 1取出左移移位寄存器:从高位移动。

p296寄存器按输入输出分类并行输入/串行输入/并行输出并行输入/串行输入/串行输出F3F2F1F00123Q 0Q 1Q 2Q 3F3F2F1F0dQ 0Q 1Q 2Q 3F3F2F1F0d 0d 1d 2d3Q 3Q 3F3F2F1F0d2. 集成电路双向移位寄存器(74LS194,国产CT1194)并行输入数据右移串入数据输出清0端时钟左移串入数据Q0 Q1 Q2 Q3D SR D0 D1 D2 D3 D SLC RS 1S 0CP74LS194011110 00 11 01 1直接清零保持右移(从Q 0向右移动)左移(从Q 3向左移动)并行输入R D C S 1S 0功能⨯⨯⨯CT74LS194功能表U CC Q 0Q 1Q 2Q 3S 1S 0C161514131211109CT74LS19413456782D 0D 1D 2D 3D SR D SL R D GND用双向移位寄存器74LS194组成节日彩灯控制电路Q4 Q3 Q2 Q1 D SR D4 D3 D2 D1 D SLC RS 1S 0CP 74LS194+5V+5VS 1=0,S 0=1右移控制Q4 Q3 Q2 Q1 D SR D4 D3 D2 D1 D SL C RS 1S 0CP 74LS194+5V1CP1SQ=0时LED 亮清0按键1k 二极管发光LED 01121.3计数器2、分类加法计数器减法计数器可逆计数器(按计数功能)异步计数器同步计数器(按计数脉冲引入方式)二进制计数器十进制计数器N 进制计数器(按计数制)1. 计数器的功能累计输入脉冲的个数;用于定时、分频并广泛用于数字测量、运算和控制等等。

掌握对计数器类型的判断21.3.1 二进制计数器按二进制的规律累计脉冲个数,它也是构成其它进制计数器的基础。

要构成n 位二进制计数器,需用n 个具有计数功能的触发器。

8位二进制表示的最大数为:11111111B=D =2551-28二进制数所表示数的范围:4位二进制表示的最大数为:1111B=15D1-24=16位二进制表示的最大数为:D=655351-2161. 异步二进制加法计数器异步:计数脉冲CP 不是同时加到各位触发器。

•最低位触发器由计数脉冲触发翻转,其他各位触发器由相邻低位触发器输出的进位脉冲来触发。

•因此各位触发器状态变换的时间先后不一,只有在前级触发器翻转后,后级触发器才能翻转。

QD 0Q1D 1Q2D 2Q 0Q 1Q 2CP 计数脉冲异步: 各触发器不同时翻转, 从低位到高位依次翻转如:二进制数Q 2Q 1Q 00 0 0 0 1 0 0 12 0 1 0 3 0 1 14 1 0 0 5 1 0 16 1 1 0 7 1 1 18 0 0 0脉冲数(C )三位二进制加法计数器状态表从状态表可看出:最低位触发器来一个脉冲就翻转一次,每个触发器由1变为0 时,要产生进位信号,这个进位信号应使相邻的高位触发器翻转。

1010当J 、K =1时,具有计数功能,每来一个脉冲触发器就翻转一次.清零R DQJ KQQ 0F0QJKQQ 1F1QJ KQQ 2F2CP计数脉冲三位异步二进制加法计数器在电路图中J 、K悬空表示J 、K =1下降沿触发翻转每来一个CP 翻转一次当相邻低位触发器由1变0 时翻转异步二进制加法器工作波形2分频4分频8分频每个触发器翻转的时间有先后,与计数脉冲不同步C 4Q 0Q 1Q 200000101001111111100113T C Q3FF32T C Q2FF21T C Q1FF1T C Q0FF0CPR DT=1二进制计数器分析:首先熟知各触发器的翻转条件,了解其触发方式。

CP Q 3 Q 2 Q 1 Q 0Q 3 Q 2 Q 1 Q 00123456789…15160101010101…10 1 1 1 11 1 1 01 1 0 11 1 0 01 0 1 11 0 1 01 0 0 11 0 0 00 1 1 10 1 1 0……0 0 0 01 1 1 1加法计数减法计数4位二进制加法计数器状态转换表0011001100 (100)1111…10000000011 (10)Q 0Q 1Q 2Q 31 4 7 10 13 15 16 CP00101110010111110000十六分频四分频八分频二分频4位异步二进制加法计数器时序图CP 的后沿Q 0翻转Q 0的后沿Q 1翻转Q 1的后沿Q 2翻转Q 2的后沿Q 3翻转用4个J-K触发器组成4位异步二进制加法计数器Q QR S J KQQR SJ KQQR SJ KQQR SJ KR清0脉冲进位脉冲1Q234CP 异步计数器优点:电路简单、可靠缺点:速度慢用D 触发器构成三位二进制异步加法器??2、若构成减法计数器C 又如何连接?1、各触发器C 应如何连接?各D 触发器已接成T ´触发器,即具有计数功能C清零R D QDQ Q 0F0QDQ Q 1F1QDQ Q 2F2P301 例21.3.12. 同步二进制加法计数器异步二进制加法计数器线路联接简单。

各触发器是逐级翻转,因而工作速度较慢。

同步计数器:计数脉冲同时接到各位触发器,各触发器状态的变换与计数脉冲同步。

同步计数器由于各触发器同步翻转,因此工作速度快。

但接线较复杂。

同步计数器组成原则:根据翻转条件,确定触发器级间连接方式—找出J 、K 输入端的联接方式。

二进制数Q 2Q 1Q 00 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 1 1 0 7 1 1 18 0 0 0脉冲数(C )二进制加法计数器状态表从状态表可看出:最低位触发器F0每来一个脉冲就翻转一次;F1:当Q 0=1时,再来一个脉冲则翻转一次;F2:当Q 0=Q 1= 1时,再来一个脉冲则翻转一次。

四位二进制同步加法计数器级间连接的逻辑关系触发器翻转条件J、K 端逻辑表达式J、K端逻辑表达式F0每输入一C翻一次F1F2F3J0 =K0 =1Q0 =1J1 =K1 = Q0Q0 = Q1= 1J2 =K2 = Q1Q0 Q0 = Q1= Q2 = 1J3 =K3= Q1Q1Q0J0 =K0 =1J1 =K1 = Q0J2 =K2 = Q1Q0J3 =K3 = Q2Q1Q0由J、K端逻辑表达式,可得出四位同步二进制计数器的逻辑电路。

(只画出三位同步二进制计数器的逻辑电路)(加法)(减法)计数脉冲同时加到各位触发器上,当每个到来后触发器状态是否改变要看J、K的状态。

最低位触发器F0每一个脉冲就翻转一次;F1:当Q=1时,再来一个脉冲则翻转一次;F2:当Q=Q1= 1时,再来一个脉冲则翻转一次。

R DQJKQF0QJKQ1F1QJKQQ2F2C三位同步二进制加法计数器12345678 CQ0Q1Q2各触发器状态的变换和计数脉冲同步分析步骤:1. 先列写控制端的逻辑表达式:J 2= K 2= Q 1Q 0J 1= K 1= Q 0J 0= K 0 = 1Q 0:来一个CP ,它就翻转一次;Q 1:当Q 0=1时,它可翻转一次;Q 2:只有当Q 1Q 0=11时,它才能翻转一次。

2. 根据控制端的逻辑表达式分析各输出端的翻转条件:3.写状态表或画波形:Q 2Q 2J 2K 2Q 1Q 1J 1K 1Q 0Q 0J 0K 0&计数脉冲三位二进制同步加法计数器CP Q 0Q 1Q 2K 0 = 1J 1 = K 1= Q 0J 0 = Q 2J 2 = Q 1Q 0K 2 = 1Q 2 Q 1 Q 0J K C 11R DCPC J K C J K[例1] 分析电路的逻辑功能。

返回上一节CPQ 2 Q 1Q 0012345J 2 K 2 J 1K 1 J 0K 00001111111010 0100101011011001000◆结论:同步五进制加法计数器。