嵌入式系统教案-中断(全英)

- 格式:pptx

- 大小:86.72 KB

- 文档页数:30

第五章中断中断是指计算机在执行程序的过程中,当出现异常情况或特殊请求时,计算机停止现行程序的运行,转向对这些异常情况或特殊请求的处理,处理结束后再返回现行程序的间断处,继续执行原程序。

中断是单片机或ARM实时地处理内部或外部事件的一种机制。

换言之,中断可以作为ARM外围设备与CPU之间的一种联系或通信方式。

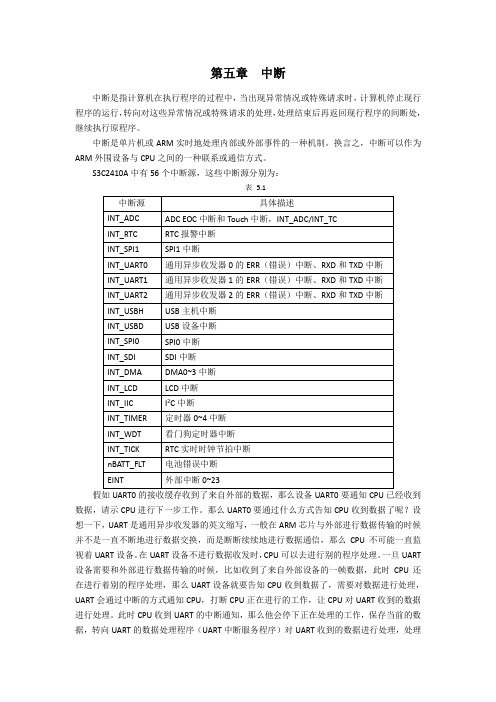

S3C2410A中有56个中断源,这些中断源分别为:表 5.1假如UART0的接收缓存收到了来自外部的数据,那么设备UART0要通知CPU已经收到数据,请示CPU进行下一步工作。

那么UART0要通过什么方式告知CPU收到数据了呢?设想一下,UART是通用异步收发器的英文缩写,一般在ARM芯片与外部进行数据传输的时候并不是一直不断地进行数据交换,而是断断续续地进行数据通信,那么CPU不可能一直监视着UART设备。

在UART设备不进行数据收发时,CPU可以去进行别的程序处理。

一旦UART 设备需要和外部进行数据传输的时候,比如收到了来自外部设备的一帧数据,此时CPU还在进行着别的程序处理,那么UART设备就要告知CPU收到数据了,需要对数据进行处理,UART会通过中断的方式通知CPU,打断CPU正在进行的工作,让CPU对UART收到的数据进行处理。

此时CPU收到UART的中断通知,那么他会停下正在处理的工作,保存当前的数据,转向UART的数据处理程序(UART中断服务程序)对UART收到的数据进行处理,处理完毕后如果没有其他设备的中断请求,CPU会跳转回UART中断之前的程序,调出中断时保存的数据继续运行中断之前的程序。

S3C2410A是以ARM920T为内核的ARM,ARM920T内核有两种中断模式:FIQ和IRQ。

IRQ全称为Interrupt Request,即是“中断请求”的意思。

FIQ全称为Fast Interrupt Request,即是“快速中断请求”的意思。

FIQ模式是特权模式中的一种,同时也属于异常模式一类。

中南大学嵌入式系统实验(二)中断实验学院:**************专业班级:*********姓名:*************学号:*************中断实验一.实验目的1.熟悉arm开发板中断原理。

并产生中断。

2.了解快速中断和普通中断。

编写嵌套中断实验。

二.实验器材PC机一台,周立功开发板一块三.实验原理EasyARM2103开发板提供了4个绿色发光二极管用作显示,电路如图1.1所示。

显示电路采用了灌电流的方式来驱动发光二极管,由于微控制器LPC2103 I/O口提供的灌电流大于其拉电流,采用此驱动方式可以保证二极管发光的亮度。

1.1Led电路原理四. 实验原理ARM体系的CPU有7种工作模式,可以通过软件来进行模式切换,或者发生各类中断、异常进行相应模式。

CPU可以识别两种类型中断,正常中断(IRQ)和快速响应中断(FIQ)状态寄存器的PSR中F和R位决定是中断的启闭。

为了使能中断,必须将PSR中F或R位清零,并且中断屏蔽寄存器相应位也要清零。

ARM中断分为子中断源和一般中断源,子中断源多了两个寄存器SUBRCPN(标识子中断源是否发生)INTSUBMSK(屏蔽子中断源)。

ARM中断发生过程如下:1.如果为子中断源,则SUBSRCPND寄存器相应位置1,然后根据子中断源屏蔽寄存器(INTSUBMSK)的设置来判断该中断是否被屏蔽,如未屏蔽,则在SRCPND寄存器相应位置1。

2.如果为非子中断则直接在SRCPND寄存器相应位置1。

3.如果INTMOD寄存器中该中断被设置为FIQ快速中断(相应位置1),即该中断立即执行。

如不是,则判断INTMSK寄存器中该中断是否被屏蔽,如未屏蔽,则进入中断优先仲裁器进行中断优先设置(PRIORITY寄存器)经过中断优先仲裁后,最高优先级的中断在INTPND寄存器中相应位置1(同一时间,此寄存器只有一位置1),INTOFFSET寄存器值用来表示INTPND寄存器置1位(即INTPND 寄存器中位[x]为1时,INTOFFSET寄存器值为x,可以用它确定是什么中断。

实验五中断控制实验(一)实验目的了解中断的作用;掌握嵌入式系统中断的处理流程;掌握ARM中断编程。

(二)实验设备计算机;ARM硬件仿真器;ARM开发板(三)实验硬件设置在做实验之前,先将开发板电源接好,将仿真器的USB连线与电脑相连,通电,然后按核心板的复位键。

(四)实验原理1. 中断的基本概念CPU与外设之间传输数据的控制方式通常有三种:查询方式、中断方式和DMA方式。

DMA 方式将在后续实验中说明。

查询方式的优点是硬件开销小,使用起来比较简单。

但在此方式下,CPU要不断地查询外设的状态,当外设未准备好时,CPU就只能循环等待,不能执行其它程序,这样就浪费了CPU的大量时间,降低了CPU的利用率。

为了解决这个矛盾,通常采用中断传送方式:即当CPU进行主程序操作时,外设的数据已存入输入端口的数据寄存器;或端口的数据输出寄存器已空,由外设通过接口电路向CPU发出中断请求信号,CPU在满足一定的条件下,暂停执行当前正在执行的主程序,转入执行相应能够进行输入/输出操作的子程序,待输入/输出操作执行完毕之后CPU再返回并继续执行原来被中断的主程序。

这样CPU就避免了把大量时间耗费在等待、查询状态信号的操作上,使其工作效率得以大大地提高。

能够向CPU发出中断请求的设备或事件称为中断源。

系统引入中断机制后,CPU与外设(甚至多个外设)处于“并行”工作状态,便于实现信息的实时处理和系统的故障处理。

中断方式的原理示意图如下所示。

图5-7 中断处理示意图1)中断响应中断源向CPU发出中断请求,若优先级别最高,CPU在满足一定的条件下,可以中断当前程序的运行,保护好被中断的主程序的断点及现场信息。

然后,根据中断源提供的信息,找到中断服务子程序的入口地址,转去执行新的程序段,这就是中断响应。

CPU响应中断是有条件的,如内部允许中断、中断未被屏蔽、当前指令执行完等。

2)中断服务子程序CPU响应中断以后,就会中止当前的程序,转去执行一个中断服务子程序,以完成为相应设备的服务。

嵌入式系统中断课程设计一、课程目标知识目标:1. 理解中断在嵌入式系统中的基本概念、作用和重要性;2. 掌握中断响应过程、中断优先级管理和中断嵌套的处理方法;3. 学会分析中断服务程序的设计和优化方法;4. 了解中断相关硬件原理,如中断控制器、中断请求和中断向量。

技能目标:1. 能够运用所学知识设计简单的中断服务程序,并实现中断功能;2. 能够运用调试工具对中断相关程序进行调试和优化;3. 能够分析和解决嵌入式系统中断相关的实际问题。

情感态度价值观目标:1. 培养学生对嵌入式系统及中断技术的兴趣,激发学习热情;2. 培养学生严谨的科学态度,注重实践与理论相结合;3. 培养学生团队协作意识,学会共同分析和解决问题。

本课程针对高年级学生,结合嵌入式系统课程特点,旨在提高学生理论联系实际的能力,培养学生解决实际工程问题的技能。

通过本课程的学习,使学生具备嵌入式系统中断相关领域的基本知识和实践技能,为后续深入学习打下坚实基础。

同时,注重培养学生的情感态度价值观,提高学生的综合素质。

二、教学内容1. 中断基本概念与原理:介绍中断的定义、分类及其在嵌入式系统中的作用;讲解中断响应过程、中断向量表和中断优先级管理。

教材章节:第三章“中断与异常”2. 中断控制器:分析中断控制器的原理、结构和功能;介绍中断请求、中断屏蔽和中断向量寄存器的作用。

教材章节:第三章“中断控制器”3. 中断服务程序设计:讲解中断服务程序的设计方法、中断处理流程和注意事项;举例说明中断服务程序的应用。

教材章节:第四章“中断服务程序设计”4. 中断嵌套与优先级管理:介绍中断嵌套的概念、实现方法及优先级管理的原则;分析中断嵌套时的程序执行流程。

教材章节:第五章“中断嵌套与优先级管理”5. 中断调试与优化:讲解中断相关程序的调试方法、技巧和优化策略;分析实际案例,提出解决方案。

教材章节:第六章“中断调试与优化”6. 实践环节:设计中断实验,使学生动手编写中断服务程序,实现特定功能;通过实验巩固理论知识,提高实际操作能力。