CMOS逻辑门电路

- 格式:ppt

- 大小:2.71 MB

- 文档页数:18

画CMOS逻辑门电路的方法1. 什么是CMOS逻辑门电路?CMOS(Complementary Metal-Oxide-Semiconductor)逻辑门电路是一种常见的数字逻辑电路,由MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)组成。

它使用p型和n型MOSFET互补对称的结构,能够在低功耗、高噪声抑制和高集成度等方面表现出色。

CMOS逻辑门电路可以实现各种基本逻辑功能,如与门、或门、非门、异或门等,并且可以通过组合这些基本逻辑门实现更复杂的数字逻辑功能。

2. CMOS逻辑门电路的基本结构CMOS逻辑门电路由p型和n型MOSFET组成,其中nMOSFET用于开关连接到地(低电平),而pMOSFET用于开关连接到正电源(高电平)。

这种互补对称的结构使得CMOS逻辑门在静态功耗上非常低。

以下是一些常见的CMOS逻辑门电路及其符号:•与非门(NAND gate)•或非门(NOR gate)•与门(AND gate)•或门(OR gate)•异或门(XOR gate)3. 画CMOS逻辑门电路的方法要画出CMOS逻辑门电路,可以按照以下步骤进行:步骤1:确定所需的逻辑功能首先,需要明确所需的逻辑功能。

根据逻辑表达式或真值表,确定所需实现的逻辑功能是与门、或门、非门还是其他类型的逻辑。

步骤2:选择合适的MOSFET类型根据所需的逻辑功能,选择合适的nMOSFET和pMOSFET。

通常情况下,nMOSFET用于实现低电平连接(0),而pMOSFET用于实现高电平连接(1)。

步骤3:绘制CMOS逻辑门的电路图根据所需的逻辑功能和选择的MOSFET类型,使用标准的CMOS逻辑门符号和电路图进行绘制。

确保符号和连接正确,并且布局整洁。

步骤4:确定电源和地线在绘制CMOS逻辑门电路时,需要为电路提供正电源和地线。

通常情况下,正电源用VDD表示,地线用GND表示。

CMOS 逻辑电路CMOS 是单词的首字母缩写,代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semicon ductor),它指的是一种特殊类型的电子集成电路(IC).集成电路是一块微小的硅片,它包含有几百万个 电子元件.术语 IC 隐含的含义是将多个单独的集成电路集成到一个电路中,产生一个十分紧凑的器件.在 通常的术语中,集成电路通常称为芯片,而为计算机应用设计的 IC 称为计算机芯片. 虽然制造集成电路的方法有多种,但对于数字逻辑电路而言 CMOS 是主要的方法.桌面个人计算机,工作 站,视频游戏以及其它成千上万的其它产品都依赖于 CMOS 集成电路来完成所需的功能.当我们注意到所 有的个人计算机都使用专门的 CMOS 芯片,如众所周知的微处理器,来获得计算性能时, CMOS IC 的 重要性就不言而喻了.CMOS 之所以流行的一些原因为: 逻辑函数很容易用 CMOS 电路来实现. CMOS 允许极高的逻辑集成密度.其含义就是逻辑电路可以做得非常小,可以制造在极小的面积上. 用于制造硅片 CMOS 芯片的工艺已经是众所周知,并且 CMOS 芯片的制造和销售价格十分合理. 这些特征及其它特征都为 CMOS 成为制造 IC 的主要工艺提供了基础. CMOS 可以作为学习在电子网络中如何实现逻辑功能的工具. CMOS 它允许我们用简单的概念和模型来构 造逻辑电路.而理解这些概念只需要基本的电子学概念. CMOS 逻辑门电路的系列及主要参数: 1.CMOS 逻辑门电路的系列 CMOS 集成电路诞生于 20 世纪 60 年代末,经过制造工艺的不断改进,在应用的广度上已与 TTL 平分秋 色,它的技术参数从总体上说,已经达到或接近 TTL 的水平,其中功耗,噪声容限,扇出系数等参数优于 TTL.CMOS 集成电路主要有以下几个系列. (1)基本的 CMOS——4000 系列. 这是早期的 CMOS 集成逻辑门产品,工作电源电压范围为 3~18V,由于具有功耗低,噪声容限大,扇出 系数大等优点,已得到普遍使用.缺点是工作速度较低,平均传输延迟时间为几十 ns,最高工作频率小于 5MHz. (2)高速的 CMOS——HC(HCT)系列. 该系列电路主要从制造工艺上作了改进,使其大大提高了工作速度,平均传输延迟时间小于 10ns,最高 工作频率可达 50MHz. 系列的电源电压范围为 2~6V. HC HCT 系列的主要特点是与 TTL 器件电压兼容, 它的电源电压范围为 4.5~5.5V.它的输入电压参数为 VIH(min)=2.0V;VIL(max)=0.8V,与 T TL 完全相同.另外,74HC/HCT 系列与 74LS 系列的产品,只要最后 3 位数字相同,则两种器件的逻辑 功能,外形尺寸,引脚排列顺序也完全相同,这样就为以 CMOS 产品代替 TTL 产品提供了方便.(3)先进的 CMOS——AC(ACT)系列 该系列的工作频率得到了进一步的提高,同时保持了 CMOS 超低功耗的特点.其中 ACT 系列与 TTL 器件 电压兼容,电源电压范围为 4.5~5.5V.AC 系列的电源电压范围为 1.5~5.5V.AC(ACT)系列的逻辑 功能,引脚排列顺序等都与同型号的 HC(HCT)系列完全相同. 2.CMOS 逻辑门电路的主要参数 CMOS 门电路主要参数的定义同 TTL 电路,下面主要说明 CMOS 电路主要参数的特点. (1)输出高电平 VOH 与输出低电平 VOL.CMOS 门电路 VOH 的理论值为电源电压 VDD,VOH(min) =0.9VDD;VOL 的理论值为 0V,VOL(max)=0.01VDD.所以 CMOS 门电路的逻辑摆幅(即高低电 平之差)较大,接近电源电压 VDD 值. (2)阈值电压 Vth.从 CMOS 非门电压传输特性曲线中看出,输出高低电平的过渡区很陡,阈值电压 Vt h 约为 VDD/2. (3)抗干扰容限.CMOS 非门的关门电平 VOFF 为 0.45VDD,开门电平 VON 为 0.55VDD.因此,其 高,低电平噪声容限均达 0.45VDD.其他 CMOS 门电路的噪声容限一般也大于 0.3VDD,电源电压 VD D 越大,其抗干扰能力越强. (4)传输延迟与功耗.CMOS 电路的功耗很小,一般小于 1 mW/门,但传输延迟较大,一般为几十 ns /门,且与电源电压有关,电源电压越高,CMOS 电路的传输延迟越小,功耗越大.前面提到 74HC 高速 CMOS 系列的工作速度己与 TTL 系列相当. (5)扇出系数.因 CMOS 电路有极高的输入阻抗,故其扇出系数很大,一般额定扇出系数可达 50.但 必须指出的是,扇出系数是指驱动 CMOS 电路的个数,若就灌电流负载能力和拉电流负载能力而言,CM OS 电路远远低于 TTL 电路. CMOS 逻辑门电路是在 TTL 电路问世之后 ,所开发出的第二种广泛应用的数字集成器件,从发展趋势来 看,由于制造工艺的改进,CMOS 电路的性能有可能超越 TTL 而成为占主导地位的逻辑器件 .CMOS 电 路的工作速度可与 TTL 相比较,而它的功耗和抗干扰能力则远优于 TTL.此外,几乎所有的超大规模存储 器件 , 以及 PLD 器件都采用 CMOS 艺制造, 且费用较低. 早期生产的 CMOS 门电路为 4000 系列 , 随后发展为 4000B 系列.当前与 TTL 兼容的 CMO 器件如 74HCT 系列等可与 TTL 器件交换使用.MOS 管主要参数:1.开启电压 VT开启电压(又称阈值电压):使得源极 S 和漏极 D 之间开始形成导电沟道所需的栅极电压;标准的 N 沟道 MOS 管,VT 约为 3~6V;通过工艺上的改进,可以使 MOS 管的 VT 值降到 2~3V. 2. 直流输入电阻 RGS 即在栅源极之间加的电压与栅极电流之比 这一特性有时以流过栅极的栅流表示 MOS 管的 RGS 可以很容易地超过 1010. 3. 漏源击穿电压 BVDS 在 VGS=0(增强型)的条件下 ,在增加漏源电压过程中使 ID 开始剧增时的 VDS 称为漏源击穿电压 B VDS ID 剧增的原因有下列两个方面: (1)漏极附近耗尽层的雪崩击穿 (2)漏源极间的穿通击穿 有些 MOS 管中,其沟道长度较短,不断增加 VDS 会使漏区的耗尽层一直扩展到源区,使沟道长度为零, 即产生漏源间的穿通,穿通后源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的 I D 4. 栅源击穿电压 BVGS 在增加栅源电压过程中,使栅极电流 IG 由零开始剧增时的 VGS,称为栅源击穿电压 BVGS. 5. 低频跨导 gm 在 VDS 为某一固定数值的条件下 , 漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导 gm 反映了栅源电压对漏极电流的控制能力 是表征 MOS 管放大能力的一个重要参数 一般在十分之几至几 mA/V 的范围内 6. 导通电阻 RON 导通电阻 RON 说明了 VDS 对 ID 的影响 ,是漏极特性某一点切线的斜率的倒数 在饱和区,ID 几乎不随 VDS 改变,RON 的数值很大 ,一般在几十千欧到几百千欧之间由于在数字电路中 , MOS 管导通时经常工作在 VDS=0 的状态下, 所以这时的导通电阻 RON 可用原点 的 RON 来近似 对一般的 MOS 管而言,RON 的数值在几百欧以内 7. 极间电容 三个电极之间都存在着极间电容:栅源电容 CGS ,栅漏电容 CGD 和漏源电容 CDS CGS 和 CGD 约为 1~3pF CDS 约在 0.1~1pF 之间 8. 低频噪声系数 NF 噪声是由管子内部载流子运动的不规则性所引起的 由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化 噪声性能的大小通常用噪声系数 NF 来表示,它的单位为分贝(dB) 这个数值越小,代表管子所产生的噪声越小 低频噪声系数是在低频范围内测出的噪声系数 场效应管的噪声系数约为几个分贝,它比双极性三极管的要小TTL 电路发展简史TTL 电路是晶体管-晶体管逻辑电路的英文缩写(Transister-Transister-Logic),是数字集成电路的一 大门类.它采用双极型工艺制造,具有高速度低功耗和品种多等特点.从六十年代开发成功第一代产品以 来现有以下几代产品.第一代 TTL 包括 SN54/74 系列,(其中 54 系列工作温度为-55℃~+125℃,7 4 系列工作温度为 0℃~+75℃),低功耗系列简称 lttl,高速系列简称 HTTL.第二代 TTL 包括肖特基箝 位系列(STTL)和低功耗肖特基系列(LSTTL)第三代为采用等平面工艺制造的先进的 STTL(ASTTL)和 先进的低功耗 STTL(ALSTTL)由于 LSTTL 和 ALSTTL 的电路延时功耗积较小,STTL 和 ASTTL 速度很 快,因此获得了广泛的应用.TTL 数字集成电路分类: 数字集成电路分类:电路类型 TTL 数字集成电路约有 400 多个品种,大致可以分为以下几类:门电路,译码器/驱动器,触发器,计数器, 移位寄存器,单稳,双稳电路和多谐振荡器,加法器乘法器,奇偶校验器,码制转换器,线驱动器/线接 收器, 多路开关,存储器特性曲线电压传输特性效应管技术文档1.什么叫场效应管? Fffect Transistor 的缩写,即为场效应晶体管.一般的晶体管是由两种极性的载流子,即多数载流子和反极性的少 数载流子参与导电,因此称为双极型晶体管,而 FET 仅是由多数载流子参与导电,它与双极型相反,也称为单极型 晶体管.FET 应用范围很广,但不能说现在普及的双极型晶体管都可以用 FET 替代.然而,由于 FET 的特性与 双极型晶体管的特性完全不同,能构成技术性能非常好的电路.2. 场效应管的特征:(a) JFET 的概念图(b) JFET 的符号图 1 JFET 的概念图,符号图 1(b)门极的箭头指向为 p 指向 n 方向,分别表示内向为 n 沟道 JFET,外向为 p 沟道 JFET. 图 1(a)表示 n 沟道 JFET 的特性例.以此图为基础看看 JFET 的电气特性的特点.首先,门极-源极间电压以 0V 时考虑(VGS =0).在此状态下漏极-源极间电压 VDS 从 0V 增加,漏电流 I D 几乎与 VDS 成比例增加,将此区域称为非饱和区.VDS 达到某值以上漏电流 ID 的变化变小,几乎达到一定 值.此时的 ID 称为饱和漏电流(有时也称漏电流用 IDSS 表示.与此 IDSS 对应的 VDS 称为夹断电压 VP , 此区域称为饱和区. 其次在漏极-源极间加一定的电压 VDS (例如 0.8V),VGS 值从 0 开始向负方向增加,ID 的值从 IDSS 开始 慢慢地减少,对某 VGS 值 ID =0.将此时的 VGS 称为门极-源极间遮断电压或者截止电压,用 VGS (off)示. n 沟道 JFET 的情况则 VGS (off) 值带有负的符号,测量实际的 JFET 对应 ID =0 的 VGS 因为很困难,在放大器 使用的小信号 JFET 时,将达到 ID =0.1-10A 的 VGS 定义为 VGS (off) 的情况多些. 关于 JFET 为什么表示 这样的特性,用图作以下简单的说明.缘型 FET(简化为 MOS FET)图 3. FET 的结构各种结构的 FET 均有门极,源极,漏极 3 个端子,将这些与双极性晶体管的各端子对应如表 1 所示.图 4 JFET 的特性例(n 沟道)输入阻抗.输出阻抗, 输入阻抗.输出阻抗,阻抗匹配定义一,输入阻抗输入阻抗是指一个电路输入端的等效阻抗.在输入端上加上一个电压源 U,测量输入端的电流 I, 则输入阻抗 Rin 就是 U/I.你可以把输入端想象成一个电阻的两端,这个电阻的 阻值,就是输入阻抗.输入阻抗跟一个普通的电抗元件没什么两样, 它反映了对电流阻碍作用的大 小.对于电压驱动的电路,输入阻抗越大,则对电压源的负载就越轻,因而就越 容易驱动,也不会对信号源有影响;而对于电流驱动型的电路,输入阻抗越小, 则对电流源的负载就越轻. 因此, 我们可以这样认为: 如果是用电压源来驱动的, 则输入阻抗越大越好;如果是用电流源来驱动的,则阻抗越小越好(注:只适合 于低频电路,在高频电路中,还要考虑阻抗匹配问题.另外如果要获取最大输出 功率时,也要考虑 阻抗匹配问题二,输出阻抗无论信号源或放大器还有电源,都有输出阻抗的问题.输出阻抗就是一个信 号源的内阻.本来,对于一个理想的电压源(包括电源),内阻应该为 0,或理 想电流源的阻抗应当为无穷大.输出阻抗在电路设计最特别需要注意 但现实中的电压源,则不能做到这一点.我们常用一个理想电压源串联一个电阻 r 的方式来等效一个实际的电压源.这个跟理想电压源串联的电阻 r,就是(信 号源/放大器输出/电源)的内阻了.当这个电压源给负载供电时,就会有电流 I 从这个负载上流过,并在这个电阻上产生 I×r 的电压降.这将导致电源输出电压 的下降,从而限制了最大输出功率(关于为什么会限制最大输出功率,请看后面 的"阻抗匹配"一问).同样的,一个理想的电流源,输出阻抗应该是无穷大, 但实际的电路是不可能的三,阻抗匹配阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式.阻抗匹配分为低频和高频两种情况讨论.我们先从直流电压源驱动一个负载入手.由于实际的电压源,总是有内阻的 (请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻 r 串联的模型.假设负载电阻为 R,电源电动势为 U,内阻为 r, 那么我们可以计算出流过电阻 R 的电流为:I=U/(R+r),可以看出,负载电阻R 越小,则输出电流越大.负载 R 上的电压为:Uo=IR=U/[1+(r/R)],可以看 出,负载电阻 R 越大,则输出电压 Uo 越高.再来计算一下电阻 R 消耗的功率为:P=I2×R=[U/(R+r)]2×R=U2×R/(R2+2×R×r+r2) =U2×R/[(R-r)2+4×R×r]=U2/{[(R-r)2/R]+4×r} 对于一个给定的信号源, 其内阻 r 是固定的, 而负载电阻 R 则是由我们来选择的. 2 2 注意式中[(R-r) /R],当 R=r 时,[(R-r) /R]可取得最小值 0,这时负载电阻 R 上可 获得最大输出功率 Pmax=U2/(4×r).即,当负载电阻跟信号源内阻相等时,负载可获得最大输出功率,这就是我们常说的阻抗匹配之一.对于纯电 . 阻电路,此结论同样适用于低频电路及高频电路.当交流电路中含有容 性或感性阻抗时,结论有所改变,就是需要信号源与负载阻抗的的实部 相等,虚部互为相反数,这叫做共扼匹配.在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相 对于传输线来说很长,传输线可以看成是"短线",反射可以不考虑(可以这么 理解:因为线短,即使反射回来,跟原信号还是一样的).从以上分析我们可以 得出结论:如果我们需要输出电流大,则选择小的负载 R;如果我们需要输出电 压大,则选择大的负载 R;如果我们需要输出功率最大,则选择跟信号源内阻匹 配的电阻 R.有时阻抗不匹配还有另外一层意思,例如一些仪器输出端是在特定 的负载条件下设计的,如果负载条件改变了,则可能达不到原来的性能,这时我 们也会叫做阻抗失配.在高频电路中, 我们还必须考虑反射的问题. 当信号的频率很高时, 则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号 叠加在原信号上将会改变原信号的形状. 如果传输线的特征阻抗跟负载 阻抗不相等(即不匹配)时,在负载端就会产生反射.为什么阻抗不匹 配时会产生反射以及特征阻抗的求解方法, 牵涉到二阶偏微分方程的求 解,在这里我们不细说了,有兴趣的可参看电磁场与微波方面书籍中的传输线理论.传输线的特征阻抗(也叫做特性阻抗)是由传输线的结构 以及材料决定的, 而与传输线的长度, 以及信号的幅度, 频率等均无关.例如,常用的闭路电视同轴电缆特性阻抗为 75 ,而一些射频设备上则常用 特征阻抗为 50 的同轴电缆. 另外还有一种常见的传输线是特性阻抗为 300 的 扁平平行线,这在农村使用的电视天线架上比较常见,用来做八木天线的馈线. 因为电视机的射频输入端输入阻抗为 75 ,所以 300 的馈线将与其不能匹配. 实际中是如何解决这个问题的呢?不知道大家有没有留意到,电视机的附件中, 有一个 300 到 75 的阻抗转换器(一个塑料封装的,一端有一个圆形的插头的 那个东东,大概有两个大拇指那么大).它里面其实就是一个传输线变压器,将 300 的阻抗,变换成 75 的,这样就可以匹配起来了.这里需要强调一点的是,特性阻抗跟我们通常理解的电阻不是一个概念,它与传输线的 长度无关,也不能通过使用欧姆表来测量.为了不产生反射,负载阻抗跟传输线的特征阻抗应该相等,这就是传输线的阻抗匹配,如果阻抗不匹配会有什 么不良后果呢?如果不匹配,则会形成反射,能量传递不过去,降低效率;会在 传输线上形成驻波(简单的理解,就是有些地方信号强,有些地方信号弱),导 致传输线的有效功率容量降低;功率发射不出去,甚至会损坏发射设备.如果是 电路板上的高速信号线与负载阻抗不匹配时,会产生震荡,辐射干扰等.当阻抗不匹配时,有哪些办法让它匹配呢?第一,可以考虑使用变压器来做 阻抗转换,就像上面所说的电视机中的那个例子那样.第二,可以考虑使用串联 /并联电容或电感的办法,这在调试射频电路时常使用.第三,可以考虑使用串 联/并联电阻的办法.一些驱动器的阻抗比较低,可以串联一个合适的电阻来跟 传输线匹配,例如高速信号线,有时会串联一个几十欧的电阻.而一些接收器的 输入阻抗则比较高,可以使用并联电阻的方法,来跟传输线匹配,例如,485 总 线接收器,常在数据线终端并联 120 欧的匹配电阻. 为了帮助大家理解阻抗不匹配时的反射问题,我来举两个例子:假设你在练 习拳击——打沙包.如果是一个重量合适的,硬度合适的沙包,你打上去会感觉 很舒服.但是,如果哪一天我把沙包做了手脚,例如,里面换成了铁沙,你还是 用以前的力打上去,你的手可能就会受不了了——这就是负载过重的情况,会产 生很大的反弹力.相反,如果我把里面换成了很轻很轻的东西,你一出拳,则可 能会扑空,手也可能会受不了——这就是负载过轻的情况.另一个例子,不知道 大家有没有过这样的经历:就是看不清楼梯时上/下楼梯,当你以为还有楼梯时, 就会出现"负载不匹配"这样的感觉了.当然,也许这样的例子不太恰当,但我 们可以拿它来理解负载不匹配时的反射情况大电容并小电容的作用大电容并小电容的作用因为大电容由于容量大,所以体积一般也比较大,且通常使用多层卷绕的方式制作(动手拆过铝电解电容 应该会很有体会,没拆过的也可以拿几种不同的电容拆来看看,不过要注意安全,别弄伤手),这就导致 等效串联电感,英文简称 ESL).大家知道,电感对高频信 了大电容的分布电感比较大(也叫等效串联电感 等效串联电感号的阻抗是很大的,所以,大电容的高频性能不好.而一些小容量电容则刚刚相 反,由于容量小,因此体积可以做得很小(缩短了引线,就减小了 ESL,因为一 段导线也可以看成是一个电感的),而且常使用平板电容的结构,这样小容量电 容就有很小的 ESL,这样它就具有了很好的高频性能,但由于容量小的缘故,对 低频信号的阻抗大.所以,如果我们为了让低频,高频信号都可以很好的通过, 就采用一个大电容再并上一个小电容的方式.常使用的小电容为 0.1uF 的瓷片电 容,当频率更高时,还可并联更小的电容,例如几 pF,几百 pF 的.而在数字电 路中,一般要给每个芯片的电源引脚上并联一个 0.1uF 的电容到地(这电容叫做 去耦电容,当然也可以理解为电源滤波电容.它越靠近芯片的位置越好),因为 在这些地方的信号主要是高频信号,使用较小的电容滤波就可以了. (By computer00为何模拟地(AG)和数字地 和数字地(DG)要分开布线 为何模拟地 和数字地 要分开布线在电路设计中,常常把模拟地与数字地独立布线.但模拟地跟数字地,最终都要接到一块的,那干吗还要 分模拟地和数字地呢? 这是因为虽然是相通的,但是距离长了,就不一样了. 同一条导线,不同的点的电压可能是不一样的,特别是电流较大时. 因为导线存在着电阻,电流流过时就会产生压降. 另外,导线还有分布电感,在交流信号下,分布电感的影响就会表现出来.所以我们要分成数字地和模拟 地,因为数字信号的高频噪声很大,如果模拟地和数字地混合的话,就会把噪声传到模拟部分,造成干扰. 如果分开接地的话,高频噪声可以在电源处通过滤波来隔离掉.但如果两个地混合,就不好滤波了.这样 隔离在保证电路设计的稳定和抗干扰.三极管特性及其放大电路三极管是电流放大器件,有三个极,分别叫做集电极 C,基极B,发射极 E.分成 NPN 和 PNP 两 种.我们仅以 NPN 三极管的共发射极放大电路为例来说明一下三极管放大电路的基 本原理.下面的分析仅对于 NPN 型硅三极管.如上图所示,我们把从基极 B 流至发射极 E 的 电流叫做基极电流 Ib;把从集电极 C 流至发射极 E 的电流叫做集电极电流 Ic.这两 个电流的方向都是流出发射极的, 所以发射极 E 上就用了一个箭头来表示电流的方向. 三极管的放大作用就是:集电极电流受基极电流的控制(假设电源能够提供给集电极 足够大的电流的话) ,并且基极电流很小的变化,会引起集电极电流很大的变化,且 变化满足一定的比例关系:集电极电流的变化量是基极电流变化量的β倍,即电流变 化被放大了β倍,所以我们把β叫做三极管的放大倍数(β一般远大于 1,例如几十, 几百) .如果我们将一个变化的小信号加到基极跟发射极之间,这就会引起基极电流 I b 的变化,Ib 的变化被放大后,导致了 Ic 很大的变化.如果集电极电流 Ic 是流过一 个电阻 R 的,那么根据电压计算公式 U=R*I 可以算得,这电阻上电压就会发生很大 的变化.我们将这个电阻上的电压取出来,就得到了放大后的电压信号了. 三极管在实际的放大电路中使用时,还需要加合适的偏置电路.这有几个原因. 首先是由于三极管 BE 结的非线性(相当于一个二极管) ,基极电流必须在输入电压大 到一定程度后才能产生(对于硅管,常取 0.7V) .当基极与发射极之间的电压小于 0. 7V 时,基极电流就可以认为是 0.但实际中要放大的信号往往远比 0.7V 要小,如果 不加偏置的话,这么小的信号就不足以引起基极电流的改变(因为小于 0.7V 时,基 极电流都是 0) 如果我们事先在三极管的基极上加上一个合适的电流 . (叫做偏置电流, 上图中那个电阻 Rb 就是用来提供这个电流的,所以它被叫做基极偏置电阻) ,那么当 一个小信号跟这个偏置电流叠加在一起时,小信号就会导致基极电流的变化,而基极 电流的变化,就会被放大并在集电极上输出.另一个原因就是输出信号范围的要求, 如果没有加偏置,那么只有对那些增加的信号放大,而对减小的信号无效(因为没有 偏置时集电极电流为 0,不能再减小了) .而加上偏置,事先让集电极有一定的电流, 当输入的基极电流变小时,集电极电流就可以减小;当输入的基极电流增大时,集电 极电流就增大.这样减小的信号和增大的信号都可以被放大了. 下面说说三极管的饱和情况.像上面那样的图,因为受到电阻 Rc 的限制(Rc 是 固定值,那么最大电流为 U/Rc,其中 U 为电源电压) ,集电极电流是不能无限增加下 当基极电流的增大, 不能使集电极电流继续增大时, 三极管就进入了饱和状态. 去的.。

CMOS集成逻辑门电路特点及使用方法

1.低功耗:CMOS电路在工作时只有短暂的电流流动,且仅在切换过程中会有瞬间的短路电流,因此功耗较低。

2.高集成度:CMOS电路能够实现大规模的集成,由于其结构简单,可以在一个芯片上实现多个逻辑门功能,从而提高整体集成度。

3.抗干扰能力强:CMOS电路采用互补器件,两种类型的晶体管结合在一起,当一种开启时,另一种关闭,因此对干扰信号的抵抗能力强。

4.工作稳定:CMOS电路由于采用了互补结构,不容易产生热失调现象,故工作稳定性较高。

5.可编程性强:CMOS电路通常具有很好的可编程性,可以通过调整电流大小、精密度等参数来实现不同逻辑功能的设计。

1.电路设计:根据需要设计逻辑电路,包括确定所需的逻辑功能、输入输出端口等。

2.电路仿真:使用电路仿真软件对设计的逻辑电路进行仿真,验证其正确性并进行必要的调整。

3.电路布局:根据设计的逻辑电路,进行电路布局设计,确定晶体管和连线的布局,保证电路的正常工作。

4.制作掩膜:根据布局设计制作相应的掩膜,并进行曝光和光刻等加工工艺。

5.生产加工:通过工艺流程,将设计好的电路图案制作到芯片上,完成电路的制造。

6.测试验证:对制作好的CMOS电路进行测试验证,检查其性能和功能是否符合设计要求。

总的来说,CMOS集成逻辑门电路具有低功耗、高集成度、抗干扰能力强、工作稳定等优点,广泛应用于数字电路、微处理器、存储器、通信电路、模拟电路等领域。

在使用CMOS集成电路时,需要进行电路设计、仿真、布局、制作掩膜、生产加工和测试验证等步骤,以确保电路的正常工作和性能达到设计要求。

CMOS技术的不断发展将为电子行业带来更多的创新和发展机遇。

CMOS 集成逻辑门电路特点及使用方法1.CMOS集成电路特点CMOS集成电路的特点是功耗极低、输出幅度大噪声容限大、扇出能力强。

MOS逻辑门电路主要分为NMOS、PMOS、CMOS三大类,PMOS是MOS逻辑门的早期产品,它不仅工作速度慢且使用负电源,不便与TTL电路连接,CMOS是在NMOS的基础上发展起来,它的各种性能较NMOS都好。

2.集成CMOS电路的特性参数CMOS门电路主要参数的定义同TTL电路,下面主要说明CMOS电路主要参数的特点。

(1)输出高电平U OH 与输出低电平U OLCMOS门电路U OH的理论值为电源电压U DD,U OH(min)=0.9U DD;U OL的理论值为0V,U OL(max)=0.01U DD。

所以CMOS门电路的逻辑摆幅(即高低电平之差)较大,接近电源电压U DD值。

(2)阈值电压U TH从CMOS 非门电压传输特性曲线中看出,输出高低电平的过渡区很陡,阈值电压U TH 约为U DD/2。

(3)抗干扰容限CMOS非门的关门电平U OFF为0.45U DD,开门电平U ON为0.55U DD。

因此,其高、低电平噪声容限均达0.45U DD。

其他CMOS门电路的噪声容限一般也大于0.3U DD,电源电压U DD 越大,其抗干扰能力越强。

(4)传输延迟与功耗CMOS电路的功耗很小,一般小于1 mW/门,但传输延迟较大,一般为几十ns/门,且与电源电压有关,电源电压越高,CMOS电路的传输延迟越小,功耗越大。

前面提到74HC 高速CMOS系列的工作速度已与TTL系列相当。

(5)扇出系数因CMOS电路有极高的输入阻抗,故其扇出系数很大,一般额定的扇出系数可达50。

但必须指出的是,扇出系数是指驱动CMOS电路的个数,若就灌电流负载能力和拉电流负载能力而言,CMOS电路远远低于TTL电路。

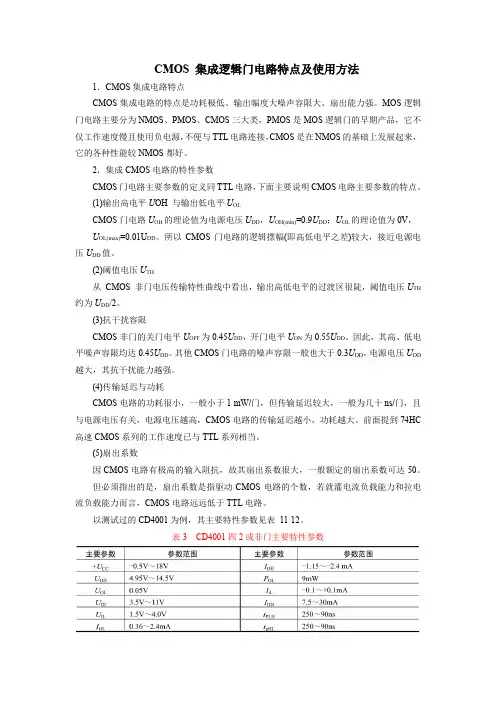

以测试过的CD4001为例,其主要特性参数见表11-12。

表3 CD4001四2或非门主要特性参数注:以上参数范围为电源电压选择5V、10V及15V的前提下所得。

cmos门电路逻辑表达式CMOS门电路逻辑表达式是一种基于场效应管(MOS)工作原理构建的电路,其本质上是一种由多个MOS晶体管和互补型晶体管(即n型MOS和p型MOS)组成的数字逻辑电路。

在CMOS门电路中,晶体管开关状态的变化导致电信号的传输、加工和控制,从而实现了不同逻辑功能的实现。

下面将分步骤阐述CMOS门电路逻辑表达式的具体内容:1. CMOS门电路中的逻辑运算在CMOS门电路中,常见的逻辑运算有与(AND)、或(OR)、非(NOT)、异或(XOR)等,这些逻辑运算的实现遵循电路的门电路设计原理,其中门电路设计的基本逻辑元件称为逻辑门。

逻辑门的输出端可以是高电平(1)或低电平(0),对应于逻辑的真(True)和假(False)两种状态。

2. CMOS门电路的逻辑表达式在CMOS门电路中,每个逻辑运算都有其对应的逻辑表达式,例如:- 与门(AND)的逻辑表达式: Y = A and B- 或门(OR)的逻辑表达式:Y = A or B- 非门(NOT)的逻辑表达式:Y = not A- 异或门(XOR)的逻辑表达式:Y = A xor B其中,A、B均为输入端口。

3. CMOS门电路的实现方法实际上,CMOS门电路的实现方法主要涉及到两个方面:传输电路和逻辑门电路。

传输电路主要负责零售运算的传输和控制,逻辑门电路则是逻辑运算的核心元件,通过晶体管的开关状态变化实现逻辑运算功能。

在CMOS门电路中,门电路组成的方式也各不相同,例如,与非门(NAND)可以通过串联一个反相器(NOT)和一个或门(OR)来实现,或者通过并联一个非门(NOT)和一个与门(AND)来实现。

这些门电路的组合方式取决于具体的设计需求和实现方式。

总之,CMOS门电路逻辑表达式是一种非常重要的数字电路设计方案,其良好的稳定性、高效率、低功耗等特点,在现代电子技术应用中得到了广泛的应用。

同时,对于电子工程师来说,掌握CMOS门电路逻辑表达式的设计和应用原理,将有助于实现高质量、高性能的数字电路设计和实现。

cmos与门逻辑电路CMOS与门逻辑电路CMOS(Complementary Metal-Oxide-Semiconductor)与门逻辑电路是一种常见的数字电路,它由一对互补的MOSFET(金属-氧化物-半导体场效应晶体管)组成。

CMOS与门电路的基本功能是将两个输入信号进行逻辑与运算,输出结果与输入信号相应的逻辑关系相符。

CMOS与门电路的工作原理是基于MOSFET的特性。

MOSFET是一种由金属、氧化物和半导体材料构成的晶体管。

它包括一个源极、一个漏极和一个栅极。

当栅极施加电压时,栅极与源极之间的电场会改变沟道的导电性,从而控制漏极和源极之间的电流流动。

CMOS与门电路中的两个MOSFET互补工作,一个是P型,一个是N型。

当输入信号为低电平时,P-MOSFET导通,N-MOSFET 截断;当输入信号为高电平时,P-MOSFET截断,N-MOSFET导通。

通过控制输入信号的高低电平,CMOS与门电路可以实现逻辑与运算。

CMOS与门电路的优点之一是能够在低功耗下工作。

由于MOSFET 只有在切换时才会消耗能量,而且CMOS电路中的两个互补MOSFET只会同时导通或截断,因此在静态情况下几乎没有功耗。

另外,CMOS与门电路的结构简单,制造工艺成熟,可靠性高,容易集成在大规模集成电路(VLSI)中。

CMOS与门电路的应用非常广泛。

它可以用于各种数字系统中,如计算机、通信设备、工业控制系统等。

在数字集成电路中,CMOS 与门电路可以作为其他逻辑门电路的基本构件,例如与非门、与或门等。

此外,CMOS与门电路也可以用于信号处理、时序电路和存储器等领域。

尽管CMOS与门电路有很多优点,但也存在一些限制。

首先,由于MOSFET的特性,CMOS与门电路的输入电压范围受限,不能超过供电电压。

其次,CMOS与门电路在切换时可能会产生一定的噪声干扰,对于某些应用场景可能需要进行抗干扰设计。

此外,CMOS 与门电路的制造成本相对较高,需要复杂的工艺流程和精密的设备。

cmos逻辑门电路一、引言CMOS逻辑门电路是数字电路中常用的一种电路,它采用了CMOS技术,具有低功耗、高速度和稳定性等优点。

本文将从CMOS逻辑门的基本原理、结构和特点入手,详细介绍CMOS逻辑门的工作原理、应用及其发展趋势。

二、CMOS逻辑门的基本原理1. CMOS技术简介CMOS技术是指利用p型MOSFET和n型MOSFET组成的互补型MOSFET来构成数字电路。

p型MOSFET和n型MOSFET分别采用p型半导体和n型半导体作为衬底,通过控制栅极上的电压来控制输出端口上的电流。

由于它们互补使用,因此称为互补型MOSFET。

2. CMOS逻辑门结构CMOS逻辑门由p型MOSFET和n型MOSFET组成,它们分别被串联在输出端口上。

当输入信号为高电平时,p型MOSFET导通,n型MOSFET截止;当输入信号为低电平时,p型MOSFET截止,n型MOSFET导通。

3. CMOS逻辑门特点(1)低功耗:CMOS逻辑门采用互补型MOSFET,因此在静态状态下几乎不消耗功率。

(2)高速度:由于p型MOSFET和n型MOSFET的导通与截止是瞬间完成的,因此CMOS逻辑门具有较高的响应速度。

(3)稳定性好:CMOS逻辑门具有很好的抗干扰能力,能够有效地抵御噪声和干扰。

三、CMOS逻辑门工作原理1. CMOS反相器CMOS反相器由一个p型MOSFET和一个n型MOSFET组成。

当输入信号为高电平时,p型MOSFET导通,n型MOSFET截止;当输入信号为低电平时,p型MOSFET截止,n型MOSFET导通。

因此输出信号与输入信号相反。

2. CMOS与非门CMOS与非门由两个串联的CMOS反相器组成。

当两个输入端口均为高电平时,两个反相器输出均为低电平,而输出端口上出现高电平;只要有一个输入端口为低电平,则整个CMOS与非门输出都为高电平。

3. CMOS或非门CMOS或非门由两个并联的CMOS反相器组成。

CMOS逻辑门电路1. 什么是CMOS逻辑门电路?CMOS(Complementary Metal-Oxide-Semiconductor)逻辑门电路是一种常用的数字电路设计技术。

它由两种类型的晶体管组成:N型金属氧化物半导体场效应晶体管(NMOS)和P型金属氧化物半导体场效应晶体管(PMOS)。

CMOS逻辑门电路采用了这两种晶体管的互补特性,能够实现低功耗、高噪声容限和高抗干扰性能。

2. CMOS逻辑门电路的基本原理CMOS逻辑门电路是通过控制晶体管的导通与截止状态来实现不同逻辑功能的。

当输入信号为高电平时,PMOS导通,NMOS截止;当输入信号为低电平时,PMOS截止,NMOS导通。

通过合理地设计和连接这些晶体管,可以实现与门、或门、非门等基本逻辑功能。

3. CMOS逻辑门电路的基本结构3.1 NMOS与PMOS晶体管NMOS和PMOS晶体管是构成CMOS逻辑门电路的基本元件。

NMOS由一个N型沟道和控制栅极组成,PMOS由一个P型沟道和控制栅极组成。

NMOS的导通与截止由栅极电压控制,当栅极电压高于阈值电压时,NMOS导通;PMOS的导通与截止也由栅极电压控制,但是当栅极电压低于阈值电压时,PMOS导通。

3.2 CMOS逻辑门的实现CMOS逻辑门由一组串联或并联的NMOS和PMOS晶体管组成。

以下是几种常见的CMOS逻辑门实现方式:•与门(AND Gate):将多个输入信号分别通过NMOS与PMOS晶体管连接,在输出端通过串联的NMOS和PMOS晶体管实现与运算。

•或门(OR Gate):将多个输入信号分别通过NMOS与PMOS晶体管连接,在输出端通过并联的NMOS和PMOS晶体管实现或运算。

•非门(NOT Gate):将输入信号通过一个NMOS晶体管接入输出端,并在输出端再接入一个PMOS晶体管,实现非运算。

4. CMOS逻辑门电路的特点4.1 高抗干扰性CMOS逻辑门电路采用了互补型结构,输入信号只需驱动其中一种晶体管,另一种晶体管处于截止状态,因此输入信号的干扰对输出信号的影响较小。

CMOS 逻辑门电路CMOS 是互补对称MOS 电路的简称(Complementary Metal-Oxide-Semiconductor ),其电路结构都采用增强型PMOS 管和增强型NMOS 管按互补对称形式连接而成,由于CMOS 集成电路具有功耗低、工作电流电压范围宽、抗干扰能力强、输入阻抗高、扇出系数大、集成度高,成本低等一系列优点,其应用领域十分广泛,尤其在大规模集成电路中更显示出它的优越性,是目前得到广泛应用的器件。

一、CMOS 反相器CMOS 反相器是CMOS 集成电路最基本的逻辑元件之一,其电路如图11-36所示,它是由一个增强型NMOS 管T N 和一个PMOS 管T P 按互补对称形式连接而成。

两管的栅极相连作为反相器的输入端,漏极相连作为输出端,T P 管的衬底和源极相连接电源U DD ,T N 管的衬底与源极相连后接地,一般地U DD >(U TN +|U TP |),(U TN和|U TP |是T N 和T P 的开启电压)。

当输入电压u i =“0”(低电平)时,NMOS 管T N 截止,而PMOS 管T P 导通,这时T N 管的阻抗比T P 管的阻抗高的多,(两阻抗比值可高达106以上),电源电压主要降在T N 上,输出电压为“1”(约为U DD )。

当输入电压u i =“1”(高电平)时,T N 导通,T P 截止,电源电压主要降在T P 上,输出u o =“0”,可见此电路实现了逻辑“非”功能。

通过CMOS 反相器电路原理分析,可发现CMOS 门电路相比NMOS 、PMOS 门电路具有如下优点:①无论输入是高电平还是低电平,T N 和T P 两管中总是一个管子截止,另一个导通,流过电源的电流仅是截止管的沟道泄漏电流,因此,静态功耗很小。

②两管总是一个管子充分导通,这使得输出端的等效电容C L 能通过低阻抗充放电,改善了输出波形,同时提高了工作速度。

③由于输出低电平约为0V ,输出高电平为U DD ,因此,输出的逻辑幅度大。