MOS管及简单CMOS逻辑门电路原理图

- 格式:doc

- 大小:111.00 KB

- 文档页数:10

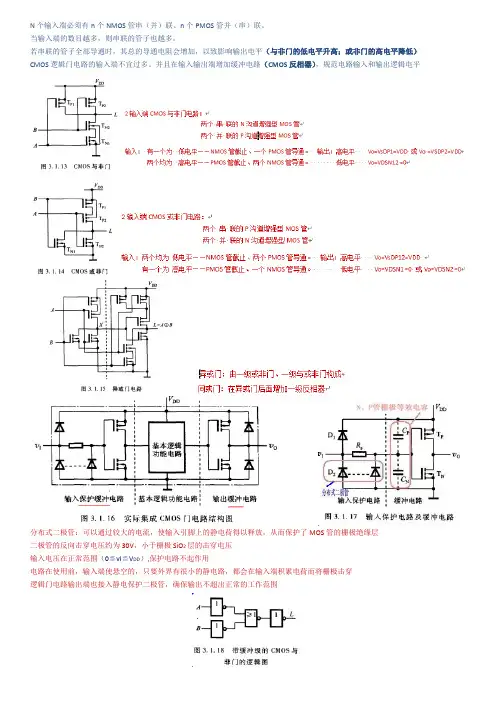

N个输入端必须有n个NMOS管串(并)联、n个PMOS管并(串)联。

当输入端的数目越多,则串联的管子也越多。

若串联的管子全部导通时,其总的导通电阻会增加,以致影响输出电平(与非门的低电平升高;或非门的高电平降低)CMOS逻辑门电路的输入端不宜过多。

并且在输入输出端增加缓冲电路(CMOS反相器),规范电路输入和输出逻辑电平

分布式二极管:可以通过较大的电流,使输入引脚上的静电荷得以释放,从而保护了MOS管的栅极绝缘层

二极管的反向击穿电压约为30V,小于栅极SiO2层的击穿电压

输入电压在正常范围(0≦vI≦V DD),保护电路不起作用

电路在使用前,输入端使悬空的,只要外界有很小的静电路,都会在输入端积累电荷而将栅极击穿

逻辑门电路输出端也接入静电保护二极管,确保输出不超出正常的工作范围。

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用C MOS工艺制成的。

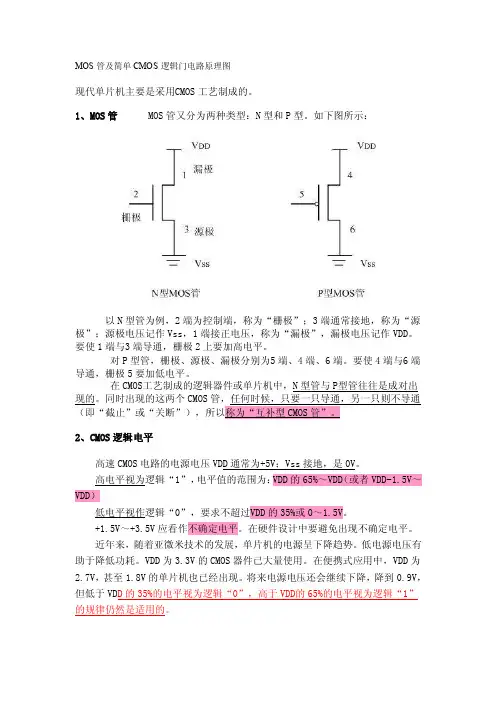

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMO S2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过V DD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMO S器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMO S管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

CMOS门电路以MOS(Metal-Oxide Semiconductor)管作为开关元件的门电路称为MOS门电路。

由于MOS型集成门电路具有制造工艺简单、集成度高、功耗小以及抗干扰能力强等优点,因此它在数字集成电路产品中占据相当大的比例。

与TTL 门电路相比,MOS门电路的速度较低。

MOS门电路有三种类型:使用P沟道管的PMOS电路、使用N沟道管的NMOS电路和同时使用PMOS和NMOS 管的CMOS电路。

其中CMOS性能更优,因此CMOS门电路是应用较为普遍的逻辑电路之一。

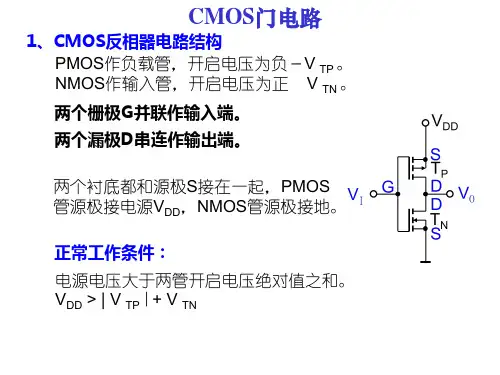

1. CMOS非门图3-16所示是一个N沟道增强型MOS管TN和一个P沟道增强型MOS管TP组成的CMOS非门。

图3-16 CMOS非门电路图3-17 CMOS与非门电路两管的栅极相连作为输入端,两管的漏极相连作为输出端。

TN的源极接地,TP的源极接电源。

为了保证电路正常工作,VDD需要大于TN管开启电压VTN和TP管开启电压VTP的绝对值的和,即UDD> UTN+ |UTP|。

当Ui=0V 时,TN截止,TP导通,Uo≈UDD为高电平;当Ui=UDD时,TN导通,TP截止,Uo≈0V为低电平。

因此实现了非逻辑功能。

CMOS非门除了有较好的动态特性外,由于CMOS非门电路工作时总有一个管子导通,所以当带电容负载时,给电容充电和放电都比较快。

CMOS非门的平均传输延迟时间约为10ns。

另外由于它处在开关状态下总有一个管子处于截止状态,因而电流极小,电路的静态功耗很低,一般为微瓦(mW)数量级。

2. CMOS与非门图3-17所示为一个两输入端的CMOS与非门电路,它由两个串联的NMOS管和两个并联的PMOS管构成。

每个输入端连到一个PMOS管和一个NMOS管的栅极。

当输入A、B均为高电平时,TN1和TN2导通,TP1和TP2截止,输出端为低电平;当输入A、B中至少有一个为低电平时,对应的TN1和TN2中至少有一个截止,TP1和TP2中至少由一个导通,输出F为高电平。

MOS 管及简单CMOS 逻辑门电路原理图现代单片机主要是采用CMO 工艺制成的。

1、MOS 管 MOS 管又分为两种类型:N 型和P 型。

如下图所示:V DD45 Ic6=VssP 型MOS 管以N 型管为例,2端为控制端,称为“栅极”;3端通常接地,称为 “源极”;源极电压记作Vss , 1端接正电压,称为“漏极”,漏极电压记作VDD 要使1端与3端导通,栅极2上要加高电平。

对P 型管,栅极、源极、漏极分别为 5端、4端、6端。

要使4 端与6端导通,栅极5要加低电平。

在CMO 工艺制成的逻辑器件或单片机中,N 型管与P 型管往往是 成对出现的。

同时出现的这两个 CMO 管,任何时候,只要一只导通,另一只则 不导通(即“截止”或“关断”),所以称为“互补型—CMO 管”。

.2、CMO 逻辑电平高速CMO 电路的电源电压 VDD S 常为+5V; Vss 接地,是0V 。

高电平视为逻辑“ 1”,电平值的范围为:VDD 勺65%-VDD 或者VDD-1.5V 〜VDD低电平视作逻辑“ 0”,要求不超过 VDD 的35%或 0〜1.5V 。

+1.5 V 〜+3.5V 应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有 助于降低功耗。

VDD 为3.3V 的CMO 器件已大量使用。

在便携式应用中, VDC 为2.7V ,甚至1.8V 的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V , 但低于VDD 的 35%勺电平视为逻辑“ 0”,高于VDD 勺65%勺电平视为逻辑“ 1” 的规律仍然是适用的。

VDD VssV DD_ VssI 订]原理图非门(反向器)是最简单的门电路,由一对 CMOS 管组成。

其工作原理如 下: A 端为高电平时,P 型管截止,N 型管导通,输出端C 的电平与Vss 保持一 致,输出低电平;A 端为低电平时,P 型管导通,N 型管截止,输出端C 的电平 与V DD —致,输出高电平。

CMOS逻辑门电路CMOS是互补对称MOS电路的简称(Complementary Metal-Oxide-Semiconductor),其电路结构都采用增强型PMOS管和增强型NMOS管按互补对称形式连接而成,由于CMOS 集成电路具有功耗低、工作电流电压范围宽、抗干扰能力强、输入阻抗高、扇出系数大、集成度高,成本低等一系列优点,其应用领域十分广泛,尤其在大规模集成电路中更显示出它的优越性,是目前得到广泛应用的器件。

一、CMOS反相器CMOS反相器是CMOS集成电路最基本的逻辑元件之一,其电路如图11-36所示,它是由一个增强型NMOS管T N和一个PMOS管T P按互补对称形式连接而成。

两管的栅极相连作为反相器的输入端,漏极相连作为输出端,T P管的衬底和源极相连接电源U DD,T N管的衬底与源极相连后接地,一般地U DD>(U TN+|U TP|),(U TN和|U TP|是T N和T P的开启电压)。

当输入电压u i=“0”(低电平)时,NMOS管T N截止,而PMOS管T P导通,这时T N 管的阻抗比T P管的阻抗高的多,(两阻抗比值可高达106以上),电源电压主要降在T N上,输出电压为“1”(约为U DD)。

当输入电压u i=“1”(高电平)时,T N导通,T P截止,电源电压主要降在T P上,输出u o=“0”,可见此电路实现了逻辑“非”功能。

通过CMOS反相器电路原理分析,可发现CMOS门电路相比NMOS、PMOS门电路具有如下优点:①无论输入是高电平还是低电平,T N和T P两管中总是一个管子截止,另一个导通,流过电源的电流仅是截止管的沟道泄漏电流,因此,静态功耗很小。

②两管总是一个管子充分导通,这使得输出端的等效电容C L能通过低阻抗充放电,改善了输出波形,同时提高了工作速度。

③由于输出低电平约为0V,输出高电平为U DD,因此,输出的逻辑幅度大。

CMOS反相器的电压传输特性如图11-37所示。

COMS 门电路 (双击自动滚屏)CMOS 反相器由一个p 沟道,一个N 沟道增强型MOS 管组成的CMOS 反相器电路。

设T 1 、T 2的开启电压为V GS(th),电源电压V DD > V GS(th)。

于是分析其逻辑功能:V I =V IL ,A=0 则 T 1T 2T1导通(其内阻为1左右)T 2夹断(其内阻为)V DD 在T 1 、T 2分压,得,Y=1V I =V IH = V DD ,A=1 则 ,V GS2=V DDT1 夹断,T 2导通,低电平(接近地电平),Y=0无论A=0,还是1,两个p 沟道和N 沟道NOS 管始终保持其一导通、其二夹断的工作状态——称为互补状态。

这种由p 沟道、另一个N 沟道增强型MOS 管组成的电路称为CMOS 电路。

本节讨论所使用的MOS 管均为增强型。

下面对此不再另做说明。

为画图方便,下面我们用图(c )(d )两个符号来代替图(a )(b )中N 沟道和p 沟道增强型MOS 管的符号。

CMOS 与非门及或非门上图的电路输出端与地之间是两N MOS管串联,与电源V DD之间是两p MOS管并联。

T2、T4只要有一个夹断(A、B两者有一个0,或都等于0),Y对地阻抗无穷大;T1、T3必有一个导通(A、B两者有一个0),Y与电源V DD导通,输出高电平Y=1。

当A=B=1,T2、T4导通,T1、T3都夹断,Y=0。

真值表如下。

通过类似的分析可得下图的真值表。

左图真值表右图真值表CMOS传输门和双向模拟开关CMOS传输门由两个增强型MOS管(一个p沟道,另一个N沟道)组成的CMOS传输门电路及逻辑符号如下图左、右所示:设控制信号C和的高低电平分别为V DD和0V,开启电压为V GS(th)1. C=0,=1时,只要输入信号v的范围不超过0~V DD,T1、T2同时夹断,输出与I输入之间呈高阻状态(>109Ω),象机械开关的开断状态一样,传输门不通。

MOS管及简单CMOS逻辑门电路原理图

现代单片机主要是采用CMOS工艺制成的。

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:

以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4

端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMOS管,任何时候,只要一只导通,另一只则不导通(即“截止”或“关断”),所以称为“互补型CMOS管”。

2、CMOS逻辑电平

高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者~VDD)

低电平视作逻辑“0”,要求不超过VDD的35%或0~。

+~+应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为的CMOS器件已大量使用。

在便携式应用中,VDD为,甚至的单片机也已经出现。

将来电源电压还会继续下降,降到,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门

非门(反向器)是最简单的门电路,由一对CMOS管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与V一致,输出高电平。

4、与非门

与非门工作原理:

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V一致,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

③、A输入低电平,B输入高电平时,情况与②类似,亦输出高电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平。

5、或非门

或非门工作原理:

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V一致,输出高电平。

②、A输入高电平,B输入低电平时,1、4管导通,2、3管截止,C端输出低电平。

③、A输入低电平,B输入高电平时,情况与②类似,亦输出低电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平。

注:

将上述“与非”门、“或非”门逻辑符号的输出端的小圆圈去掉,就成了“与”门、“或”门的逻辑符号。

而实现“与”、“或”功能的电路图则必须在输出端加上一个反向器,即加上一对CMOS管,因此,“与”门实际上比“与非”门复杂,延迟时间也长些,这一点在电路设计中要注意。

6、三态门

三态门的工作原理:

当控制端C为“1”时,N型管3导通,同时,C端电平通过反向器后成为低电平,使P型管4导通,输入端A的电平状况可以通过3、4管到达输出端B。

当控制端C为“0”时,3、4管都截止,输入端A的电平状况无法到达输出端B,输出端B呈现高电阻的状态,称为“高阻态”。

这个器件也称作“带控制端的传输门”。

带有一定驱动能力的三态门也称作“缓冲器”,逻辑符号是一样的。

注:

从CMOS等效电路或者真值表、逻辑表达式上都可以看出,把“0”和“1”换个位置,“与非”门就变成了“或非”门。

对于“1”有效的信号是“与非”关系,对于“0”有效的信号是“或非”关系。

上述图中画的逻辑器件符号均是正逻辑下的输入、输出关系,即对“1”(高电平)有效而言。

而单片机中的多数控制信号是按照负有效(低电平有效)定义的。

例如片选信号CS(Chip Select),指该信号为“0”时具有字符标明的意义,即该信号为“0”表示该芯片被选中。

因此,“或非”门的逻辑符号也可以画成下图。

7、组合逻辑电路

“与非”门、“或非”门等逻辑电路的不同组合可以得到各种组合逻辑电路,如译码器、解码器、多路开关等。

组合逻辑电路的实现可以使用现成的集成电路,也可以使用可编程逻辑器件,如PAL、GAL等实现。

三态门与高阻态

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。

高阻态相当于隔断状态(电阻很大,相当于开路)。

三态门都有一个EN控制使能端,来控制门电路的通断。

可以具备这三种状态的器件就叫做三态(门,总线,......).

计算机里面用 1和0表示是,非两种逻辑,但是,有时候,这是不够的,比如说,他不够富有,但是他也不一定穷啊;她不漂亮,但也不一定丑啊,处于这两个极端的中间,就用那个既不是+也不是―的中间态表示,叫做高阻态。

高电平,低电平可以由内部电路拉高和拉低。

而高阻态时引

之一就是I/O(输入/输出)口在输入时读入外部电平用。

高阻态相当于该门和它连接的电路处于断开的状态。

(因为实际电路中你不可能去断开它,所以设置这样一个状态使它处于断开状态)。

三态门是一种扩展逻辑功能的输出级,也是一种控制开关。

主要是用于总线的连接,因为总线只允许同时只有一个使用者。

通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。

如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

如果你的设备端口要挂在一个总线上,必须通过三态缓冲器。

因为

以输入这个输出端口的数据。

所以你还需要有总线控制管理,访问到哪个端口,那个端口的三态缓冲器才可以转入输出状态,这是典型的三态门应用。

如果在线上没有两个以上的输出设备, 当然用不到三态门,而线或逻辑又另当别论了。

++++++++++++++++++++++++++++++++++++

高阻态这是一个数字电路里常见的述语,指的是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定。

高阻态的实质:电路分析时高阻态可做开路理解。

你可以把它看作输出(输入)电阻非常大。

他的极限可以认为悬空。

也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。

而实际应用上与引脚的悬空几是一样的。

(当门电路的输出上拉管导通而下拉管截止时,输出为高电平;反之就是低电平;如上拉管和下拉管都截止时,输出端就相当于浮空(没有电流流动),其电平随外部电平高低而定,即该门电路放弃对输出端电路的控制)

典型应用:

1、在总线连接的结构上。

总线上挂有多个设备,设备于总线以高阻的形式连接。

这样在设备不占用总线时自动释放总线(放弃对总线的使用),以方便其他设备获得总线的使用权。

2、大部分单片机I/O使用时都可以设置为高阻输入,如陵阳,AVR等等。

高阻输入(类似于CMOS输入阻抗)可以认为输入电阻是无穷大的,认为I/O对前级影响极小,而且不产生电流(不衰减),而且在一定程度上也增加了芯片的抗电压冲击能力

触发器/寄存器/锁存器

1、D触发器

2、寄存器

3、锁存器。