CD4046锁相环在感应加热电源中的应用[1]

- 格式:pdf

- 大小:197.06 KB

- 文档页数:4

CD 4046集成锁相环在感应加热电源中的应用重庆大学(630044) 毛 鸿成都铁路分局供电段(610081) 王 翔摘 要:提出一种由CD 4046集成锁相环设计的应用于感应加热电源的无相差频率跟踪控制系统,并就控制系统的相位补偿、电源的起动等问题进行了分析讨论。

关键词:锁相环 频率跟踪 相位补偿 感应加热电源在加热过程中,由于温度的变化和炉料熔化等因素,负载等效参数发生变化,负载固有频率也发生变化。

对可控硅中频逆变器而言,为了保证感应加热电源逆变器件可靠换流(可控硅中频电源要求它的负载为电容性)和电源工作在较高的功率因数,逆变器输出频率需要随负载频率而变化,也就是说,控制电路必须具有自动频率跟踪功能〔2〕。

由可关断器件构成的逆变器件,虽然不象可控硅那样存在换流问题,但为了使逆变器始终工作在功率因数接近或等于1的准谐振或谐振状态,以实现逆变器件的零电流换流(ZCS )或零电压换流(Z V S ),频率跟踪电路也是不可图2 频率跟踪控制电路与主电路缺少的。

而且,由于逆变器输出频率的提高,频率跟踪电路的快速性和准确性要求也相应提高,为此,本文提出一种用集成锁相环CD 4046,霍尔电流传感器和高速比较器实现的无相差频率跟踪控制系统,该控制电路具有跟踪快速、准确、保护容易、抗干扰能力强等优点。

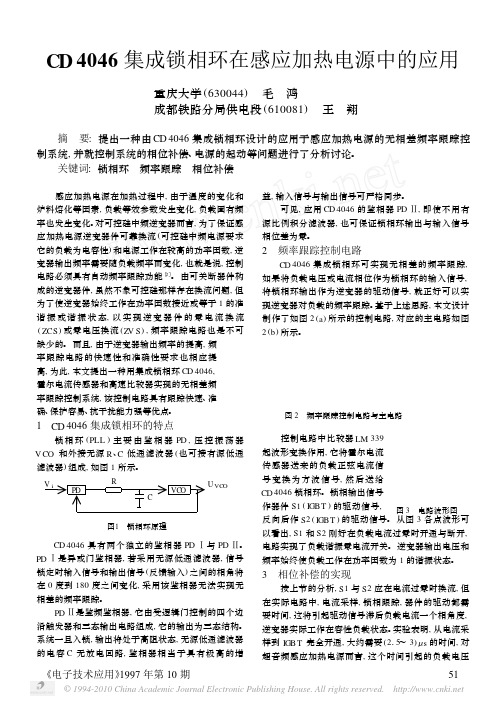

1 CD 4046集成锁相环的特点锁相环(PLL )主要由鉴相器PD ,压控振荡器V CO 和外接无源R 、C 低通滤波器(也可接有源低通滤波器)组成,如图1所示。

・图1锁相环原理iV CVC OU VC ORPDCD 4046具有两个独立的鉴相器PD 与PD 。

PD 是异或门鉴相器,若采用无源低通滤波器,信号锁定时输入信号和输出信号(反馈输入)之间的相角将在0度到180度之间变化,采用该鉴相器无法实现无相差的频率跟踪。

PD 是鉴频鉴相器,它由受逻辑门控制的四个边沿触发器和三态输出电路组成,它的输出为三态结构。

CD4046 锁相环在感应加热电源中的应用

应用于钎焊、熔炼等热加工工艺的感应加热电源在运行过程中,随着负载温度升高和炉料的熔化,负载等效参数会产生时变,从而引起负载固有谐振频率的变化。

为了使逆变器始终工作在功率因数接近或等于 1 的准谐振或谐振状态,控制电路必须能够实现频率自动跟踪。

本文采用LEM 电流传感器、电压比较器和CD4046 锁相环对负载电流

进行频率跟踪,实现了功率器件的零电流开关(ZCS),减小了开关损耗和电磁干扰(EMI)。

由于在电路刚起动时,电流反馈信号为零,CD4046 不能入锁。

本文提出了一种利用CD4046 自身特点实现的它激到自

激的转换电路,很好地解决了这一问题。

另外,加上相位补偿电路的引入,最终实现了频率自动跟踪控制。

整个电路具有跟踪速度快、跟踪频率准确、保护容易、抗干扰能力强等优点。

CD4046 锁相环在感应加热电源中的应用----锁相环功能原理

锁相环简称为PLL ,主要由3 个基本单元构成:相位比较器PD 、压

控振荡器VCO 和外接的R 、C 无源低通滤波器LPF 。

CD4046 包含前

面 2 个单元,使用时外接低通滤波器,从而形成完整的锁相环。

PLL 功能框图如图1 所示。

目前对于电动机rpm(revolutionsperminute,r/m)转速测量的方法很多,常见的有机械rpm转速测量法、光学rpm转速测量法等方法。

机械rpm转速测量是最古老的rpm转速测量方法。

它通过机械测量传感器采集数据,再通过仪器内部的电子分析才能得到测量结果。

这种测量方法在测量过程中依赖于接触压力,其最大的缺点是加载运动不连续。

光学rpm转速测量法是一种采用反射原理的转速测量法。

它是利用测量仪器发射出的光线(红外线),经固定在待测目标上的反射条反射后,即携带上有关转速信息。

测量仪器接收反射波后,经过处理即可得到转速。

这种测量方法虽然要比机械rpm测量法先进,但是这种测量需要在考虑辐射干扰、电磁干扰和传导干扰等因素的同时,确保测量的可靠性和测量精度。

鉴于以上分析,本文在光学rpm转速测量法的基础上提出了一种改进方法,介绍了利用锁相环实现电动机转速测量的电路设计方案。

该方案设计简单,测量方便、可靠。

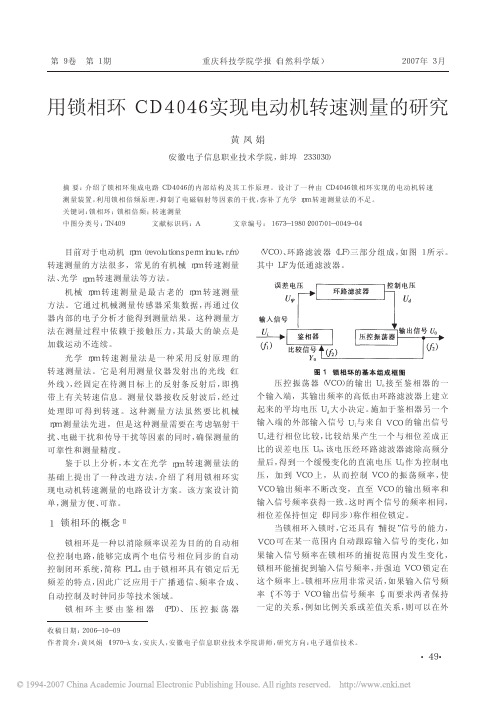

1锁相环的概念[1]锁相环是一种以消除频率误差为目的的自动相位控制电路,能够完成两个电信号相位同步的自动控制闭环系统,简称PLL。

由于锁相环具有锁定后无频差的特点,因此广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由鉴相器(PD)、压控振荡器(VCO)、环路滤波器(LF)三部分组成,如图1所示。

其中LF为低通滤波器。

图1锁相环的基本组成框图压控振荡器(VCO)的输出Uo接至鉴相器的一个输入端,其输出频率的高低由环路滤波器上建立起来的平均电压Ud大小决定。

施加于鉴相器另一个输入端的外部输入信号Ui与来自VCO的输出信号Uo进行相位比较,比较结果产生一个与相位差成正比的误差电压UΨ,该电压经环路滤波器滤除高频分量后,得到一个缓慢变化的直流电压Ud作为控制电压,加到VCO上,从而控制VCO的振荡频率,使VCO输出频率不断改变,直至VCO的输出频率和输入信号频率获得一致。

这时两个信号的频率相同,相位差保持恒定(即同步)称作相位锁定。

退出登录用户管理锁相环CD4046的原理详细介绍及应用电路作者:佚名来源:不详发布时间:2006-4-17 21:18:04 [收藏] [评论]锁相环CD4046的原理详细介绍及应用电路锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如图1所示。

图1压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

图2当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约1 00MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

CD4046CD4046引脚图锁相环芯片CD4046原理及特性过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:图3是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。

当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图4所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。

从图中还可知,fout不一定是对称波形。

对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。

它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。

在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。

锁相环CD4046应用介绍:频率相等,相位同步也就是相位相差一个固定值锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(V CO)。

低通滤波器三部分组成,如图1所示。

压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。

这个平均值电压Ud朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16 脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

CD4046中文资料锁相环CC4046为数字PLL,内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。

它具有电源电压范围宽、功耗低、输入阻抗高等优点,其工作频率达1MHz,内部VCO 产生50% 占空比的方波,输出电平可与TTL电平或CMOS 电平兼容。

同时,它还具有相位锁定状态指示功能。

信号输入端:允许输入0.1V左右的小信号或方波,经A1放大和整形,提供满足PD要求的方波。

PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率PDI由异或门构成,具有三角形鉴相特性。

它要求两个输入信号均为50%占空比的方波。

当无输入信号时,其输出电压为VDD/2,用以确定VCO的自由振荡频率。

通常输入信噪比以及固有频差较小时采用PDI,输入信噪比较高或固有频差较大时,采用PDⅡ。

R1 、R2、C确定VCO 频率范围。

R1控制最高频率,R2控制最低频率。

R2=∞时,最低频率为零。

无输入信号时,PDⅡ将VCO调整到最低频率。

锁相环CD4046的一个重要功能是:内部压迫、控振荡器的输出信号从第4脚输出后引至第3脚输入,与从第14脚输入的外部基准频率信号和相位的比较。

当两者频率相同时同,压控振荡器的频率能自动调整,直到与基准频率相同。

CD4046引脚图DC Supply Voltage 直流供电电压(VDD) −0.5 to +18 VDC Input Voltage输入电压(VIN) −0.5 to VDD +0.5 VDC Storage Temperature Range储存温度范围(TS) −65℃ to +150℃Power Dissipation功耗(PD)Dual-In-Line 普通双列封装700 mWSmall Outline 小外形封装500 mW焊接温度(TL)(焊接10秒)260℃Recommended Operating Conditions 建议操作条件:DC Supply Voltage 直流供电电压(VDD) 3 to 15 VDC Input Voltage输入电压(VIN) 0 to VDD VDC Operating Temperature Range工作温度范围(TA) −55℃ to +125℃符号引脚号名称功能PH1114相位比较器输入端(基准信号输入),相位比较器输入信号,输入允许将0.1V左右的小信号或方波信号在内部放大并再经过整形电路后,输出至相位比较器。

收稿日期:2000—04—17作者简介:熊腊森(1947—),男,湖北人,副教授,1983年~1984年美国威斯康星大学机械工程系访问学者,从事焊接教学与科研。

CD4046锁相环在感应加热电源中的应用熊腊森,全亚杰(华中理工大学,湖北武汉430074)摘要:采用了LE M 电流传感器、电压比较器和C D4046锁相环对负载电流实现了频率跟踪,使逆变器工作在功率因数接近或等于1的准谐振状态,并分析了电路中的相位补偿和起动问题。

关键词:感应加热;频率跟踪;功率因数;相位补偿;锁相环中图分类号:TG 454 文献标识码:A 文章编号:1001-2303(2000)06-0014-04Application of CD4046in induction heating pow er sourceXI ONGLa -sen ,QUAN Y a 2jie(Huazhong University of Science and T echnology ,Wuhan 430074,China )Abstract :The frequency tracking of load current is implemented by the current transducer LE M 、v oltage comparator and C D4046in this paper.The inverter operates at the quasi -res onant or res onantcondition that the power factor is nearly of equal to unity.M oreoner ,this paper analyzes the phase compensation and question of starting.K ey w ords :induction heating ;frequency tracking ;power factor ;phase compensation ;phase lock loop (P LL )1 引言应用于钎焊、熔炼等热加工工艺的感应加热电源在运行过程中,随着负载温度升高和炉料的熔化,负载等效参数会产生时变,从而引起负载固有谐振频率的变化。

为了使逆变器始终工作在功率因数接近或等于1的准谐振或谐振状态,控制电路必须能够实现频率自动跟踪。

本文采用LE M 电流传感器、电压比较器和C D4046锁相环对负载电流进行频率跟踪,实现了功率器件的零电流开关(ZCS ),减小了开关损耗和电磁干扰(E MI )。

由于在电路刚起动时,电流反馈信号为零,C D4046不能入锁。

本文提出了一种利用C D4046自身特点实现的它激到自激的转换电路,很好地解决了这一问题。

另外,加上相位补偿电路的引入,最终实现了频率自动跟踪控制。

整个电路具有跟踪速度快、跟踪频率准确、保护容易、抗干扰能力强等优点。

2 锁相环功能原理锁相环简称为P LL ,主要由3个基本单元构成:相位比较器PD 、压控振荡器VC O 和外接的R 、C 无源低通滤波器LPF 。

C D4046包含前面2个单元,使用时外接低通滤波器,从而形成完整的锁相环。

P LL 功能框图如图1所示。

图1 P LL 功能框图施加于相位比较器的有输入信号V i (t )和压控振荡器的输出信号V o (t )。

相位比较器输出信号V e (t )正比于V i (t )和V o (t )的相位差。

V e (t )经低通滤波器滤去高频成分后得到一个平均电压V d (t ),去控制压控振荡器的频率变化,使输入与输出信号频率之差不断减少,直到这个差值为零时锁定,实现频率跟踪。

低通滤波器的时间参数决定了跟随输入信号的速度,同时也限制了P LL 的捕捉范围。

3 CD4046锁相环的逻辑结构从图2中可以看出,C D4046包含了2个相位比较器(鉴相器)、1个压控振荡器以及2个附加部分,即输入信号源极跟随器和稳压管,比较器有2个共同输入信号端(3和14脚),“信号输入”既可以与大信号直接匹配,又可以间接地通过串联电容接入小信号。

自偏置电路可在放大器的线性区域调整小电压信号。

图2 C D4046锁相环的逻辑结构相位比较器1是异或门,产生1个数字信号(2脚),并在“信号输入”与“相位比较器输入”信号之间的中心频率处维持90°相移(要求输入信号占空比为50%)。

相位比较器2由逻辑门控制的4个边沿触发器和3态输出电路组成,产生数字误差信号(13脚)和相位脉冲输出(1脚),并在“信号输入”与“相位比较器输入”信号之间保持严格同步,产生0°相移(与占空比无关)。

故本文采用相位比较器2。

线性VC O (4脚)产生1个输出信号,其频率与VC O 输入的电压以及连接到引出端的电容C 值及R 1和R 2的阻值有关。

并且输出频率范围f min ~f max满足以下公式[1]:f min =1R 2(C 1+32pF )(1)f max =1R 1(C 1+32pF )+f min(2)其中 10k Ω≤R 1≤1MΩ;10k Ω≤R 2≤1MΩ;100pF ≤C 1≤0101μF 。

相位脉冲输出端(1脚),用于表示锁定或2个信号之间的相位差。

如果相位脉冲端输出高电平,表示处于锁定状态。

在信号输入端无信号输入时,压控振荡器被调整在最低频率上。

4 锁相环频率跟踪电路图3给出了对应的逆变器主电路[2]。

若将负载电压U 0和负载电流I 0的信号采样后,送至C D4046的相位比较器2,则可使U 0和I 0的相位差为零,即逆变器工作在负载谐振状态。

图3 逆变器主电路如果忽略电路中的各种时延,VC O 的输出可近似为U 0的采样信号,i 0的采样通过LE M 电流传感器实现,然后经过零比较器变换成方波信号i ,与U 0同时送至C D4046锁相环。

只要负载固有谐振频率的变化在锁相环的跟踪范围内,就可保证锁相环实现自动跟踪,U 0和i 0的相位差为零,使逆变器的功率因数达到1[3]。

根据以上分析,本文设计了如图4所示的频率跟踪电路。

图4中R 3、R 4和C 4构成了低通滤波器,它是锁相环正常工作中不可忽视的部分,其时间常数限制了系统跟踪输入信号频率变化的速度,同时也限制了捕捉范围。

另外,环路滤波器还能帮助防止噪声电压干扰环路的正常工作。

这是由于存储在环路滤波器上的电容能帮助很快重新捕获因噪声尖峰或其它瞬态效应丢失的信号。

如果时间常数过长,会使环路跟踪在较快变化的输入频率时引起过度的延迟;而过小,使环路跟踪快速变化的输入信号会引起压控振荡器输出频率的反常变化。

一般取R 3=470Ω,R 4=47Ω,C 4=011μF 。

最佳的工作状态是电阻R 4的阻值为电阻R 3的10%~30%。

由于图2中使用的是相位比较器2,具体的工作原理如下。

首先假设14脚信号超前3脚,也就是说必须增图4 频率跟踪电路加VC O 频率,以便使其上升沿进入适当的相位,于是鉴相器2的输出置为高电平,导致环路滤波器给VC O 输入端充电(即9脚电位升高),增加VC O 的频率。

一旦检测到3脚信号的前沿,输出就变为高阻态,保持VC O 输入电压等于环路滤波器的电压,若VC O 仍然滞后于14脚,则鉴相器就会在2个波形的前边沿时间内继续给VC O 输入端充电,直到2个波形的上升沿一致。

如果3脚超前14脚,则当VC O 的前沿出现时,相位比较器2的输出就变为低电平。

这样环路滤波器放电,直到检测到14脚的前沿为止。

此时环路滤波器的输出又无效,从而降低了VC O 频率,重新使得两个波形的上升沿一致。

当4脚信号(VC O 输出信号)与14脚信号(相位比较器2输入信号)正边沿之间相差为0°时,相位比较器2迫使P LL 锁定。

5 CD4046锁相环的起动入锁由于电路起动瞬间,电流反馈信号为零,VC O 始终在最低频率处振荡,这样就存在起动时不能自动入锁问题。

一般采用它激到自激的转换电路来实现起动问题。

如图5所示,电路启动后,随着电容C s 的充电,A 点电压由V CC 逐渐降低,VC O 输出频率从最大值f max 滑向最小值f min 。

只要负载的固有谐振频率在f max 至f min 之间,就会引起负载谐振,锁相环进入锁定状态,顺利地启动逆变器。

此过程完成后,二极管V 将转换电路与图4中的滤波电路隔离,锁相环正常工作于无相差跟踪状态。

图5 它激到自激的转换电路6 相位补偿的实现在实际电路中,电流采样、锁相跟踪、隔离驱动和M OSFET 的开关都需要时间,这将引起负载电压U 0滞后i 01个角度,使得逆变器实际工作在容性负载状态。

它一方面使M OSFET 在大电流处开通,另一方面使电源的功率因数降低,影响功率输出。

基于此原因,必须在实际电路中加入相位补偿环节。

本文利用C D4046锁相环的特点,配合比较器N ,巧妙地实现了相位补偿。

图6为相位补偿原理图。

在N 的正向输入端加一偏置电压U p ,使N 的输出信号上升沿提前ΔT 时间,锁相环对应的输出信号作为图3中S 1的驱动信号,反相后作S 2的驱动信号,驱动信号相对电流而言,提前了ΔT 时间,而ΔT 就是相位补偿时间。

电容C 和二极管VD 对采样电流信号i 起整流滤波作用,U p 与i 0的幅值成正比。

这样,可保证ΔT 不随I 0的幅值波动而变化。

调节电位器W ,即可根据需要调节ΔT 的值。

另外,为了防止逆变桥上下桥臂的直通短路,对(下转第19页)会导致换流时间太长使占空比损失。

一般,C s 的值应取5nF ~30nF 左右。

C r 的值一般应该取得比C s 的值大5~30倍比较合适,以满足V F 的零电压关断,并且不使有效占空比变得太少。

L r 的值影响V F 开通时和整流桥上桥臂两管关断时的电流上升率,应主要根据流过V F 管的最大电流的值进行选取,一般选择1~10μH 。

由于V 7、V 8只在极短的时间内流过电流,故可以选择比较小的管子。

214 仿真结果为验证该电路的可行性,对开关频率为50kH z ,输入电压为交流220V ,输出电压为400V ,功率为2kW 的电路用计算机来进行仿真,仿真主要参数为:L m =0.8m H ,C o =1200μF ,L r =5μH ,C r =0.1μF ,C s =0.01μF 。

输入电流波形见图4。

3 结束语本文介绍了一种可用于小功率逆变电焊机的带无源无损耗缓冲电路单元的低通态损耗新型软开关功率因数校正电路拓扑方案。

在该电路中,VF 、整流桥上桥臂两管、缓冲电路中的V 7和V 8都实现了软开关,而且整流桥的下桥臂两管在输入电压的半个周期才进行1次换流,V 5和V 6的电压应力又非常小,从而降低了该电路的损耗。