零总线翻转静态随机存取存储器(ZBT)简介

- 格式:docx

- 大小:169.28 KB

- 文档页数:3

静态随机存储器工作原理

静态随机存储器(Static Random Access Memory,SRAM)是

一种用于计算机内存的存储设备,其工作原理是利用存储电路中的稳定电荷储存信息。

SRAM由一组双稳态触发器构成,每个触发器可以储存一个

二进制位(bit),这些触发器以交叉反馈方式连接,形成稳

定的存储单元。

每个存储单元都有两个稳定的状态,即0和1,分别对应着低电平和高电平的电信号。

SRAM的读写操作是通过控制信号来完成的。

当要读取某个

存储单元的值时,控制电路将相应行线选通,并将其连接到读取电路,读取电路通过放大和判别电路将单元的电平状态转换为相应的输出信号。

当要写入某个存储单元的值时,控制电路将相应行线选通,并将写入数据送入存储单元,存储单元根据输入数据的电平状态来改变其状态。

SRAM相对于动态随机存储器(DRAM)来说,具有读写速

度快、读写可靠性高的特点,但也相应占用较大的面积和功耗较高。

因此,在计算机系统中,SRAM通常用于高速缓存等

需要快速读写的存储器部分。

主存储器随机存取,简称随机存取,是一种计算机存储器的数据访问方式。

在随机存取中,存储器的每个存储单元都有一个唯一的地址,可以通过该地址直接访问存储单元。

这种存取方式可以使计算机更快地访问和修改存储器中的信息。

随机存取存储器,简称RAM,是一种常见的主存储器类型。

RAM存储器具有速度快、价格低廉等特点,被广泛应用于计算机、智能手机、平板电脑等设备中。

RAM存储器分为两类:静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)。

静态随机存取存储器(SRAM)的特点是速度快、功耗低,但价格较高。

SRAM通常用于高速缓存和寄存器等对速度要求较高的应用。

动态随机存取存储器(DRAM)的特点是价格较低、容量较大,但速度较慢、功耗较高。

DRAM被广泛应用于计算机的主存储器中。

随机存取存储器在计算机系统中发挥着重要作用。

例如,在操作系统中,随机存取存储器被用于存储正在运行的程序和所需的数据。

当计算机需要访问这些数据时,它可以直接通过随机存取方式快速访问存储器。

此外,随机存取存储器还被用于存储计算机的BIOS和其他基本输入输出系统。

随着科技的发展,随机存取存储器技术也在不断发展。

例如,新型的存储器技术如铁电随机存取存储器(FRAM)和相变随机存取存储器(PCM)正在逐渐兴起。

这些新型存储器技术在速度和功耗等方面具有更好的性能,有望在未来取代传统的随机存取存储器。

随机存取存储器名词解释

随机存取存储器(Random Access Memory,RAM)是计算机中一

种用于临时存储数据的主要存储设备。

它是一种易失性存储器,意

味着在断电或重启计算机时,存储在RAM中的数据会被清空。

RAM具有随机访问的特性,这意味着可以直接读取或写入存储

器中的任何位置,而不需要按照顺序逐个访问。

这种随机存取的特

性使得RAM能够快速地存取和处理数据,比起其他存储设备(如硬

盘或固态硬盘)具有更快的读写速度。

RAM通常分为两种类型,静态随机存取存储器(Static RAM,SRAM)和动态随机存取存储器(Dynamic RAM,DRAM)。

SRAM由触

发器构成,能够在没有时钟信号的情况下保持数据的稳定性,因此

具有更快的访问速度,但相对较高的成本。

而DRAM则使用电容来存

储数据,需要定期刷新以保持数据的稳定,相对于SRAM,DRAM的访

问速度较慢,但成本较低。

RAM在计算机中扮演着重要的角色,用于存储正在运行的程序、操作系统和临时数据。

它的容量决定了计算机可以同时处理的数据量,较大的RAM容量可以提高计算机的性能和多任务处理能力。

然

而,由于RAM是易失性存储器,断电或重启计算机会导致数据丢失,因此需要将重要的数据定期保存到非易失性存储设备上,如硬盘或

固态硬盘。

计算机组成原理第四章存储系统4.3 静态存储器工作原理1SRAM 存储单元结构•工作管: T 1、 T 2 (保存数据) V ss (0V)T 4T 3 T 1 T 2 T 7T 8T 5T 6V DD (5V)I/OO /IX 地址译码线•负载管: T 3、 T 4 (补充电荷)•门控管: T 5、T 6 、T 7、T 8 (开关作用)Y 地址译码线A B⏹Y 地址选通 (列选通)☐T7、T8管导通☐A 点电位输出到I/O 端2SRAM 存储单元工作原理V ss (0V)T 4T 3 T 1 T 2 T 7 T 8T 5T 6V DD (5V)I/OO /IX 地址译码线Y 地址译码线⏹X 地址选通(行选通) ☐T5、T6管导通☐A 点与位线相连 A B2SRAM 存储单元工作原理•写过程X 有效→ T 5、 T 6 通 → A 与 I/O 连通 Y 有效→ T 7、 T 8 通 → B 与 I/O 连通I/O=1 →A= 1→ T 2 通→ B=0 → T 1 截止I/O=0 →B= 0→ T 1截止→ A=1 → T 2通 此时, T 1、T 2形成了稳态: A=1、B=0此时, T1、T2形成了稳态,B=1、A=0I/O=0 →A= 0→ T 2截止 → B=1 → T 1通 I/O=1 →B= 1→ T 1 通→A=0 → T 2 截止写1写0V ss (0V)T 4T 3 T 1 T 2 T 7 T 8T 5T 6V DD (5V)I/OO /IX 地址译码线Y 地址译码线A B2SRAM 存储单元工作原理•读过程X 有效→ T 5、 T 6 通 → A 与 I/O 连通Y 有效→ T 7、 T 8 通 → B 与 I/O 连通V ss (0V)T 4T 3 T 1 T 2 T 7 T 8T 5T 6V DD (5V)I/OO /IX 地址译码线Y 地址译码线通过外接于I/O 与 I/O 间的电流放大器中的电流方向可判断读出的是1还是0(与写入时定义的1和0有关)无论读/写,都要求X 和 Y 译码线同时有效A B2SRAM 存储单元工作原理•保持X 、 Y 撤销后,由负载管 T 3、 T 4 分别为工作管T 1、 T 2 提供工作电流,保持其稳定互锁状态不变。

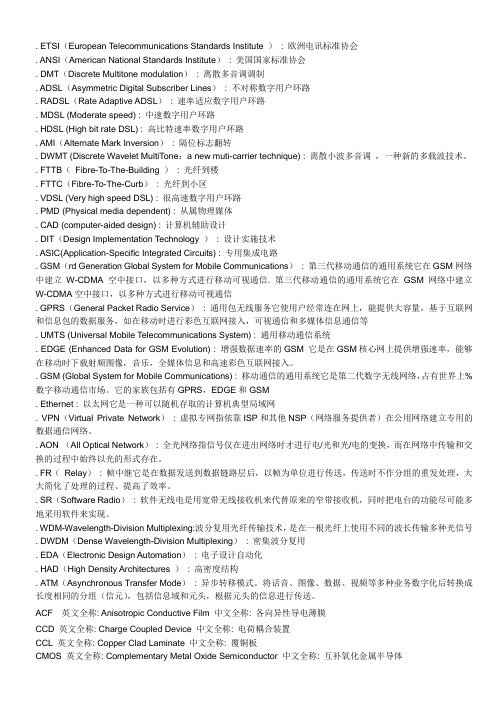

. ETSI(European Telecommunications Standards Institute ): 欧洲电讯标准协会. ANSI(American National Standards Institute): 美国国家标准协会. DMT(Discrete Multitone modulation): 离散多音调调制. ADSL(Asymmetric Digital Subscriber Lines): 不对称数字用户环路. RADSL(Rate Adaptive ADSL): 速率适应数字用户环路. MDSL (Moderate speed) : 中速数字用户环路. HDSL (High bit rate DSL) : 高比特速率数字用户环路. AMI(Alternate Mark Inversion): 隔位标志翻转. DWMT (Discrete Wavelet MultiTone:a new muti-carrier technique) : 离散小波多音调,一种新的多载波技术。

. FTTB(Fibre-To-The-Building ): 光纤到楼. FTTC(Fibre-To-The-Curb): 光纤到小区. VDSL (Very high speed DSL) : 很高速数字用户环路. PMD (Physical media dependent) : 从属物理媒体. CAD (computer-aided design) : 计算机辅助设计. DIT(Design Implementation Technology ): 设计实施技术. ASIC(Application-Specific Integrated Circuits) : 专用集成电路. GSM(rd Generation Global System for Mobile Communications): 第三代移动通信的通用系统它在GSM网络中建立W-CDMA空中接口,以多种方式进行移动可视通信. 第三代移动通信的通用系统它在GSM网络中建立W-CDMA空中接口,以多种方式进行移动可视通信. GPRS(General Packet Radio Service): 通用包无线服务它使用户经常连在网上,能提供大容量,基于互联网和信息包的数据服务,如在移动时进行彩色互联网接入,可视通信和多媒体信息通信等. UMTS (Universal Mobile Telecommunications System) : 通用移动通信系统. EDGE (Enhanced Data for GSM Evolution) : 增强数据速率的GSM 它是在GSM核心网上提供增强速率,能够在移动时下载射频图像,音乐,全媒体信息和高速彩色互联网接入。

静态随机存取存储器(SRAM)目录1.前言: (1)2.关于静态存储器SRAM的简单介绍 (2)3.基本的静态存储元阵列 (2)4.基本的SRAM逻辑结构 (3)5.SRAM读/写时序 (7)6.存储器容量的扩充 (8)6.1.位扩展 (8)6.2.字扩展 (9)6.3.字位扩展 (10)1.前言:主存(内部存储器)是半导体存储器。

根据信息存储的机理不同可以分为两类:静态读写存储器(SRAM):存取速度快动态读写存储器(DRAM):存储密度和容量比SRAM大。

-VDD一CSDN@rn0_736794312.关于静态存储器SRAM的简单介绍SRAM是采用CMOS工艺的内存。

自CMOS发展早期以来,SRAM一直是开发和转移到任何新式CMOS工艺制造的技术驱动力。

SRAM它实际上是一个非常重要的存储器,用途非常广泛。

SRAM数据完整性可以在快速读取和刷新时保持。

SRAM以双稳态电路的形式存储数据。

SRAM 目前的电路结构非常复杂。

SRAM大部分只用于CPU内部一级缓存及其内置二级缓存。

只有少量的网站服务器及其路由器可以使用SRAM o半导体存储体由多个基本存储电路组成,每个基本存储电路对应一个二进制数位。

SRAM中的每一位均存储在四个晶体管中,形成两个交叉耦合反向器。

存储单元有两个稳定状态,一般为0和1。

此外,还需要两个访问晶体管来控制存储单元在读或写过程中的访问。

因此,存储位通常需要六个MoSFET。

SRAM内部包含的存储阵列可以理解为表格,数据填写在表格上。

就像表格搜索一样,特定的线地址和列地址可以准确地找到目标单元格,这是SRAM存储器寻址的基本原理。

这样的每个单元格都被称为存储单元,而这样的表也被称为存储矩阵。

地址解码器将N个地址线转换为2个N立方电源线,每个电源线对应一行或一列存储单元,根据地址线找到特定的存储单元,完成地址搜索。

如果存储阵列相对较大,地址线将分为行和列地址,或行,列重用同一地址总线,访问数据搜索地址,然后传输列地址。

存储器的工作原理一、引言存储器是计算机系统中的重要组成部份,用于存储和检索数据。

它的工作原理涉及到数据的存储、访问和传输等方面。

本文将详细介绍存储器的工作原理。

二、存储器的分类存储器按照不同的工作原理和功能可以分为随机存储器(RAM)和只读存储器(ROM)两大类。

其中,RAM又可分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。

三、静态随机存储器(SRAM)的工作原理SRAM是一种基于触发器的存储器,它的工作原理如下:1. SRAM由一组触发器组成,每一个触发器可以存储一个比特(0或者1)的数据。

2. 当写入数据时,控制电路将数据传输到指定的触发器中,并将写入信号传递给触发器,使其将数据存储起来。

3. 当读取数据时,控制电路将读取信号传递给指定的触发器,触发器将存储的数据输出给外部设备。

四、动态随机存储器(DRAM)的工作原理DRAM是一种基于电容的存储器,它的工作原理如下:1. DRAM由一组存储单元组成,每一个存储单元由一个电容和一个开关(通常是一个MOSFET)组成。

2. 当写入数据时,控制电路将数据传输到指定的存储单元的电容中,并将写入信号传递给开关,使其打开或者关闭,以控制电容的充放电状态。

3. 当读取数据时,控制电路将读取信号传递给指定的存储单元的开关,开关的状态决定了电容的充放电状态,从而输出存储的数据。

五、只读存储器(ROM)的工作原理ROM是一种只能读取数据而无法写入数据的存储器,它的工作原理如下:1. ROM中的数据是在创造过程中被编程的,无法在运行时修改。

2. ROM的存储单元通常由一个开关(通常是一个MOSFET)组成,其状态决定了存储的数据。

3. 当读取数据时,控制电路将读取信号传递给指定的存储单元的开关,开关的状态决定了存储的数据输出。

六、存储器的访问速度存储器的访问速度是指从发出读取或者写入指令到数据可用的时间间隔。

它受到存储器类型、存储单元数量、控制电路设计等因素的影响。

静态存储器的名词解释静态存储器是一种计算机数据存储设备,它的主要作用是用来存储和读取计算机程序和数据。

相对于动态存储器来说,静态存储器具有较快的访问速度和较低的功耗。

在计算机系统中,静态存储器扮演着重要角色,它使得计算机能够高效地储存和使用数据。

静态存储器主要包括随机存取存储器(RAM)和只读存储器(ROM)。

RAM 是一种可读写的存储器,它被用来暂时存储程序和数据。

当计算机加电启动时,操作系统和其他必要的软件程序会被加载到RAM中,这样CPU可以迅速访问和执行它们。

RAM通常被划分为许多小的存储单元,每个存储单元都有一个唯一的地址,通过地址可以访问到特定的数据。

ROM是一种只能读取的存储器,它的数据在出厂时就被固化到芯片中了。

这些数据通常包括计算机的基本输入输出系统(BIOS)和其他不需要经常修改的软件程序。

ROM的优点是数据的持久性和稳定性,即使断电重启,存储在ROM中的数据也不会丢失。

但是,由于ROM的数据无法被修改,因此它只适用于储存固定的程序和数据,无法灵活地满足计算机系统的需求。

静态存储器的特点是它们的存储单元不需要定期刷新,因此数据可以长时间地保留下来。

这使得静态存储器在计算机系统中扮演着重要的角色,特别是需要快速访问数据的应用。

然而,静态存储器也有一些限制。

首先,它相对于动态存储器来说更昂贵,这使得它在大容量存储需求的应用中不太经济实惠。

其次,静态存储器的能耗较高,这对于需要长时间运行的移动设备来说可能是个问题。

虽然静态存储器具有许多优势,但它也不是没有缺点。

静态存储器的主要问题之一是容量限制。

由于制造静态存储器需要更多的物理空间,因此相对于动态存储器,静态存储器的容量较小。

此外,静态存储器的制造成本也比较高,这使得大容量静态存储器的价格相对较高。

近年来,随着技术的不断进步,静态存储器的性能和容量得到了显著提升。

新一代静态存储器产品采用了更先进的制造工艺,使得存储单元的密度大大提高,容量也呈指数级增长。

16-Mbit (1M x 16) Static RAMCY62167DV30MoBLFeatures•Very high speed: 55 ns•Wide voltage range: 2.20V – 3.60V •Ultra-low active power— Typical active current: 2 mA @ f = 1 MHz — Typical active current: 15 mA @ f = f max •Ultra-low standby power•Easy memory expansion with CE 1, CE 2, and OE features•Automatic power-down when deselected •CMOS for optimum speed/power•Packages offered in a 48-ball BGA and 48-pin TSOPIFunctional Description [1]The CY62167DV30 is a high-performance CMOS static RAM organized as 1M words by 16 bits. This device features advanced circuit design to provide ultra-low active current.This is ideal for providing More Battery Life (MoBL ) in portable applications such as cellular telephones. The device also has an automatic power-down feature that significantlyreduces power consumption by 99% when addresses are not toggling. The device can also be put into standby mode when deselected (CE 1 HIGH or CE 2 LOW or both BHE and BLE are HIGH). The input/output pins (I/O 0 through I/O 15) are placed in a high-impedance state when: deselected (CE 1HIGH or CE 2LOW), outputs are disabled (OE HIGH), both Byte High Enable and Byte Low Enable are disabled (BHE, BLE HIGH),or during a Write operation (CE 1 LOW, CE 2 HIGH and WE LOW).Writing to the device is accomplished by taking Chip Enables (CE 1 LOW and CE 2 HIGH) and Write Enable (WE) input LOW.If Byte Low Enable (BLE) is LOW, then data from I/O pins (I/O 0through I/O 7), is written into the location specified on the address pins (A 0 through A 19). If Byte High Enable (BHE) is LOW, then data from I/O pins (I/O 8 through I/O 15) is written into the location specified on the address pins (A 0 through A 19).Reading from the device is accomplished by taking Chip Enables (CE 1 LOW and CE 2 HIGH) and Output Enable (OE)LOW while forcing the Write Enable (WE) HIGH. If Byte Low Enable (BLE) is LOW, then data from the memory location specified by the address pins will appear on I/O 0 to I/O 7. If Byte High Enable (BHE) is LOW, then data from memory will appear on I/O 8 to I/O 15. See the truth table at the back of this data sheet for a complete description of Read and Write modes.Note:1.For best-practice recommendations, please refer to the Cypress application note “System Design Guidelines” on .Logic Block Diagram1M × 16RAM ArrayI/O0 – I/O7R O W D E C O D E RA 8A 7A 6A 5A 2COLUMN DECODERA 11A 12A 13A 14A 15S E N S E A M P SDATA IN DRIVERSOE A 4A 3I/O8 – I/O15WE BLEBHE A 16A 0A 1A 17A 9 A 18A 10Power-down CircuitBHE BLECE 2CE 1CE 2CE 1A 19Pin Configuration [2, 3, 4, 5]FBGA48TSOPI (Forward)Notes:2.NC pins are not connected on the die.3.DNU pins have to be left floating.4.The BYTE pin in the 48-TSOPI package has to be tied HIGH to use the device as a 1M × 16 SRAM. The 48-TSOPI package can also be used as a 2M × 8 SRAM by tying the BYTE signal LOW. For 2M × 8 Functionality, please refer to the CY62168DV30 datasheet. In the 2M × 8 configuration, Pin 45 is A20.5.Ball H6 for the FBGA package can be used to upgrade to a 32M density.WE A 11A 10A 6A 0A 3CE 1I/O 10I/O 8I/O 9A 4A 5I/O 11I/O 13I/O 12I/O 14I/O 15V SS A 9A 8OE Vss A 7I/O 0BHE CE 2A 17A 2A 1BLE V CC I/O 2I/O 1I/O 3I/O 4I/O 5I/O 6I/O 7A 15A 14A 13A 12A 19A 18DNU326541D E B A C F G HTop ViewA 16 DNU Vcc Top View123456789101112131415161718192021222324484746454443424140393837363534333231302928272625A15A14A13A12A11A10A9A8A19NC WE CE2DNU BHE BLE A18A17A7A6A5A4A3A2A1A16BYTE VssI/O15/A20I/O7I/O14I/O6I/O13I/O5I/O12I/O4Vcc I/O11I/O3I/O10I/O2I/O9I/O1I/O8I/O0OE Vss CE1A0Maximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature ................................–65°C to + 150°C Ambient Temperature withPower Applied............................................–55°C to + 125°C Supply Voltage to Ground Potential.......–0.2V to V CC + 0.3V DC Voltage Applied to Outputsin High-Z State[6, 7].................................–0.2V to V CC + 0.3V DC Input Voltage[6, 7].............................–0.2V to V CC + 0.3V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... > 2001V (per MIL-STD-883, Method 3015)Latch-up Current.....................................................> 200 mA Operating RangeDevice RangeAmbientTemperature V CC[8] CY62167DV30L Industrial–40°C to +85°C 2.20V to3.60V CY62167DV30LLProduct PortfolioProductV CC Range (V)Speed(ns)Power DissipationOperating I CC(mA)Standby I SB2(µA)f = 1MHz f = f maxMin.Typ.[9]Max.Typ.[9]Max.Typ.[9]Max.Typ.[9]Max.CY62167DV30L 2.20 3.0 3.6055241530 2.530701225CY62167DV30LL55241530 2.522701225Electrical Characteristics Over the Operating RangeParameter Description Test ConditionsCY62167DV30-55CY62167DV30-70Unit Min.Typ.[9]Max.Min.Typ.[9]Max.V OH Output HIGH Voltage I OH = –0.1 mA V CC = 2.20V 2.0 2.0VI OH = –1.0 mA V CC = 2.70V 2.4 2.4V V OL Output LOW Voltage I OL = 0.1 mA V CC = 2.20V0.40.4VI OL = 2.1mA V CC = 2.70V 0.40.4VV IH Input HIGH Voltage V CC = 2.2V to 2.7V 1.8V CC+0.3V 1.8V CC+0.3VVV CC= 2.7V to 3.6V 2.2V CC+0.3V 2.2V CC+0.3VVV IL Input LOW Voltage V CC = 2.2V to 2.7V–0.30.6–0.30.6VV CC= 2.7V to 3.6V–0.30.8–0.30.8V I IX Input Leakage Current GND < V I < V CC–1+1–1+1µA I OZ Output LeakageCurrentGND < V O < V CC, Output Disabled–1+1–1+1µAI CC V CC Operating SupplyCurrent f = f MAX = 1/t RC V CC = V CCmaxI OUT = 0 mACMOS levels15301225mA f = 1 MHz2424mAI SB1Automatic CEPower-downCurrent — CMOSInputs CE1 > V CC − 0.2V or CE2 < 0.2VV IN > V CC – 0.2V, V IN < 0.2V)f = f MAX (Address and Data Only),f = 0 (OE, WE, BHE, BLE), V CC = 3.60VL 2.530 2.525µALL 2.522 2.522I SB2Automatic CEPower-downCurrent — CMOSInputs CE1 > V CC – 0.2V or CE2 < 0.2V,V IN > V CC – 0.2V or V IN < 0.2V,f = 0, V CC = 3.60VL 2.530 2.530µALL 2.522 2.522Notes:6.V IL(min.) = –2.0V for pulse durations less than 20 ns.7.V IH(Max) = V CC + 0.75V for pulse durations less than 20 ns.8.Full Device AC operation requires linear V CC ramp from 0 to V CC(min.)> = 500 µs.9.Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at V CC = V CC(typ.), T A = 25°C.Capacitance [10, 11]ParameterDescriptionTest ConditionsMax.Unit C IN Input Capacitance T A = 25°C, f = 1 MHz,V CC = V CC(typ)8pF C OUTOutput Capacitance10pFThermal ResistanceParameterDescriptionTest ConditionsBGA TSOP I Unit ΘJA Thermal Resistance (Junction to Ambient)[10]Still Air, soldered on a 3 × 4.5 inch, two-layer printed circuit board5560°C/W ΘJCThermal Resistance (Junction to Case)[10]164.3°C/WAC Test Loads and WaveformsV CCV CC OUTPUTR250 pF INCLUDING JIG AND SCOPEGND90%10%90%10%Rise Time = 1 V/nsFall Time = 1 V/nsOUTPUT VEquivalent to:THÉ V ENIN EQUIVALENTALL INPUT PULSESR THR1Parameters2.50V3.0V Unit R1166671103ΩR2153851554ΩR TH 8000645ΩV TH1.201.75VData Retention Characteristics (Over the Operating Range)Parameter DescriptionConditionsMin.Typ.[9]Max.Unit V DR V CC for Data Retention 1.5V I CCDR Data Retention CurrentV CC = 1.5VCE 1 > V CC – 0.2V , CE 2 < 0.2V,V IN > V CC – 0.2V or V IN < 0.2VL 15µALL 10t CDR [10]Chip Deselect to Data Retention Time 0ns t R [12]Operation Recovery Timet RCnsData Retention Waveform [13]Notes:10.Tested initially and after any design or process changes that may affect these parameters.11.This applies for all packages.12.Full device operation requires linear V CC ramp from V DR to V CC(min.) > 100 µs or stable at V CC(min.) > 100 µs.13.BHE.BLE is the AND of both BHE and BLE. Chip can be deselected by either disabling the chip enable signals or by disabling both BHE and BLE.V CC , min.V CC , min.t CDRV DR >1.5 VDATA RETENTION MODEt RCE 1 or V CCBHE .BLECE 2orSwitching Characteristics Over the Operating Range[14] Parameter Description55 ns70 nsUnit Min.Max.Min.Max.Read Cyclet RC Read Cycle Time5570nst AA Address to Data Valid5570nst OHA Data Hold from Address Change1010nst ACE CE1 LOW and CE2 HIGH to Data Valid5570nst DOE OE LOW to Data Valid2535nst LZOE OE LOW to LOW Z[15]55nst HZOE OE HIGH to High Z[15, 16]2025nst LZCE CE1 LOW and CE2 HIGH to Low Z[15]1010nst HZCE CE1 HIGH and CE2 LOW to High Z[15, 16]2025nst PU CE1 LOW and CE2 HIGH to Power-up00nst PD CE1 HIGH and CE2 LOW to Power-down5570nst DBE BLE/BHE LOW to Data Valid5570nst LZBE BLE/BHE LOW to Low Z[15]1010nst HZBE BLE/BHE HIGH to HIGH Z[15, 16]2025ns Write Cycle[17]t WC Write Cycle Time5570nst SCE CE1 LOW and CE2 HIGH to Write End4060nst AW Address Set-Up to Write End4060nst HA Address Hold from Write End00nst SA Address Set-Up to Write Start00nst PWE WE Pulse Width4045nst BW BLE / BHE LOW to Write End4060nst SD Data Set-Up to Write End2530nst HD Data Hold from Write End00nst HZWE WE LOW to High-Z[15, 16]2025nst LZWE WE HIGH to Low-Z[15]1010ns Notes:14.Test conditions for all parameters other than three-state parameters assume signal transition time of 1 ns/V, timing reference levels of V CC(typ)/2, input pulselevels of 0 to V CC(typ.), and output loading of the specified I OL/I OH as shown in the “AC Test Loads and Waveforms” section.15.At any given temperature and voltage condition, t HZCE is less than t LZCE, t HZBE is less than t LZBE, t HZOE is less than t LZOE, and t HZWE is less than t LZWE for anygiven device.16.t HZOE, t HZCE, t HZBE, and t HZWE transitions are measured when the outputs enter a high impedance state.17.The internal Write time of the memory is defined by the overlap of WE, CE1 = V IL, BHE and/or BLE = V IL, and CE2 = V IH. All signals must be ACTIVE to initiatea write and any of these signals can terminate a write by going INACTIVE. The data input set-up and hold timing should be referenced to the edge of the signalthat terminates the Write.Switching WaveformsRead Cycle 1 (Address Transition Controlled)[18, 19]Read Cycle 2 (OE Controlled)[19, 20]Notes:18.The device is continuously selected. OE, CE 1 = V IL , BHE and/or BLE = V IL , and CE 2 = V IH .19.WE is HIGH for read cycle.ADDRESSDATA OUTPREVIOUS DATA VALIDDATA VALIDt RCt AAt OHA50%50%DATA VALIDt RCt ACEt DOEt LZOEt LZCEt PUHIGH IMPEDANCE t HZOEt PD HIGH OECE 1I CC I SBIMPEDANCEADDRESSCE 2V CC SUPPLY CURRENTt HZBEBHE/BLEt LZBEt HZCEDATA OUT t DBEWrite Cycle 1 (WE Controlled)[17, 21, 22, 23]Notes:20.Address valid prior to or coincident with CE 1, BHE, BLE transition LOW and CE 2 transition HIGH.21.Data I/O is high-impedance if OE = V IH .22.If CE 1 goes HIGH and CE 2 goes LOW simultaneously with WE = V IH , the output remains in a high-impedance state.23.During this period, the I/Os are in output state and input signals should not be applied.Switching Waveforms (continued)t HDt SDt PWEt SAt HAt AWt SCEt WCt HZOEVALID DATACE 1ADDRESSCE 2WEDATA I/OOEBHE/BLEt BWSee Note 23Write Cycle 2 (CE 1 or CE 2 Controlled)[17, 21, 22, 23]Write Cycle 3 (WE Controlled, OE LOW)[22, 23]Switching Waveforms (continued)t HDt SDt PWEt HAt AWt SCEt WCt HZOEVALID DATACE 1ADDRESSCE 2WEDATA I/OOESee Note 23BHE/BLEt BWt SAVALID DATAt HD t SDt LZWEt PWEt SAt HAt AWt SCEt WCt HZWECE 1ADDRESSCE 2WEDATA I/Ot BW BHE /BLESee Note 23Write Cycle 4 (BHE/BLE Controlled, OE LOW)[22, 23]Truth TableCE 1CE 2WE OE BHE BLE Inputs/Outputs ModePower H X X X X X High Z Deselect/Power-Down Standby (I SB )X L X X X X High Z Deselect/Power-Down Standby (I SB )X X X X H H High ZDeselect/Power-DownStandby (I SB )L H H L L L Data Out (I/O 0–I/O 15)Read Active (I CC )L H H L H L Data Out (I/O 0–I/O 7); High Z (I/O 8–I/O 15)Read Active (I CC )L H H L L H High Z (I/O 0–I/O 7);Data Out (I/O 8–I/O 15)Read Active (I CC )L H H H L H High Z Output Disabled Active (I CC )L H H H H L High Z Output Disabled Active (I CC )L H H H L L High ZOutput DisabledActive (I CC )L H L X L L Data In (I/O 0–I/O 15)Write Active (I CC )L H L X H LData In (I/O 0–I/O 7);High Z (I/O 8–I/O 15)Write Active (I CC )LHLXLH High Z (I/O 0–I/O 7);Data In (I/O 8–I/O 15)WriteActive (I CC )Switching Waveforms (continued)DATA I/O ADDRESSt HDt SDt SAt HAt AWt WCCE 1 WEVALID DATAt BWBHE/BLEt SCECE 2t PWESee Note 23Ordering InformationSpeed(ns)Ordering Code PackageName Package TypeOperatingRange55CY62167DV30L-55BVI BV48B48-ball Fine Pitch BGA (8 mm × 9.5mm × 1 mm)Industrial CY62167DV30LL-55BVI55CY62167DV30L-55ZI Z48A48 Pin TSOP I Industrial CY62167DV30LL-55ZI70CY62167DV30L-70BVI BV48B48-ball Fine Pitch BGA (8 mm × 9.5mm × 1 mm)Industrial CY62167DV30LL-70BVI70CY62167DV30L-70ZI Z48A48-pin TSOP I Industrial CY62167DV30LL-70ZIPackage DiagramsCY62167DV30MoBLDocument #: 38-05328 Rev. *E Page 11 of 12© Cypress Semiconductor Corporation, 2004. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.MoBL is a registered trademark and More Battery Life is a trademark of Cypress Semiconductor Corporation. All product and company names mentioned in this document may be the trademarks of their respective holders.Package DiagramsCY62167DV30MoBL Document #: 38-05328 Rev. *E Page 12 of 12 Document History PageDocument Title:CY62167DV30 MoBL 16-Mbit (1M x 16) Static RAMDocument Number: 38-05328REV.ECN NO.Issue DateOrig. ofChange Description of Change**11840809/30/02GUG New Data Sheet*A12369202/11/03DPM Changed Advanced to PreliminaryAdded package diagram*B12655504/25/03DPM Minor change: Changed Sunset Owner from DPM to HRT*C12784109/10/03XRJ Added 48 TSOP I package*D205701AJU Changed BYTE pin usage description for 48 TSOPI package*E238050See ECN KKV/AJU Replaced 48-lead VFBGA package diagram; Modified Package Name inOrdering Information table from BV48A to BV48B。

ZBT是Zero Bus Turnaround SRAM的缩写,即“零总线翻转静态随机存取存储器”。

属于SRAM的一种,SRAM的类型有很多种,如下图所示:

1).ASRAM是普通异步静态随机存取存储器,该器件内部无参考时钟,读写时序比较简单,只要将控制信号选中指定地址和数据线即可读取或写入数据;

2).SSRAM是同步静态随机存取存储器,与ASRAM相比,内部多了一个参考时钟;

3).DPSRAM即Double Port SRAM,双口SRAM的意思;

4).Synchronous Burst SSRAM即同步突发SSRAM,读写速率比异步SRAM 快,主要有Flow-Through(直通方式)和Pipeline(流水线方式)两种操作方式;

5).DDR SRAM即双数据速率SRAM;

6).QDR SRAM即四倍数据速率SRAM,前面已经专题介绍过了;

7).ZBT SRAM即零总线翻转SRAM,也是本文的重点介绍内容。

记得之前在介绍RAM器件的时候介绍过,RAM器件在读/写操作间进行状态转换的时候,需要一些空闲指令周期NOP(No Operation)来进行过渡,普通SRAM

进行读操作时,数据滞后两个时钟周期,而写操作是即时的,从写操作状态切换到读操作状态需要等待两个时钟周期。

如果在某些需要频繁进行读/写操作切换的系统中使用普通SRAM的话,总线利用效率将会变得非常低。

为此,IDT公司联合推出ZBT SRAM,该器件通过简单的接口控制逻辑消除了读写操作转换的等待时间,在读写操作状态转换过程中无需等待,直接切换,总线利用率可达100%,非常适合读写操作频繁切换的场合。

普通SRAM和ZBT SRAM读写状态切换对比图下图所示:

ZBT SRAM根据所带有的接口的不同,可分为两种即pipelined ZBT SRAM 和flow -through ZBT SRAM,在pipelined ZBT SRAM中,读命令发出两个时钟周期之后,可得到读取的数据,写命令发出两个时钟周期之后,可以写数据;在flow - through ZBT SRAM中读命令发出一个时钟周期之后,可得到读取的数据,写命令发出一个时钟周期之后,可以写数据。

他们都支持TTL和COMS I/O口标准。

其总线操作过程如下图所示。

ZBT SRAM的接口信号主要由时钟信号、控制总线、地址总线和数据总线等组成。

其中,时钟信号是为ZBT SRAM实现包括读、写操作在内的各种操作提供驱动信号;

1).RW#是读写控制信号,RW# = 1允许读操作,RW# = 0允许写操作。

2).BW#是同步字节写使能信号,低电平有效。

3).ADV_LD#是地址控制信号,ADV_LD#= 0时内部的寄存器加载新的地址,

若在时钟的上升沿ADV_LD# = 1则内部地址计数器增加;

4).地址总线SA[ASIZE-1 :0],它为对ZBT SRAM读写操作存储器单元提供存储地址寻址信号。

其位数由ZBT SRAM的存储容量决定;

5).数据总线DQ[DSIZE-1:0]是ZBT SRAM在读写操作时与外部进行数据交换的通道。