使用Vivado 2015.4在Nexys4 DDR开发板上实现DDR的读写例程

- 格式:doc

- 大小:29.00 KB

- 文档页数:6

vivado下ddr3的读写和测试详解最近博主在根据例程做ddr3的读写测试,发现根本看不到好吧,虽然之前博主做过SDRAM的读写测试,但是ddr3更加复杂,时序写起来很吃力,所以需要用到vivado下自带的ip核。

具体来看下面例化过程:1.在ip核下搜索mig 双击打开2.直接next 然后在当前界面修改你的ddr3ip核的名字这里博主是因为已经例化了ip核,所以名字不能修改,然后next3.这是要不要兼容芯片,不选,点击next4.勾选你的存储器类型,我的是ddr3,点击next5.这个配置比较多,第一个时钟为ddr3实际工作的时钟,然后选择你的内存型号,数据宽度即可,点击next6.然后输入时钟可能需要pll倍频得到,一般是200Mhz,这里注意看下最后一行的用户地址类型,它是由bank+row+column组成的,这个在后面的读写测试会进一步提到。

7.时钟选择不差分,然后参考时钟为用户时钟。

8.下面就是默认next,然后就是分配管脚了,这个你买的开发板一般都会提高ucf文件,直接复制就行。

然后next,生成。

以上就是ip核的简单例化过程,这个步骤网上有很多类似的,博主就不一一讲解了,把精力放在读写测试这块。

首先来看老三样:ip核用户界面下的控制命令,读和写这是控制命令,可以让用户来发送读或者写命令,需要注意的事只有当app_rdy和app_en同为高时才有效,命令被发出。

这里博主通过ila上电分析发现app_rdy为ip核自己产生的输出信号,但是它并不是一直都是高电平,所以在后续的读写测试时需要判断,至于怎么判断,我们后面代加上电分析。

上面是写命令,可以看到当add_wdf_wren和add_wdf_end同为高时数据才能有效被写进去,同时app_wdf_rdy也要为高。

需要注意的一点是,写数据和写命令此时不再有关系,为什么,因为写数据其实是通过fifo缓存,当写命令有效时,由于先进先出的特性会把它所对应数据给写入,当然这个很拗口,下面会给出示例上面的是读过程,可以看出当读命令发出后需要一个延迟读数据才会有效。

用Xilinx FPGA实现DDR SDRAM控制器用Xilinx FPGA实现DDR SDRAM控制器1引言在高速信号处理系统中,需要缓存高速、大量的数据,存储器的选择与应用已成为系统实现的关键所在。

DDR SDRAM是一种高速CMOS、动态随机访问存储器,它采用双倍数据速率结构来完成高速操作。

SDR SDRAM一个时钟周期只能传输一个数据位宽的数据,因此在相同的数据总线宽度和工作频率下,DDR SDRAM的总线带宽比SDR SDRAM的总线带宽提高了一倍。

Xilinx VirtexTM-4FPGA具备ChipSync源同步技术等优势。

它的输入输出模块(IOB)提供了封装引脚与内部可配置逻辑之间的接口,无论是输入路径还是输出路径都提供了一个可选的SDR和DDR寄存器。

VirtexTM-4的IOB专门针对源同步设计进行了优化,包括每一位的偏移校正、数据的串行化和解串行化、时钟分频以及专用的本地时钟资源等,而且它在每一个I/O模块中都提供了64-阶延迟线。

这些特性使得VirtexTM-4FPGA能够更好的实现DDR SDRAM控制器的逻辑设计,准确可靠的捕获数据。

实验板选择专为DSP应用而优化的Virtex-4SX35作为DDR SDRAM控制器的实现平台,选用Micron MT46V8M16P-75Z DDR SDRAM。

2DDR SDRAM控制器工作原理DDR SDRAM控制器的主要功能就是完成对DDR SDRAM的初始化,将DDR SDRAM复杂的读写时序转化为用户简单的读写时序,以及将DDR SDRAM接口的双时钟沿数据转换为用户的单时钟沿数据,使用户像操作普通的RAM一样控制DDR SDRAM;同时,控制器还要产生周期性的刷新命令来维持DDR SDRAM内的数据而不需要用户的干预。

该控制器的模块化表示。

DDR SDRAM上电后必须按照规定的程序完成初始化的过程。

在初始化过程中一定要注意普通模式寄存器与扩展模式寄存器的值是否正确。

ddr读写流程范文DDR是一种高速存储器,常用于计算机系统中。

DDR的读写流程可以分为以下几个步骤:1.硬件初始化:在进行DDR读写操作之前,需要先对硬件进行初始化设置。

这包括设置读写时钟频率、时序参数等。

2.地址设置:首先,需要将要读写的地址信息发送给DDR控制器。

DDR控制器通过预先设置的地址映射表将逻辑地址转换为物理地址。

3.发送读命令:一旦地址设置完成,接下来发送读命令给DDR控制器。

读命令包括读使能信号和其他相关的控制信号,用于通知DDR控制器开始读取数据。

4.数据传输:DDR控制器接收到读命令后,会根据地址信息从存储器中读取数据,并通过数据总线将数据传输到内存控制器。

数据传输的速度取决于设定的时钟频率和传输宽度。

5.数据接收:内存控制器接收到DDR控制器传输的数据后,将其存储到寄存器中。

数据在存储器中的存储方式取决于具体的DDR存储器架构。

6.数据处理:一旦数据被存储到寄存器中,处理器可以通过访问寄存器来对数据进行读取、修改或其他处理操作。

处理器可以使用访问内存的指令来实现这些操作。

7.发送写命令:如果需要将处理后的数据写入DDR存储器,需要发送写命令给DDR控制器。

写命令包括写使能信号和其他相关的控制信号,用于通知DDR控制器开始写入数据。

8.数据传输:内存控制器将要写入DDR存储器的数据传输到DDR控制器,并通过地址信息将数据写入存储器的指定位置。

9.数据确认:DDR控制器在数据写入存储器后,会对写操作进行确认,确保数据已经正确写入。

以上是DDR的基本读写流程,但实际的DDR读写操作可能会有更多的细节和控制信号。

此外,DDR的读写性能还受到多个因素的影响,包括时钟频率、时序参数、总线宽度、电压供给等。

为了提高DDR的读写速度和稳定性,硬件设计者需要仔细设置这些参数,并对DDR控制器进行适当的编程。

1概述

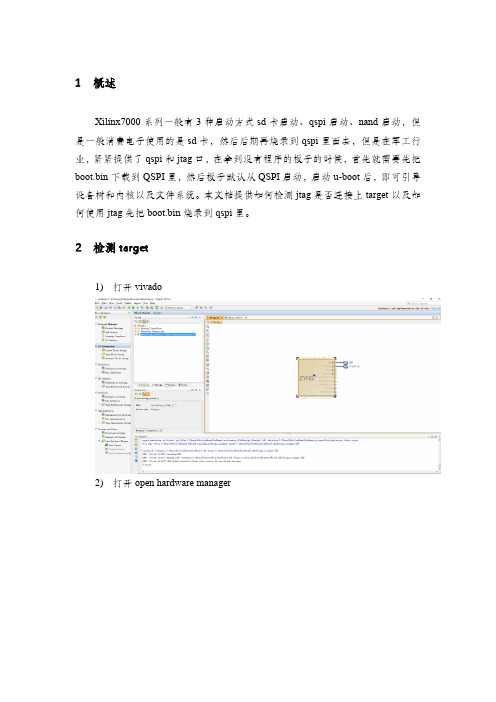

Xilinx7000系列一般有3种启动方式sd卡启动、qspi启动、nand启动,但是一般消费电子使用的是sd卡,然后后期再烧录到qspi里面去,但是在军工行业,紧紧提供了qspi和jtag口,在拿到没有程序的板子的时候,首先就需要先把boot.bin下载到QSPI里,然后板子默认从QSPI启动,启动u-boot后,即可引导设备树和内核以及文件系统。

本文档提供如何检测jtag是否连接上target以及如何使用jtag先把boot.bin烧录到qspi里。

2检测target

1)打开vivado

2)打开openhardwaremanager

3)点击opentarget

4)点击autoconnect

5)失败

6)成功

3下周boot.mcs或者boot.bin

3.1启动SDK,选择xilinx Tools中的programflash

3.2找到下载镜像,选择通信类型

Zed板子是single的,一般板子是dual的,点击program

3.3开始下载

3.4完成。

XilinxVivado的使⽤详细介绍(4):Zedboard+vivado之流⽔灯(加SDK)Vivado+zedboard之初学流⽔灯Author:zhangxianhe 环境:vivado 2016.3(已验证适⽤于2015.4)开发板:Zedboard version xc7z020clg484-1实验:使⽤Vivado和SDK进⾏Zedboard开发,制作⼀个简单的流⽔灯程序以说明软硬件协同设计的⽅法、开发流程等。

本⽂将分为三个部分:1. 使⽤Vivado创建⼀个⼯程,并构建⼀个Zynq嵌⼊式处理系统。

2. 在上述基础上,将完成后的硬件导⼊到SDK中进⾏软件设计。

3. 最后下载到ZedBoard上进⾏调试。

具体步骤如下:1. 使⽤Vivado创建⼯程1.1新建⼯程 1).⿏标左键双击Vivado2016.3图标,打开Vivado 2016.3; 2).单击Create New Project创建⼀个新的⼯程; 3).单击Next执⾏下⼀步; 4).选择⼯程所在的位置,并输⼊⼯程名ledflow,单击Next; 5).在Vivado中新建⼀个RTL⼯程,暂不添加⽂件(勾选 Do not specify sources at this time),后⾯需要的时候添加,单击Next; 6).这⼀步要注意,在左上⾓Select处选择Boards,选择ZedBoard Zynq Evaluation and Development Kit version D器件,单击Next; 7).单击Finish 8).等待软件根据设定新建⼀个RTL⼯程。

这样新建⼯程的步骤就完成了,下⾯进⾏硬件设计步骤;1.2 Vivado硬件设计 1). 单击Create Block Design,创建并添加IP核; 2).输⼊⼯程名led,单击OK; 3).等待软件Create Block Design 4).Add IP.右边空⽩处⼀般会提⽰This design is empty. To get started, Add IP from the catalog,单击 Add IP会出现IP的⽬录,如果此处没有提⽰,可以单击Diagram左边框的Add IP添加; 5). 在⽬录Search中输⼊ZYNQ7 Processing System; 6).双击ZYNQ7 Processing System完成IP核的添加; 7).等待软件Add IP,接下来⼯程窗上部分会出现Run Block Automation,点Run Block Automation,直接点OK。

DDR读写流程的步骤和流程DDR(Double Data Rate)是一种常见的内存接口技术,广泛应用于计算机系统和嵌入式系统中。

DDR读写流程是指在DDR存储器中进行数据读取和写入的过程。

本文将详细描述DDR读写流程的步骤和流程。

1. DDR基本概念首先,我们需要了解一些DDR的基本概念。

1.1 数据总线数据总线是指在计算机系统中用于传输数据的一组并行线路。

在DDR中,数据总线通常有32位或64位宽度。

1.2 控制总线控制总线是指用于传输控制信号的一组线路。

在DDR中,控制总线包括地址信号、命令信号、时钟信号等。

1.3 内存芯片内存芯片是指存储数据的集成电路芯片,例如SDRAM(Synchronous Dynamic Random Access Memory)芯片。

1.4 预充电(Precharge)预充电是指将内存芯片上的所有位线拉高至高电平状态。

1.5 访问周期(Access Cycle)访问周期是指完成一次读取或写入操作所需的时间。

2. DDR读写流程下面我们将详细描述DDR读写流程的步骤和流程。

2.1 初始化在进行DDR读写操作之前,需要进行初始化设置。

初始化包括以下几个步骤:1.设置控制总线的时钟频率和数据总线的宽度。

2.设置预充电命令,将内存芯片上的所有位线拉高至高电平状态。

3.配置读写模式,包括读取延迟、写入延迟等参数。

2.2 读取数据DDR读取数据的流程如下:1.发送读命令:通过控制总线发送一个读命令给内存芯片,包括要访问的地址信息。

2.检测预充电:检测内存芯片上是否已经进行了预充电操作。

如果没有,则需要先进行预充电操作。

3.发送地址:通过控制总线发送要访问的地址信息给内存芯片。

4.接收数据:等待一段时间后,从数据总线上接收到所需的数据。

2.3 写入数据DDR写入数据的流程如下:1.发送写命令:通过控制总线发送一个写命令给内存芯片,包括要访问的地址信息和要写入的数据。

2.检测预充电:检测内存芯片上是否已经进行了预充电操作。

ddr读写流程

DDR读写流程如下:

1. 发送写请求:首先,CPU向DDR控制器发送写请求,指定要写入的地址和数据。

2. 控制器检查:DDR控制器接收到写请求后,首先检查地址是否有效,然后将写请求发送到DDR存储芯片。

3. 地址解码和行预充电:DDR存储芯片中的地址解码器解码接收到的写请求地址,并确定要进行写操作的行地址。

然后,在这个行地址上进行预充电操作。

4. 列选择和写入数据:接下来,地址解码器根据写请求中指定的列地址选择要写入的存储单元。

然后,DDR存储芯片将CPU提供的数据写入已选择的存储单元中。

5. 数据刷新:在写入数据之后,DDR存储芯片为了维持数据的可靠性和稳定性,需要进行定期的数据刷新操作,防止数据丢失。

DDR读取流程如下:

1. 发送读请求:CPU向DDR控制器发送读请求,指定要读取的地址。

2. 控制器检查:DDR控制器接收到读请求后,首先检查地址

是否有效,然后将读请求发送到DDR存储芯片。

3. 地址解码和行预充电:DDR存储芯片中的地址解码器解码接收到的读请求地址,并确定要进行读操作的行地址。

然后,在这个行地址上进行预充电操作。

4. 列选择和数据输出:地址解码器根据读请求中指定的列地址选择要读取的存储单元,并将存储单元中的数据输出给DDR 存储芯片的输出缓冲区。

5. 数据传输:DDR存储芯片将输出缓冲区中的数据传输到DDR控制器。

6. 数据传输给CPU:最后,DDR控制器将传输来的数据传输给CPU,完成读取操作。

nexys4-DDR开发板数码管驱动-第⼆篇1. 有这个板⼦使⽤的是Artix-7系列的XC7A100T-1CSG324C芯⽚。

作为7系列中的⼀款FPGA,这个芯⽚的结构与Kintex-7和Virtex-7⼏乎⼀样。

也配备了XADC。

在Artix-7系列中,100T和200T与其它芯⽚不同,这两款是ISE与Vivado同时⽀持的芯⽚,⽽更⼩的35T,50T和75T,ISE的⽀持会相对差⼀些。

从这个⾓度说,100T的可玩性⽐较⼤。

这也是Nexys-4⽐Avnet Artix-5 50T板⼦要好⼀些的地⽅。

2. 打算⽤数码管驱动测试⼀下。

打开vivado2014.2软件,创建⼯程3. 增加⽂件,shumaguan.v,代码⽐较简单。

1 `timescale 1ns / 1ps2 module shumaguan(seg,dig,clock,);3 input clock;4 output [7:0] seg; //数码管段码输出5 output [3:0] dig; //数码管位码输出6 reg [7:0] seg; //数码管段码输出寄存器7 reg [3:0] dig; //数码管位码输出寄存器8 reg [3:0] disp_dat; //显⽰数据寄存器9 reg [36:0] count; //定义计数寄存器10 always @ (posedge clock )11 begin12 count = count + 1'b1;13 dig= 8'b1110;//14 end15 always @ (count[24])16 begin17 disp_dat = {count[28:25]};18 end19 always @ (disp_dat)20 begin case (disp_dat)214'h0 : seg = 8'hc0; //显⽰"0"224'h1 : seg = 8'hf9; //显⽰"1"234'h2 : seg = 8'ha4; //显⽰"2"244'h3 : seg = 8'hb0; //显⽰"3"254'h4 : seg = 8'h99; //显⽰"4"264'h5 : seg = 8'h92; //显⽰"5"274'h6 : seg = 8'h82; //显⽰"6"284'h7 : seg = 8'hf8; //显⽰"7"294'h8 : seg = 8'h80; //显⽰"8"304'h9 : seg = 8'h90; //显⽰"9"314'ha : seg = 8'h88; //显⽰"a"324'hb : seg = 8'h83; //显⽰"b"334'hc : seg = 8'hc6; //显⽰"c"344'hd : seg = 8'ha1; //显⽰"d"354'he : seg = 8'h86; //显⽰"e"364'hf : seg = 8'h8e; //显⽰"f"37 endcase38 end39 endmodule4. 先点击Simulation功能仿真,然后Synthesis综合,综合完之后,在Implementation下⾯Implemented Design会从灰⾊切换到可点击状态。

ddr读写工作原理嗨,朋友!今天咱们来唠唠DDR(双倍数据率同步动态随机存取存储器)读写工作原理,这听起来有点高大上,其实可有趣啦。

咱们先说说DDR是个啥。

你可以把DDR想象成一个超级大的仓库,这个仓库呢,是专门用来存放计算机里的数据的。

比如说,你在电脑上打开一个文档,这个文档的数据就可能在DDR这个大仓库里找个小格子住下啦。

那它怎么读数据呢?这就像是在仓库里找东西。

DDR里面有好多好多的存储单元,就像一个个小盒子。

当计算机要读取数据的时候,它就像一个小快递员,会发送一个地址信号。

这个地址信号就像是小快递员手里的地址标签,告诉DDR:“我要去那个小盒子里拿东西。

”然后呢,DDR就根据这个地址,迅速地找到对应的存储单元,把里面的数据拿出来,再通过电路发送给计算机的其他部分。

这就像是小快递员把找到的包裹送到收件人手里一样。

而且啊,DDR很聪明,它能够以双倍的数据率来工作呢。

就好比普通的快递员一次只能送一个包裹,DDR这个超级快递员一次能送两个包裹,速度可快啦。

再来说说写数据。

这就像是往仓库里放东西。

计算机有了新的数据,就会告诉DDR:“我这儿有个新包裹,你得找个地方给我放好呀。

”计算机同样会发送地址信号,告诉DDR把数据放在哪个小盒子里。

DDR收到信号后,就会把数据存到指定的存储单元里。

这个过程也很快哦,就像你把东西快速地放到仓库的架子上一样。

不过呢,DDR在做这些读写操作的时候,可不是随随便便的。

它得按照一定的时钟信号来工作。

这个时钟信号就像是一个指挥家,滴答滴答地打着节拍。

DDR就跟着这个节拍来进行数据的读写。

如果节拍乱了,那可就糟糕啦,就像乐队里的乐手不跟着指挥的节奏演奏,那曲子就乱套了。

而且呀,DDR还有个很神奇的地方。

它里面的数据不是一直待在那儿不动的,因为它是动态随机存取存储器嘛。

这意味着数据会像调皮的小精灵一样,时不时地需要刷新一下,就像你要时不时地整理一下仓库,把东西摆放整齐。

如果不刷新,数据可能就会变得乱七八糟,就像仓库里的东西乱成一团,到时候计算机要找数据就找不到啦。

pl读写psddr例程PL读写PSDDR例程PL(Programmable Logic)是可编程逻辑器件,它可以通过编程实现各种逻辑电路的功能。

而PSDDR(Processor System DDR)是处理器系统中的一种内存类型。

在FPGA(Field Programmable Gate Array)中,PL和PSDDR可以通过AXI总线进行通信。

本文将介绍如何在Vivado中编写PL读写PSDDR的例程。

1. 创建工程首先,打开Vivado软件,创建一个新的工程。

选择“RTL Project”,输入工程名称和路径,选择FPGA型号,点击“Next”。

2. 添加IP核在工程中添加AXI Interconnect IP核和AXI GPIO IP核。

AXI Interconnect IP核用于连接PL和PSDDR,AXI GPIO IP核用于控制LED灯的亮灭。

添加完毕后,连接两个IP核,如下图所示。

3. 编写Verilog代码在工程中添加一个Verilog文件,命名为“pl_psddr.v”。

在该文件中,定义一个模块,包含一个输入端口和一个输出端口。

输入端口连接AXI GPIO IP核,输出端口连接AXI Interconnect IP核。

在模块中,使用Verilog语言编写读写PSDDR的代码,如下所示。

```verilogmodule pl_psddr(input wire [7:0] gpio,output wire [31:0] psddr);reg [31:0] data;always @(*) begincase(gpio)8'h00: data = 32'h00000000;8'h01: data = 32'h11111111;8'h02: data = 32'h22222222;8'h03: data = 32'h33333333;8'h04: data = 32'h44444444;8'h05: data = 32'h55555555;8'h06: data = 32'h66666666;8'h07: data = 32'h77777777;default: data = 32'h00000000;endcaseendassign psddr = data;endmodule```在上述代码中,输入端口gpio是一个8位的信号,用于控制PSDDR 中存储的数据。

使用Vivado 2015.4在Nexys4 DDR开发板上实现DDR的读写例程最近项目需要用到DDR,于是在网上找相关资料,发现网上关于Xilinx DDR 的资料不多,而且比较老,官方文档又是纯英文,且超级长。

所以笔者写了这篇文章,为像笔者一样的初学者介绍一下DDR的使用。

在此不介绍DDR是什么了,请自行查资料。

(相信用到这篇文章的人不会不知道DDR是啥吧。

)

好了,闲话休提言归正传。

本文使用Vivado 2015.4在Nexys4 DDR(以下简称N4DDR)开发板上实现DDR的读写。

FPGA如果需要对DDR进行读写,则需要一个DDR的控制器。

根据官方的文档(UG586,下载链接在文末),DDR控制器的时序主要有三:

(1)首先是控制信号,如下图:

从上图可以看出,只有当app_rdy信号有效时,程序所发出的读写命令才会被控制器接收。

这点必须注意。

(2)然后是写操作时序,如下图:

由图可知,在向DDR写数据时,需要提供写命令app_cmd、地址app_addr、数据app_wdf_data等信号,且写入的数据最多可以比app_cmd提前一个时钟周期有效,最迟可以比app_cmd晚两个时钟周期有效。

【特别注意】在写数据的时候必须检测app_rdy和app_wdf_rdy信号是否同时有效,否则写入命令无法成功写入到DDR控制器的命令FIFO中,从而导致写操作失败。

(3)最后是读操作时序,如下图所示:

读操作的时序比较简单,只需要注意app_rdy是否有效即可,其余不再赘述。

Xilinx在Vivado中提供的Memory Interface Generator的IP核就是我们需要的DDR控制器,。