微电子器件课后答案(第三版)

- 格式:ppt

- 大小:919.50 KB

- 文档页数:42

微电子器件_电子科技大学中国大学mooc课后章节答案期末考试题库2023年1.线性缓变结的耗尽层宽度正比于【图片】。

参考答案:正确2.反向偏置饱和电流可看成是由中性区内少数载流子的产生而导致的。

参考答案:正确3.减薄p+n突变结的轻掺杂区厚度,不但能减少存储电荷,还能降低反向抽取电流。

参考答案:错误4.在异质结双极型晶体管中,通常用()。

参考答案:宽禁带材料制作发射区,用窄禁带材料制作基区5.( )的集电结反向电压VCB称为共基极集电结雪崩击穿电压,记为BVCBO。

参考答案:发射极开路时,使6.【图片】对高频小信号注入效率的影响的物理意义是,【图片】的存在意味着【图片】必须先付出对势垒区充放电的多子电流【图片】后,才能建立起一定的【图片】。

这一过程需要的时间是()。

参考答案:发射结势垒电容充放电时间常数7.某长方形扩散区的方块电阻为200Ω,长度和宽度分别为100μm和20μm,则其长度方向的电阻为()。

参考答案:1KW8.要提高均匀基区晶体管的电流放大系数的方法()。

参考答案:减小基区掺杂浓度_减小基区宽度9.防止基区穿通的措施是提高()。

参考答案:增大基区宽度_增大基区掺杂浓度10.从发射结注入基区的少子,由于渡越基区需要时间tb ,将对输运过程产生三方面的影响( )。

参考答案:时间延迟使相位滞后_渡越时间的分散使减小_复合损失使小于111.晶体管的共发射极输出特性是指以输入端电流【图片】作参量,输出端电流【图片】与输出端电压【图片】之间的关系。

参考答案:正确12.电流放大系数与频率成反比,频率每提高一倍,电流放大系数下降一半,功率增益降为四分之一。

参考答案:正确13.特征频率【图片】代表的是共发射极接法的晶体管有电流放大能力的频率极限,而最高振荡频率【图片】则代表晶体管有功率放大能力的频率极限。

参考答案:正确14.模拟电路中的晶体管主要工作在()区。

参考答案:放大15.共发射极电路中,基极电流IB是输入电流,集电极电流IC是输出电流。

第一章习题答案1.1 写出题图中有源支路的电压,电流关系式。

(a) (b) (c) (d) 题图在题图中已知U 2=2V , (1) 求 I,U 1,U 3,U 4,U ac ,(2) 比较a,b,c,d,e 各点电位的高低。

题图在题图所示电路中U ab题图 求题图所示电路电压+a2V Ω + a+ 2Ω 2Ω 2Ω 2Ωa b c d e3V 22V24VΩΩ题多量程直流电流表如题图所示,计算0-1,0-2及0-3各端点的等效电阻,即各挡的电流表内阻,已知表头等效电阻R A =15k Ω,各分流电阻R 1=100Ω,R 2=400Ω,R 3=500Ω。

题图 两个额定值是110V,40W 的灯泡能否串联后接到220V 的电源上使用如果两个灯泡的额定电压相同,都是110V ,而额定功率一个是40W ,另一个是100W,问能否把这两个灯泡串联后接在200V 电源上使用,为什么电路如题图所示.试问ab 支路是否有电压和电流题图题图中若(1)U=10V, I=2A, (2)U=10V,I=-2A 。

试问哪个元件是吸收功率哪个元件是输出功率为什么题图1. 计算题图所示各电路的等效电阻.1 23U UUU +++ + - -- -(c)(a) (b) (d)1. 电路如题图所示,试求以下电路的电压U 和电流I 。

(c) (d)在指定的电压u 和电流i 参考方向下,写出图所示各元件u 和i 的约束方程.(a) (b) (c)(d) (e)1A 20Ω+ 30V U-U 30V + -u - + - u 10μF u -+U5V +-U + -求题图所示电路中的U 1和U 2.题图求题图中所示电路化成等值电流源电路。

(a) (b) (c) 题图求题图中所示电路化成等值电压源电路。

(a(b)题图求题图所示电路的电流I 和电压U 。

4V1A2V 1A6V6V3A( a) (b) 题图求题图所示各电流源输出的功率。

题图求题图所示各电路源输出的功率。

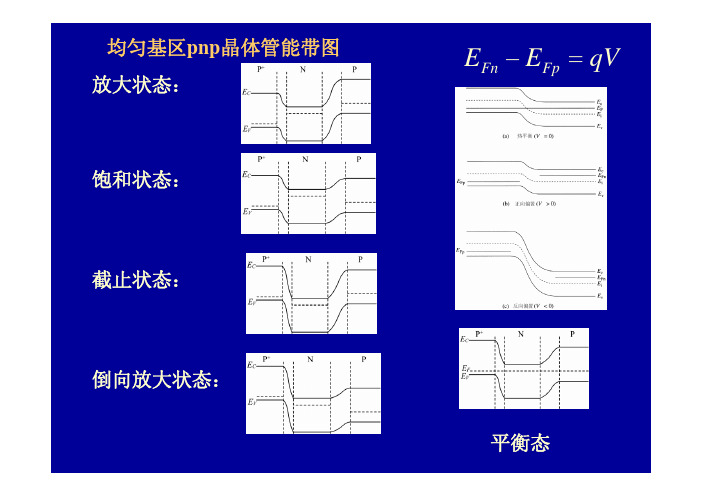

均匀基区pnp晶体管能带图 放大状态:EFn − EFp = qV饱和状态:截止状态:倒向放大状态: 平衡态均匀基区pnp晶体管的各边界上少子浓度⎛ qVEB ⎞ nE = nE0 exp ⎜ ⎟ kT ⎝ ⎠E Emitter P⎛ qVEB ⎞ pB = pB0 exp ⎜ ⎟ ⎝ kT ⎠Base N Collector P CnE = nE0BnC = nC0⎛ qVCB ⎞ pB = pB0 exp ⎜ ⎟ ⎝ kT ⎠⎛ qVCB ⎞ nC = nC0 exp ⎜ ⎟ ⎝ kT ⎠均匀基区pnp晶体管的少子分布图: 放大状态:饱和状态:截止状态:倒向放大状态:忽略势垒区产生复合电流, 处于放大状态的晶体管内部的 各电流成分如下图所示:I pEI pCI prI nEI nrI ncI E = I pE + I nE , I B = I nE + I nr − I nc ≈ I nE + I nr , I C = I pc + I nc ≈ I pC = I pE − I pr = I E − I nE − I nrI pEI pCI prI nEI nr从 IE 到 IC ,发生了两部分亏损(PNP): InE 与 In r 。

要减小 InE ,就应使NE >> NB ; 要减小In r ,就应使WB << LB 。

§ 3-2 均匀基区晶体管的放大系数均匀基区晶体管:基区掺杂为均匀分布。

少子在基区中主 要作扩散运动,又称为 扩散晶体管。

(本节以pnp为例)均匀基区晶体管(理想晶体管)• 发射区、基区、集电区均匀非简并掺杂,发射结与集 电结为突变结; • 晶体管在一维稳态条件下工作; • 中性区满足小注入水平; • 发射结与集电结的耗尽区内复合-产生可以忽略不 计; • 发射区与集电区的中性区宽度远大于少子扩散长度, 而基区的中性区宽度则远小于少子扩散长度。

均匀基区相关知识点I pEI pCI prI nEI nr相关公式β∗W B2 τb =1− =1− 2 2 LB τBD EW B N B WBρE γ = 1− D W N = 1− W ρ B E E E B⎛ W B2 α =⎜ ⎜1 − 2 L2 B ⎝2 B 2 BR口E = 1− R口B1⎞⎛ R口E ⎞ W B2 R口E ⎟ ⎟⎜ ⎟ ≈ 1 − 2 L2 − R ⎜1 − R ⎟ 口 B1 ⎠ B 口 B1 ⎠⎝⎛W R口E ⎜ β ≈⎜ + R口B1 ⎝ 2L⎞ ⎟ ⎟ ⎠−1§3-3 缓变基区晶体管的放大系数以NPN 管为例,结电压为 VBE 与 VBC 。

现代晶体管,如双扩散外延平面管 属缓变基区晶体管,由于载流子在 基区主要是以漂移运动在传输,故 它又称为 漂移晶体管。

N+0PN杂质浓度分布图:x jE x jCWB = x jC − x jEN E ( x) N B ( x)NC0x jE x jCx1、基区内建电场的形成与求解 形成的物理机理(以P型基区的Xmb-Xjc段为例)xjE 和xjC为发射结 和集电结结深, xmB为杂质补偿后 基区净杂质浓度 的极值位置杂质浓度高的地方留下不 可移动的电离杂质电荷 (NA-),杂质浓度低的地 方积累多子(空穴)杂质(NA) 浓度梯度杂质电离多子(空 穴) 浓度梯度多子(空 穴) 扩散正负电荷 分离内建电场内建电场的作用 漂移晶体管电场方向:指向发射结 加速场 电场作用: 基区的少子(电子) 向集电结方向漂移运 动,对少子有加速作用 向发射结方向漂移运动, 抵消多子扩散运动 多子电流等于零基区的多子(空穴)xjE到xmB段,将产生一个与EB方向相反的自建电场EB’,它将阻止 基区中少子(电子)流向集电结,称阻滞电场,该部分基区称阻 滞区。

一般情况下,相对与整个基区而言,阻滞区很窄,一般可以忽略。

请从以下几方面总结半导体器件中的内建电场① 掺杂不均匀产生的内建电场 ~ 产生机理? 对多数载流子运动的影响? 对少数载流子运动的影响? ② 大注入产生的内建电场 ~ 产生机理? 对多数载流子运动的影响? 对少数载流子运动的影响 ? ③ p-n结中的内建电场 ~ 产生机理? 势垒区(阻挡层)→阻挡多数载流子还是阻挡少数载流子? 耗尽层近似?→ 耗尽什么种类的载流子?三个内建电场形成机理的比较内建电场种类形成原因 P区与N区刚接触 时冶金结两边存 在自由载流子浓 度差 大注入时中性区 多子具有浓度梯 度分布电荷分离的表现形式 冶金结两边自由载流子扩散,留下不 可移动的电离施主和受主杂质电荷在 空间上分离 多子与少子同时扩散,但由于多子扩 散得不到补充,最终使得靠近耗尽区 少子浓度高于多子浓度,远离耗尽区 边界少子浓度低于多子浓度,最终多 子与少子电荷在空间上分离 多子浓度扩散,使得靠近发射结耗尽 区的电离杂质电荷高于多子,靠近集 电结耗尽区的电离杂质电荷低于多 子,造成电离杂质电荷与多子电荷在 空间上分离作用 载流子的扩散运 动等于漂移运动PN结空间电 荷区内建电 场 大注入PN结 中性区中的 内建电场 (自建场) 缓变基区BJT 中基区内建 电场多子的扩散运动 与漂移运动抵 消,加强少子扩 散运动 多子的扩散运动与 漂移运动抵消,少 子在基区以漂移运 动为主掺杂原子具有浓 度梯度,多子具 有相同的浓度梯 度分布基区内建电场表达式的推导 设基区杂质浓度分布为:NB (0)NB (x)⎛ ηx ⎞ N B ( x ) = N B ( 0 ) exp ⎜ ⎜− W ⎟ ⎟ B ⎠ ⎝ 式中 η 是表征基区内杂质变化程度的一个参数:NB (WB )0WBxN B (W B ) = N B ( 0 ) exp (− η )N B (0) η = ln N B (W B )当 η = 0 时为均匀基区。

第一章1-1 EDA技术与ASIC设计和FPGA开发有什么关系? P3~4 答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD 通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD的应用是EDA 技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

1-2与软件描述语言相比,VHDL有什么特点? P6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

综合在电子设计自动化中的地位是什么?答:是核心地位(见图1-3)。

双基极条:Se Sb C d rbb′ = R口B1 + R口B 2 + R口B 3 + Ω 12l 2l 6l 2lS b圆环行基极:rbb′dB 4C Ω 1 1 = R口 B 1 + ln R口 B 2 + 2 8π 2π S e π ( d S2 − d B )降低 rbb’ 的措施: (1)减小 R口B1 与 R口B2 ,即增大基区掺杂与结深, 但这 会降低 β ,降低发射结击穿电压与提高发射结势垒电容。

(2)无源基区重掺杂, 以减小 R口B3 和 CΩ 。

(3)减小 Se 、Sb 与 d ,增长 L , 即采用细线条,并增加 基极条的数目, 但这受光刻工艺水平和成品率的限制。

§3-7 电流放大系数与频率的关系随着频率的增加, BJT的电流放大系数会怎么变化? 为什么?β3dBα = 20lg α ( dB )6分贝/ 倍频电流放大系数( dB) 0β02αβ =1α023dBfβfT fαf课堂练习如果忽略两个空间电荷区的复合产生电流,说 明直流电流在晶体管内部的传输过程中有哪些 电流损失?直流电流在BJT中的传输过程(NPN)• 发射极电流由发射结注入到基区,通过基区输运到集电 结,被集电结收集形成集电极输出电流 • 发射极电流传输过程的电流损失(对理想情况):1.与 发射结反向注入电流的在发射区复合;2.输运到基区的 少子电流与基极多子电流在基区的复合。

下面定性分析交流电流在晶体管内部的传输过程损失请画出二极管的交流等效电路图P区NApp0 NAND+N区ND+ nn0课堂练习请说明工作于正偏模式BJT 时存在的电容工作于正偏模式BJT 中的电容 发射结扩散电容:CDeN P集电结扩散电容:CDcN发射结势垒电容:CTe集电结势垒电容:CTc一、高频小信号电流在晶体管中的传输过程(NPN)直流情况下的两种损耗仍然存在发射过程当发射极输入一交变信号时,交变信号将叠加在直流上作用 于发射结上,发射结的空间电荷区宽度将随着信号电压的变 化而改变,因此需要一部分电子电流对CTe进行充放电。

《微电子器件》题集一、选择题(每题2分,共20分)1.下列哪种材料常用于制造微电子器件中的晶体管?A. 硅(Si)B. 铜(Cu)C. 铝(Al)D. 铁(Fe)2.在CMOS逻辑电路中,哪种类型的逻辑门在输入为高电平时导通?A. NAND门B. NOR门C. AND门D. OR门3.以下哪个参数描述的是二极管的电流放大能力?A. 击穿电压B. 反向电流C. 电流放大系数D. 截止频率4.在集成电路制造中,哪种工艺步骤用于定义晶体管和其他元件的几何形状?A. 氧化B. 扩散C. 光刻D. 金属化5.MOSFET器件中,栅极电压对沟道电流的控制是通过什么机制实现的?A. 欧姆定律B. 量子隧穿效应C. 电场效应D. 热电子发射6.下列哪项技术用于减小集成电路中的寄生电容和电阻?A. SOI技术B. BICMOS技术C. CMOS技术D. TTL技术7.在半导体存储器中,DRAM与SRAM相比,主要缺点是什么?A. 成本高B. 速度慢C. 需要定期刷新D. 功耗高8.下列哪种类型的二极管常用于微波电子器件中?A. 肖特基二极管B. 光电二极管C. 变容二极管D. 整流二极管9.集成电路的特征尺寸越小,通常意味着什么?A. 集成度越低B. 性能越差C. 功耗越高D. 制造成本越高10.在半导体工艺中,哪种掺杂技术用于形成P-N结?A. 离子注入B. 扩散C. 外延生长D. 氧化二、填空题(每空2分,共20分)1.在CMOS逻辑电路中,当输入信号为低电平时,PMOS晶体管处于______状态,而NMOS晶体管处于______状态。

2.二极管的正向电压超过一定值时,电流会急剧增加,这个电压值称为二极管的______电压。

3.在集成电路制造中,______步骤用于形成晶体管的栅极、源极和漏极。

4.MOSFET器件的沟道长度减小会导致______效应增强,从而影响器件的性能。

5.DRAM存储单元由一个晶体管和一个______组成。