系统集成电路大作业

- 格式:docx

- 大小:428.97 KB

- 文档页数:25

返回继续教育系统首页我的课程服务指南集成电路专题讲座总分:100及格分数:60考试剩余时间:1时56分37秒单选题(共7题,每题5分)2、现阶段已商业化的SiC产品主要集中在()电压等级,3300V以上电压等级器件尚处于工程样品阶段。

A、650V-4700VC、650V-2700VD、650V-1700VD6、MCU芯片是()。

A、驱动类芯片C、计算类芯片D、电源类芯片B7、砷化镓的器件的缺点是功率较低,低于()。

A、50WC、150WD、200WA判断题(共7题,每题5分)1、1963年,日本电气股份有限公司(NEC)获得了仙童半导体公司的技术授权。

正确2、FPGA设计完成后,无法改动硬件资源,灵活性受限。

错误3、传统存储器通过结构优化、材料升级等也可形成新型存储器。

正确4、目前最先进的SOC设计还远远未达到制造工艺和材料物理属性的极限限制。

错误5、1989-1992年,日本超越美国,成为全球最大的半导体生产国。

正确6、未来5年将是第三代半导体产业发展的关键期,全球资本加速进入第三代半导体材料、器件领域,产能大幅度提升,企业并购频发,正处于产业爆发前的“抢跑”阶段。

正确7、异构集成是指将单独制造的组件集成到更高级别组装,总体上提供更强的功耗和改进的操作特征。

交卷返回继续教育系统首页我的课程服务指南集成电路专题讲座总分:100及格分数:60考试结果相关信息:未合格,您的总分为:30单选题(共7题,每题5分)3、连接芯片设计工作和IT基础架构的重要环节是?()答案:C、EDA技术支持正确答案:B、CAD服务4、SRAM的响应通常可以做到()级别。

答案:D、毫秒正确答案:B、纳秒5、()是数字经济最有价值的资源,作为数字经济全新的、关键的生产要素,贯穿于数字经济发展的全部流程,将引发生产要素多领域、多维度、系统性的突破。

答案:A、算力正确答案:B、数据1、()是全球MEMS行业最大的一个应用领域。

答案:A、工业正确答案:D、消费电子多选题(共6题,每题5分)1、碳化硅下游主要应用场景有()。

一、简答题1、列出三个及以上世界知名EDA公司的名称、主要芯片产品以及配套软件。

答:(1)Xilinx公司(FPGA的发明者)。

产品主要有:7系列All Programmable FPGA产品(Artix-7、Kintex-7等)、6系列FPGA (Vertex-6)、 XC9500/4000、Coolrunner(XPLA3)、Xilinx All Programmable SoC、CPLD等,其最大的Vertex—II Pro器件已达到800万门。

开发软件为Foundation和ISE。

欧洲多用Xilinx 公司产品,中国和亚太地区用ALTERA的人多,美国则是平分秋色。

全球PLD/FPGA产品60%以上是由Altera 和Xilinx提供的。

(2)Altera公司。

主要产品有:可编程系统级芯片 (SOPC) 、FPGA、CPLD(MAX3000/7000/9000/II等系列)、Cylone、APEX20K、ACEX、Stratix等。

配套软件:可编程逻辑技术与软件工具,其开发工具—MAX+PLUS II是较成功的PLD开发平台,最新又推出了Quartus II开发软件。

Altera公司提供较多形式的设计输入手段,绑定第三方VHDL综合工具,如:综合软件FPGA Express、Leonard Spectrum,仿真软件ModelSim。

(3)Latticee公司,是ISP(In—System Programmability)技术的发明者,ISP技术极大地促进了PLD 产品的发展。

与ALTERA和XILINX相比,其开发工具比Altera和Xilinx略逊一筹。

中小规模PLD比较有特色,大规模PLD、FPGA的竞争力还不够强,2019年推出可编程模拟器件,99年收购Vantis(原AMD子公司),成为第三大可编程逻辑器件供应商。

2019年12月收购Agere公司(原Lucent微电子部)的FPGA 部门。

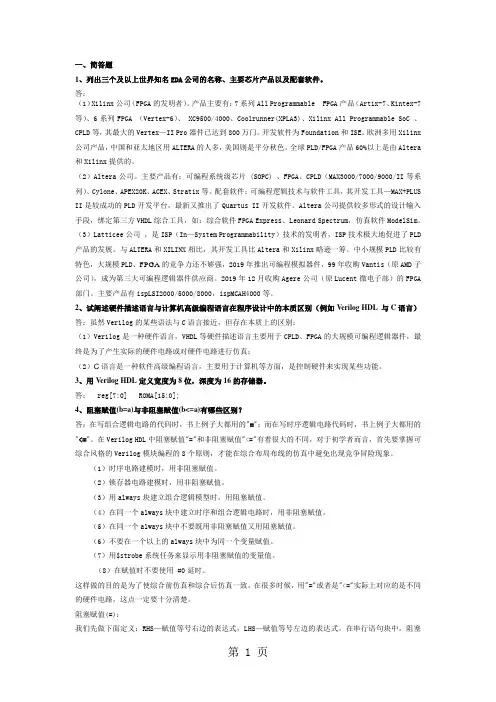

实验一:(1)分频:将八分频更改为二分频和四分频在源程序中,将#0t_data_in=4'b0000;#3000t_data_in=4'b1000;,分别改为#0t_data_in=4'b0000;#3000t_data_in=4'b1100;和#0t_data_in=4'b0000;#3000t_data_in=4'b1110;即可得到四分频和二分频图像。

四分频二分频(2)反序:改变电路使彩灯变成逆时针旋转方式:源程序改动将源程序4'b0000:lamp=16'b0000_0000_0000_0001;4'b0001:lamp=16'b0000_0000_0000_0010;4'b0010:lamp=16'b0000_0000_0000_0100;4'b0011:lamp=16'b0000_0000_0000_1000;4'b0100:lamp=16'b0000_0000_0001_0000;4'b0101:lamp=16'b0000_0000_0010_0000;4'b0110:lamp=16'b0000_0000_0100_0000;4'b0111:lamp=16'b0000_0000_1000_0000;4'b1000:lamp=16'b0000_0001_0000_0000;4'b1001:lamp=16'b0000_0010_0000_0000;4'b1010:lamp=16'b0000_0100_0000_0000;4'b1011:lamp=16'b0000_1000_0000_0000;4'b1100:lamp=16'b0001_0000_0000_0000;4'b1101:lamp=16'b0010_0000_0000_0000;4'b1110:lamp=16'b0100_0000_0000_0000;4'b1111:lamp=16'b1000_0000_0000_0000;default:lamp=16'b0000_0000_0000_0000;首尾相对应语句依次调换位置,即可得到新的源程序,执行后可观测到新的亮灯顺序为反序。

模拟CMOS集成电路设计大作业设计题:假定μn C ox =110 μA/V 2, μp C ox =50 μA/V 2 ,λn =0.04V -1, λp =0.04V -1(有效沟道长度为1μm 时),λn =0.02V -1, λp =0.02V -1(有效沟道长度为2μm 时),λn =0.01V -1, λp =0.01V -1(有效沟道长度为4μm 时),γ=0.2,V THN =| V THP | =0.7V 。

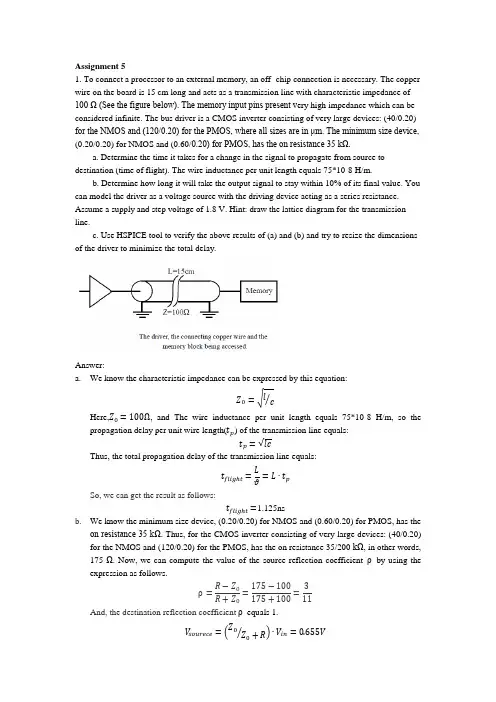

设计如下图的放大器,满足如下要求,其中负载电容C L = 5pF 。

A v > 5000V/V , VDD = 5V , GB ≥ 5MHz ,SR > 10V/µs ,60° 相位裕度, Vout 摆幅在0.5~4.5V 范围, ICMR 为1.5~4.5V , Pdis s ≤ 2mW1.请说明详细的设计过程,包括公式表达式(假定Cox = 0.35fF/µm 2,栅源电容按ox gs C L W C 33367.0=计算);2.给出进行交流仿真和瞬态仿真的spice 仿真的网表,并给出仿真波形和结果以及必要的讨论和说明。

3.如果要求A v至少提高为原来的2倍,其它要求不变,如何修改电路(注意讨论对其它性能参数的影响)?4.如果要求增益带宽积GB提高为原来的2倍,其它要求不变,如何修改电路(注意讨论对其它性能参数的影响)?注意事项:1.计算得到的极点频率为角频率。

2.尺寸最后应选取整数,工艺精度的限制。

3.尾电流增加,A v增加还是减小?一.设计过程:0. 确定正确的电路偏置,保证所有晶体管处于饱和区。

为保证良好的电流镜,并确保M4处于饱和区。

(Sx=Wx/Lx )由 I6=I7 得57462S S S S =1.根据需要的PM =60deg 求Cc (假定w z >10GB )c c L c 22.0>2.由已知的Cc 并根据转换速率的要求(或功耗要求)选择ISS (I5)的范围;3.由计算得到的电流偏置值(I5 /2),设计W3/L3( W4/L4 )满足上ICMR(或输出摆幅)要求,即饱和区条件;4.验证M3处镜像极点是否大于10GB;5.设计W1/L1(W2/L2 )满足GB的要求;6.设计W5/L5满足下ICMR(或输出摆幅)要求;7.根据Wp2>2.2GB 计算得到gm6;并且根据偏置条件VSG4=VSG6计算得到M6的尺寸;8.根据尺寸和gm6计算I6,并验证Vout,max是否满足要求;9.计算M7的尺寸。

1+X集成电路理论习题库(附参考答案)一、单选题(共39题,每题1分,共39分)1.如果焊接面上有(),不能生成两种金属材料的合金层。

A、阻隔浸润的污垢B、氧化层C、没有充分融化的焊料D、以上都是正确答案:D2.激光打字在打标前需要调整()的位置。

A、场镜和收料架B、场镜和光具座C、显示器和收料架D、光具座和显示器正确答案:B3.进行芯片检测工艺中的编带外观检查时,其步骤正确的是()。

A、编带固定→固定卷盘→归纳放置→检查外观→编带回料B、归纳放置→固定卷盘→检查外观→编带回料→编带固定C、固定卷盘→归纳放置→检查外观→编带回料→编带固定D、检查外观→归纳放置→固定卷盘→编带回料→编带固定正确答案:B4.引线键合前一道工序是()。

A、第二道光检B、晶圆切割C、芯片粘接D、晶圆清洗正确答案:C答案解析:晶圆贴膜→晶圆切割→晶圆清洗→第二道光检→芯片粘接→引线键合5.下列关于平移式分选机描述错误的是()。

A、传送带将料架上层的料盘输送至待测区料盘放置的指定区域B、料盘输送到待测区的指定位置后,吸嘴从料盘上真空吸取芯片,然后转移至“中转站”C、等待芯片传输装置移动到“中转站”接收芯片并将芯片转移至测试区D、当待测区料盘上的芯片全部转移后,需要更换料盘,继续进行上料正确答案:A6.单晶硅生长完成后,需要进行质量检验,其中四探针法可以测量单晶硅的()参数。

A、少数载流子寿命B、电阻率C、导电类型D、直径正确答案:B7.利用全自动探针台进行扎针测试时,关于上片的步骤,下列所述正确的是()。

A、打开盖子→花篮放置→花篮下降→花篮到位→花篮固定→合上盖子B、打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子C、打开盖子→花篮放置→花篮下降→花篮固定→花篮到位→合上盖子D、打开盖子→花篮放置→花篮到位→花篮下降→花篮固定→合上盖子正确答案:B8.晶圆检测工艺中,在进行上片之前需要进行( )操作。

A、导片B、加温、扎针调试C、扎针测试D、打点正确答案:A答案解析:晶圆检测工艺流程:导片→上片→加温、扎针调试→扎针测试→打点→烘烤→外检→真空入库。

1+X集成电路理论模拟习题+参考答案一、单选题(共39题,每题1分,共39分)1.在刻蚀工艺中,有几个非常重要的参数,其中()定义为当刻蚀线条时,刻蚀的深度V 与一边的横向增加量ΔX 的比值V/ΔX,比值越大,说明横向刻蚀速率小,刻蚀图形的保真度好。

A、刻蚀因子B、刻蚀速率C、选择比D、均匀性正确答案:A2.风淋的作用是()。

A、清除进入车间的人或物体表面的灰尘B、检测进入车间人员的体重与生态状况C、降低人体衣物表面的温度D、使衣物保持洁净、平整正确答案:A答案解析:风淋的操作是针对芯片处于裸露状态工艺的车间设计的,其目的是为了清除进入车间的人或物体表面的灰尘,保证车间内的无尘环境不被破坏。

3.装片机上料区上料时,是将()的引线框架传送到进料槽。

A、最顶层B、任意位置C、中间层D、最底层正确答案:D4.请根据下列图片判断哪幅图片是合格针迹?()A、图片B、图片C、图片D、图片正确答案:A5.晶圆烘烤时,温度一般设置在( )℃。

A、110B、120C、130D、140正确答案:B答案解析:晶圆烘烤时,温度一般设置在120℃。

6.平移式分选机设备分选环节的流程是:( )。

A、分选→吸嘴吸取芯片→收料B、吸嘴吸取芯片→分选→收料C、吸嘴吸取芯片→收料→分选D、分选→收料→吸嘴吸取芯片正确答案:B答案解析:平移式分选机设备测试环节的流程是:吸嘴吸取芯片→分选→收料。

7.一般情况下,待编至( )颗时,需更换卷盘,并在完成编带的卷盘上贴上小标签,便于后期识别。

A、2000B、4000C、6000D、8000正确答案:B答案解析:一般情况下,待编至4000颗左右时,需要更换卷盘,即一盘编带一般装有4000颗的芯片。

8.先进的平坦化技术有 ()。

A、反刻法B、高温回流法C、旋涂玻璃法D、化学机械抛光法正确答案:D答案解析:反刻法、高温回流法、旋涂玻璃法属于传统平坦化技术,化学机械抛光法属于先进平坦化技术。

9.下列有关平移式分选机描述错误的是()。

郭小明2011060100010 大规模集成电路一二章作业第一章作业1、集成电路是哪一年有谁发明的?答:1958年的Texas Instruments(美国德州仪器)公司的Jack Kilby 发明的,基于锗材料采用单管互连方法制作了一个简单的振荡器,可以使认为第一块雏形集成电路,1959年申请小型化电子电路的专利,并于2000年获得诺贝尔物理学奖。

2、诺伊斯对集成电路的主要贡献是什么?答:1959年提出的发明平面工艺技术和PN结隔离技术奠定了半导体集成电路的基础,美国仙童公司的Robert Noyce结合其同事Jean Hoerni发明的刻蚀氧化工艺,在电路上淀积金属薄层进行电路连接,使得复杂集成电路成为可能,并在1959年突出平面型晶体管之后,1961年推出用平面工艺制造出的第一块双极型集成电路,从此旋开了集成电路的新篇章。

1968年7月,Robert Noyce和Gordon Moore,离开Fairchild公司,建立Intel。

2000年,Jack Kilby,Robert Noyce获得Nobel物理奖。

3、MOS场效应管是哪年出现的?1960年Jhon Atalla和Dawon Kahng发明了MOS场效应晶体管,1962年美国的RCA 公司研制出MOS场效应晶体管,并于1963年研制出第一块MOS集成电路。

4、集成电路的发展规律是由谁总结提出来的,具体规律是什么摩尔定律是由英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)提出来的。

其内容为:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

换言之,每一美元所能买到的电脑性能,将每隔18个月翻两倍以上。

这一定律揭示了信息技术进步的速度。

5、叙述集成电路的层次设计步骤层次化设计是大规模集成电路设计中最广泛使用的方法,可以简化设计的复杂性。

层次化设计分为自顶向下和自底向上两种方法。

1+X集成电路理论练习题库及参考答案一、单选题(共39题,每题1分,共39分)1.进行芯片检测工艺中的编带外观检查时,其步骤正确的是()。

A、检查外观→归纳放置→固定卷盘→编带回料→编带固定B、固定卷盘→归纳放置→检查外观→编带回料→编带固定C、编带固定→固定卷盘→归纳放置→检查外观→编带回料D、归纳放置→固定卷盘→检查外观→编带回料→编带固定正确答案:D2.()是指按照一定的方式将杂质掺入到半导体等材料中,改变材料电学性质,达到形成半导体器件的目的。

A、光刻B、掺杂C、刻蚀D、金属化正确答案:B答案解析:掺杂是指按照一定的方式将杂质掺入到半导体等材料中,改变材料电学性质,达到形成半导体器件的目的。

3.打点过程中,在显微镜下看到有墨点偏大出现时需要进行的操作是:( )。

A、调节打点器的旋钮B、调节打点的步进C、更换墨管D、更换晶圆正确答案:C答案解析:出现墨点大小点等情况时需更换墨管。

4.选择集成电路的关键因素主要包括()。

A、性能指标B、工作条件C、性价比D、以上都是正确答案:D5.平移式设备芯片检测工艺流程中,上料之后的环节是( )。

A、测试B、分选C、真空包装D、外观检查正确答案:A答案解析:平移式分选机设备芯片检测工艺的操作步骤一般为:上料→测试→分选→外观检查→真空包装。

6.()分选工序依靠主转盘执行,上料后主转盘旋转,每转动一格,都会将产品送到各个工位,每个工位对应不同的作用,包括上料位、光检位、旋转纠姿位、功能测试位等,从而实现芯片的测试与分选。

A、重力式分选机B、平移式分选机C、真空螺旋分选机D、转塔式分选机正确答案:D7.下列有关平移式分选机描述错误的是()。

A、平移式分选机是采用测压手臂下压的压测方式进行的B、通过入料梭移动将芯片从待测区“中转站”转移至测试区,等待测压手臂吸取芯片进行测试。

C、收料时,为了确保料盘能平稳地放入,需要将收料架上的料盘向下压紧D、测试机通过GPIB将测试结果反馈给分选机,在分选机的显示界面显示测试结果并记录正确答案:C8.封装工艺中,在晶圆切割后的光检中环节发现的不良废品,需要做()处理。

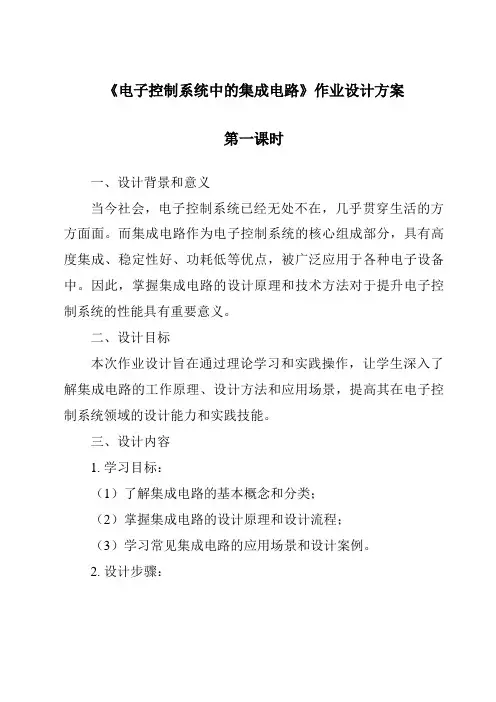

《电子控制系统中的集成电路》作业设计方案第一课时一、设计背景和意义当今社会,电子控制系统已经无处不在,几乎贯穿生活的方方面面。

而集成电路作为电子控制系统的核心组成部分,具有高度集成、稳定性好、功耗低等优点,被广泛应用于各种电子设备中。

因此,掌握集成电路的设计原理和技术方法对于提升电子控制系统的性能具有重要意义。

二、设计目标本次作业设计旨在通过理论学习和实践操作,让学生深入了解集成电路的工作原理、设计方法和应用场景,提高其在电子控制系统领域的设计能力和实践技能。

三、设计内容1. 学习目标:(1)了解集成电路的基本概念和分类;(2)掌握集成电路的设计原理和设计流程;(3)学习常见集成电路的应用场景和设计案例。

2. 设计步骤:(1)理论学习:通过课堂讲解、教材阅读和相关资料查阅,学习集成电路的基本概念、功能和工作原理,了解集成电路的分类和特点;(2)设计方案:根据所学知识,设计一个包含集成电路的电子控制系统方案,包括硬件组成、软件编程等内容;(3)实验操作:搭建电子控制系统的实验平台,进行集成电路的测试和调试,验证设计方案的可行性和稳定性;(4)数据分析:分析实验结果,总结经验教训,完善设计方案,提出改进建议;(5)报告撰写:撰写实验报告,总结设计过程和成果,展示实验成果和心得体会。

四、设计要求1. 设计思路清晰,操作规范,结果准确可靠;2. 实验数据真实可靠,结论合理有效;3. 设计报告内容完整,结构清晰,文字表达流畅;4. 鼓励创新设计,提倡合作交流,展示设计成果。

五、评分标准1. 设计方案:30%2. 实验操作:30%3. 数据分析:20%4. 报告撰写:20%六、参考资料1. 《集成电路设计与应用》2. 《电子控制系统原理与设计》3. 相关学术论文和资料七、总结通过本次作业设计,学生将能够深入了解集成电路的设计原理和应用,掌握电子控制系统的设计方法和实践技能,提升综合能力和动手能力,为将来从事电子工程领域的研究和实践奠定基础。

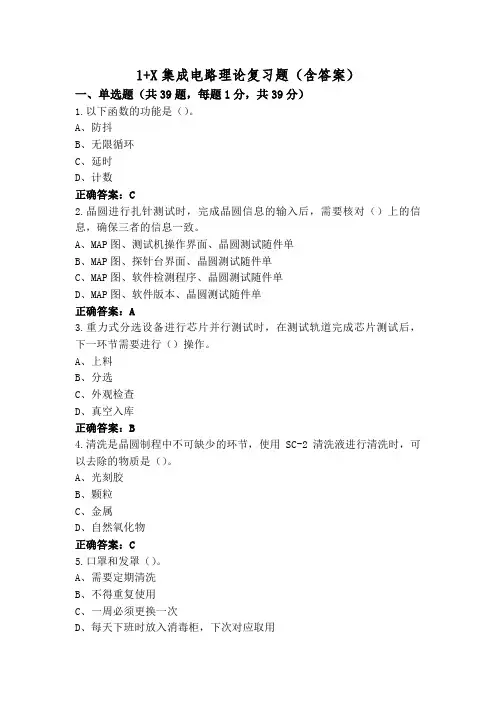

1+X集成电路理论复习题(含答案)一、单选题(共39题,每题1分,共39分)1.以下函数的功能是()。

A、防抖B、无限循环C、延时D、计数正确答案:C2.晶圆进行扎针测试时,完成晶圆信息的输入后,需要核对()上的信息,确保三者的信息一致。

A、MAP图、测试机操作界面、晶圆测试随件单B、MAP图、探针台界面、晶圆测试随件单C、MAP图、软件检测程序、晶圆测试随件单D、MAP图、软件版本、晶圆测试随件单正确答案:A3.重力式分选设备进行芯片并行测试时,在测试轨道完成芯片测试后,下一环节需要进行()操作。

A、上料B、分选C、外观检查D、真空入库正确答案:B4.清洗是晶圆制程中不可缺少的环节,使用SC-2清洗液进行清洗时,可以去除的物质是()。

A、光刻胶B、颗粒C、金属D、自然氧化物正确答案:C5.口罩和发罩()。

A、需要定期清洗B、不得重复使用C、一周必须更换一次D、每天下班时放入消毒柜,下次对应取用正确答案:B答案解析:口罩和发罩不得重复使用,每天需穿戴全新的口罩和发罩。

6.关于全自动探针台扎针调试的步骤,下列说法正确的是:()。

A、输入晶圆信息→调出检测MAP图→自动对焦→扎针调试B、输入晶圆信息→自动对焦→调出检测MAP图→扎针调试C、输入晶圆信息→自动对焦→扎针调试→调出检测MAP图D、输入晶圆信息→调出检测MAP图→扎针调试→自动对焦正确答案:B答案解析:全自动探针台扎针调试步骤:输入晶圆信息→自动对焦→调出检测MAP图→扎针调试。

7.( )可以实现探针测试卡的探针和晶圆的每个晶粒上的测试模块之间一一对应。

A、测试机B、探针台C、塑封机D、真空包装机正确答案:B答案解析:探针台可以实现探针测试卡的探针和晶圆的每个晶粒上的测试模块之间一一对应。

8.芯片检测工作流程()。

A、确定产品等级、研读Spe确定机械手、确定测试机、设计测试DUT、方案编程调试、批量验证B、确定产品等级、研读Spe确定机械手、设计测试DUT、确定测试机、方案编程调试、批量验证C、确定产品等级、方案编程调试、研读Spe确定测试机、确定机械手、设计测试DUT、批量验证D、确定产品等级、研读Spe确定测试机、确定机械手、设计测试DUT、方案编程调试、批量验证正确答案:D9.下列语句的含义是()。

北京城市学院信息学部2011-2012-2学期《网络工程设计与系统集成》课程大作业专业:(四号宋体居中,2倍行距,下同)班级:学生姓名:学号:年月目录第一章综述 (3)1.1网络设计背景分析 (3)1.2网络设计采用的方法和原则 (3)第二章用户需求分析 (4)2.1用户业务需求分析 (4)2.2网络性能需求分析 (4)第三章网络拓扑结构设计 (5)3.1网络拓扑结构 (5)3.2网络硬件结构 (5)3.3网络硬件结构 (5)第四章网络性能设计 (6)第五章网络可靠性设计 (7)第六章网络安全设计 (8)第七章网络物理设计 (9)7.1网络传输介质的选择 (9)7.2网络综合布线设计 (9)第八章课程设计总结与体会 (10)参考文献 (11)第一章综述1.1网络设计背景分析×××××××××(正文部分小4号宋体,20磅行距,每段开头左缩进两字)××××××××××××××××××…………[扼要介绍一下网络规划与设计的必要性,对进行网络设计的单位(例如某某学校或企业等)情况进行简单介绍,以使读者了解网络设计的背景信息]1.2网络设计采用的方法和原则×××××××××(正文部分小4号宋体,20磅行距,每段开头左缩进两字)××××××××××××××××××…………[扼要介绍一下本网络设计方案所采取的方法以及网络设计过程中所遵循的原则,所用知识点可参见教材第1章1.4节]第二章用户需求分析2.1用户业务需求分析×××××××××(正文部分小4号宋体,20磅行距,每段开头左缩进两字)××××××××××××××××××…………[对进行网络设计的用户的需求进行详细阐述,所用知识点可参见教材第2章]2.2网络性能需求分析×××××××××(正文部分小4号宋体,20磅行距,每段开头左缩进两字)××××××××××××××××××…………[将用户对网络性能的需求进行详细阐述,所用知识点可参见教材第2章]第三章网络拓扑结构设计3.1网络拓扑结构×××××××××(正文部分小4号宋体,20磅行距,每段开头左缩进两字)××××××××××××××××××…………[根据用户要求对网络拓扑结果进行描述,最好使用图表形式进行说明。

H a r b i n I n s t i t u t e o f T e c h n o l o g y模拟C M O S集成电路大作业设计题目:二级运放设计院系:班级:设计者:学号:设计时间:2011.6.20哈尔滨工业大学2012年设计题:假定μn C ox=110 μA/V2,μp C ox=50 μA/V2,λn=0.04V-1,λp=0.04V-1(有效沟道长度为1μm时),λn=0.02V-1,λp=0.02V-1(有效沟道长度为2μm时),λn=0.01V-1,λp=0.01V-1(有效沟道长度为4μm时),γ=0.2,V THN=| V THP | =0.7V。

设计如下图的放大器,满足如下要求,其中负载电容C L= 10pF。

Av > 4000V/V,VDD = 5V,GB = 5MHz ,SR > 10V/µs ,60°相位裕度,Vout 摆幅=0.5~4.5V, ICMR 1.5~4.5V,Pdiss≤ 2mW1.请说明详细的设计过程,包括公式表达式(假定C ox = 0.35fF/µm2,栅源电容按计算);2.给出进行交流仿真和瞬态仿真的spice仿真的网表,并给出仿真波形和结果。

3.如果要求Av至少提高为原来的2倍,其它要求不变,如何修改电路(注意讨论对其它性能参数的影响)?注意事项:1.计算得到的极点频率为角频率。

2.尺寸最后应选取整数,工艺精度的限制。

3.尾电流增加,Av增加还是减小?1.根据相位裕度PM=60deg的要求,求C c(假定ωz>10GB);考虑零点的影响,CC的选取:PM=60°时,GB处︒-︒=⎪⎪⎭⎫ ⎝⎛+⎪⎪⎭⎫ ⎝⎛+⎪⎪⎭⎫ ⎝⎛60180c c c 21z p p GB tg ar GB tg ar GB tg ar ωωω令ωz =10GB 时()︒-︒=+⎪⎪⎭⎫⎝⎛+︒601801.0c c 902tg ar GB tg ar p ω若PM>60 °, ωp2>2.2GB ,并由ωz =10GB2.210mII mII L C g g C C >⨯由此可得:LC C C 22.0>负载电容C L =10pF,所以C c >2.2pF,取C c =3pF2.由已知的Cc 并根据转换速率的要求(或功耗要求)选择ISS (I5)的范围;A I A I s V S C I S r Cr μμμ40,30,/10555=>>=取可得,由3.由计算得到的电流偏置值(I5 /2),设计W3/L3( W4/L4 )满足上ICMR (或输出摆幅)要求,即饱和区条件;极限情况下,即ICMR 达最大4.5V 时,M3,M4管的过驱动电压为:3,4OD DD THn THpV V ICMR V V +=-+-由此可得,M3,M4管的漏电流:2253(4)3,411/2()2022p ox OD p ox DD THn THp W WI I C V C V ICMR V V A L L μμμ+===-+-=代入μp C ox =50 μA/V 2,VDD = 5V ,ICMR +=4.5V ,I 5=40μA ,V THN =| V THP | =0.7V 可得:3,43,4() 3.2()=4W WL L =,此时取4. 验证M3处镜像极点是否大于10GBGBC gC C g gs m gs gs m 10233433>=+验证F101.5008100.354440.6767.0-14-15333⨯=⨯⨯⨯⨯⨯==ox gs C L W CV A I L WC g oxp m /1044.891020410502266633---⨯=⨯⨯⨯⨯⨯=⋅=μ代入验证成立5. 设计W1/L1( W2/L2 )满足GB 的要求1/m cGB g C =6121110521032⨯⨯⨯⨯=⋅=⋅=-πμGB C I L WC g c oxn m由此解得:1,21,2()=2.01()=3W WL L ,此时取6. 设计W5/L5满足下ICMR (或输出摆幅)要求; 当ICMR 取最小值1.5V 时,M5管的过驱动电压为:-6151-61222010=1.5-0.7=0.45V (/)110103OD GS TH n ox I V ICMR V ICMR V C W L μ--⎛⎫⎛⎫⨯⨯=-=-++ ⎪ ⎪ ⎪ ⎪⨯⨯⎝⎭⎝⎭255)(21OD ox n V L W C I μ=4)(3.59)(55==L WL W ,取由此可得, 7. 根据ωp2>2.2GB 计算得到gm6;并且根据偏置条件VSG4=VSG6计算得到M6的尺寸6222GB=; 2.2C m m p p L Cg gGB C ωω=>由,且得: 62622.2/,=2.2/m m L c m m L cg g C C g g C C >令2266 2.2()()()()n ox GS THN L p ox GS THP cWC V V C WL C V V LC μμ--=所以2224421412;()()2422p ox GS THP n ox GS THN W W I I C V V C V V L L μμ=-=-根据电路结构得:即 64642(2/2),()(4/4)n GS GS GS THP GS THP GS THN p W L V V V V V V V V W L μμ=-=-=-又因为所以6666(W2/L2)(W4/L4)2.2 2.21011034:==37.68=38350n LC p W WC L C L μμ⨯⨯⨯=联立可得,取8. 根据尺寸和g m6计算I 6,并验证V out,max 是否满足要求666444/3820190/4W L I I AW L μ==⨯=66666221901060.45(/)501038OD p ox I M V V C W L μ--⨯⨯===⨯⨯管的过驱动电压:6,max 50.45 4.55,DD OD out V V V V -=-=>满足要求9. 计算M7的尺寸。

1+X集成电路理论测试题+参考答案一、单选题(共39题,每题1分,共39分)1.元器件的引线直径与印刷焊盘孔径应有()的合理间隙。

A、0.2~0.4mmB、0.2~0.3mmC、0.1~0.4mmD、0.1~0.3mm正确答案:A2.在半自动探针台进行扎针调试时,当针尖悬于待测点上方,先调节( )旋钮。

A、X轴B、Y轴C、Z轴D、X-Y-Z微调正确答案:B答案解析:在半自动探针台上进行扎针调试时,当针尖悬于待测点上方,先用Y轴旋钮将探针退后少许,再用Z轴旋钮下针,最后用X轴旋钮。

3.点银浆时,银浆的覆盖范围需要()。

A、小于50%B、大于50%C、大于75%D、不小于90%正确答案:C答案解析:引线框架被推至点银浆指定位置后,点胶头在晶粒座预定粘着晶粒的位置点上定量的银浆(银浆覆盖范围>75%)。

4.转塔式分选机设备测试环节的流程是:( )。

A、测前光检→测后光检→测试→芯片分选B、芯片分选→测前光检→测后光检→测试C、测前光检→测试→测后光检→芯片分选D、测前光检→测后光检→芯片分选→测试正确答案:C答案解析:转塔式分选机设备测试环节的流程是:测前光检→测试→测后光检→芯片分选。

5.植球时,球和焊盘金属形成冶金结合,此时形成的焊点为()。

A、第一焊点B、第二焊点C、第三焊点D、芯片焊点正确答案:A答案解析:劈刀下降到芯片焊点表面,加大压力和功率,使球和焊盘金属形成冶金结合,形成第一焊点。

6.管装包装时,将真空包装的编带盘放入内盒、合上盖子后,需要在内盒的封口边( )处贴上“合格”标签。

A、左侧B、右侧C、中央D、任意位置正确答案:C答案解析:管装包装时,将真空包装的编带盘放入内盒、合上盖子后,需要在内盒的封口边中央处贴上“合格”标签。

7.下列关于重力式分选设备描述错误的是()。

A、装料时不需要注意芯片方向和管脚朝向B、重力式分选机手动上料的步骤分为两步,装料和上料夹具夹持C、手动装料需要操作人员取下待测料管一端的塞钉,并将料管整齐地摆放在操作台D、自动装料减少了人工补料的次数,节省了取塞钉与摆放料管的时间,降低了人工成本正确答案:A8.封装工艺中,()工序后的合格品进入塑封工序。

综合布线和系统集成⼤作业2014届课程⼤作业《综合布线和系统集成》课程⼤作业学⽣姓名李志博学号5011210506所属学院信息⼯程学院专业计算机科学与技术班级计算机14-5指导教师范泽华教师职称讲师塔⾥⽊⼤学教务处制综合布线的发展趋势⽹络综合布线是⼀门新发展起来的⼯程技术,它涉及许多理论和技术问题,是⼀个多学科交叉的新领域,也是计算机技术、通信技术、控制技术与建筑技术紧密结合的产物。

现今,我们⽣活在⼀个信息化时代,⼈们的⽣活已经离不开计算机⽹络系统了,⽽这些系统全部是由⽹络综合布线系统来⽀持的。

综合布线的未来趋势将会沿着⾼密度、模块化、智能化布线的⽅向发展。

综合布线从市场格局来看,将是百花齐放的状态,综合布线作为通⽤标准的系统,各个⼚商也都有各⾃不同的特长,百家争鸣的情况还会继续。

但从发展来看,综合布线将向数据中⼼、光纤到户、三⽹融合、⾼带宽、智能管理系统以及绿⾊环保等⽅向发展。

⼀、数据中⼼数据中⼼的布线系统,数据中⼼布线也有两种不同的类型(如互联⽹数据中⼼与企业数据中⼼),云计算应⽤领域的蓬勃发展与互联⽹数据中⼼规模发展互相促进,使布线在这⼀领域向规模化⽅向发展,且布线产品也有专业化发展的趋势,特别是近年来移动互联⽹的迅猛增长趋势,使互联⽹数据中⼼的应⽤有了新的增长点。

对于企业级数据中⼼⽽⾔,数据中⼼与信息资产在企业中的地位越来越重要,规模也在不断扩⼤,且相⽐较互联⽹数据中⼼,企业级数据中⼼对布线系统的可靠性与品牌会更加关注,与楼宇布线系统的趋向完全竞争的格局不同,企业级数据中⼼将在较长时期内处于⼀种寡头垄断的不完全竞争状态。

其三是布线系统除了承载上述的两⽅⾯应⽤外,还会较多的应⽤于其他基于IP⽹络的弱电⼦系统内,如视频会议系统、IP监控系统、楼宇⾃控系统、门禁系统、机房智能PDU系统等。

布线系统将成为基于IP⽹络的基础传输平台,在其他⼦系统的应⽤增长下,布线系统的总体市场⽤量相⽐较以前有额外的增长。

《电子控制系统中的集成电路》作业设计方案一、课程背景及目标《电子控制系统中的集成电路》是电子信息工程专业的一门重要课程,旨在帮助学生深入了解集成电路在电子控制系统中的应用及原理。

通过本课程的进修,学生将掌握集成电路的基本知识、设计方法和实际应用技巧,为将来从事电子控制系统相关工作打下坚实的基础。

二、作业设计要求1. 熟悉常见的集成电路类型及其特点;2. 掌握集成电路的设计原理和方法;3. 能够应用EDA软件进行集成电路的仿真设计;4. 能够分析和解决集成电路设计中的实际问题。

三、作业设计内容1. 熟悉常见的集成电路类型及其特点学生将通过独立进修和小组讨论的方式,了解常见的集成电路类型,包括数字集成电路、模拟集成电路和混合集成电路等,掌握它们的特点和应用领域。

2. 掌握集成电路的设计原理和方法学生将进修集成电路的设计原理和方法,包括逻辑门设计、模拟电路设计、混合信号电路设计等内容,通过理论进修和实验操作,掌握集成电路设计的基本技能。

3. 应用EDA软件进行集成电路的仿真设计学生将进修如何应用EDA软件进行集成电路的仿真设计,包括电路图绘制、参数设置、仿真分析等操作,通过实际操作,加深对集成电路设计的理解和掌握。

4. 分析和解决集成电路设计中的实际问题学生将通过案例分析和实际项目仿真,分析和解决集成电路设计中的实际问题,培养解决问题的能力和实践能力,提高对集成电路设计的应用水平。

四、作业设计步骤1. 独立进修和讨论常见的集成电路类型及特点;2. 进修集成电路的设计原理和方法,完成相关理论知识的进修任务;3. 应用EDA软件进行集成电路的仿真设计,完成仿真实验任务;4. 分析和解决集成电路设计中的实际问题,完成案例分析和项目仿真任务;5. 撰写作业报告,总结进修效果和心得体会。

五、作业评分标准1. 对常见集成电路类型及特点的掌握水平;2. 集成电路设计原理和方法的理解和应用能力;3. 应用EDA软件进行仿真设计的操作技能;4. 分析和解决实际问题的能力;5. 作业报告的撰写质量和表达能力。

系统集成与应用实验设计报告16路模拟信号发生器班级:小组成员:指导教师:目录1、设计任务和要求分析 (2)2、整体方案设计选择 (2)3、理论计算 (6)4、电路设计及仿真 (7)5、实验总结 (11)六、附录 (12)一、设计任务与要求分析1.1设计任务用C8051F020单片机完成16路信号源的输出,并通过单片机内部A/D转换器进行输出信号源的反馈采样,最后通过异步串行接口(UART)将采样结果输出。

利用C8051单片机将波形量化数据放置于内部ROM,通过内部D/A产生信号以及I/O端口控制多路模拟开关,同时生成16路信号源,注意信号源调理电路中采保部分的选值,并给出理论计算结果。

反馈回采部分采用单片机的12位高精度A/D转换器,采样频率自定(要求给出理论计算值),并通过UART接口将采样值送出按9600bps的波特率发出(接收对象可以是计算机或其它)。

1.2任务要求分析我们通过集体讨论与分析,确定了如下的设计流程:图 1.系统流程图在进行具体的实验设计之后,我们进行了电路简化,放大滤波通过一个运算放大器来实现,不仅使电路得到了简化,而且也节省了资源。

二、整体方案设计选择2.1单片机部分单片机选用 C8051F020,是完全集成的混合信号系统级 MUC 芯片具有64个数字I/O引脚;具有12位100kps的8通道ADC,带PGA和多路模拟开关;具有2个12位DAC,具有可编程数据更新方式;64K可在系统编程的FLASH存储器;4352字节的片内RAM;可寻址64K字节地址空间的数据存储器接口:2个UART串行接口。

基于以上优良特性,故选用该单片机。

单片机具有上电复位、掉电复位、外部复位、软件强制复位等多种复位方式。

在应用中外部复位方式得到广泛应用。

外部/RST引脚提供使用外部电路使单片机强制复位的手段。

在外部/RST引脚加一个低电平有效信号,将使单片机复位,最好提供一个外部上拉,或对RST引脚去耦以防止噪声引起复位。

系统集成与应用实验设计报告16路模拟信号发生器班级:小组成员:指导教师:目录一、设计任务和要求分析 (2)二、整体方案设计选择 (2)三、理论计算................... ... ... ... .. (6)四、电路设计及仿真..................................... .. (7)五、实验总结 (11)六、附录 (12)一、设计任务与要求分析1.1 设计任务用C8051F020单片机完成16路信号源的输出,并通过单片机内部A/D转换器进行输出信号源的反馈采样,最后通过异步串行接口(UART)将采样结果输出。

利用C8051单片机将波形量化数据放置于内部ROM,通过内部D/A产生信号以及I/O 端口控制多路模拟开关,同时生成16路信号源,注意信号源调理电路中采保部分的选值,并给出理论计算结果。

反馈回采部分采用单片机的12位高精度A/D 转换器,采样频率自定(要求给出理论计算值),并通过UART接口将采样值送出按9600bps的波特率发出(接收对象可以是计算机或其它)。

1.2 任务要求分析我们通过集体讨论与分析,确定了如下的设计流程:图1.系统流程图在进行具体的实验设计之后,我们进行了电路简化,放大滤波通过一个运算放大器来实现,不仅使电路得到了简化,而且也节省了资源。

二、整体方案设计选择2.1 单片机部分单片机选用C8051F020,是完全集成的混合信号系统级MUC芯片具有64个数字I/O引脚;具有12位100kps的8通道ADC,带PGA和多路模拟开关;具有2个12位DAC,具有可编程数据更新方式;64K可在系统编程的FLASH存储器;4352字节的片内RAM;可寻址64K字节地址空间的数据存储器接口:2个UART串行接口。

基于以上优良特性,故选用该单片机。

单片机具有上电复位、掉电复位、外部复位、软件强制复位等多种复位方式。

在应用中外部复位方式得到广泛应用。

外部/RST引脚提供使用外部电路使单片机强制复位的手段。

在外部/RST引脚加一个低电平有效信号,将使单片机复位,最好提供一个外部上拉,或对RST引脚去耦以防止噪声引起复位。

图2 单片机外部电路2.2 电源部分设计电源的选定好与坏对于系统设计来说至关重要,一个好的电源的设计标志着成功的一半。

在这个系统中我们需要用到一个正负5V的双电源,用于给运放LM358供电,尽管LM358可以采用单电源供电,但是输入信号的幅度比较小时,用单电源供电运算放大器的特性会变差,而我们的设计中,输入信号的变化范围较大,,用双电源比较合适。

同时还需要给模拟开关ADG406和构成采样保持电路的CA3140提供正5V的电源电压。

综上所述,我们通过用LM7805,LM7905组成一个正负5V的双电源电路提供正负5V的电源。

此外,C8051F020的供电电压为3.3V,所以我们还需要用LM1117(低压差三端稳压器)将5V电源转换为3.3V给C8051F020单片机供电。

图3. 7805设计参考资料图4. 7905设计参考资料2.3 模拟开关部分在整个设计中,我们的多路模拟开关采用ADG406,单芯片CMOS模拟多路复用器。

ADG406根据4位二进制地址线A0,A1,A2,A3所确定的地址,将16路输入之一切换至公共输出。

所有器件均提供EN输入,用来使能或禁用器件。

禁用时,所有通道均关闭。

ADG406采用增强型LC2MOS工艺设计,具有低功耗,高开关速度和低导通电阻特性,因而适合高速度数据采集系统和音频信号开关应用。

低功耗特性则适合电池供电系统。

接通时,各通道在两个方向的导电性能相同,输入信号范围可扩展至电源电压范围。

在断开的条件下,达到电源电压的信号电平被阻止。

所有通道均采用先开后合式开关,防止开关通道时发生瞬时短路。

设计本身具有低电荷注入特性,当切换数字输入时,可实现最小的瞬变。

我们采用ADG406进行采样时的16路信号的切换以及将16路信号输入单片机AD时的16路信号切换。

图5.ADG406真值表以及转换时间2.4 信号调理部分设计2.4.1采样保持电路采样保持电路采用的是CA3140集成采样保持芯片。

它的输入阻抗高达1210 ,输入偏流约10PA,工作速度较高(SR=9V/us),常用于积分及保持电路等。

它既可以双电源供电(±2V~±18V),又可以单电源供电(4V~36V)。

其工作温度范围为-55℃~-125℃,使用CA3140的注意事项如下:(1)因其输入级为MOSFET,故安装焊接时应符合MOSFET的要求。

(2)CA3140的最大允许差模电压为±8V,故一般应接保护电路,以免因电压过高而击穿,其输入回路电流应小于1mA,因此需在输入及反馈回路中接限流电阻,其值一般不小于3.9KΩ。

(3)其输出负载电阻应大于2kΩ,否则将使负向输出动态范围变小。

2.4.2放大滤波器部分由于C8051F020的AD转换器输出电压为2.4V,且在实际线路输出过程中会受到噪声干扰,所以需要设计放大滤波电路。

我们选用LM358芯片进行放大滤波,不仅可以简化电路,并且成本较低。

三、理论计算3.1 DAC 输出频率通过手册可知,C8051F020内部DAC 最高输出频率为100kHz ,模拟开关最快切换时间为180ns ,采样保持电路的采样时间约为4.5ns ,计算如下:180+4.5=184.5ns所以DA 的采样周期必须比184.5ns 大,这里我们取DA 的输出周期为184.5*3=553.5ns 。

即频率约为:190000hz ,但是却超过了C8051F020内部DAC 最高输出频率为100kHz 。

所以只要低于190000hz 就可以了,为了以后的设计方便,也为了能够在采集一个周期中尽可能多的点,我们取DAC 输出频率为1600Hz. 此时每一路模拟开关的输出频率为100Hz 。

3.2 ADC 回采频率计算依据题目ADC 回采后经串口发送,串口波特率为9600,所以ADC 回采频率受到串口波特率制约,所以取ADC 回采频率与串口波特率一致:96001200b 8ps = 所以ADC 采集每一路模拟信号的频率为1.2kHz 。

3.3 采样保持电容计算采样保持电容大小选取受到切换速度的制约,与模拟开关、输出放大器的性能都有关系,具体计算如下:41s 32i =.8s= 2.880sR C R C ττ--≤⨯≥⨯切换时间110轮换时间1计算得: 79.4710p 0.11F C F μ-⨯<<结果取0.01uf 的电容。

3.4 滤波器的设计计算由于C8051F020的AD 转换器输出电压为2.4V ,而其内部的DA 转换器的输入电压可以达到4.8V ,且在实际线路输出过程中会受到噪声干扰,所以我们采用放大倍数为2倍的低通滤波器。

我们设计的滤波器是无限增益多路型低通滤波器,滤波器的参数分别如下:12325.65,32.92,51.30R k R k R k =Ω=Ω=Ω,120.1,0.015C F C F μμ==所以,增益312p R K R =-=-,固有频率0628.93w ==,阻尼系数为:011231111()/ 1.413w CR RR α=++=。

所以截至频率为0/2100w Hz π=。

四、电路设计及仿真4.1 电源设计及仿真图6.双电源设计电路图图7.双电源仿真结果图4.2 放大滤波设计及仿真设计及仿真由于C8051F020的AD 转换器输出电压为2.4V ,而其内部的DA 转换器的输入电压可以达到4.8V ,且在实际线路输出过程中会受到噪声干扰,所以我们采用放大倍数为2倍的低通滤波器。

我们设计的滤波器是无限增益多路型低通滤波器,滤波器的参数分别如下:12325.65,32.92,51.30R k R k R k =Ω=Ω=Ω,120.1,0.015C F C F μμ==所以,增益312p R K R =-=-,固有频率02312628.93w R R C C ==,阻尼系数为:011231111()/ 1.413w C R R R α=++=。

所以截至频率为0/2100w Hz π=。

图8.低通滤波及放大电路图9.低通滤波及放大电路仿真图4.3采用保持电路的设计图10.采样保持电路原理图4.4模拟开关电路设计图11.模拟开关电路原理图4.5抗干扰设计图12.耦合电容设计图13.地隔离的设计4.6 整体电路设计图14.整体电路原理图4.7 pcb设计图15.pcb版图五、实验总结这次课程设计我们先从C8051F020芯片的引脚功能和工作原理入手。

将里面所涉及到的功能用我所学的系统集成以及模数电、测控电路的知识进行运用。

在实现电路的稳压功能时,用到了7805和7905,LM1117这三种芯片。

在设计电路的过程中,我们发现芯片的选择是非常重要的一个环节,芯片的参数以及功能和成本都是我们需要考虑的问题。

同时这次课程设计让我们小组成员进一步巩固了对Multisim软件仿真和AD 的使用和操作,在设计中遇到了很多问题,我们通过上网查资料以及同学和老师的帮助,大都得到了解决。

除此之外,小组成员也感受到了合作的力量,积极分工,在做好自己的工作的同时,协助其他成员。

在此,感谢老师的悉心指导和他同学的无私帮助!附录:程序源码:#include <c8051f020.h> // SFR declarations//-----------------------------------------------------------------------------// 16-bit SFR Definitions for 'F02x//-----------------------------------------------------------------------------sfr16 RCAP4 = 0xE4; // Timer4 capture/reloadsfr16 TMR4 = 0xF4; // Timer4sfr16 DAC0 = 0xd2; // DAC0 datasfr16 DAC1 = 0xd5; // DAC1 data//-----------------------------------------------------------------------------// Global Constants//-----------------------------------------------------------------------------#define SYSCLK 22118400 // Internal oscillator frequency in Hz#define SAMPLE_RATE_DAC 100000L // DAC sampling rate in Hz#define PHASE_PRECISION 65536 // range of phase accumulator#define FREQUENCY 1000 // Frequency of output waveform in Hz// <PHASE_ADD> is the change in phase between DAC samples; It is used in// the set_DACs routine.unsigned int PHASE_ADD = FREQUENCY * PHASE_PRECISION / SAMPLE_RATE_DAC;////////////自加////////////////unsigned long AD;//AD转换的值unsigned char temp_l;unsigned char temp_h;bit ReceiveBit;/*接收标志位*/unsigned char temp;////////////////////////////int code SINE_TABLE[256] = {0x0000, 0x0324, 0x0647, 0x096a, 0x0c8b, 0x0fab, 0x12c8, 0x15e2,0x18f8, 0x1c0b, 0x1f19, 0x2223, 0x2528, 0x2826, 0x2b1f, 0x2e11,0x30fb, 0x33de, 0x36ba, 0x398c, 0x3c56, 0x3f17, 0x41ce, 0x447a,0x471c, 0x49b4, 0x4c3f, 0x4ebf, 0x5133, 0x539b, 0x55f5, 0x5842,0x5a82, 0x5cb4, 0x5ed7, 0x60ec, 0x62f2, 0x64e8, 0x66cf, 0x68a6,0x6a6d, 0x6c24, 0x6dca, 0x6f5f, 0x70e2, 0x7255, 0x73b5, 0x7504,0x7641, 0x776c, 0x7884, 0x798a, 0x7a7d, 0x7b5d, 0x7c29, 0x7ce3,0x7d8a, 0x7e1d, 0x7e9d, 0x7f09, 0x7f62, 0x7fa7, 0x7fd8, 0x7ff6,0x7fff, 0x7ff6, 0x7fd8, 0x7fa7, 0x7f62, 0x7f09, 0x7e9d, 0x7e1d,0x7d8a, 0x7ce3, 0x7c29, 0x7b5d, 0x7a7d, 0x798a, 0x7884, 0x776c,0x7641, 0x7504, 0x73b5, 0x7255, 0x70e2, 0x6f5f, 0x6dca, 0x6c24,0x6a6d, 0x68a6, 0x66cf, 0x64e8, 0x62f2, 0x60ec, 0x5ed7, 0x5cb4,0x5a82, 0x5842, 0x55f5, 0x539b, 0x5133, 0x4ebf, 0x4c3f, 0x49b4,0x471c, 0x447a, 0x41ce, 0x3f17, 0x3c56, 0x398c, 0x36ba, 0x33de,0x30fb, 0x2e11, 0x2b1f, 0x2826, 0x2528, 0x2223, 0x1f19, 0x1c0b,0x18f8, 0x15e2, 0x12c8, 0x0fab, 0x0c8b, 0x096a, 0x0647, 0x0324,0x0000, 0xfcdc, 0xf9b9, 0xf696, 0xf375, 0xf055, 0xed38, 0xea1e, 0xe708, 0xe3f5, 0xe0e7, 0xdddd, 0xdad8, 0xd7da, 0xd4e1, 0xd1ef, 0xcf05, 0xcc22, 0xc946, 0xc674, 0xc3aa, 0xc0e9, 0xbe32, 0xbb86, 0xb8e4, 0xb64c, 0xb3c1, 0xb141, 0xaecd, 0xac65, 0xaa0b, 0xa7be, 0xa57e, 0xa34c, 0xa129, 0x9f14, 0x9d0e, 0x9b18, 0x9931, 0x975a, 0x9593, 0x93dc, 0x9236, 0x90a1, 0x8f1e, 0x8dab, 0x8c4b, 0x8afc, 0x89bf, 0x8894, 0x877c, 0x8676, 0x8583, 0x84a3, 0x83d7, 0x831d, 0x8276, 0x81e3, 0x8163, 0x80f7, 0x809e, 0x8059, 0x8028, 0x800a, 0x8000, 0x800a, 0x8028, 0x8059, 0x809e, 0x80f7, 0x8163, 0x81e3, 0x8276, 0x831d, 0x83d7, 0x84a3, 0x8583, 0x8676, 0x877c, 0x8894, 0x89bf, 0x8afc, 0x8c4b, 0x8dab, 0x8f1e, 0x90a1, 0x9236, 0x93dc, 0x9593, 0x975a, 0x9931, 0x9b18, 0x9d0e, 0x9f14, 0xa129, 0xa34c, 0xa57e, 0xa7be, 0xaa0b, 0xac65, 0xaecd, 0xb141, 0xb3c1, 0xb64c, 0xb8e4, 0xbb86, 0xbe32, 0xc0e9, 0xc3aa, 0xc674, 0xc946, 0xcc22, 0xcf05, 0xd1ef, 0xd4e1, 0xd7da, 0xdad8, 0xdddd, 0xe0e7, 0xe3f5, 0xe708, 0xea1e, 0xed38, 0xf055, 0xf375, 0xf696, 0xf9b9, 0xfcdc, };//-----------------------------------------------------------------------------// Function Prototypes//-----------------------------------------------------------------------------void main(void);void OSCILLATOR_Init(void);void DAC0_Init (void);void DAC1_Init (void);void TIMER4_Init(int counts);void Set_DACs(void);//////////////自加///////////////void PORT_Init (void);void Timer3_Init (int counts);void ADC_Init(void);void UART0_Init (void);void delayms(unsigned int z);//////////////////////////////-----------------------------------------------------------------------------// MAIN Routine//-----------------------------------------------------------------------------void main (void){unsigned char temp1=0xff,temp2=0xff;unsigned int ad_now;WDTCN = 0xde; // Disable watchdog timerWDTCN = 0xad;OSCILLATOR_Init (); // Initialize oscillatorDAC0_Init (); // Initialize DAC0PORT_Init ();Timer3_Init (SYSCLK / 1200 );ADC_Init();UART0_Init();AMX0SL =0x00; //选择通道AIN0TIMER4_Init(SYSCLK/SAMPLE_RATE_DAC);// Initialize Timer4 to overflow// <SAMPLE_RATE_DAC> times per// secondEA = 1; // Enable global interrupts ES0 =1;//串口中断使能while(1){temp1=0xff;temp2=0xff;ad_now=AD;temp1&=ad_now;temp2&=(ad_now>>8);SBUF0=temp1;while(!TI0);TI0=0;SBUF0=temp2;while(!TI0);TI0=0;SBUF0=0x0d;while(!TI0);TI0=0;SBUF0=0x0a;while(!TI0);TI0=0;delayms(200);}}////////////////自加//////////////////void delayms(unsigned int z){unsigned int x,y;for(x=0;x<z;x++)for(y=0;y<121;y++);}void PORT_Init (void){XBR2 = 0x40;/*使能交叉开关*/P2MDOUT =0xff;//XBR0 = 0x04; /*使能UART0*/// XBR1 = 0x00;// //XBR2 = 0x40; /*使能交叉开关和弱上拉*/ // P0MDOUT |= 0x01; /*使能TX0作为推挽输出*/ // P1MDOUT |= 0x40; /*时能P1.6 (LED)作为推挽输出*/// P3MDOUT |= 0xdf;XBR0 = 0x04;/*使能UART0*/}//函数功能: 定时器3初始化//入口参数: int countsvoid Timer3_Init (int counts){TMR3CN = 0x00;TMR3RLL = -counts; //初始化重载值TMR3L = 0xffff; //设置自动重载值TMR3CN |= 0x04;}//函数功能: ADC0初始化void ADC_Init(void){ADC0CN |=0x84;/*ADC0使能,定时器3溢出使能模/数转换*/REF0CN |=0x03;/*内部电压基准提供从VREF脚输出,ADC0电压基准取自VREF0*/ADC0CF |=0x50;/*转换周期和增益为1*/AMX0CF |=0x00;/*单端输入*/EIE2 |=0x02;/*ADC0转换结束中断*/}//函数功能: AD中断服务程序void ADC_ISR (void) interrupt 15{AD0INT=0;//清A/D中断标志temp_l=ADC0L;temp_h=ADC0H;AD=temp_h*256+temp_l;}void UART0_Init (void){SCON0=0x50; //串口方式1TMOD=0X20; //选用定时器1作为波特率发生器TH1=0xF4;TL1=0xF4;PCON=0x80;//波特率为9600TR1=1; //定时器启动}void UART0_ISR (void) interrupt 4{//if(TI0) //是发送中断还是接收中断// {//SBUF0=AD;//while(!TI0);//TI0=0;// }}////////////////////////////////////-----------------------------------------------------------------------------// Interrupt Service Routines//-----------------------------------------------------------------------------//-----------------------------------------------------------------------------// TIMER4_ISR -- Wave Generator//-----------------------------------------------------------------------------//// This ISR is called on Timer4 overflows. Timer4 is set to auto-reload mode // and is used to schedule the DAC output sample rate in this example.// Note that the value that is written to DAC1 during this ISR call is// actually transferred to DAC1 at the next Timer4 overflow.////-----------------------------------------------------------------------------void TIMER4_ISR (void) interrupt 16{static unsigned char ch_i;ch_i++;if(ch_i==16){ch_i=0;Set_DACs();}P2=ch_i;T4CON &= ~0x80; // Clear Timer4 overflow flag }//-----------------------------------------------------------------------------// Initialization Routines//-----------------------------------------------------------------------------//-----------------------------------------------------------------------------// OSCILLATOR_Init//-----------------------------------------------------------------------------//// Return Value : None// Parameters : None//// This routine initializes the system clock to use an 22.1184MHz crystal// as its clock source.////-----------------------------------------------------------------------------void OSCILLATOR_Init (void){int i; // Delay counterOSCXCN = 0x67; // Start external oscillator with// 22.1184MHz crystalfor (i=0; i < 256; i++) ; // Wait for osc. to start upwhile (!(OSCXCN & 0x80)) ; // Wait for crystal osc. to settleOSCICN = 0x88; // Select external oscillator as SYSCLK// source and enable missing clock// detector}//-----------------------------------------------------------------------------// DAC0_Init//-----------------------------------------------------------------------------//// Return Value : None// Parameters : None//// Configure DAC0 to update on Timer4 overflows and enable the the VREF buffer.////-----------------------------------------------------------------------------void DAC0_Init(void){DAC0CN = 0x94; // Enable DAC0 in left-justified mode// managed by Timer4 overflowsREF0CN |= 0x03; // Enable the internal VREF (2.4v) and// the Bias Generator }//-----------------------------------------------------------------------------// TIMER4_Init//-----------------------------------------------------------------------------//// Return Value : None// Parameters :// 1) int counts - calculated Timer overflow rate// range is positive range of integer: 0 to 32767//// Configure Timer4 to auto-reload at interval specified by <counts> using// SYSCLK as its time base.////-----------------------------------------------------------------------------void TIMER4_Init (int counts){T4CON = 0x00; // Stop Timer4; Clear overflow flag (TF4);// Set to Auto-Reload ModeCKCON |= 0x40; // Timer4 counts SYSCLKsRCAP4 = -counts; // Set reload valueTMR4 = RCAP4; // Initialzie Timer4 to reload valueEIE2 |= 0x04; // Enable Timer4 interruptsT4CON |= 0x04; // Start Timer4}//-----------------------------------------------------------------------------// Set_DACs//-----------------------------------------------------------------------------//// Return Value : None// Parameters : None//// Calculates the update values for the two DACs using SINE_TABLE. The DACs // will actually be updated upon the next Timer4 interrupt. Until that time,// the DACs will hold their current value.////-----------------------------------------------------------------------------void Set_DACs(void){static unsigned phase_acc = 0; // Holds phase accumulatorint SIN_temp; // Temporary 16-bit variablesunsigned char index; // Index into SINE tablephase_acc += PHASE_ADD; // Increment phase accumulator index = phase_acc >> 8;SIN_temp = SINE_TABLE[index]; // Read the table value// Add a DC bias to change the the rails from a bipolar (-32768 to 32767)// to unipolar (0 to 65535)// Note: the XOR with 0x8000 translates the bipolar quantity into// a unipolar quantity.DAC0 = SIN_temp ^ 0x8000;}//-----------------------------------------------------------------------------// End Of File。