AMD-opteron6100体系结构.jsp

- 格式:doc

- 大小:1.23 MB

- 文档页数:25

cpu-z是怎么看内存颗粒的如何用cpu-z看内存,怎么看?下面店铺整理了有关cpuz的知识,希望对你有帮助。

电脑cpu怎么看查看cpu的方法有很多,也非常的简单,最直接的方法是进入-- 我的电脑 -在空白区域右键单击鼠标选择-- 属性即可看到电脑最重要的硬件部分CPU和内存的一些参数,如下图。

从上图中可以看出使用cpu-z软件查看cpu的信息比较全面,比较推荐新手朋友们使用。

怎么看cpu好坏关于cpu性能主要看以下参数CPU系列如早期的赛扬,到奔腾双核再到酷睿(core)双核,目前主流处理器有corei3与i5,i7以及AMD四核处理器CPU内核 CPU内核 PreslerCPU架构 64位【32位和64位的区别】核心数量双核心四核心,甚至更高的核心,核心越高性能越好。

内核电压(V) 1.25-1.4V 电压越低,功耗越低。

制作工艺(微米) 0.065 微米目前多数处理器为45nm技术,高端处理器目前采用32nm,越低工艺越高,相对档次就越高。

CPU频率主频(MHz) 2800MHz 主频越高,处理器速度越快总线频率(MHz) 800MHz附上为大家之作的cpu性能分布图:下面进行决定cpu性能的决定参数性能指标主频主频也叫时钟频率,单位是兆赫(MHz)或千兆赫(GHz),用来表示CPU的运算、处理数据的速度。

CPU的主频=外频×倍频系数。

很多人认为主频就决定着CPU的运行速度,这不仅是片面的,而且对于服务器来讲,这个认识也出现了偏差。

至今,没有一条确定的公式能够实现主频和实际的运算速度两者之间的数值关系,即使是两大处理器厂家Intel(英特尔)和AMD,在这点上也存在着很大的争议,从Intel的产品的发展趋势,可以看出Intel很注重加强自身主频的发展。

像其他的处理器厂家,有人曾经拿过一块1GHz的全美达处理器来做比较,它的运行效率相当于2GHz 的Intel处理器。

主频和实际的运算速度存在一定的关系,但并不是一个简单的线性关系. 所以,CPU的主频与CPU实际的运算能力是没有直接关系的,主频表示在CPU内数字脉冲信号震荡的速度。

Top500强中超级计算机的体系结构(1)超级计算机“京”(K Computer)是⽇本RIKEN⾼级计算科学研究院(AICS)与富⼠通的联合项⽬。

“京”(K Computer)没有使⽤GPU加速,⽽是完全基于传统处理器搭建。

“现在的“京”(K Computer)配备了88128颗富⼠通SPARC64 VIIIfx 2.0GHz⼋核⼼处理器,核⼼总量705024个,最⼤计算性能10.51Petaflop/s,峰值性能 11.28038 Petaflop/s,同时效率⾼达93.2%,总功耗为12659.9千⽡。

(2)位于中国天津国家超级计算机中⼼的“天河⼀号系统”计算能⼒达到2.57 petaflop/s。

天河⼀号采⽤了CPU+GPU的混合架构。

配有14336颗Intel Xeon X5670 2.93GHz六核⼼处理器、7168块NVIDIA Tesla M2050⾼性能计算卡,以及2048颗我国⾃主研发的飞腾FT-1000⼋核⼼处理器,总计20多万颗处理器核⼼,同时还配有专有互联⽹络。

(3)“JAGUAR”超级计算机系统⾪属于美国能源部,坐落于美国橡树岭国家实验室。

“JAGUAR XT5”系统由美国国家科学基⾦会出资、Cray公司建造、⽥纳西⼤学和国家计算科学研究院共同拥有。

它曾在2010年6⽉的TOP500排⾏榜中排名第⼀。

“JAGUAR”是⼀台民⽤计算机,采⽤AMD Magny-Cours核⼼六核Opteron处理器,其最⼤计算能⼒为1.75 petaflop/s。

(4)“星云”坐落于我国深圳国家超级计算机中⼼。

“星云”系统运算峰值达到3 petaflop/s,最⼤计算性能1.271 petaflop/s,并且是中国第⼀台、世界第三台实现双精度浮点计算超千万亿次的超级计算机,且其单位耗能所提供的性能达到了4.98亿次/⽡。

“星云”超级计算机采⽤⾃主设计的HPP体系结构,由4640个计算单元组成,采⽤了⾼效异构协同计算技术,系统包括了9280颗通⽤CPU和4640颗专⽤GPU组成。

AMD Athlon 64位微处理器的体系结构完成人:吕晴 03级5班 033344 onion2005@甘爱梅 03级5班 033349 yisuoyuyan_@徐彦 03级5班 033348 xuyan5888@完成时间:2006-6-8摘要:信息技术的飞速发展,32位计算平台在越来越多的高端应用中显得力不从心,而64位时代的到来,无疑是广大用户的福音。

本文详细介绍了AMD这个全球知名处理器制造厂商所制造的64位最新微处理器产品――Athlon,并从各个方面综合的比较了Athlon与苹果公司,Intel公司产品的差别所在,指出了64位高端微处理器的未来发展方向。

目录一引言 (3)二 64位微处理器市场背景介绍 (3)三、AMD的64位时代 (4)四、 Athlon详细介绍 (5)4.1 Athlon 64 的3大区分特征 (5)4.2 Athlon 核心介绍 (6)4.3 Venice 核心特点介绍 (7)五、Athlon 与PowerMac G5、Itantium之比较 (9)5.1 Athlon VS PowerMac G5 (9)5.2 Athlon VS Itantium (11)六、AMD64位微处理器的发展展望 (14)6.1 64位将成为主流双核心是发展方向 (14)6.2 90nm工艺、应变硅和防毒技术将得到大量应用 (14)6.3软件环境必须发展成熟 (15)七、小结 (15)八、参考文献 (15)一引言随着计算机应用的不断深入和半导体芯片制造水平的提高,计算机的应用正在向64位计算演进。

目前主流CPU使用的64位技术主要有AMD公司的AMD64位技术、Intel公司的EM64T技术、和Intel公司的IA-64技术。

其中IA-64是Intel独立开发,不兼容现在的传统的32位计算机,仅用于Itanium(安腾)以及后续产品Itanium 2。

这里的64位技术是相对于32位而言的,这个位数指的是CPU GPRs(General-Purpose Registers,通用寄存器)的数据宽度为64位,64位指令集就是运行64位数据的指令,也就是说处理器一次可以运行64bit数据。

ReferencesAMD(2012)AMD Opteron TM6300series processor quick reference guide.Tech.Rep.,August Aochi H,Ulrich T,Ducellier A,Dupros F,Michea D(2013)Finite difference simulations of seismic wave propagation for understanding earthquake physics and predicting ground motions:advances and challenges.J Phys Conf Ser454(1):012010.https:///10.1088/ 1742-6596/454/1/012010Awasthi M,Nellans DW,Sudan K,Balasubramonian R,Davis A(2010)Handling the problems and opportunities posed by multiple on-chip memory controllers.In:Parallel architectures and compilation techniques(PACT),pp319–330Azimi R,Tam DK,Soares L,Stumm M(2009)Enhancing Operating system support for multicore processors by using hardware performance monitoring.ACM SIGOPS Oper Syst Rev43(2):56–65.https:///10.1145/1531793.1531803Bach M,Charney M,Cohn R,Demikhovsky E,Devor T,Hazelwood K,Jaleel A,Luk CK,Lyons G,Patil H,Tal A(2010)Analyzing parallel programs with pin.IEEE Comput43(3):34–41 Barrow-Williams N,Fensch C,Moore S(2009)A communication characterisation of splash-2and parsec.In:IEEE international symposium on workload characterization(IISWC),pp86–97.https:///10.1109/IISWC.2009.5306792Bellard F(2005)Qemu,a fast and portable dynamic translator.In:USENIX annual technical conference(ATEC).USENIX Association,Berkeley,pp41–41Bienia C,Kumar S,Li K(2008a)PARSEC vs.SPLASH-2:a quantitative comparison of two mul-tithreaded benchmark suites on Chip-Multiprocessors.In:IEEE international symposium on workload characterization(IISWC),pp47–56.https:///10.1109/IISWC.2008.4636090 Bienia C,Kumar S,Singh JP,Li K(2008b)The PARSEC benchmark suite:characterization and architectural implications.In:International conference on parallel architectures and compilation techniques(PACT),pp72–81Binkert N,Beckmann B,Black G,Reinhardt SK,Saidi A,Basu A,Hestness J,Hower DR,Krishna T,Sardashti S,Sen R,Sewell K,Shoaib M,Vaish N,Hill MD,Wood DA(2011)The gem5 simulator.ACM SIGARCH Comput Archit News39(2):1–7Borkar S,Chien AA(2011)The future of mun ACM54(5):67–77 Broquedis F,Aumage O,Goglin B,Thibault S,Wacrenier PA,Namyst R(2010)Structuring the execution of OpenMP applications for multicore architectures.In:IEEE international parallel &distributed processing symposium(IPDPS),pp1–10Caparros Cabezas V,Stanley-Marbell P(2011)Parallelism and data movement characterization of contemporary application classes.In:ACM symposium on parallelism in algorithms and architectures(SPAA)51©The Author(s),under exclusive licence to Springer International Publishing AG,part of Springer Nature2018E.H.M.Cruz et al.,Thread and Data Mapping for Multicore Systems,SpringerBriefs in Computer Science,https:///10.1007/978-3-319-91074-1Casavant TL,Kuhl JG(1988)A taxonomy of scheduling in general-purpose distributed computing systems.IEEE Trans Softw Eng14(2):141–154Chishti Z,Powell MD,Vijaykumar TN(2005)Optimizing replication,communication,and capacity allocation in CMPs.ACM SIGARCH Comput Archit News33(2):357–368.https:// /10.1145/1080695.1070001Conway P(2007)The AMD opteron northbridge architecture.IEEE Micro27(2):10–21Corbet J(2012a)AutoNUMA:the other approach to NUMA scheduling./Articles/ 488709/Corbet J(2012b)Toward better NUMA scheduling./Articles/486858/Coteus PW,Knickerbocker JU,Lam CH,Vlasov Y A(2011)Technologies for exascale systems.IBM J Res Develop55(5):14:1–14:12.https:///10.1147/JRD.2011.2163967Cruz EHM,Alves MAZ,Navaux POA(2010)Process mapping based on memory access traces.In:Symposium on computing systems(WSCAD-SCC),pp72–79Cruz E,Alves M,Carissimi A,Navaux P,Ribeiro C,Mehaut J(2011)Using memory access traces to map threads and data on hierarchical multi-core platforms.In:IEEE international symposium on parallel and distributed processing workshops and Phd forum(IPDPSW)Cruz EHM,Diener M,Navaux POA(2012)Using the translation lookaside buffer to map threads in parallel applications based on shared memory.In:IEEE international parallel&distributed processing symposium(IPDPS),pp532–543.https:///10.1109/IPDPS.2012.56Cruz EHM,Diener M,Alves MAZ,Navaux POA(2014)Dynamic thread mapping of shared memory applications by exploiting cache coherence protocols.J Parallel Distrib Comput 74(3):2215–2228.https:///10.1016/j.jpdc.2013.11.006Cruz EHM,Diener M,Navaux POA(2015a)Communication-aware thread mapping using the translation lookaside buffer.Concurr Comput Pract Exp22(6):685–701Cruz EHM,Diener M,Pilla LL,Navaux POA(2015b)An efficient algorithm for communication-based task mapping.In:International conference on parallel,distributed,and network-based processing(PDP),pp207–214Cruz EH,Diener M,Alves MA,Pilla LL,Navaux PO(2016a)Lapt:a locality-aware page table for thread and data mapping.Parallel Comput54(C):59–71./10.1016/j.parco.2015.12.001Cruz EHM,Diener M,Pilla LL,Navaux POA(2016b)A sharing-aware memory management unit for online mapping in multi-core architectures.In:Euro-par parallel processing,pp659–671.https:///10.1007/978-3-319-43659-3Cruz EHM,Diener M,Pilla LL,Navaux POA(2016c)Hardware-assisted thread and data mapping in hierarchical multicore architectures.ACM Trans Archit Code Optim13(3):1–25.https://doi.org/10.1145/2975587Dashti M,Fedorova A,Funston J,Gaud F,Lachaize R,Lepers B,Quéma V,Roth M(2013)Traffic management:a holistic approach to memory placement on NUMA systems.In:Architectural support for programming languages and operating systems(ASPLOS),pp381–393Diener M,Madruga FL,Rodrigues ER,Alves MAZ,Navaux POA(2010)Evaluating thread placement based on memory access patterns for multi-core processors.In:IEEE international conference on high performance computing and communications(HPCC),pp491–496.http:// /10.1109/HPCC.2010.114Diener M,Cruz EHM,Navaux POA(2013)Communication-based mapping using shared pages.In:IEEE international parallel&distributed processing symposium(IPDPS),pp700–711.https:///10.1109/IPDPS.2013.57Diener M,Cruz EHM,Navaux POA,Busse A,HeißHU(2014)kMAF:automatic kernel-level management of thread and data affinity.In:International conference on parallel architectures and compilation techniques(PACT),pp277–288Diener M,Cruz EHM,Navaux POA,Busse A,HeißHU(2015a)Communication-aware process and thread mapping using online communication detection.Parallel Comput43(March):43–63 Diener M,Cruz EHM,Pilla LL,Dupros F,Navaux POA(2015b)Characterizing communi-cation and page usage of parallel applications for thread and data mapping.Perform Eval 88–89(June):18–36Diener M,Cruz EHM,Alves MAZ,Navaux POA,Koren I(2016)Affinity-based thread and data mapping in shared memory systems.ACM Comput Surv49(4):64:1–64:38./10.1145/3006385Dupros F,Aochi H,Ducellier A,Komatitsch D,Roman J(2008)Exploiting intensive multi-threading for the efficient simulation of3d seismic wave propagation.In:IEEE international conference on computational science and engineering(CSE),pp253–260.https:///10.1109/CSE.2008.51Feliu J,Sahuquillo J,Petit S,Duato J(2012)Understanding cache hierarchy contention in CMPs to improve job scheduling.In:International parallel and distributed processing symposium (IPDPS).https:///10.1109/IPDPS.2012.54Gabriel E,Fagg GE,Bosilca G,Angskun T,Dongarra JJ,Squyres JM,Sahay V,Kambadur P, Barrett B,Lumsdaine A(2004)Open MPI:goals,concept,and design of a next generation MPI implementation.In:Recent advances in parallel virtual machine and message passing interface Gennaro ID,Pellegrini A,Quaglia F(2016)OS-based NUMA optimization:tackling the case of truly multi-thread applications with non-partitioned virtual page accesses.In:IEEE/ACM international symposium on cluster,cloud,and grid computing(CCGRID),pp291–300.https:// /10.1109/CCGrid.2016.91Intel(2008)Quad-core Intel R Xeon R processor5400series datasheet.Tech.Rep.,March.http:// /assets/PDF/datasheet/318589.pdfIntel(2010a)Intel R Itanium R architecture software developer’s manual.Tech.Rep.Intel(2010b)Intel R Xeon R processor7500series.Tech.Rep.,MarchIntel(2012)2nd generation Intel core processor family.Tech.Rep.,SeptemberJin H,Frumkin M,Yan J(1999)The OpenMP implementation of NAS parallel benchmarks and its performance.Tech.Rep.,October,NASAJohnson M,McCraw H,Moore S,Mucci P,Nelson J,Terpstra D,Weaver V,Mohan T(2012) PAPI-V:performance monitoring for virtual machines.In:International conference on parallel processing workshops(ICPPW),pp194–199.https:///10.1109/ICPPW.2012.29Klug T,Ott M,Weidendorfer J,Trinitis C(2008)Autopin—automated optimization of thread-to-core pinning on multicore systems.High Perform Embed Archit Compilers3(4):219–235 LaRowe RP,Holliday MA,Ellis CS(1992)An analysis of dynamic page placement on a NUMA multiprocessor.ACM SIGMETRICS Perform Eval Rev20(1):23–34Löf H,Holmgren S(2005)Affinity-on-next-touch:increasing the performance of an industrial PDE solver on a cc-NUMA system.In:International conference on supercomputing(SC), pp387–392Magnusson P,Christensson M,Eskilson J,Forsgren D,Hallberg G,Hogberg J,Larsson F,Moestedt A,Werner B(2002)Simics:a full system simulation platform.IEEE Comput35(2):50–58.https:///10.1109/2.982916Marathe J,Mueller F(2006)Hardware profile-guided automatic page placement for ccNUMA systems.In:ACM SIGPLAN symposium on principles and practice of parallel programming (PPoPP),pp90–99Marathe J,Thakkar V,Mueller F(2010)Feedback-directed page placement for ccNUMA via hardware-generated memory traces.J Parallel Distrib Comput70(12):1204–1219Martin MMK,Hill MD,Sorin DJ(2012)Why on-chip cache coherence is here to mun ACM55(7):78.https:///10.1145/2209249.2209269Nethercote N,Seward J(2007)Valgrind:a framework for heavyweight dynamic binary instrumen-tation.In:ACM SIGPLAN conference on programming language design and implementation (PLDI)OpenMP(2013)OpenMP application program interface.Tech.Rep.,JulyPatel A,Afram F,Chen S,Ghose K(2011)MARSSx86:a full system simulator for x86CPUs.In: Design automation conference2011(DAC’11)Piccoli G,Santos HN,Rodrigues RE,Pousa C,Borin E,Quintão Pereira FM,Magno F(2014) Compiler support for selective page migration in NUMA architectures.In:International conference on parallel architectures and compilation techniques(PACT),pp369–380Radojkovi´c P,Cakarevi´c V,VerdúJ,Pajuelo A,Cazorla FJ,Nemirovsky M,Valero M(2013) Thread assignment of multithreaded network applications in multicore/multithreaded proces-sors.IEEE Trans Parallel Distrib Syst24(12):2513–2525Ribeiro CP,Méhaut JF,Carissimi A,Castro M,Fernandes LG(2009)Memory affinity for hierar-chical shared memory multiprocessors.In:International symposium on computer architecture and high performance computing(SBAC-PAD),pp59–66Ribeiro CP,Castro M,Méhaut JF,Carissimi A(2011)Improving memory affinity of geophysics applications on numa platforms using minas.In:International conference on high performance computing for computational science(VECPAR)Shwartsman S,Mihocka D(2008)Virtualization without direct execution or jitting:designing a portable virtual machine infrastructure.In:International symposium on computer architecture (ISCA),BeijingSwamy T,Ubal R(2014)Multi2sim4.2–a compilation and simulation framework for hetero-geneous computing.In:International conference on architectural support for programming languages and operating systems(ASPLOS)Tanenbaum AS(2007)Modern operating systems,3rd edn.Prentice Hall Press,Upper Saddle RiverTerboven C,an Mey D,Schmidl D,Jin H,Reichstein T(2008)Data and thread affinity in OpenMP programs.In:Workshop on memory access on future processors:a solved problem?(MAW), pp377–384.https:///10.1145/1366219.1366222Tikir MM,Hollingsworth JK(2008)Hardware monitors for dynamic page migration.J Parallel and Distrib Comput68(9):1186–1200Tolentino M,Cameron K(2012)The optimist,the pessimist,and the global race to exascale in20 megawatts.IEEE Comput45(1):95–97Torrellas J(2009)Architectures for extreme-scale computing.IEEE Comput42(11):28–35 Verghese B,Devine S,Gupta A,Rosenblum M(1996)OS support for improving data locality on CC-NUMA compute servers.Tech.Rep.,FebruaryVillavieja C,Karakostas V,Vilanova L,Etsion Y,Ramirez A,Mendelson A,Navarro N,Cristal A,Unsal OS(2011)DiDi:mitigating the performance impact of TLB Shootdowns using a shared TLB directory.In:International conference on parallel architectures and compilation techniques(PACT),pp340–349.https:///10.1109/PACT.2011.65Wang W,Dey T,Mars J,Tang L,Davidson JW,Soffa ML(2012)Performance analysis of thread mappings with a holistic view of the hardware resources.In:IEEE International symposium on performance analysis of systems&software(ISPASS)Woodacre M,Robb D,Roe D,Feind K(2005)The SGI Altix3000global shared-memory architecture.Tech.Rep.Zhou X,Chen W,Zheng W(2009)Cache sharing management for performance fairness in chip multiprocessors.In:International conference on parallel architectures and compilation techniques(PACT),pp384–393.https:///10.1109/PACT.2009.40Ziakas D,Baum A,Maddox RA,Safranek RJ(2010)Intel quickpath interconnect-architectural features supporting scalable system architectures.In:Symposium on high performance inter-connects(HOTI),pp1–6。

第15章Unix/常用的小型机及其操作系统【本章提要】小型机及其操作系统介绍Unix操作系统及其管理本章主要介绍当今几种主流的小型机及相关的Unix操作系统。

作为对Linux 部分的补充,本章还介绍了Unix/Linux的文件管理、用户管理、设备管理等系统管理内容,把可以在Linux操作系统部分介绍的NFS服务器也放在了此处介绍。

15.1 小型机计算机从处理能力上可以分为:大型机、中型机、小型机和微型机。

当前小型机在大中型公司的使用比较普遍,一般小型机具有以下特征:CPU为64bit芯片,一般采用RISC结构操作系统一般为专用UNIX操作系统;硬件性能很高性能参数包括内存容量,内存总线位数,系统总线带宽与外频,CPU运算速度,CPU和内存的扩展性,二级缓存大小,自适应和热插拔性能以及系统的安全性等,这些参数值大部分都优于微型机。

目前比较有影响的RISC处理器产品有HP公司的Alpha和PA-RISC、IBM公司的Power PC、MIPS公司的MIPS和Sun公司的SPARC。

下面介绍三种应用最广的小型机。

15.1.1 HP小型机HP把它的所有服务器产品分成了六大类,它们分别是:ProLiant和tc系列、高扩充型(Superdome Server)系列、AlphaServer系列、机架式服务器系列、NonStop 容错服务器系列和刀片式服务器系列。

1. ProLiant和tc系列ProLiant和tc系列服务器是HP服务器领域的一个最大系列,其中的产品特别多,但所有的产品均属于工业标准服务器类型,特别适用于中小企业选用。

这类服务器基本上都采用IA处理器架构(目前也有采用AMD X86-64 架构的)、所采用的操作系统也是常见的Windows、Linux和Netware。

这类服务器的性价是最高的,但其稳定性等方面相对UNIX服务器要稍差些。

在这个系列中,服务器的档次从入门级到企业级一应俱有;服务器也是包括塔式、机架式和刀片式这三种服务器结构。

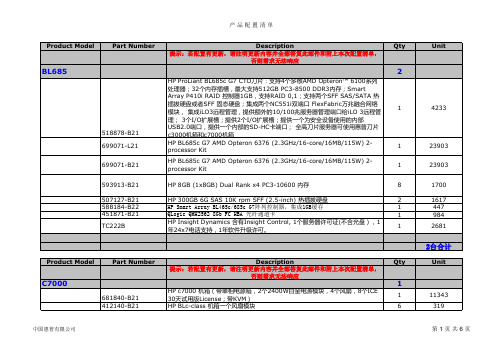

高端服务器推荐配置:配置一:主板:超微MBD-X9QR7-TF+11900.00x1=11900.00 Intel 至强E5 系列Single socket R (LGA 2011)Intel C602 chipset Intel X540 Dual port 10GBase-T32个D3 REG ECC 1600MHz槽,最高支持1TCPU:Intel Xeon E5-2630L 4500.00x4=18000.00 服务器CPU 主频:2000MHz 核心数量:六核心线程数量:12 L3缓存:15MB 制作工艺:32纳米工作功率:60W 架构:64位类型:至强系列:Xeon E5-2600系列CPU散热器:纯铜自适应风扇LGA2011 650.00x4=2700.00机箱:超微SC733TQ-665B+电源2850.00x1=2850.00 塔式主板:12英寸x13英寸E-ATX 硬盘位:4个3.5英寸SAS/SATA硬盘位热插拔系统:散热系统:1×120mmPWM后方排气扇1×90mm PWM气扇电源类型:665W电源80PLUS供电前置接口:2*USB 2.0 机箱尺寸:427*178*531mmI/O扩展位4×LED指示灯开关/Reset开关机箱重量:18.2kg金士顿8GB DDR3 1333(Reg ECC) 950.00x6=5700.00 希捷Barracuda 2TB 7200转64MB SATA3 600.00x1=600.00 合计:41750.00 注:Intel的八核还没有上市。

配置二:主板: 泰安S8812WGM3NR 8800.00 x1=8800.00 主芯片组:AMD SR5690 集成芯片:显卡/网卡/声卡CPU种类:Opteron 6100 插槽:Socket G34 数量:4颗32个800/1066/1PCI插槽:1×PCI-E Gen.2 x16电源插口:两个八针,一个24针网络芯片:板载Intel 82574L/I SATA接口:SATA II(3.0 Gb/s)USB接口:7×USB2.0接口图形芯片:Aspeed AST2050CPU: AMD 八核皓龙6128 2550.00x4=10200.00 类型:Socket G34 主频:2000MHz 核心数量:八核心L2缓存:512KB×8 L3缓存:12MB 制作工艺:45纳米工作功率:80W CPU内核:Magny-Cours 内存控制器:支持四通道LV 和U/RDDR3,-1333..虚拟化技术:AMD VTCPU系列:Opteron 6000系列CPU散热器:纯铜自适应风扇G34 650.00x4=2700.00机箱:超微SC733TQ-665B+电源2850.00x1=2850.00 塔式主板:12英寸x13英寸E-ATX 硬盘位:4个3.5英寸SAS/SATA硬盘位热插拔系统:散热系统:1×120mmPWM后方排气扇1×90mm PWM气扇电源类型:665W电源80PLUS供电前置接口:2*USB 2.0 机箱尺寸:427*178*531mmI/O扩展位4×LED指示灯开关/Reset开关机箱重量:18.2kg金士顿8GB DDR3 1333(Reg ECC) 950.00x6=5700.00 希捷Barracuda 2TB 7200转64MB SATA3 600.00x1=600.00 合计:30850.00。

AMD全球首推8/12核心处理器Opteron 6100系列AMD今天正式发布了全新一代Opteron 6100系列服务器处理器产品,这也是全球首批8核心以及12核心x86处理器,主要面向双路和四路服务器市场。

一、新的封装形式Opteron 6100系列处理器开发代号“马尼库尔”(Magny-Cours),基于两颗六核心“伊斯坦布尔”(Istanbul),并采用新的1944针Socket G34封装接口,不过非核心(Uncore)部分发生了很大变化:内存控制器升级支持标准D DR3-1333和低压LV-DDR3-1333,并且为了控制缓存一致性做了多方面的增强。

内存方面,Opteron 6100内部的节点拥有两个DDR3通道,整个处理器支持四通道内存,理论峰值带宽42.7GB/s,不过北桥速度只有1.8GHz,因此两个64位北桥合力带宽也不过28.8GB/s,这也是为了保持功耗的代价。

下图就是12核心Opteron 6100处理器的结构简图,其中红色虚线代表四个内存通道,蓝线代表内部HT缓存一致性连接,灰线代表外部缓存HT连接,绿线代表非一致性I/O HT连接,其中粗线是HT x16带宽、细线是HT x8带宽。

Opteron 6100系列采用了第二代直连架构(DAC 2.0),每个处理器内部的两个内核(Die)或称节点(Node)之间拥有多达24条HT总线直接相连,完全不存在带宽瓶颈问题,优于Intel当年通过外部前端总线(FSB)连接两个内核的做法。

下边就是Opteron 6100处理器在单路和双路情况下的互联情况,限于篇幅这里不再详述(可参考这里)。

二、型号与规格Opteron 6100处理器采用GlobalFoundries 45nm SOI工艺制造,每个内核/节点的核心面积为346平方毫米,总共集成18.08亿个晶体管,一级缓存每核心64+64KB,二级缓存每核心512KB,三级缓存共享12MB,支持四条HT 3.0 x16总线,每连接最高带宽6.4GT/s,支持四通道LV & U/R DDR3,-1333内存,每通道最多三条内存条,每处理器最多12条,支持AMD -V虚拟化技术。

Opteron 6100系列处理器首批型号共有十款,其中8核心、12核心各五款,主频1.7-2.3GHz不等,平均处理器功耗(ACP)有65W(HE)、80W、10 5W(SE)三种,价格455-1386美元,具体如下:Opteron 6176 SE实物图:三、功耗Opteron 6100系列处理器支持多种节能技术,包括全局性的CoolSpeed、管理内核的PowerNow!、管理缓存的SmartFetch、管理HT总线连接和内存控制器的C1E。

C1E模式只有在所有核心均长期处于完全空闲状态的时候才能达到,此时一级和二级缓存中的所有数据都转移到三级缓存之中,然后所有核心进行时钟门控(Clock Gated),HT总线连接和芯片组也随之转入低功耗状态。

在双路配置中两颗处理器要么都是C1E模式,要么都不是。

C1E模式之下,核心时钟关闭(时钟门控C1状态),三级缓存、北桥和内存控制器时钟频率分离,所有的HT总线连接转入LS2低功耗状态(LDT_STOP_L),DRAM DLL关闭。

按照AMD的说法,六核心Opteron 2425 HE 2.1GHz/55W在满负载下的功耗是215W,而核心数量翻番的Opteron 6164 HE 1.7GHz/65W 满载功耗也不过225W,只增加了区区4%。

两颗Opteron 6174 2.2GHz/ 80W在同样的双路系统上实测满载功耗为263W。

四、芯片组与未来规划Opteron 6100系列处理器搭配的芯片组是SR56x0系列北桥芯片、SP510 0南桥芯片,前者采用台积电65nm工艺制造,29×29mm FCBGA封装,最大热设计功耗13W,空闲功耗7.5/7.3/7.1W,分为SR5690、SR5670、SR5650三款型号,支持HT 3.0总线(最大带宽5.2GT/s)、PCI-E 2.0总线、可分别提供42/30/22条PCI-E连接,支持AMD-VI(IOMMU 1.2)虚拟化技术,并支持多种错误纠正和隔离技术。

SP5100南桥采用台积电0.13微米工艺制造,21×21mm 528-ball FCBGA 封装,最大热设计功耗4W,空闲功耗1W,支持12个USB 2.0和2个USB 1.1接口、PCI 2.3总线、6个SATA 3Gbps接口(可独立屏蔽)、支持Dot Hill RAID组建软件磁盘阵列。

Opteron 6100系列处理器加上SR56x0+SP5100芯片组构成了AMD的新一代服务器平台“马拉内罗”(Maranello),稍后还会有代号“里斯本”(Lisbon)的4/6核心处理器Opteron 4100系列,使用Socket C32封装接口,加上芯片组构成新平台“圣马力诺”(San Marino)和“阿德莱德”(Adelaide),面向单路和双路市场。

等到2011年,备受瞩目的全新架构“推土机”(Bulldoz er)终将面世,处理器有代号“英特拉格斯”(Interlagos)的12/16核心Opteron 6200系列和“巴伦西亚”(Valencia)的6/8核心Opteron 4200系列,分别继续使用Socket G34和Socket C32接口,向下兼容。

Opteron 6100系列不仅是全球首批8核心以及12核心处理器,也是AMD全新服务器时代的开端,代表着AMD服务器市场策略的一次转变。

等到Optero n 4100系列跟进推出后,AMD服务器平台将会使用这种双平台齐头并进的方式,重新规划单路、双路、四路乃至八路市场。

AMD Opteron 6100平台已经获得广泛的行业支持,Cray、SGI、宏碁、惠普、戴尔等OME厂商都会陆续推出基于新平台的服务器系统。

六核心的选择:伊斯坦布尔AMD最新推出的代号“伊斯坦布尔(Istanbul)”的六核心服务器,是四核Shanghai的即用型升级版产品,其可使现有的AMD服务器每平方英尺、每BTU、每分贝和每千瓦的工作负载能力将提升50%。

采用直连架构的原生六核心设计,适合双路、四路、八路服务器市场,支持AMD-V虚拟化技术和AMD-P电源管理技术套装,继续采用Socket F 1207平台和低价高能效DDR2内存架构,性能每瓦特相比上代四核心“上海”最多提升34%。

图3 将原有系统直接升级为伊斯坦布尔处理器,可带来性能的直接提升在技术特性上,AMD伊斯坦布尔处理器充分利用了现有的平台基础架构以及低成本、高能效的DDR2内存,有助于降低系统的采购成本;高性能计算、虚拟化和数据库工作负载等将从提升高达60%的4P STREAM内存带宽中受益匪浅,这归功于超传输总线HT Assist技术,它可以帮助降低处理器到处理器之间的延迟和数据流量;AMD虚拟化技术(AMD-V)和AMD-P套件电源管理特性广泛应用于各个性能和功耗段,确保客户不会面对性能和功耗的两难选择。

AMD在6月1日正式发布了面向服务器的Opteron 2400(适合2路系统,平均TDP功耗75W)/8400(适合4路和8路系统,平均TDP功耗115W)系列,这次发布的Istanbul六核Opteron新增加了一项名为Hyper Transport Assist的功能,其可以通过BIOS关闭在多路服务器中,当某个CPU运行的时候可能会需要另一个CPU本地缓存中的数据,其功能是可保存全部缓存的索引并阻止不必要的同步请求,大大降低HT总线的繁忙度。

而Shanghai四核Opteron对每个CPU采用“广播”的方法来发送信号,查看其他CPU中是否有本地缓存请求的数据。

Cray、戴尔、惠普、IBM、Sun等OEM厂商,已开始提供基于AMD六核皓龙处理器的系统,同时该处理器还得到了主板和基础架构合作伙伴的支持。

近期,AMD还发布了五款新的六核心“伊斯坦布尔”服务器处理器,包括三款55W低功耗的Opteron 2400 HE系列,以及两款105W高性能的Opteron 8400 SE系列。

55W的六核心Opteron HE包含两款面向双路领域的Opteron 2423/2425 HE 和一款面向四路/八路市场的Opteron 8425 HE,规格方面45nm SOI工艺制造,Socket F接口,主频2.0/2.1/2.1GHz,二级缓存6×512KB,三级缓存6MB,HT 总线频率4.8GHz,核心电压1.3V,最高温度55-76℃。

支持“Socket F(1207)”插槽。

可从现有四核处理器“Quad-Core AMD Opteron”轻松升级,单位功耗的处理性能最大可提高18%。

105W的Opteron 2439/8439 SE主频均达到了2.8GHz,除了最高温度55-71℃之外其他规格均相同。

AMD称这次发布的HE版本比标准版的性能功耗比高出18%左右,而六核心的SE版本比4核心的Shanghai性能提升了50%。

AMD Opteron 8439SE/8425HE/2439SE/2425HE/2423HE的售价分别为2649/1514/1019/523/455美元,直折合人民币分别为18099/10344/6962/3573/3108元。

总之,在完全相同的平台上,与前一代四核处理器相比,新款AMD六核皓龙处理器的每瓦性能提高达34%。

AMD新六核皓龙处理器满足了对降低总体拥有成本、更高的每瓦性能和可扩展性的不断增长的综合需求。

AMD六核皓龙处理器能为用户以最简单有效的方式带来最高的性能。

相关处理器报价图4 Opteron 2435处理器AMD高级副总裁:最好的CPU+最好的GPU=APU2010年可能是近10年来PC核心架构发生变化最大的一年,Intel率先在1月推出了集成了GPU(图形逻辑)的全新酷睿处理器i5及i3,而更早实行了PC 核心融合战略"Fusion"的AMD,也迫不及待的宣布了全新“APU”产品,虽然问世时间会较晚,但APU的CPU+GPU融合方式更为彻底。

就让我们来一起看看AMD高级副总裁兼技术事业部总经理Chekib Akrout先生是如何诠释APU的。

-----------------------------------------------------------------------------------------------2010年2月1日下午,北京融科中心AMD公司的会议室内,AMD高级副总裁兼技术事业部总经理Chekib Akrout先生给国内的媒体带来了处理器产品线上的最新进展--“APU”,APU是AMD将于2011年投向市场的全新产品类型,它是现有CPU和GPU产品的深度融合,AMD计划用APU来开创桌面、移动以及企业多个领域的全新格局。