CMOS常见的设置方法

- 格式:pdf

- 大小:134.88 KB

- 文档页数:3

CMOS设置什么是CMOS?CMOS是Complementary Metal-Oxide-Semiconductor的缩写,中文译为互补金属氧化物半导体。

它通常用于计算机硬件中的一种技术,用于存储和提供系统设置。

CMOS芯片的作用CMOS芯片是计算机主板上的一块芯片,其主要作用是存储BIOS设置和控制计算机的基础配置。

它也负责管理系统的实时时钟(RTC)和保存密码等敏感信息。

如何进入CMOS设置要进入CMOS设置,首先需要重启计算机。

当计算机重新启动时,按下指定的按键,通常是Del键、F1键或F2键,以进入BIOS设置界面。

在BIOS设置界面中,可以找到相关的设置选项,包括系统时间和日期、启动顺序、CPU和内存设置等。

CMOS设置的常见选项以下是CMOS设置中常见的选项:1.系统时间和日期设置:用于设置计算机的当前时间和日期。

通常可以手动设置或从操作系统同步。

2.引导顺序设置:用于设置系统启动时按照何种顺序检测和选择启动设备。

可以选择从硬盘、光盘、USB设备或网络启动。

3.CPU和内存设置:用于设置CPU频率、电压、内存频率和电压等。

这些设置需要根据硬件规格和性能需求进行调整。

4.硬盘设置:用于设置硬盘驱动器的参数,包括IDE模式、AHCI模式和RAID模式等。

B设置:用于启用或禁用USB接口,以及设置USB设备的优先级。

6.安全设置:用于设置系统密码、启用或禁用启动密码、管理系统访问权限等安全选项。

7.电源管理设置:用于设置系统的电源管理选项,包括睡眠模式、关机时间、电源管理模式等。

CMOS设置的注意事项在修改CMOS设置之前,需要注意以下几点:1.谨慎修改:修改CMOS设置可能会对计算机的正常运行产生影响,因此在修改设置之前,最好备份当前的设置,以便在需要时恢复到以前的状态。

2.了解硬件规格:在修改CPU和内存设置时,需要了解硬件的规格和处理器的支持频率,以避免超频或不当的设置。

3.遵循制造商建议:在修改CMOS设置时,建议参考计算机制造商的建议和文档,以确保正确的设置和最佳的性能。

CMOS设置(教案)课题:CMOS设置时间:2课时教学目标:1.掌握CMOS基本设置(时间,日期,硬盘主从盘,软驱)2.了解启动盘的先后顺序,密码设置(用户密码,超级用户密码)3.掌握CMOS的恢复默认设置,退出保存(不保存)等教学重点:1.CMOS基本设置S的恢复默认设置,退出,保存等教学难点:1.密码设置2.硬盘的主从盘讲授方法:多媒体演示法教学内容:一、如何进入CMOS设置1.三种主板CMOS:AW ARD,PHOENIX,AMI2.CMOS的概念3.CMOS的进入方法:开机按DEL,F1,F2,或ESC键,根据不同的主板确定二、标准CMOS设置1.System Date:设置系统的日期2.System Time:设置系统的时间3.硬盘主从盘(Master 主,Slave从)4.软驱设置(Drive A/B)5.Halt on:系统加电自检出现错误信息三、高级CMOS设置BOOT DEVICE SELECT :开机启动顺序(主要用于操作系统设置成CDROM)四、恢复默认设置(所做操作全部取消还原到系统原先设置)五、载入CMOS默认设置(保存所操作的选项)六、密码设置1.用户密码设置(SET USER PASSWORD):按ENTER输入密码,再确认;如需要去除密码,只须在该选项按三下ENTER2.超级用户密码(SET SUPERVISOR PASSWORD):操作与用户密码一样,但特别注意是:在SECURITY OPTION中把SETUP 改成SYSTEM七、SA VE AND EXIT(保存退出)八、EXIT WITHOUT SA VING(保存不退出)九、清除CMOS 参数1.硬件:拔电池2.软件debug。

电脑进入cmos及设置cmos方法介绍你还在为不知道电脑进入cmos及设置cmos方法介绍而烦恼么?接下来是小编为大家收集的电脑进入cmos及设置cmos方法介绍,希望能帮到大家。

电脑进入cmos及设置cmos方法介绍在开机后,当显示屏有显示信号出现时,按下键盘上的PAUSE键,并仔细察看显示信息中关于进入CMOS的提示,如还未出现,则可以按ENTER键,继续开机进程,并当CMOS提示出现时,随时按下PAUSE键,在察看即可.如果按DEL没反应按F2进入,除了IBM的是按F1以外!其他的都应该是F2或DEL,不过有些杂牌的是按其他的进入有的需要按「CTRL」+「S」,筆記型電腦有的則是按「F2」(如ASUS),IBM電腦則是按「F12」,所以要看看你的電腦為何~ CMOS是微机主板上的一块可读写的芯片,用来保存当前系统的硬件配置和用户对某些参数的设定。

进入CMOS设置有三种基本方法:(1)开机启动时按热键:在开机时按下特定组合键可以进入设置,不同类型的机器的热键不同,有些会在屏幕上给出提示例如按DEL键、按CTRL+ALT+ESC组合键等。

(2)系统提供的软件:现在很多主板提供DOS下对系统设置信息进行管理的程序,而Windows95中已经包含了诸如节能保护、电源管理等功能。

3)可以读写CMOS的应用软件:一些应用程序(如QAPLUS)提供对CMOS的读、写、修改功能,通过它们可以对一些基本系统设置进行修改。

开启计算机或重新启动计算机后,在屏幕显示“Waiting……”时,按下“Del”键就可以进入CMOS的设置界面。

要注意的是,如果按得太晚,计算机将会启动系统,这时只有重新启动计算机了。

大家可在开机后立刻按住Delete键直到进入CMOS。

进入后,你可以用方向键移动光标选择CMOS设置界面上的选项,然后按Enter进入副选单,用ESC键来返回父菜单,用PAGE UP和PAGE DOWN键来选择具体选项,F10键保留并退出BIOS设置。

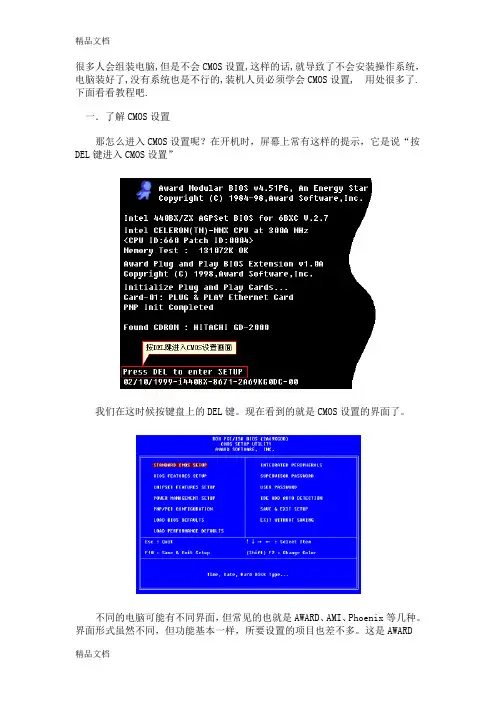

很多人会组装电脑,但是不会CMOS设置,这样的话,就导致了不会安装操作系统,电脑装好了,没有系统也是不行的,装机人员必须学会CMOS设置, 用处很多了.下面看看教程吧.一.了解CMOS设置那怎么进入CMOS设置呢?在开机时,屏幕上常有这样的提示,它是说“按DEL键进入CMOS设置”我们在这时候按键盘上的DEL键。

现在看到的就是CMOS设置的界面了。

不同的电脑可能有不同界面,但常见的也就是AWARD、AMI、Phoenix等几种。

界面形式虽然不同,但功能基本一样,所要设置的项目也差不多。

这是AWARD的CMOS设置画面,是最常见的一种。

其实你只要明白了一种CMOS的设置方法,其它的就可以触类旁通了。

在主界面的下面有很多个参数需要设置,大部分项目本来就已经设置了正确的参数值,或者说许多选项对电脑的运行影响不太大,所以一般我们只要注意几个关键项就可以了。

通常,我在设置CMOS时,只简单地做以下几步:1、设置出厂设定值2、检测硬盘参数3、设置软驱4、设置启动顺序5、如果有必要可以设置密码二、设置出厂设定值第一步:设置出厂设定值。

你看,这一项“LOAD SETUP DEFAULTS”是“调入出厂设定值”的意思,实际上就是推荐设置,即在一般情况下的优化设置。

将光标用上下箭头移到这一项,然后回车,屏幕提示“是否载入默认值”。

我们输入“Y”表示“Ye s,是”的意思,这样,以上几十项设置都是默认值了。

如果在这种设置下,你的电脑出现异常现象,可以用另外这项“Load BIOS Setup” 用来恢复 BIOS 默认值,它是最基本的也是最安全的设置,这种设置下不会出现设置问题,但有可能电脑性能就不能得到最充分的发挥。

三、自动检测硬盘第二步:自动检测硬盘。

将光标移到这一项,回车,电脑自动检测硬盘。

这是电脑检测到的硬盘参数。

这是电脑检测到了主硬盘,它可以以三种方式设置:如果你的硬盘是6.4G 的话,选NORMAL模式你只能用到528M;选LARGE模式,只能用到2.1GB;而实际使用中我们都选LBA 模式。

电脑如何进入cmos,设置cmos方法篇一:如何进入电脑CMOS设置如何进入电脑CMOS设置如果是兼容台式电脑,并且是Award、AMI、Phoenix公司的BIOS设置程序,那么开机后按Delete键或小键盘上的Del键就可以进入CMOS设置界面。

如果是品牌机(包括台式电脑或笔记本电脑),如果按Delete 不能进入CMOS,那么就要看开机后电脑屏幕上的提示,一般是出现【Press XXX to Enter SETUP】,我们就按“XXX”键就可以进入CMOS 了。

如果没有如何提示,就要查看电脑的使用说明书。

如果实在找不到,那么就试一试下面的这些品牌机常用的键:“F2”,“F10”,“F12”,“Ctrl+F10”,“Ctrl+Alt+F8”,“Ctrl+Alt+Esc”等。

电脑CMOS设置具体操作方法一、进入CMOS设置界面开启计算机或重新启动计算机后,在屏幕显示“Waiting??”时,按下“Del”键就可以进入CMOS的设置界面。

要注意的是,如果按得太晚,计算机将会启动系统,这时只有重新启动计算机了。

大家可在开机后立刻按住Del键直到进入CMOS。

进入后,你可以用方向键移动光标选择CMOS设置界面上的选项,然后按Enter进入副选单。

二、设置日期我们可以通过修改CMOS设置来修改计算机时间。

选择第一个标准CMOS设定(Standard CMOS Setup),按Enter进入标准设定界面,CMOS中的日期的格式为,除星期是由计算机根据日期来计算以外,其它的可以依次移动光标用数字键输入,如今天是6月1日,你可以将它改为6月2日。

当然,你也可以用PageUp/Page Down来修改。

三、设置启动顺序如果我们要安装新的操作系统,一般情况下须将计算机的启动顺序改为先由软盘(A)启动或光盘(CD-ROM)启动。

选择CMOS主界面中的第二个选项BIOS特性设定(BIOS Features Setup),将光标移到启动顺序项(Boot Sequence),然后用PageUp或PageDown选择修改,其中A表示从软盘启动,C表示从硬盘启动,CD-ROM表示从光盘启动,SCSI表示从SCSI设备启动,启动顺序按照它的排列来决定,谁在前,就从谁最先启动。

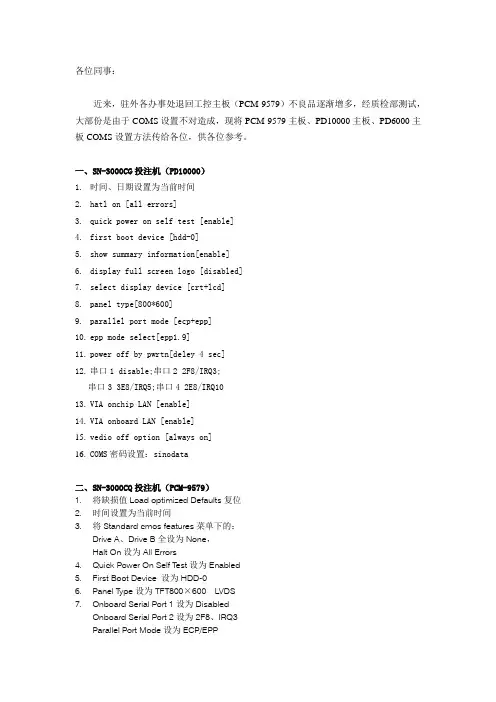

各位同事:近来,驻外各办事处退回工控主板(PCM-9579)不良品逐渐增多,经质检部测试,大部份是由于COMS设置不对造成,现将PCM-9579主板、PD10000主板、PD6000主板COMS设置方法传给各位,供各位参考。

一、SN-3000CG投注机(PD10000)1.时间、日期设置为当前时间2.hatl on [all errors]3.quick power on self test [enable]4.first boot device [hdd-0]5.show summary information[enable]6.display full screen logo [disabled]7.select display device [crt+lcd]8.panel type[800*600]9.parallel port mode [ecp+epp]10.epp mode select[epp1.9]11.power off by pwrtn[deley 4 sec]12.串口1 disable;串口2 2F8/IRQ3;串口3 3E8/IRQ5;串口4 2E8/IRQ1013.VIA onchip LAN [enable]14.VIA onboard LAN [enable]15.vedio off option [always on]S密码设置:sinodata二、SN-3000CQ投注机(PCM-9579)1.将缺损值Load optimized Defaults复位2.时间设置为当前时间3.将Standard cmos features菜单下的:Drive A、Drive B全设为None,Halt On设为All Errors4.Quick Power On Self Test设为Enabled5.First Boot Device 设为HDD-06.Panel Type设为TFT800×600LVDS7.Onboard Serial Port 1设为DisabledOnboard Serial Port 2设为2F8、IRQ3Parallel Port Mode设为ECP/EPPOnboard Serial Port 3设为3E8Serial port 3 USE IRQ设为IRQ5Onboard Serial Port 4设为2E8Serial Port 4 USE IRQ设为IRQ10三、SN-3000CL(PD6000)1.时间、日期设置为当前时间、日期2.halt on [ALL Errors]3.quick power on selt test [enable]4.first boot device [hdd-0]5.show summary information[enable]6.display full screen logo [disabled]7.select display device [crt+lcd]8.panel type[640*480]9.parallel port mode [ecp+epp]10.epp mode select[epp1.9]11.vedio off option[always on]12.power off by pwrtn[deley 4 sec]13.串口1 3F8/IRQ4;串口2 2F8/IRQ3B keyboard support[disabled]15.Set supervisor password(密码设置):sinodata。

CMOS设置经典技巧对于大多数用户来说,了解如何正确配置CMOS设置可以带来许多优势。

下面是一些经典的CMOS设置技巧,有助于提高计算机性能和用户体验。

1.配置系统时间和日期:在CMOS设置中,您应该始终确保系统时间和日期的准确性。

这对于一些应用程序和操作系统功能(如文件时间戳)是非常重要的。

2.设定启动设备顺序:在CMOS设置中,您可以设置计算机的启动设备顺序,以确定计算机在启动时首先查找的设备。

您可以通过将主引导硬盘设置为第一启动设备,以提高计算机的启动速度。

这将确保计算机首先加载操作系统而不是其他设备。

3.设置CPU时钟速度:大多数计算机允许用户通过CMOS设置更改CPU的时钟速度。

在一些情况下,您可能需要更改这些设置以提高计算机性能或适应特定的应用程序需求。

然而,一般用户应该小心调整这些设置,以免对系统稳定性造成负面影响。

4.改变内存配置:您可以使用CMOS设置配置计算机上的安装内存。

在一些情况下,您可能需要添加或删除内存模块,以便更好地适应您的计算需求。

CMOS设置允许您更改内存配置,以确保计算机正确地识别和使用可用的内存。

5.配置硬盘模式:在CMOS设置中,您可以配置硬盘模式,以确定计算机识别硬盘和访问数据的方式。

IDE和AHCI是两种常见的硬盘模式。

IDE模式较旧,适用于IDE接口硬盘,而AHCI模式更现代,支持SATA接口硬盘,它具有更快的传输速度和更多的功能。

6.启用或禁用主板集成设备:在CMOS设置中,您可以启用或禁用主板上的各种集成设备,如音频,网络和USB控制器。

这在一些情况下是必要的,例如当您使用独立的音频或网络卡,或者当您想限制特定的USB设备连接。

7.设置密码保护:在CMOS设置中,您可以设置BIOS密码来保护计算机免受未经授权的访问。

密码保护可确保只有授权的用户才能更改系统配置,从而提高计算机的安全性。

总之,熟悉和正确配置CMOS设置可以提高计算机性能和用户体验。

如何正确地设置CMOS做以下几步:1、设置出厂设定值2、检测硬盘参数3、设置软驱4、设置启动顺序5、如果有必要可以设置密码第一、设置出厂设定值。

你看,这一项“LOAD SETUP DEFAULTS”是“调入出厂设定值”的意思,实际上就是推荐设置,即在一般情况下的优化设置。

将光标用上下箭头移到这一项,然后回车,屏幕提示“是否载入默认值”。

我们输入“Y”表示“Yes,是”的意思,这样,以上几十项设置都是默认值了。

如果在这种设置下,你的电脑出现异常现象,可以用另外这项“Load BIOS Setup” 用来恢复 BIOS 默认值,它是最基本的也是最安全的设置,这种设置下不会出现设置问题,但有可能电脑性能就不能得到最充分的发挥。

第二、自动检测硬盘。

将光标移到这一项,回车,电脑自动检测硬盘。

这是电脑检测到的硬盘参数。

这是电脑检测到了主硬盘,它可以以三种方式设置:如果你的硬盘是6.4G的话,选NORMAL模式你只能用到528M;选LARGE模式,只能用到2.1GB;而实际使用中我们都选LBA 模式。

选“Y”这是电脑的推荐选项。

你看,主硬盘参数设置好了。

因为这台电脑只有一个硬盘,所以下面我们就按ESC键,取消检测。

这台电脑能接四个IDE设备,简单的说可以接四个硬盘,它们分别是这四种接法。

通常,我们只有一个硬盘,一般设置为第一种,其它的就略过。

如果我有两个硬盘,那么接着再像这样设置一下就可以用了。

设置完硬盘后,我们先按ESC键退出硬盘检测项,你看,回到了刚才的主设置画面。

第三、设置软驱。

将光标移到第一项STANDARD CMOS SETUP上,按回车。

这是日期、时间。

现在我们可以调节它们。

这是硬盘情况,刚才我们检测到的硬盘参数在这里可以看到,这时只有一个硬盘,4335M,有时我们安装了多个硬盘时,想去掉一个硬盘,就要在这里操作,将光标移动到这里,然后按Page up,将其选择为NONE即可。

这是软驱设置。

你看,这台电脑只有一个1.44M软驱,我们就把光标移到这一项,按“Page Up”和“Page Down”键来改变。

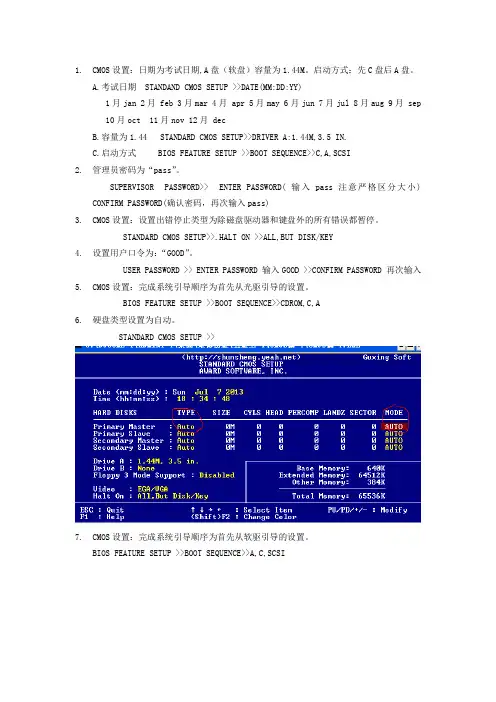

1.CMOS设置:日期为考试日期,A盘(软盘)容量为1.44M。

启动方式:先C盘后A盘。

A.考试日期 STANDAND CMOS SETUP >>DATE(MM:DD:YY)1月jan 2月 feb 3月mar 4月 apr 5月may 6月jun 7月jul 8月aug 9月 sep 10月oct 11月nov 12月 decB.容量为1.44 STANDARD CMOS SETUP>>DRIVER A:1.44M,3.5 IN.C.启动方式 BIOS FEATURE SETUP >>BOOT SEQUENCE>>C,A,SCSI2.管理员密码为“pass”。

SUPERVISOR PASSWORD>> ENTER PASSWORD( 输入pass注意严格区分大小) CONFIRM PASSWORD(确认密码,再次输入pass)3.CMOS设置:设置出错停止类型为除磁盘驱动器和键盘外的所有错误都暂停。

STANDARD CMOS SETUP>>.HALT ON >>ALL,BUT DISK/KEY4.设置用户口令为:“GOOD”。

USER PASSWORD >> ENTER PASSWORD 输入GOOD >>CONFIRM PASSWORD 再次输入5.CMOS设置:完成系统引导顺序为首先从光驱引导的设置。

BIOS FEATURE SETUP >>BOOT SEQUENCE>>CDROM,C,A6.硬盘类型设置为自动。

STANDARD CMOS SETUP >>7.CMOS设置:完成系统引导顺序为首先从软驱引导的设置。

BIOS FEATURE SETUP >>BOOT SEQUENCE>>A,C,SCSI8.在自动检测硬盘中选取自动模式(或LBA模式)。

CMOS设置图解2007-10-16 20:52CMOS设置图解分类:电脑知识Award Bios和AMI Bios里面有很多东西是相同的,可以说基本上是一样的,虽然有些名字叫法不同,但是实际作用是一样的。

在前文中已经了解了一些Bios 的基本知识,和设置,那么在这篇文章里面我就会更详细的介绍一下Bios的超频设置,希望对那些想超频但是又没有接错过超频的玩家能有一些帮助。

和AMI Bios一样,再开机画面时按下“Del”键进入Bios设置菜单(有些是按F1键),如图:进入后大家会看到以下菜单,也有可能会有一些差别,但是基本上是差不多的,及算名字不同,但是基本上作用是一样的!大家可以用方向键移动光标,回车键确认,ESC键返回,用PageUp,PageDown 和数字键键调整设置,在任何设置菜单中可以按下F10键退出并保存设置,这些都和AMI Bios设置差不多!那么就正是进入设置!一.SoftMenu Setup(软超频设置)其实这个Soft Menu Setup,是升技主板独有的技术,这里提供了丰富的CPU外频、倍频调节(需要CPU支持)、AGP/PCI总线频率以及CPU/内存/AGP的电压调节频率等等。

这个项目相当于一些主板中的“Frequency/Voltage Control”前面是CPU的一些基本信息显示,下面的选项就是CPU超频的主要选项了!1. CPU Operating Speed(CPU外频设置):这个项目根据你所使用的处理器型式以及速度来显示该处理器的运作速度,您可以选择[User Define](使用者设定)的选项来手动输入其运作速度。

如图:好了,到了这里我就先放下Bios的设置引导了,在教大家超频之前先向大家解释一下什么叫超频以及超频的原理吧,这样才能让你能更好的进入下一步Bios设置超频!CPU超频,它的主要目的是为了提高CPU的工作频率,也就是CPU的主频。

而CPU的主频又是外频(FSB)和倍频(Multiplier Factor)的乘积。

完全CMOS设置图解教程CMOS设置直接关系到电脑的性能,甚至影响到您的设备能否正常使用。

或许您已经会使用一些简单CMOS设置,比如设置启动驱动器,改变倍频等等,但这些是远远不够的,想要让你的电脑发挥出最优性能,首先我们就要彻底的了解CMOS设置的基础知识。

那么下面这篇CMOS 设置图解教程就可以让您轻松的掌握这些知识。

一.进入CMOS Setup设置在打开计算机电源后的几秒钟的时间内,电脑首先进行POST(Power On Self Test,开机自检),在这个时候按下“Del”键后,就可以看到下图所示的CMOS Setup主菜单。

在主菜单中你可以选择不同的设置选项,按上下左右方向键来选择,按“Enter”键进入子菜单。

1.功能键说明(向上键)移到上一个选项(向下键)移到下一个选项(向左键)移到左边的选项(向右键)移到右边的选项Enter键选择当前项目Esc键回到主画面,或从主画面中结束Setup程序Page Up或+键改变设置状态,或增加栏位中的数值内容Page Down或-键改变设置状态,或减少栏位中的数值内容F1功能键显示目前设置项目的相关说明F5功能键装载上一次设置的值F6功能键装载最安全的值F7功能键装载最优化的值F10功能键储存设置值并离开CMOS Setup程序2.子菜单说明请注意设置菜单中各项内容.如果菜单项左边有一个三角形的指示符号,表示若选择了该项子菜单,将会有一个子菜单弹出来.3.辅助说明当你在Setup主画面时,随着选项的移动,下面显示相应选项的主要设置内容。

当你在设置各个栏位的内容时,只要按下“F1”,便可得到该栏位的设置预设值及所有可以的设置值,如BIOS缺省值或CMOS Setup缺省值。

如果想离开辅助说明窗口,只须按“Esc”键即可。

二.Standard CMOS Features(标准CMOS功能设置)在Standard CMOS Features中,主要是为了设置IDE硬盘的种类,以顺利开机,除此之外,还要设置日期、时间、软驱规格及显示卡的种类。

完全CMOS设置图解教程(1)CMOS设置直接关系到电脑的性能,甚至影响到您的设备能否正常使用。

或许您已经会使用一些简单CMOS设置,比如设置启动驱动器,改变倍频等等,但这些是远远不够的,想要让你的电脑发挥出最优性能,首先我们就要彻底的了解CMOS设置的基础知识。

那么下面这篇CMOS设置图解教程就可以让您轻松的掌握这些知识。

一.进入CMOS Setup设置在打开计算机电源后的几秒钟的时间内,电脑首先进行POST(Power On Self Test,开机自检),在这个时候按下“Del”键后,就可以看到下图所示的CMOS Setup主菜单。

在主菜单中你可以选择不同的设置选项,按上下左右方向键来选择,按“Enter”键进入子菜单。

1.功能键说明(向上键)移到上一个选项(向下键)移到下一个选项(向左键)移到左边的选项(向右键)移到右边的选项Enter键选择当前项目Esc键回到主画面,或从主画面中结束Setup程序Page Up或+键改变设置状态,或增加栏位中的数值内容Page Down或-键改变设置状态,或减少栏位中的数值内容F1功能键显示目前设置项目的相关说明F5功能键装载上一次设置的值F6功能键装载最安全的值F7功能键装载最优化的值F10功能键储存设置值并离开CMOS Setup程序2.子菜单说明请注意设置菜单中各项内容.如果菜单项左边有一个三角形的指示符号,表示若选择了该项子菜单,将会有一个子菜单弹出来.3.辅助说明当你在Setup主画面时,随着选项的移动,下面显示相应选项的主要设置内容。

当你在设置各个栏位的内容时,只要按下“F1”,便可得到该栏位的设置预设值及所有可以的设置值,如BIOS缺省值或CMOS Setup缺省值。

如果想离开辅助说明窗口,只须按“Esc”键即可。

二.Standard CMOS Features(标准CMOS功能设置)在Standard CMOS Features中,主要是为了设置IDE硬盘的种类,以顺利开机,除此之外,还要设置日期、时间、软驱规格及显示卡的种类。

电脑CMOS设置1. STANDARD CMOS SETUP(标准CMOS设置)硬盘工作模式:λ★(1)NORMAL模式这是原有的IDE方式。

在此方式下对硬盘访问时,BIOS和IDE控制器对参数不作任何转换。

在该模式下支持的最大柱面数为1024,最大磁头数为16,最大扇区数为63,每一扇区的字节数为512。

因此支持最大硬盘容量为:512*63*16*1024=528MB。

即使硬盘的实际容量大于528MB时,可访问的硬盘空间也只能是528MB。

★(2)LBA(Logical Block Addressing)模式这种模式管理的硬盘空间可达8.4GB。

在该模式下设置的柱面、磁头、扇区等参数并不是实际硬盘的物理参数。

在硬盘工作时,由IDE控制器把由柱面、磁头、扇区等参数确定的逻辑地址转换为实际硬盘的物理地址。

在该模式下,可设置的最大磁头数是255,其余参数与普通模式相同。

★(3)LARGE大硬盘模式当硬盘的柱面超过1024而又不为LBA支持时可采用此种模式。

LARGE模式采取的方法是把柱面数除以2,磁头数乘以2,其结果总容量不变。

该模式支持的最大容量为1GB。

★(4)AUTO系统自动选择硬盘模式硬盘的参数设置非常重要,特别是柱面数和磁头数等参数,如果设置错误,将可能导致系统不能正常使用。

λHalt On-All Errors(BIOS检测到任何错误,系统启动暂停并给出出错信息)-No Errors(BIOS检测到任何错误都不使系统启动暂停)-All But Keyboard(BIOS检测到除键盘以外所有错误后使系统启动暂停)-All But Diskette(BIOS检测除磁盘以外所有错误后使系统启动暂停)-All But Disk/key(BIOS检测到除磁盘和键盘以外错误后使系统启动暂停)2. BIOS FEATURES SETUP(BIOS功能设定)λVirus Warning(病毒警告功能)本项设置值为Enabled时,在系统启动和工作时,任何个性系统引导扇区或者分区表的操作都将使系统挂起并且给出下列警告信息“WARNING,Disk Boot sector is to be modified,Type “Y” accept write or “N”to abort write”,此时键入“Y”才能写入,而键入“N”则无法写入。

系统维护员教程

一、CMOS的设置

1、进入CMOS设置,当开机后屏幕出现提示时,一般情况下是按下DEL键,具体按什么键,请看屏幕提示。

这里提示:F2键进入CMOS设置,F12键为网络启动,ESC键为引导设置,假如我们只进行引导设置,在这里就按ESC键就行了,如还要进行其他的设置,则要按F2键。

⑴假如我们这里只进行引导盘设置,当出现提示时,按ESC键,会出现以下选择。

这里的各项意思是:1、从可移动设备启动,比如U盘等。

2、从硬盘启动。

3、从光盘启动。

4、从网络启动。

这里我们是从光盘安装操作系统,所以选3从光盘启动。

⑵假如我们要进入CMOS设置,在前面,我们就按F2进入以下界面。

设置完成后,要记得点YES保存。

二、系统的安装

1、将引导设置成从光盘启动

这里直接选择1即可。

了。

CMOS常见的设置方法

时间:2012-10-10 15:10来源:未知作者:优优系统点击:1704次

CMOS是微机主板上的一块可读写的RAM芯片,主要用来保存当前系统的硬件配置和操作人员对某些参数的设定。

CMOS RAM芯片由系统通过一块后备电池供电,因此无论是在关机状态中,还是遇到系统掉电情况,CMOS信息都不会丢失。

CMOS设置方法:

一、进入CMOS设置界面

开启计算机或重新启动计算机后,在屏幕显示“Waiting……”时,按下“Del”键就可以进入CMOS的设置界面。

要注意的是,如果按得太晚,计算机将会启动系统,这时只有重新启动计算机了。

大家可在开机后立刻按住Del键直到进入CMOS。

进入后,你可以用方向键移动光标选择CMOS 设置界面上的选项,然后按Enter进入副选单。

二、设置日期

我们可以通过修改CMOS设置来修改计算机时间。

选择第一个标准CMOS设定(Standard CMOS Setup),按Enter进入标准设定界面,CMOS 中的日期的格式为<星期><月份><日期><年份>,除星期是由计算机根据日期来计算以外,其它的可以依次移动光标用数字键输入,如今天是6月1日,你可以将它改为6月2日。

当然,你也可以用 Page

Up/Page Down来修改。

三、设置启动顺序

如果我们要安装新的操作系统,一般情况下须将计算机的启动顺序改为先由软盘(A)启动或光盘(CD-ROM)启动。

选择CMOS主界面中的第二个选项BIOS特性设定(BIOS Features Setup),将光标移到启动顺序项(Boot Sequence),然后用PageUp或PageDown选择修改,其中A表示从软盘启动,C表示从硬盘启动,CD-ROM表示从光盘启动,SCSI表示从SCSI设备启动,启动顺序按照它的排列来决定,谁在前,就从谁最先启动。

如C:CDROM,A,表示最先从硬盘启动,如果硬盘启动不了则从光盘启动,如果硬盘和光盘都无法启动则从A盘启动。

是不是很简单^_^在BIOS特性设定中,还有几个重要选项在这儿顺便讲一下:

①Quick Power On Self

Test(快速开机自检),当电脑加电开机的时候,主板BIOS会执行一连串的检查测试,检查的是系统和周边设备。

如果该项选择了Enabled,则BIOS将精简自检的步骤,以加快开机的速度。

②Boot Up Floppy

Seek(开机软驱检查),当电脑加电开机时,BIOS会检查软驱是否存

在。

选择Enabled时,如果BIOS不能检查到软驱,则会提示软驱错误。

选择Disabled,BIOS将会跳过这项测试。

③Boot UP NumLock

Status(启动数字键状态),一般情况下,小键盘(键盘右部)是作为数字键用的(默认为ON,启用小键盘为数字键),如果有特殊需要,只要将ON改成OFF,小键盘就变为方向键。

④安全选择(Security Option)

有两个选项,如果设置为Setup时,开机时不需要密码,进入CMOS 时就需要密码(当然事先要设置密码)了,但只有超级用户的密码才能对CMOS的各种参数进行更改,普通用户的密码不行。

如果设为System时,则开机时就需要密码(超级用户与普通用户密码都可以),到CMOS修改时,也只有超级用户的密码才有修改权。

四、设置CPU

CPU作为电脑的核心,在CMOS中有专项的设置。

在主界面中用方向键移动

到“<<>>”,此时我们就可以设置CPU的各种参数了。

在“Adjust CPU Voltage”中,设置CPU的核心电压。

如果要更改此值,用方向键移动到该项目,再用“Page UP/Page Down”或“+/-”来选择合适的核心电压。

然后用方向键移到“CPU Speed”,再用“Page UP/Page Down”或“+/-”来选择适用的倍频与外频。

注意,如果没有特殊需要,初学者最好不要随便更改CPU相关选项!

五、设置密码

CMOS中为用户提供了两种密码设置,即超级用户/普通用户口令设定(SUPERVISOR/USER PASSWORD)。

口令设定方式如下:

1.选择主界面中的“SUPERVISOR PASSWORD”,按下Enter键后,出现:Enter Password:(输入口令),

2.你输入的口令不能超过8个字符,屏幕不会显示输入的口令,输入完成按Enter键。

3.这时出现让你确认口令:“Confirm Password”(确认口令),输入你刚才输入的口令以确认,然后按Enter键,就设置好了。

普通用户口令与其设置一样,就不再多说了,如果您需要删除您先前设定的口令,只需选择此口令然后按Enter键即可(不要输入任何字符),这样你将删除你先前的所设的口令了。

超级用户与普通用户的密码的区别在于进入CMOS时,输入超级用户的密码可以对CMOS所有选项进行修改,而普通用户只能更改普通用户密码,而不能修改CMOS中的其它参数,联系在于当安全选择(Security

Option)设置为SYSTEM时,输入它们中任一个都可以开机。

六、设置硬盘参数

如果你要更换硬盘,安装好硬盘后,你要在CMOS中对硬盘参数进行设置。

CMOS中有自动检测硬盘参数的选项。

在主界面中选择“IDE HDD AUTO DETECTION”选项,然后按Enter键,CMOS将自动寻找硬盘参数并显示在屏幕上,其中SIZE为硬盘容量,单位是 MB;MODE为硬盘参数,第1种为NORMAL,第2种为LBA,第3种为LARGE。

我们在键盘上键入“Y”并回车确认。

接着,系统检测其余的三个IDE接口,如果检测到就会显示出来,你只要选择就可以了。

检测以后,自动回到主界面。

这时硬盘的信息会被自动写入主界面的第一个选项——标准CMOS设定

(STANDARD CMOS SETUP)中。

七、保存设置

我们所做的修改工作都要保存才能生效,要不然就会前功尽弃。

设置完成后,按ESC返回主界面,将光标移动到“SAVE & EXIT

SETUP”(存储并结束设定)来保存(或按F10键),按Enter后,选

择“Y”,就OK了。

(责任编辑:优优系统)。