集成电路版图设计的技巧

- 格式:pdf

- 大小:182.62 KB

- 文档页数:2

Layout主要工作注意事项●画之前的准备工作●与电路设计者的沟通●Layout 的金属线尤其是电源线、地线●保护环●衬底噪声●管子的匹配精度一、l ayout 之前的准备工作1、先估算芯片面积先分别计算各个电路模块的面积,然后再加上模块之间走线以及端口引出等的面积,即得到芯片总的面积。

2、Top-Down 设计流程先根据电路规模对版图进行整体布局,整体布局包括:主要单元的大小形状以及位置安排;电源和地线的布局;输入输出引脚的放置等;统计整个芯片的引脚个数,包括测试点也要确定好,严格确定每个模块的引脚属性,位置。

3、模块的方向应该与信号的流向一致每个模块一定按照确定好的引脚位置引出之间的连线4、保证主信号通道简单流畅,连线尽量短,少拐弯等。

5、不同模块的电源,地线分开,以防干扰,电源线的寄生电阻尽可能较小,避免各模块的电源电压不一致。

6、尽可能把电容电阻和大管子放在侧旁,利于提高电路的抗干扰能力。

二、与电路设计者的沟通搞清楚电路的结构和工作原理明确电路设计中对版图有特殊要求的地方包含内容:(1)确保金属线的宽度和引线孔的数目能够满足要求(各通路在典型情况和最坏情况的大小)尤其是电源线盒地线。

(2)差分对管,有源负载,电流镜,电容阵列等要求匹配良好的子模块。

(3)电路中MOS管,电阻电容对精度的要求。

(4)易受干扰的电压传输线,高频信号传输线。

三、layout 的金属线尤其是电源线,地线1、根据电路在最坏情况下的电流值来确定金属线的宽度以及接触孔的排列方式和数目,以避免电迁移。

电迁移效应:是指当传输电流过大时,电子碰撞金属原子,导致原子移位而使金属断线。

在接触孔周围,电流比较集中,电迁移更容易产生。

2、避免天线效应长金属(面积较大的金属)在刻蚀的时候,会吸引大量的电荷,这时如果该金属与管子栅相连,可能会在栅极形成高压,影响栅养化层质量,降低电路的可靠性和寿命。

解决方案:(1)插一个金属跳线来消除(在低层金属上的天线效应可以通过在顶层金属层插入短的跳线来消除)。

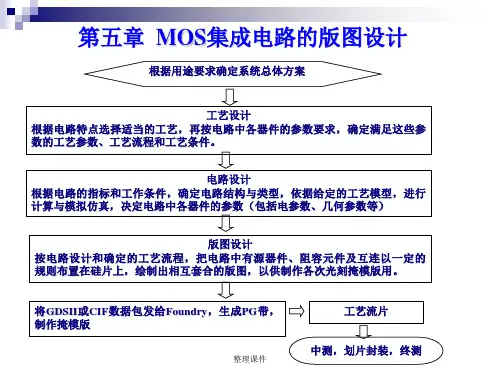

2023集成电路布图设计•集成电路布图设计概述•集成电路布图设计的制作流程•集成电路布图设计的实际应用•集成电路布图设计的前沿技术与发展趋势目•集成电路布图设计的挑战与解决方案•集成电路布图设计的案例分析录01集成电路布图设计概述集成电路布图设计,也称为集成电路设计,是指通过计算机辅助设计软件,将电路设计在半导体芯片上的一种方法。

定义集成电路布图设计具有高集成度、高可靠性、高性价比、低功耗等特点,是现代电子信息产业的基础。

特点定义与特点1集成电路布图设计的基本要素23根据功能需求,进行电路逻辑设计,确定各个元件之间的连接关系。

电路设计将电路设计转化为实际芯片版图,需要考虑芯片制造工艺和制程参数。

版图设计通过物理验证工具,对版图进行功能和性能验证,确保版图满足设计要求。

物理验证03促进产业发展集成电路布图设计的发展,促进了半导体产业的发展和壮大,推动了电子信息产业的进步。

集成电路布图设计的意义与作用01提高性能通过集成电路布图设计,可以将多个电子元件集成在一块芯片上,提高电路性能和可靠性。

02降低成本通过集成电路布图设计,可以减少电子设备的体积和成本,提高生产效率。

02集成电路布图设计的制作流程明确所设计集成电路的功能、性能和规格等要求,确定设计计划和方案。

明确设计目标选择合适的集成电路设计软件和工具,配置好所需的硬件和软件环境。

准备工具和环境熟悉所设计集成电路的相关规范、标准和工艺要求。

了解设计规范制作前的准备根据设计目标,选择合适的设计方案,包括芯片结构、功能模块、接口和信号等设计。

电路设计与仿真确定设计方案使用电路设计软件绘制集成电路的电路图。

电路图绘制利用电路仿真工具对所设计的电路进行模拟和调试,验证其功能和性能是否符合设计目标。

电路仿真与调试版图绘制使用布图设计软件,将电路图转化为集成电路版图。

选择工艺制程根据设计方案,选择合适的集成电路制造工艺制程。

版图验证与优化通过版图验证工具对版图进行检验、优化和修复错误。

集成电路设计综合实验报告班级:微电子学1201班姓名:学号:日期:2016年元月13日一.实验目的1、培养从版图提取电路的能力2、学习版图设计的方法和技巧3、复习和巩固基本的数字单元电路设计4、学习并掌握集成电路设计流程二.实验内容1. 反向提取给定电路模块(如下图所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。

2. 设计一个CMOS结构的二选一选择器。

(1)根据二选一选择器功能,分析其逻辑关系。

(2)根据其逻辑关系,构建CMOS结构的电路图。

(3)利用EDA工具画出其相应版图。

(4)利用几何设计规则文件进行在线DRC验证并修改版图。

三.实验原理1. 反向提取给定电路模块方法一:直接将版图整体提取(如下图)。

其缺点:过程繁杂,所提取的电路不够直观,不易很快分析出其电路原理及实现功能。

直接提取的整体电路结构图方法二:将版图作模块化提取,所提取的各个模块再生成symbol,最后将symbol按版图连接方式组合成完整电路结构(如下图)。

其优点:使电路结构更简洁直观、结构严谨、层次清晰,更易于分析其原理及所实现的功能。

CMOS反相器模块CMOS反相器的symbolCMOS传输门模块 CMOS传输门的symbolCMOS三态门模块 CMOS三态门的symbolCMOS与非门模块 CMOS与非门的symbol各模块symbol按版图连接方式组合而成的整体电路经分析可知,其为一个带使能端的D锁存器,逻辑功能如下:①当A=1,CP=0时,Q=D,Q—=D—;②当A=1,CP=1时,Q、Q—保持;③当A=0,Q=0,Q—=1。

2.CMOS结构的二选一选择器二选一选择器(mux2)的电路如图所示,它的逻辑功能是:①当sel=1时,选择输入A通过,Y=A;②当sel=0时,选择输入B通过,Y=B。

二选一选择器(mux2)由三个与非门(nand)和一个反相器(inv)构成(利用实验1 的与非门和反相器symbol即可)。

集成电路版图设计技巧分析与研究作者:杨志磊来源:《科学与财富》2018年第23期摘要:文章以提高集成电路版图设计能力与效率为目的,首先介绍了版图设计的根本原则以及设计方法存在的优缺点,其次阐述了集成电路版图设计流程,并且着重分析了设计技巧,重点在于如何更加高效的完成集成电路版图设计,为后续版图数据tape-out奠定基础。

关键词:集成电路版图;版图设计;设计技巧信息技术的发展推动了集成电路设计水平的提升,由于芯片面积和工艺尺寸的不断减小,使集成电路版图设计技巧方面面临非常严格的要求。

设计人员必须要对电路形式、参数设置以及应用场景等进行充分考虑,才能够满足设计需求。

但是版图工程师在进行集成电路版图设计的过程中,经常会面临一些问题,影响芯片的功能与性能。

为了保证集成电路版图设计的正确性和准确性,文章重点围绕设计技巧展开论述。

1 版图设计根本原则作为电路的设计人员,必须保证电路设计环节的紧凑型,以更快的效率完成产品设计。

版图设计主要涉及到几种不同的设计方式:如果以自动化程度为依据,版图设计分为人工设计、自动布局布线两种;如果以布局模块限制为依据,版图设计有全定制、半定制这两种类型[1]。

通常正式开始版图设计前,设计人员必须了解所使用的工艺文件及设计规则,将其作为设计的参考依据。

明确设计规则期间,要对掩膜对准以及非线性等因素进行全面考虑。

设计规则规定了各种图形所要满足的要求,然而各个企业所使用的工艺及设计规则存在很大差异,因此要解决这一问题,需要应用高级CAD工具,兼容各种工艺,便于设计版图。

自然其中也存在一些缺点,比如线性度的应用范围受限等,这些都对集成电路版图设计造成限制。

2 集成电路版图设计技巧2.1 整体规划设计针对集成电路版图设计,其中最为重要的就是整体设计(即top设计),直接关系到所有block所在位置以及布局布线。

整体布局设计方法和成型电路图相似度非常高,按照模块面积进行适当的调整,将其进行有效拼凑。

Cadnece版图设计技巧总结Cadence 版图设计技巧总结在集成电路设计领域,Cadence 版图设计是至关重要的环节。

它不仅关系到芯片的性能、功耗和可靠性,还直接影响到芯片的制造成本和生产周期。

对于版图设计师来说,掌握一些实用的技巧能够显著提高设计效率和质量。

接下来,就让我们一起深入探讨 Cadence 版图设计中的那些关键技巧。

一、布局规划良好的布局规划是成功版图设计的基础。

在开始设计之前,需要对整个芯片的功能模块进行合理划分,并确定它们之间的连接关系。

这有助于减少布线长度,降低寄生电容和电阻,从而提高芯片的性能。

首先,要考虑电源和地的分布。

电源和地网络应该尽可能地均匀分布,以减少电压降和噪声。

可以采用多层金属来构建电源和地的平面,以提供低阻抗的路径。

其次,对于高速信号线路,要尽量缩短其走线长度,并避免穿越其他信号密集区域。

同时,要注意信号之间的隔离,以防止串扰。

另外,在布局时还要预留足够的空间用于放置 ESD(静电放电)保护器件、测试结构和封装引脚等。

二、器件匹配在模拟和混合信号电路中,器件的匹配性对性能有着重要影响。

为了实现良好的匹配,需要遵循一些原则。

首先,将需要匹配的器件放置在相邻位置,并采用相同的方向。

这样可以减少由于工艺偏差引起的不匹配。

其次,对于对称的电路结构,要保持布局的对称性。

例如,差分放大器的两个晶体管应该具有相同的环境和布局。

此外,在布线时,要确保匹配器件的连线长度和宽度相同,并且走在相同的层次上。

三、布线策略布线是版图设计中的关键步骤之一。

合理的布线策略可以减少信号延迟、串扰和功耗。

对于电源线和地线,要使用较宽的金属线来降低电阻。

同时,要避免出现锐角和狭窄的通道,以防止电流集中和电迁移现象。

对于信号线,要根据信号的频率和特性选择合适的布线层次。

高频信号通常需要走在顶层金属层,以减少寄生电容。

在布线过程中,要注意控制走线的阻抗,以保证信号的完整性。

另外,要合理设置过孔的数量和位置。

集成电路版图技巧总结1、对敏感线的处理对敏感线来说,至少要做到的是在它的走线过程中尽量没有其他走线和它交叉。

因为走线上的信号必然会带来噪声,交错纠缠的走线会影响敏感线的信号。

对于要求比较高的敏感线,则需要做屏蔽。

具体的方法是,在它的上下左右都连金属线,这些线接地。

比如我用M3做敏感线,则上下用M2和M4重叠一层,左右用M3走,这些线均接地。

等于把它像电缆一样包起来。

2、匹配问题的解决电路中如果需要匹配,则要考虑对称性问题。

比如1:8的匹配,则可以做成33的矩阵,“1”的放在正中间,“8”的放在四周。

这样就是中心对称。

如果是2:5的匹配,则可以安排成AABABAA的矩阵。

需要匹配和对称的电路器件,摆放方向必须一致。

周围环境尽量一致。

3、噪声问题的处理噪声问题处理的最常用方法是在器件周围加保护环。

N mos管子做在衬底上因此周围的guardring是Pdiff,在版图上是一层PPLUS,上面加一层DIFF,用CONTACT连M1。

Pdiff接低电位。

Pmos管子做在NWELL里面因此周围的GUARDING是Ndiff,在版图上先一层NPLUS,上面加一层DIFF,用CONTACT连M1。

Ndiff接高电位。

在一个模块周围为了和其他模块隔离加的保护环,用一圈NWELL,里面加NDIFF,接高电位。

电阻看类型而定,做在P衬底上的周围接PDIFF型guarding接地;做在NWELL里面的则周围接NDIFF型guarding接高电位。

各种器件,包括管子,电容,电感,电阻都要接体电位。

如果不是RF型的MOS管,则一般尽量一排N管一排P管排列,每排或者一堆靠近的同类型管子做一圈GUARDING,在P管和N管之间有走线不方便打孔的可以空出来不打。

4、版图对称性当电路需要对称的时候,需要从走线复杂度,面积等方面综合考虑。

常见的对称实现方式:一般的,画好一半,折到另一半去,复制实现两边的对称。

如果对称性要求高的,可以用质心对称的方式,把管子拆分成两个,四个甚至更多。

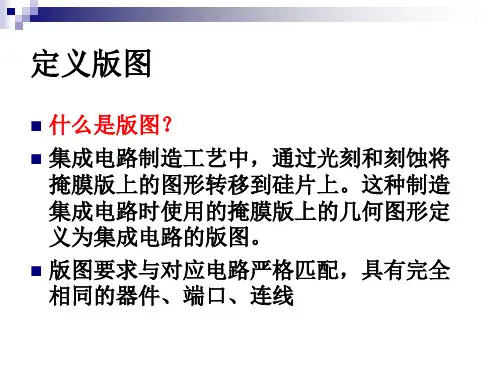

2023-11-04CATALOGUE目录•集成电路布图设计概述•集成电路布图设计的基本要素•集成电路布图设计的技巧和方法•集成电路布图设计的工具与平台•集成电路布图设计的挑战与解决方案•集成电路布图设计的应用案例01集成电路布图设计概述集成电路布图设计是指将电子器件及其连接关系以几何图形的方式在集成电路芯片上分布并按照一定规则布局的技术方案。

定义集成电路布图设计具有高度复杂性、精密性和集成性,要求设计者具备深厚的电子设计自动化(EDA)工具使用技能和专业知识。

特点定义与特点物理设计根据逻辑电路设计,进行布局布线、信号完整性分析等物理设计,生成可制造的版图文件。

设计输入明确设计需求,提供功能描述和性能参数等设计输入信息。

逻辑设计将功能描述转化为逻辑电路,进行功能仿真和调试。

版图验证对版图文件进行功能和性能验证,确保设计与制造的一致性。

制造与测试将版图文件交由半导体制造厂进行芯片制造,并进行测试与验证。

合理的布图设计可以优化芯片的性能、速度和功耗等方面的表现。

提高芯片性能降低制造成本推动产业发展通过优化布图设计,可以提高芯片的可制造性和良品率,降低制造成本。

集成电路布图设计是半导体产业的核心技术之一,对于推动产业发展具有重要意义。

03020102集成电路布图设计的基本要素确定芯片的功能和性能参数,进行逻辑门级设计,实现功能描述到逻辑电路的转换。

逻辑设计进行芯片的物理布局和布线设计,包括信号完整性、电源完整性、时序等。

物理设计通过仿真工具对设计的电路进行功能和性能验证,确保设计的正确性。

仿真验证将电路设计转换为版图设计,需要考虑工艺、制程等因素对电路性能的影响。

抽象层次使用版图编辑工具进行版图的绘制和编辑,实现电路到版图的转换。

版图编辑对版图进行质量检查和验证,确保版图的正确性和可制造性。

版图验证检查版图设计是否符合制造工艺的要求,确保版图的可制造性。

设计规则检查(DRC)分析版图布局对电路性能的影响,以及各种寄生效应对电路性能的影响。