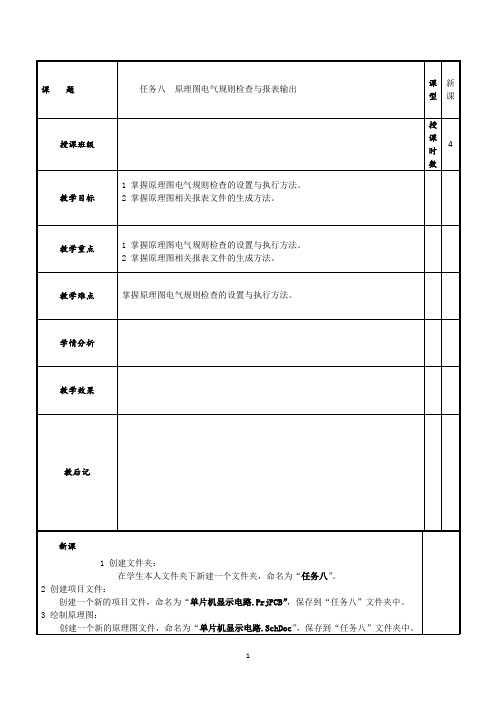

【精品课件】原理图电气规则检查及报表

- 格式:ppt

- 大小:901.00 KB

- 文档页数:36

用模块电路绘制该上层原理图,如图1所示。

图1 单片机显示电路.SchDoc利用层次原理图自上而下的设计方式,创建并绘制下层原理图,如图2、图3、图4、图5所示。

图2 时钟模块.SchDoc图3 复位模块.SchDoc图4 控制模块.SchDoc图5 显示模块.SchDoc4 执行电气规则检查(ERC):在原理图设计窗口中执行菜单命令Project/Project Options,将弹出“Options for PCB Project单片机显示电路.PrjPCB”对话框。

如图6所示图6 “Options for PCB Project 单片机显示电路.PrjPCB”对话框在该对话框的Error Reporting(错误报告)和Connection Matrix(连接矩阵)两个选项卡中进行电气规则设置,或单击按钮实现默认设置,设置完成单击OK按钮退出。

执行菜单命令“Project/Compile PCB Project单片机显示电路.PrjPCB”对整个项目编译查错。

在Massages窗口中查看错误报告并修改相关错误。

如系统提示为“warning”,可根据原理图中波浪线提示内容判断,若不认为是错误,则返回“Options for PCB Project 单片机显示电路.PrjPCB”对话框,找到相关选项进行报告模式“Report Mode”的设置,设置为“No Report”后,再重新进行原理图的编译查错,直到没有问题出现为止。

5 生成网络表文件:在原理图设计窗口中执行菜单命令Design/Netlist For Project/Protel ,系统则会生成当前整个项目的网络表文件,如图7所示图7 “单片机显示电路”网络表文件6 生成元器件清单报表:在原理图设计窗口中执行菜单命令Reports/ Bill of Materials,将会弹出如图8所示的元器件清单报表对话框。

单击“Export...”按钮,可将该报表以“.xls”格式文件保存。

原理图电气规则检查电路规则检查属于集成电路设计物理验证的一部分。

其主要目的是验证版图与电路原理图的电路结构是否一致。

电路设计者完成电路设计和仿真后交由版图设计者完成掩模工作。

确保所画版图与设计电路完全一致就是LVS工具要做的工作。

LVS检查的内容可以槪括为两点:①所有信号的电气连接关系是否一致;②器件类型尺寸是否一致。

LVS不是一个简单地将版图与电路原理图进行比较的过程,它需要分两步完成。

第—步“抽取”,第二步“比较”。

首先根据LVS提取规则,EDA工具从版图中抽取出版图所确定的网表文件;然后将抽取出的网表文件与电路网表文件进行比较。

需要说明的是:抽取的网表为晶体管级的SPICE网表,而电路网表为门级的Verilog网表,该门级网表需要结合SPICE模型/CDL模型转化为SPICE网表,才能与抽取的网表进行逻辑等效性比对。

如果两个网表的电路连接关系和器件完全一致则通过LVS检査。

反之,说明版图存在与电路不一致的地方,需要进行检査并加以处理或修改更正。

实现“抽取”的主要步骤是网表提取,它可以实现从版图提取网表,包含连接关系提取和器件提取两大模块。

连接关系提取模块的主要功能是标识线网和为线网命名。

标识线网是指把金属、通孔、多晶等半导体划分为不同的连通集合,从而生成不同的线网。

器件提取模块的主要功能是识别器件、计算器件属性和输出网表。

实现“比较“的步骤是网表比较,它包括网表预处理、版图和原理图网表比较。

网表预处理的主要工作是串并联结构约简,虚拟器件过滤,门电路识别等。

在版图设计中,宽长较大的MOS管通常会采用版图折叠的方法将其等效于多个晶体管的并联,所以为避免在检査器件数目和尺寸时发生错误,需要把版图中折叠的、并联或串联的器件合并成一个再进行比较。

而门电路结构可以作为一个整体对待,以此减少需要处理的节点数量。

完成网表预处理后,则可以开始进行网表比较。

网表比较本质上是图同构问题,图同构问题是一个NP完全问题。