开题报告模版-正弦信号发生器的设计

- 格式:doc

- 大小:306.50 KB

- 文档页数:7

毕业设计(论文)开题报告题目正弦信号发生器的FPGA设计专业光信息科学与技术班级光信072学生周力强指导教师杨秀芳2011 年一、毕业设计(论文)课题来源、类型本课题是在长期研究可编程逻辑技术及数字逻辑原理基础上提出的,通过对于FPGA及VHDL硬件描述语言的了解与研究,以及对于开发软件Quartus Ⅱ的掌握,所进行的正弦信号发生器的设计。

课题来源:自选课题。

课题类型:系统设计。

二、选题的目的及意义信号发生器是各种测试和实验过程中不可缺少的工具,在通信、测量、雷达、控制、教学等领域应用十分广泛。

不论是在生产、科研还是在数学上,信号发生器都是电子工程师信号仿真实验的最佳工具,而且,信号发生器的设计方法多,设计技术也越来越先进。

随着我国经济和科技的发展,对相应的测试仪器和测试手段提出了更高的要求,信号发生器已成为测试仪器中至关重要的一类,因此开发信号发生器具有重大意义。

本课题的目的是研究正弦信号发生器的设计方法,设计出具有调频、调幅功能的正弦信号发生器。

本文是以现场可编程门阵列(FPGA)作为硬件基础,先将所需要产生的正弦信号波形的一个周期的若干个采样点的二进制信息存储在波形存储器(ROM)中,再通过硬件电路依次从波形存储器中读取出来。

经数模转换以及滤波后得到正弦信号的波形。

三、本课题在国内外的研究状况及发展趋势正弦信号主要用于测量电路和系统的频率特性、非线性失真、增益及灵敏度等。

按频率覆盖范围分为低频信号发生器、高频信号发生器和微波信号发生器;按输出电平可调节范围和稳定度分为简易信号发生器(即信号源)、标准信号发生器(输出功率能准确地衰减到-100分贝毫瓦以下)和功率信号发生器(输出功率达数十毫瓦以上);按频率改变的方式分为调谐式信号发生器、扫频式信号发生器、程控式信号发生器和频率合成式信号发生器等。

信号发生器在电路实验和设备检测中具有十分广泛的用途。

例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。

《EDA技术》设计报告设计题目正弦信号发生器的设计院系:信息工程学院专业:通信工程____学号:姓名:__________一.设计任务及要求1.设计任务:利用实验箱上的D/A 转换器和示波器设计正弦波发生器,可以在示波器上观察到正弦波2.设计要求:(1) 用VHDL 编写正弦波扫描驱动电路(2)设计可以产生正弦波信号的电路(3)连接实验箱上的D/A 转换器和示波器,观察正弦波波形二.设计方案(1)设计能存储数据的ROM 模块,将正弦波的正弦信号数据存储在在ROM 中,通过地址发生器读取,将正弦波信号输入八位D/A 转化器,在示波器上观察波形(2)用VHDL 编写正弦波信号数据,将正弦波信号输入八位D/A 转化器,在示波器上观察波形三.设计框图图 1 设计框图信号发生器主要由以下几个部分构成:计数器用于对数据进行采样,ROM 用于存储待采样的波形幅度数值,TLV5620用于将采集的到正弦波数字量变为模拟量,最后通过示波器进行测量获得的波形。

其中,ROM 设置为7根地址线,8个数据位,8位并行输出。

TLV5260为串行输入的D/A 转换芯片,因此要把ROM 中并行输出的数据进行并转串。

四.实现步骤1.定制ROM计 数 器 7根地址线 8 位 R O M 并转串输出 CLKTLV5620D/A 转换RSTROM的数据位选择为8位,数据数选择128个。

利用megawizard plug-in manager定制正弦信号数据ROM宏功能块,并将上面的波形数据加载于此ROM中。

如图3所示。

图2 ROM存储的数据图3 调入ROM初始化数据文件并选择在系统读写功能2.设计顶层顶层设计主要是通过编写VHDL语言或设计原理图用于产生计数信号和调用room存储的数据并输出。

在此步骤里要建立EDA工程文件,工程文件结构如图4所示,SIN_CNT中的VHDL代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SIN_GNT ISPORT ( RST, CLK, EN : IN STD_LOGIC;ADDR : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END SIN_GNT;ARCHITECTURE BEHA VIOR OF SIN_GNT ISCOMPONENT ROM ISPORT ( address : IN STD_LOGIC_VECTOR(6 DOWNTO 0);inclock : IN STD_LOGIC;q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END COMPONENT;SIGNAL Q : STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINU : ROM PORT MAP ( address => Q,inclock => CLK,q => DOUT);PROCESS(CLK, RST, EN)BEGINIF RST = '0' THENQ <= "0000000";ELSIF CLK'EVENT AND CLK = '1' THENIF EN = '1' THENQ <= Q + 1;END IF;END IF;END PROCESS;ADDR <= Q;END BEHA VIOR;工程文件的建立步骤简述如下:1、新建一个文件夹。

摘要本正弦波发生器以FPGA为控制核心设计的,该系统主要由FPGA控制模块、STM32单片控制模块,按键输入模块、5110液晶显示模块、以AD9850为核心的DDS模块、运算放大电路和直流稳压电源组成。

FPGA运算速度较快,适用于强干扰和要求速度较高的场合。

仅用单片FPGA就实现了直接数字频率合成技术(DDS),产生稳幅正弦波,并在数字域实现了AM、FM、ASK、PSK等四类调制信号。

调制信号既可由用户输入参数由FPGA内部生成,整个系统结构紧凑,电路简单,功能强大,可扩展性强。

关键词: FPGA STM32 DDS AD9850AbstractThe sine wave generator is designed with FPGA as the core, the system is mainly controlled by FPGA module, STM32 monolithic control module, key input module, liquid crystal display module 5110, with a core of AD9850 DDS module, the operational amplifier circuit and a dc regulated power supply. FPGA faster calculation speed, is suitable for the strong interference and high speed required. Only with a single chip FPGA to realize the direct digital frequency synthesis (DDS) technology, to produce steady sine wave, and in the digital domain for AM, FM, ASK, PSK modulation signal. Modulation signal can be input by the user parameters are generated internally by the FPGA, the whole system structure is compact, the circuit is simple, powerful, strong extensibility.一、系统方案比较与论证根据题目要求,系统分为以下几个模块,各模块的实现方案选择如下:1.主控器件比较与选择方案一:采取FPGA它具有体积小、I/O口较多、编程改动灵活的特点、资源丰富、速度高,本晶振为50M,可以通过锁相环(PLL)任意倍频,在信号处理领域中应用广泛,并且稳定性强,为以后系统的升级,作品的商品化提供了保障。

《EDA》课程设计报告——正弦波信号发生器的设计一、设计目的:进一步熟悉QuartusII及其LPM_ROM与FPGA 硬件资源的使用方法。

培养动手能力以及合作能力。

二、设计要求:1、clk为12MHz。

2、通过DAC0832输出正弦波电压信号,电压范围0~-5V。

3、通过示波器观察波形。

三、设计内容:在QUARTUSII上完成正弦波信号发生器的设计,包括仿真和资源利用情况了解(假设利用Cyclone器件)。

最后在实验系统上实测,包括FPGA中ROM的在系统数据读写测试和利用示波器测试。

信号输出的D/A使用实验系统上的ADC0832。

四、设计原理:图1所示的正弦波信号发生器的结构由四部分组成:1、计数器或地址发生器(这里选择10位)。

2、正弦信号数据ROM(10位地址线,8位数据线),含有1024个8位数据(一个周期)。

3、VHDL顶层设计。

4、8位D/A(实验中可用ADC0832代替)。

图1所示的信号发生器结构图中,顶层文件singt.vhd在FPGA中实现,包含两个部分:ROM的地址信号发生器,由10位计数器担任;一个正弦数据ROM,由LPM_ROM模块构成。

LPM_ROM底层是FPGA 中的EAB、ESB或M4K等模块。

地址发生器的时钟clk的输入频率fo与每周期的波形数据点数(在此选择1024点),以及D/A输出的频率f的关系是:f=fo/1024图1 正弦信号发生器结构框图图2 正弦波信号发生器的设计图五、设计步骤:1、建立.mif格式文件首先,mif文件可用C语言程序生成,产生正弦波数值的C程序如下:#include<stdio.h>#include<math.h>main(){int i;float s;for(i=0;i<1024;i++){s=sin(atan(1)*8*i/256);printf("%d :%d;\n",i,(int)((s+1)*255/2)) }}其次,把上述程序编译后,在DOS命令行下执行命令:romgen > sdata.mif;将生成的sdata.mif 文件,再加上.mif文件的头部说明即可。

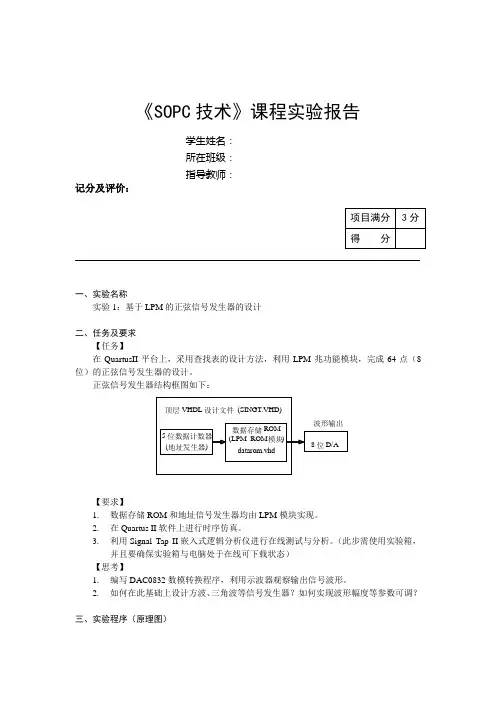

《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:记分及评价:一、实验名称实验1:基于LPM的正弦信号发生器的设计二、任务及要求【任务】在QuartusII平台上,采用查找表的设计方法,利用LPM兆功能模块,完成64点(8位)的正弦信号发生器的设计。

正弦信号发生器结构框图如下:【要求】1.数据存储ROM和地址信号发生器均由LPM模块实现。

2.在Quartus II软件上进行时序仿真。

3.利用Signal Tap II嵌入式逻辑分析仪进行在线测试与分析。

(此步需使用实验箱,并且要确保实验箱与电脑处于在线可下载状态)【思考】1.编写DAC0832数模转换程序,利用示波器观察输出信号波形。

2.如何在此基础上设计方波、三角波等信号发生器?如何实现波形幅度等参数可调?三、实验程序(原理图)VCCclkINPUT q[7..0]OUTPUT up counterclockq[5..0]aninst28 b i t s 64 w o r d saddress[5..0]inclock outclockq[7..0]rominst四、仿真及结果分析如图所示,在外部时钟clk 的驱动下,把采样值依次取出来送到输入端,周而复始的循环执行,输出的数据经过8位的D/A 转换成模拟信号,就得到了正弦波。

改变时钟频率就可以改变正弦波的频率。

五、硬件验证1、 选择模式:2、 引脚锁定情况表:六、小结本次实验是我们第一次接触FPGA ,做完还有许多不清楚的地方《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:记分及评价:一、实验名称实验2:基于DSP Builder正弦信号发生器的设计二、任务及要求【任务】采用DSP Builder系统建模的方法,设计正弦信号发生器,要求采用查找表的方法,完成正弦信号发生器模块的建模、仿真。

Signal Compiler【要求】:1.完成模型构建及仿真,得到如下波形图。

2. 将模型转换成VHDL 硬件描述语言,利用Modelsim 软件进行RTL 仿真。

正弦波信号发生器的设计摘要:从结构上看,正弦波振荡电路就是一个没有输入信号的带选频网络的正反馈放大电路。

分析RC串并联选频网络的特性,根据正弦波振荡电路的两个条件,即振幅平衡与相位平衡,来选择合适的放大电路指标,来构成一个完整的振荡电路。

很多应用中都要用到范围可调的 LC 振荡器,它能够在电路输出负载变化时提供近似恒定的频率、几乎无谐波的输出。

电路必须提供足够的增益才能使低阻抗的 LC 电路起振,并调整振荡的幅度,以提高频率稳定性,减小 THD(总谐波失真)。

关键词:正弦波;振荡电路;稳幅1 引言在实践中,广泛采用各种类型的信号产生电路,就其波形来说,可能是正弦波或非正弦波。

在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,这就需要能产生高频信号的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火,超声波焊接,超声诊断,核磁共振成像等,都需要功率或大或小、频率或高或低的振荡器。

可见,正弦波振荡电路在各个科学技术部门的应用是十分广泛的。

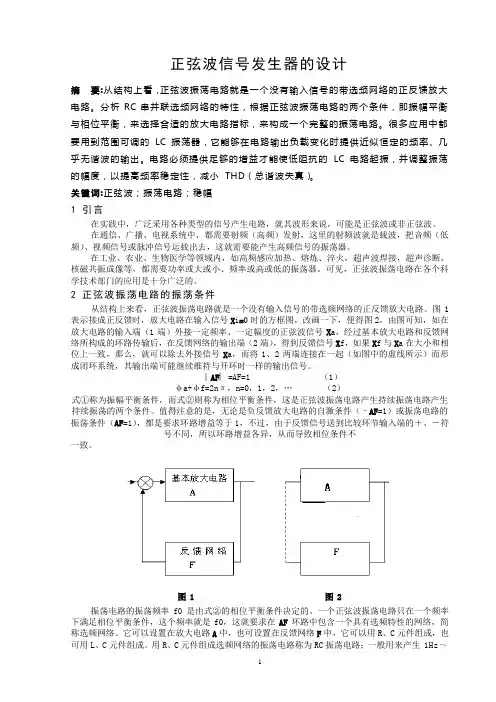

2正弦波振荡电路的振荡条件从结构上来看,正弦波振荡电路就是一个没有输入信号的带选频网络的正反馈放大电路。

图1表示接成正反馈时,放大电路在输入信号X i=0时的方框图,改画一下,便得图2。

由图可知,如在放大电路的输入端(1端)外接一定频率、一定幅度的正弦波信号X a,经过基本放大电路和反馈网络所构成的环路传输后,在反馈网络的输出端(2端),得到反馈信号X f,如果X f与X a在大小和相位上一致,那么,就可以除去外接信号X a,而将1、2两端连接在一起(如图中的虚线所示)而形成闭环系统,其输出端可能继续维持与开环时一样的输出信号。

︱AF︳=AF=1 (1)φa+φf=2nπ,n=0,1,2, (2)式①称为振幅平衡条件,而式②则称为相位平衡条件,这是正弦波振荡电路产生持续振荡电路产生持续振荡的两个条件。

电子技术课程设计课题名称: 低频正弦信号发生器班级: 32010803姓名:指导教师:日期: 2012年12月27号前言此次课程设计,我们组所选的题目是低频正弦信号发生器,它的要求如下:1.信号频率范围20HZ~20kHZ;2.输出信号电压幅度 5;3.输出信号频率数字显示;4.输出电压幅度数字显示。

根据题目的要求,我们根据所学的知识初步判断,这是一个数字电子技术与模拟电子技术相结合的题目,中间必然会用到数模之间的转换,很明显,我们要用的是A/D转换。

于是我们组就先将题目大致分成四个模块:正弦波的产生、正弦波幅值的调节、频率数字显示和幅度数字显示。

并根据手中已有的数字电子技术和模拟电子技术教材,在网上和图书馆中寻找我们需要的资料。

当资料收集的差不多的时候,就着手进行开始电路图的设计与仿真。

在工作的过程中,我们又发现所收集的资料与具体的操作中有出入,中途又几次在网上和图书馆中收集我们所欠缺的资料,最终经过一周多的时间完成了此次任务,也从中学到了很多。

由于时间仓促和我们水平的有限,其中不免会有不太合理的地方,请谅解。

目录前言 (2)摘要 (4)一、系统概述 (5)二、单元电路设计 (8)1、正弦波的产生模块 (8)2、正弦波的幅值调节模块 (13)3、正弦波的的频率数字显示模块 (14)4、正弦波的幅值数字显示模块 (18)三、参考文献 (22)四、鸣谢 (22)五、元器件明细表 (22)六、收获体会与存在问题 (23)七、评语 (25)低频正弦信号发生器摘要正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。

由数字电路构成的低频信号发生器,多是由一些芯片组成,其低频性能比模拟信号发生器好得多,并且体积较小,输出的信号谐波较少,频率和振幅相对比较稳定。

本文借助555定时器产生方波,再借助滤波电路,产生频率可调且输出稳定的正弦波。

开题报告电气工程及其自动化基于FPGA的DDS正弦波信号发生器设计一、课题研究意义及现状这些年来随着我国对超大规模集成电路的重视,也发表了许多关于DDS技术的论文,逐步走上了发展的道路,但是在这之中主要是利用DDS技术去实现功能的改进和对性能指标的提高,几乎是没有关于DDS芯片的设计和研发,因此我国在DDS的研究上与国际水平还是有很大的差距。

近几年来我国芯片产业的快速发展,对DDS的研究已经有了突破性的进展从而推动数字信号处理器的飞速发展,使微处理器具有先进的数字信号处理技术,能实现多种功能,对正弦波发生器而言,随着DDS技术的诞生,使波形发生器技术得到进一步的飞跃。

相对与其他频率合成技术,DDS技术产生的正弦波具有全数字化、输出频率精度高、波形失真小、频率稳定度高、分辨率高、输出相位连续可调、控制灵活方便、可产生宽带正交信号及其他多种调制信号以及等特点。

本次研究课题是基于FPGA的DDS正弦波发生器设计,现在FPGA的主流发展趋势就是在FPGA中嵌入可编程的低功耗、高速收发器,具有嵌入式高速收发器的FPGA为数据传输提供了可行的单芯片解决方案,能够快速地解决协议和速率的变化问题,以及为了提高性能和为产品增加新功能时所做的设计修改所需的重新编程问题。

本课题采用FPGA设计实现DDS电路的可行性和可靠性,也更为灵活,可以根据不同的需要对控制方式和接口进行相应的修改,要想使DDS电路产生正弦波形,只要对FPGA中ROM表的数据进行修改。

另外FPGA设计还具有相对较宽的带宽、频率转换时间较短、相位连续变化、频率分辨率高等优点。

同时FPGA芯片还可以对体统进行现场修改和调试,性能也使用要求,所以将DDS设计嵌入到FPGA片所构成的系统中,将使系统具有很高的性价比。

本次研究主要利用的是Quartus Ⅱ软件进行DDS正弦波信号发生器功能的实现进行编译,仿真,培养了自己的动手能力把理论和实际结合起来。

二、课题研究的主要内容和预期目标1.主要内容本次课题的主要内容就是采用DDS技术设计一个正弦波发生器,主控要求用FPGA实现。

模拟电路课程设计报告设计课题:信号发生器设计班级:10通信工程三班学生姓名:陶冬波学号:2010550921指导教师:设计时间:目录一、信号发生器摘要--------------------3二、设计目的---------------------3三、设计内容和要求四、设计方案------------------------------------------34.1 RC桥式正弦波产生电路--------------------------------------3 4.2方波产生电路----------------------------------------------------6 4.3三角波产生电路-------------------------------------------------84.4多用信号发生器-------------------------------------------------9五、组装调试及元件清单---------------------------105.1 测试仪器---------------------------------------------------------10 5.2信号发生器元件清单-----------------------------------------------115.3调试中出现的故障、原因及排除方法----------------------11六、总结设计电路,改进措施----------------------116.1 正弦波产生电路改进措施--------------------------------------116.2多用信号发生器改进措施---------------------------------------11七、收获和体会-----------------------------------------12八、参考文献--------------------------------------------12信号发生器设计一、信号发生器设计摘要:本设计介绍了波形发生器的制作和设计过程,并根据输出波形特性研究该电路的可行性。

正弦信号发生器设计报告摘要本系统主要由正弦信号发生模块、STC89C52单片机控制模块、LCD1602液晶显示模块和电源组成。

用AD9850信号发生模块实现了波形的输出,产生稳幅正弦波。

本设计以STC89C52单片机为控制核心,基于AD9850制作了一个频率值能在一定范围内调节的多功能信号源。

该信号源在1KHZ~10MHZ 范围能输出稳定可调的正弦波,并通过LCDJ1602显示步进及其频率。

系统由5V 稳压电源所驱动,具有显示、按键控制功能和频率和步进设置功能。

在Ω50负载电阻下输出的电压峰-峰值p p V -≥1V 可调。

关键字:正弦信号发生器、STC89C52单片机、LCD1602、AD9850模块1.系统方案确定1.1.题目分析:本设计要求可以输出较宽频带且频率稳定度足够高的正弦信号,并且具有一定的负载能力,同时可输出指标满足正弦波信号。

综合题目指标要求及相关分析,得到该设计的功能框架图如图1所示。

本设计可分为以下几个部分:波形发生模块、单片机控制模块、液晶显示模块和按键控制模块(频率设置和步进调节)。

图1功能模块框图1.2.各模块方案比较1.2.1正弦信号发生模块方案1:由于DDS集成芯片能达到要求,而且节省硬件电路,程控调节能够方便实现,采用直接频率合成集成芯片AD9850。

AD9850是AD公司生产的DDS 芯片,带并行和串行加载方式,AD9850内含可编程DDS 系统和高速比较器,能实现全数字编程控制的频率合成。

作为1KHZ~10MHZ正弦信号发生。

方案2:采用反馈型LC振荡原理。

选择合适的电容、电感就能产生相应的正弦信号。

其中电容采用变容二极管,通过控制二极管的电压来改变电容,最终控制输出信号频率。

此方案器件比较简单,但是难以达到高精度的程控调节,而且稳定度不高。

方案3:采用FPGA器件。

将某一标准正弦信号经过高速采样后送到外部存储器中储存好,然后用一个计数器产生地址读出存储器中的数据后送到D/A转换器件中输出,可以通过改变计数器的参数,改变地址信号,实现,也可以通过处理数据改变信号的幅度。

《EDA技术》设计报告设计题目正弦信号发生器的设计院系:信息工程学院专业:通信工程学姓号:名:RST7 根地址线CLK计 数器8 位R O M并转串输出TLV5620 D/A 转换一.设计任务及要求1. 设计任务 :利用实验箱上的 D/A 转换器和示波器设计正弦波发生器,可以在示波器上观察到正弦波2. 设计要求 :(1) 用 VHDL 编写正弦波扫描驱动电路 (2) 设计可以产生正弦波信号的电路(3) 连接实验箱上的 D/A 转换器和示波器,观察正弦波波形二.设计方案(1)设计能存储数据的 ROM 模块,将正弦波的正弦信号数据存储在在 ROM 中,通过地址发生器读取,将正弦波信号输入八位 D/A 转化器,在示波器上观察波形(2)用 VHDL 编写正弦波信号数据, 将正弦波信号输入八位 D/A 转化器, 在示波器上观察波形三.设计框图图 1 设计框图信号发生器主要由以下几个部分构成:计数器用于对数据进行采样,ROM用于存储待采样的波形幅度数值, TLV5620 用于将采集的到正弦波数字量变为模拟量,最后通过示波器进行测量获得的波形。

其中,ROM 设置为 7 根地址线, 8个数据位,8 位并行输出。

TLV5260 为串行输入的 D/A 转换芯片,因此要把 ROM 中并行输出的数据进行并转串。

四.实现步骤1. 定制 ROMROM 的数据位选择为8 位,数据数选择128 个。

利用megawizard plug-in manager定制正弦信号数据ROM 宏功能块,并将上面的波形数据加载于此ROM 中。

如图 3 所示。

图2 ROM 存储的数据图3 调入ROM 初始化数据文件并选择在系统读写功能2. 设计顶层.顶层设计主要是通过编写VHDL 语言或设计原理图用于产生计数信号和调用room 存储的数据并输出。

在此步骤里要建立EDA 工程文件,工程文件结构如图4 所示,SIN_CNT 中的VHDL 代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SIN_GNT ISPORT ( RST, CLK, EN : IN STD_LOGIC;ADDR : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END SIN_GNT;ARCHITECTURE BEHA VIOR OF SIN_GNT ISCOMPONENT ROM ISPORT ( address : IN STD_LOGIC_VECTOR(6 DOWNTO 0);inclock : IN STD_LOGIC;q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END COMPONENT;SIGNAL Q : STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINU : ROM PORT MAP ( address => Q,inclock => CLK,q => DOUT);PROCESS(CLK, RST, EN)BEGINIF RST = '0' THENQ <= "0000000";ELSIF CLK'EVENT AND CLK = '1' THENIF EN = '1' THENQ <= Q + 1;END IF;END IF;END PROCESS;ADDR <= Q;END BEHA VIOR;工程文件的建立步骤简述如下:1、新建一个文件夹。

南阳理工学院计算机与信息工程学院软硬件专业大实验总结报告题目:正弦波信号发生器设计与分析*名:***学号:************专业:通信工程学院:计算机与信息工程学院指导教师:***起止日期: 11.11.14—12.01.06南阳理工学院计算机与信息工程学院软硬件专业大实验任务书实践题目正弦波信号发生器设计与分析学生姓名通信工程班级2010060802 学号104060820058指导教师徐春雨职称讲师实践地点通信工程试验中心实践日期2011年11月14日起至2012年1月6日选题的目的:精确地输出正弦波、调幅波、调频波、PSK、ASK等信号及保证信号的高可靠性,设计出一种新型的正弦信号发生器。

以可编程逻辑器件CPLD和单片机A T89S52为基础,采用数字频率合成DDS技术实现频率合成功能,结合高速D/A器件AD9713使得输出频率维持在1 k~10 MHz范围内,步进为100 Hz,通过对CPLD采用相应的数字控制算法实现调频FM,调幅AM和键控PSK、ASK数字调制功能。

技术要求:(1)正弦波输出频率范围 1 kHz~10 MHz。

(2)具有频率设置功能,频率步进100 Hz。

(3)输出信号频率稳定度优于10-4。

(4)输出电压幅度在50 Ω负载电阻上的电压峰-峰值V opp≥1 V。

(5)失真度用示波器观察时无明显失真。

进度安排:2011年11月14日——2011年11月27日可行性研究、需求分析2011年11月28日——2011年12月11日总体设计2011年12月12日——2011年12月25日详细设计2011年12月26日——2012年01月01日系统调试、测试2012年01月02日——2012年01月06日撰写实训报告主要参考资料:[1]樊昌信曹丽娜通信原理国防工业出版社(第六版)2010[2]陈怀琛等.MATLAB及在电子信息课程中的应用.北京:电子工业出版社,2003。

正弦信号发生器摘要本系统以单片机和FPGA为控制和处理核心,基于直接数字频率合成原理,利用DDS集成芯片AD9851实现了300Hz~13MHz、步进为0.1Hz的正弦信号发生器和高频偏的DDS调频(FM)信号发生器;通过模拟乘法器MC1496实现调幅功能,其低频调制信号由FPGA和DAC0800构成DDS低频发生器产生;利用可变增益宽带放大器AD600实现幅度程控,通过检波和ADC反馈给单片机,检测和调整输出电压,实现精确的幅度控制。

使用了多种抗干扰措施以减少噪声并抑制高频自激;后级功放采用两片宽带运放AD811组成桥式功率放大器来实现。

本系统硬件设计应用了EDA工具,软件采用模块化的编程思想。

关键字:正弦信号发生器 DDS 调幅幅度控制桥式功率放大器AbstractBased on the principle of DDS, the system uses the A T89C51 and FPGA as the control and processing unit ,and uses the DDS chip AD9851 to realize the Sine and FM signal generator .The signal generator can output Sine signal of 300 Hz ~13M Hz with 0. 1 Hz frequency step, the MC 1496 is used to realize AM performance, the Amplitude control of signals are realized by using chip AD600,the low frequency modulation signal is produced by DDS made of FPGA and DAC 0800..Many methods are employed to diminish noises and restrain high frequency self-excitation. The test results show that the system achieves the requirements of design.正弦信号发生器一、方案论证与选择本系统难点有:1.产生稳定性高、频率步进较低、频带范围较广且具有一定带负载能力的正弦信号源;2.以1kHz为调制信号,在较大动态范围(100kHz~10MHz)内产生频偏为10kHz的调频信号;3.产生AM、ASK、PSK等调制信号。

电子设计报告正弦信号发生器设计小组成员院系名称专业名称班级二○一四年 7 月 17 日正弦信号发生器设计内容提要:本次设计是基于FPGA与DSP设计与制作的一个正弦信号发生器,结合了EDA 技术与直接数字频率合成(DDS)技术。

EDA技术是现代电子设计技术的核心,DDS技术是最为先进的频率合成技术,具有频率分辨率高、频率切换速度快、相位连续、输出相位噪声低等许多优点。

我们利用EDA技术,简历正弦信号DDS产生的模型,编写源程序,产生输出频率1Hz-10MHz的正弦波。

在设计中,我们使用FPGA开发板构造直接数字频率合成器(DDS)产生正弦信号,再通过DSP来控制产生的正弦信号的频率。

经过DDS输出的正弦信号通过低通滤波器与宽带放大器之后就可以输出频率与幅度均达到要求的正弦信号。

通过查阅资料,提出了符合FPGA的正弦信号发生器设计方案并且通过QUARTUS II软件进行设计实现,DDS由相位累加器和正弦ROM查找表两个功能块组成,其中ROM查找表由宏功能模块LPM_ROM来实现。

在了解了EDA技术的相关知识与DDS技术的工作原理、电路结构,及设计的思路和实现方法的基础上。

经过仿真测试,设计可以达到技术要求。

关键词:FPGA 直接数字频率合成(DDS)正弦信号 DSP目录1. 方案设计与论证 (1)1.1 正弦信号输出方案设计与论证 (1)1.2 宽带放大器方案设计与论证 (1)2. 硬件电路设计 (2)2.1宽带放大器设计 (2)2.2 DA转换电路设计 (4)2.3低通通滤波器设计 (4)3. 软件设计 (4)3.1有关直接数字频率合成器(DDS) (4)3.2 软件总体框图 (5)4. 参考文献 (6)正弦信号发生器设计报告1.方案设计与论证1.1 正弦信号输出方案设计与论证方案一:采用分立元件模拟直接合成来产生正弦波,这种方法的优点是转换速度快,频率分辨率高,缺点是转换的量程要靠手动来实现,体积大难以集成,而且可靠性和准确度都比较低,很难得到提高。

正弦信号发生器设计报告正弦信号发生器设计报告作者王贞炎、石磊、齐欣乐赛前辅导及文稿整理辅导教师肖看摘要本系统由FPGA、单片机控制模块、键盘、LCD液晶显示屏、DAC输出电路和末级放大电路构成。

仅用单片FPGA就实现了直接数字频率合成技术(DDS),产生稳幅正弦波,并在数字域实现了AM、FM、ASK、PSK 等四类调制信号。

调制信号既可由用户输入参数由FPGA内部生成,也可以从外部输入。

整个系统结构紧凑,电路简单,功能强大,可扩展性强。

Abstract This system is composed by FPGA, MCU controller, keyboard, LCD, DAC and amplifier modules. The DDS, Direct Digital Synthesizer, which is implemented by a unique FPGA IC, can provide the stable sine signal with digital AM, FM, ASK, PSK modulation. The modulation signal can be provided NOT only by FPGA, which will receive parameters from user, but also from external input. This system features in compact module, simple circuit, powerful functions and flexible expansion.一、方案论证与比较根据题目要求,基本部分需要实现正弦波信号发生,而发挥部分主要需要实现信号调制。

1. 正弦信号输出方案方案一采用专用信号发生器。

MAX038是美信公司的低失真单片信号发生器集成电路,内部电路完善。

使用该芯片,设计简单,可以生成同一频率信号的各种波形信号,但频率精确度和稳定度都难以达到要求。

基于DDS的正弦信号发生器设计报告院系:电子工程系专业:电子信息工程班级:姓名:1. DDS信号发生器原理对于正弦信号发生器,它的输出可以用下式来描述:其中,S out是指该信号发生器的输出信号波形,f out只输出信号对应的频率。

上式的表述对于时间t是连续的,为了用数字逻辑实现该表达式,必须进行离散化处理,用基准时钟clk进行抽样,令正弦信号的的相位θ为在一个clk周期Tclk,相位θ的变化量为其中f clk指clk的频率对于2π可以理解为“满”相位,为了对Δθ进行数字量化,把2π切割成2N,用词每个clk周期的相位增量Δθ用量化值BΔθ来描述:BΔθ=(Δθ·2N)/2π,且BΔθ为整数与上式联立可得:显然,信号发生器可以描述其中θk-1指前一个clk周期的相位值,同样得出由以上推倒可以得出,只要对相位的量化值进行简单的累加运算,就可以得到正弦信号的当前相位值,而用于累加的香味增量量化值BΔθ决定了信号的输出频率f out并呈现简单的线性关系。

直接数字合成器DDS就是根据以上原理而设计的数控频率合成器,下图为其基本DDS 结构,主要有相位累加器、相位调制器、正弦ROM查找表构成图中的相位累加器、相位调制器、正弦ROM查找表是DDS结构中的数字部分,图 12. 基于DDS的正弦信号发生器设计实现根据设计原理框图分别设计出加法器、寄存器、正弦波ROM。

2.1.1. 32位加法器ADDER32设计在原理图文件文件下在空白处双击,单击“MegaWizard Plug-In Manager”选择第一项图 2选择器件为cyclone,语言方式为VerilogHDL。

在算数项Arithmetic中选择计数器LPM_ADD_SUB.存于所建工程文件夹下命名为ADDER32.单击NEXT,进入以后对话框后选择32位加法器工作模式选择有一位加法进位输出,选择有符号加法方式,选择2级流水线工作模式 ,此时该加法器变为有时序电路的模块,最后至finish按钮,编辑完成。

毕业设计(论文)

开题报告

题目正弦信号发生器的

FPGA设计

专业光信息科学与技术

班级光信072

学生周力强

指导教师杨秀芳

2011 年

一、毕业设计(论文)课题来源、类型

本课题是在长期研究可编程逻辑技术及数字逻辑原理基础上提出的,通过对于FPGA及VHDL硬件描述语言的了解与研究,以及对于开发软件Quartus Ⅱ的掌握,所进行的正弦信号发生器的设计。

课题来源:自选课题。

课题类型:系统设计。

二、选题的目的及意义

信号发生器是各种测试和实验过程中不可缺少的工具,在通信、测量、雷达、控制、教学等领域应用十分广泛。

不论是在生产、科研还是在数学上,信号发生器都是电子工程师信号仿真实验的最佳工具,而且,信号发生器的设计方法多,设计技术也越来越先进。

随着我国经济和科技的发展,对相应的测试仪器和测试手段提出了更高的要求,信号发生器已成为测试仪器中至关重要的一类,因此开发信号发生器具有重大意义。

本课题的目的是研究正弦信号发生器的设计方法,设计出具有调频、调幅功能的正弦信号发生器。

本文是以现场可编程门阵列(FPGA)作为硬件基础,先将所需要产生的正弦信号波形的一个周期的若干个采样点的二进制信息存储在波形存储器(ROM)中,再通过硬件电路依次从波形存储器中读取出来。

经数模转换以及滤波后得到正弦信号的波形。

三、本课题在国内外的研究状况及发展趋势

正弦信号主要用于测量电路和系统的频率特性、非线性失真、增益及灵敏度等。

按频率覆盖范围分为低频信号发生器、高频信号发生器和微波信号发生器;按输出电平可调节范围和稳定度分为简易信号发生器(即信号源)、标准信号发生器(输出功率能准确地衰减到-100分贝毫瓦以下)和功率信号发生器(输出功率达数十毫瓦以上);按频率改

变的方式分为调谐式信号发生器、扫频式信号发生器、程控式信号发生器和频率合成式信号发生器等。

信号发生器在电路实验和设备检测中具有十分广泛的用途。

例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的振荡器。

四、本课题主要研究内容

1、安装QuartusⅡ开发工具软件,熟悉QuartusⅡ基本使用方法。

2、查阅资料,熟悉数字逻辑电路分析和设计方法,学习数字电路描述语言VHDL(Very High Speed Integrated Circuit Hardware Description Language)或Verilog HDL。

3、在对于FPGA的结构和特性了解的基础上,设计出正弦信号发生器的两种实现方案。

4、对两种方案进行时序仿真测试,验证其设计的正确性。

5、完成引脚锁定和编程下载,使用嵌入式逻辑分析仪进行实时测试。

6、完成文献综述及翻译外文资料。

五、完成论文的条件和采用的研究手段(途径)

1、首先查阅相关的资料,了解FPGA的三大组成部分:

①二维的逻辑块阵列(逻辑单元),构成了器件的逻辑组成核心;

②输入/输出模块;

③连接逻辑块的互联资源,用于逻辑块之间,逻辑块与输入/输出块之间的

连接。

2、熟悉VHDL硬件描述语言的组成部分及其功能;

①库。

其功能是用来存放已经编译的实体说明、结构体、程序包和配置;

②程序包。

其功能是用来存放各种设计模块都共享的类型、常量和子程序等;

③实体说明。

其功能是用来描述设计系统的外部接口特征;

④结构体。

其功能是用来描述设计系统的行为和结构;

⑤配置。

其功能是用来描述设计实体和元件或者结构体之间的连接关系。

3、熟悉QuartusⅡ开发工具的设计流程:

①设计输入。

②综合。

③布局布线。

④时序分析。

⑤仿真。

⑥编程和配置。

4、设计出基于QuartusⅡ开发环境下的正弦波发生器方案:

①将要产生的波形数据存入FPGA的ROM中;

②在一定的频率的作用先使计数器循环计数,并且将计数器的输出作为读取波形存储器ROM的地址;

③读出的波形数据送至D/A转换器,D/A转换器输出的波形经低通滤波处理后,便输出了光滑的模拟信号。

计,是常规检查的革新方案;无限远平场长工作距离物镜,使得观察标本

视野更平坦、亮度更高、反差更强,且更容易观察活细胞的状态;配备标准相衬环板,中心可调,可观察低反差或透明标本的鲜明图像。

2、拟定显微镜光学系统总体方案:

(1)生物显微镜光学系统外形尺寸计算:

①物镜数值孔径NA的计算:NA=0.61λ/σ=0.6mm sinu=0.6

②令β=﹣10 Γ=20 得ƒ1'=﹣Lβ/(1-β)²= 15mm

ƒ2'=250/Γ=12.5mm

③显微镜总焦距F:F=250/Ғ=1.25mm

④物镜线视场:2y=0.9mm 目镜线视场:2y'=β*2y=9mm

目镜视场角2w':tanw'=2y'/2(ƒ2')=0.36 得w'=20

⑤出瞳距L''的计算:1/L''-1/L'=1/ƒ2' 得L''=13.46mm

⑥出瞳直径2a'的计算:D'=2a'=1.9mm

⑦L=Ī像-Ī物=180mm β=Ī像/Ī物=﹣10 得Ī像=164Ī物=16

⑧物镜作为孔径光阑:D物=2Ī物tanu+1=25mm

目镜通光口径:D目=2(L''tanw')+D'=11.59mm

(2)根据上述计算,得出显微镜光学系统图。

3、对本次设计中的难点问题进行处理:

(1)要求视场无渐晕。

(2)要求出瞳直径在1mm —5mm之间。

4、进行照明系统设计:照明方式有亮视场照明和暗视场照明两种。

暗视场照明用于观察细菌、细胞和微生物等生物显微镜中,因此选用暗视场照明。

暗视场照明依靠标本内部的散射光通过物镜成像,增强对比,有利于辨别标本内部结构差异。

暗视场照明也有透射照明和反射照明两类,观察生物切片一类透明的标本采用透射照明。

透射暗视场照明最简单的办法是将聚光镜中部孔径挡掉,使照明光束不能直接射入显微物镜。

5、用ZEMAX软件对系统进行优化,并且绘制光路图。

六、本课题进度安排、各阶段预期达到的目标:

第一到三周:查阅资料,了解生物显微镜的基本结构及特点。

第四到六周:根据本系统的技术指标,计算出光学系统的外形尺寸。

第七到九周:进行光学系统物镜与目镜初始结构的确定,学习ZEMAX软件,对系统进行优化。

第十周:绘制光学系统图、光学部件图、光学零件图。

第十一到十二周:完成本次毕业设计的文献综述,翻译外文资料。

第十三到十六周:整理并完成毕业论文。

七、指导教师意见

对本课题的深度、广度及工作量的意见和对设计(论文)结果的预测:

指导教师:

八、所在专业审查意见

负责人:。