晶振负载电容计算方法

- 格式:pdf

- 大小:131.65 KB

- 文档页数:2

一、概述12.5pf负载电容是一个在晶振电路设计中常见的参数,它对晶振的性能以及整个电路的稳定性起着至关重要的作用。

借助适当的外接电容,我们可以有效地调节晶振的振荡频率,保证其在指定范围内稳定工作。

本文将重点探讨12.5pf负载电容晶振的外接电容设计,并对其原理和注意事项进行深入分析。

二、12.5pf负载电容的作用12.5pf负载电容在晶振电路中的作用主要有两个方面:1. 调节晶振的振荡频率:晶振在工作时需要和外部电路形成谐振,而12.5pf负载电容则可以影响晶振的谐振频率。

适当调节12.5pf负载电容的数值,可以使晶振的振荡频率在设计要求的范围内稳定工作。

2. 提高电路的稳定性:通过12.5pf负载电容的加入,可以有效抑制晶振的共振峰值,使得整个电路在外部环境变化等因素的影响下保持较好的稳定性。

三、12.5pf负载电容的外接原理为了充分发挥12.5pf负载电容的作用,我们需要合理选择外接电容的数值。

一般来说,外接电容的数值可以通过以下公式计算得到:Cp = (CL - Ci - Cstray) / 2其中,Cp为外接电容的数值,CL为晶振的额定负载电容,Ci为晶振自带电容,Cstray为电路布线与晶振之间的杂散电容。

通过以上公式,我们可以根据实际情况计算得到12.5pf负载电容晶振的外接电容数值,并进行合理的选取和设计。

四、12.5pf负载电容外接设计的注意事项在进行12.5pf负载电容的外接设计时,需要注意以下几个方面:1. 充分考虑布线电容:电路布线可能会带来一定的杂散电容,这些电容会对外接电容的选择产生影响。

在设计时需要充分考虑电路布线的影响,进行合理的校正和补偿。

2. 注意电容的精度和稳定性:外接电容的精度和稳定性对晶振电路的性能有着重要的影响。

选择高精度、稳定性好的外接电容可以提高电路的稳定性和可靠性。

3. 避免共振和串扰:在进行外接电容设计时,需要避免电路出现共振或者串扰等问题。

因此需要根据实际情况进行电路的布线和外接电容的合理安排,以减小电路的干扰和噪声。

详细讲解晶振,一篇文章学会计算晶振的负载电容,电阻选型(1)前言作为一名硬件工程师,从接触单片机的那天,就看到MCU的旁边经常看到会用到晶振,经常的旁边往往会放两个电容,有时候还会再放个电阻,很多硬件工程师都是看别的工程师放多大的电容,电阻,自己也跟着放,这样也没错,但是知其然不知其所以然,对你的硬件水平提高是没有任何帮助的,今天我们就讲一下晶振电路,以及晶振外围阻容器件的选型计算,下一篇文章会讲晶振和MCU是否匹配已经晶振常见问题处理。

晶振晶振电路晶振电路有两种,一种是Pierce电路,另外一种是Colpitts电路,其实就是两种晶振拓扑,比较常用的是Pierce电路。

所以我们大概介绍一下Colpitts电路的特点就跳过了,采用Colpitts电路的晶振的缺点是晶振两端会有杂散电抗,此时比较难考虑杂散电抗的影响,说白了就是计算起来比较麻烦,电路可靠性也更低,还会在晶振两端形成DC偏置电压,有点是电路有振幅限制,从而功耗更低,对外部电路辐射干扰更小。

我们重点要介绍的是Pierce电路,具体电路就是下图这种形式,也是最常见的拓扑图,该电路一般由非门电路(增益特别大的运放),反馈电阻,负载电容构成,电容和晶振是外置的,一般要自己选型,运放和反馈电阻一般集成在IC内部,启动速度更快,可靠性更高,所以说除非有很严苛的功耗要求,一般推荐使用此电路。

1)Rs是限流电阻,Rs的值越小,晶振启动速度越快,为了避免晶振过驱动,Rs也不能过小,在高频晶振中,Rs可以短路。

2)Rb是反馈电阻,为运放输入提供反馈,让运放工作在线性区,当运放工作在线性区时,晶振才能正常起振,当然反馈电阻Rb也会影响运放的环路增益,反馈电阻越大,增益越大。

阻容元件计算1)负载电容计算Cl=(C1*C2) / (C1+C2)+Cs+CpCs就是晶振内部的杂散电容,晶振规格书中一般会标出该值,Cp 就是PCB板上的走线以及晶振引脚的寄生电容,Cs和Cp的电容加起来总计2-8pF,最准确的方法是通过测试晶振输出波形来确认负载电容是否合适。

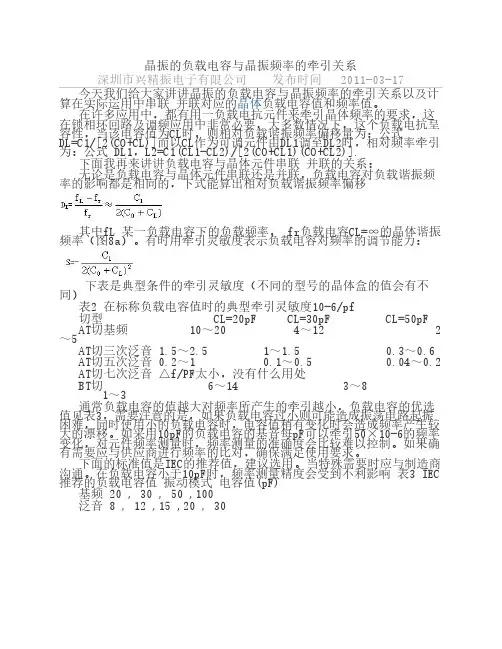

晶振的负载电容与晶振频率的牵引关系深圳市兴精振电子有限公司 发布时间 2011-03-17今天我们给大家讲讲晶振的负载电容与晶振频率的牵引关系以及计算在实际运用中串联 并联对应的晶体负载电容值和频率值。

在许多应用中,都有用一负载电抗元件来牵引晶体频率的要求,这在锁相环回路及调频应用中非常必要,大多数情况下,这个负载电抗呈容性,当该电容值为CL时,则相对负载谐振频率偏移量为:公式DL=C1/[2(CO+CL)]而以CL作为可调元件由DL1调至DL2时,相对频率牵引为:公式 DL1,L2=C1(CL1-CL2)/[2(CO+CL1)(CO+CL2)].下面我再来讲讲负载电容与晶体元件串联 并联的关系:无论是负载电容与晶体元件串联还是并联,负载电容对负载谐振频率的影响都是相同的,下式能算出相对负载谐振频率偏移其中fL 某一负载电容下的负载频率, fr负载电容CL=∞的晶体谐振频率(图8a)。

有时用牵引灵敏度表示负载电容对频率的调节能力:下表是典型条件的牵引灵敏度(不同的型号的晶体盒的值会有不同)表2 在标称负载电容值时的典型牵引灵敏度10-6/pf切型 CL=20pF CL=30pF CL=50pF AT切基频 10~20 4~12 2~5AT切三次泛音 1.5~2.5 1~1.5 0.3~0.6 AT切五次泛音 0.2~1 0.1~0.5 0.04~0.2 AT切七次泛音 △f/PF太小,没有什么用处BT切 6~14 3~8 1~3通常负载电容的值越大对频率所产生的牵引越小,负载电容的优选值见表3,需要注意的是,如果负载电容过小则可能造成振荡电路起振困难,同时使用小的负载电容时,电容值稍有变化时会造成频率产生较大的漂移。

如采用10pF的负载电容的基音每pF可以牵引50×10-6的频率变化,对元件频率测量时,频率测量的准确度会比较难以控制。

如果确有需要应与供应商进行频率的比对,确保满足使用要求。

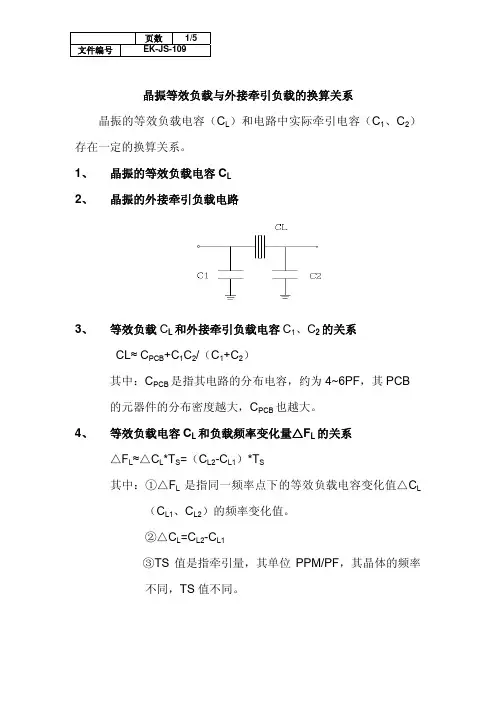

页数1/5文件编号EK-JS-109晶振等效负载与外接牵引负载的换算关系晶振的等效负载电容(C L)和电路中实际牵引电容(C1、C2)存在一定的换算关系。

1、晶振的等效负载电容C L2、晶振的外接牵引负载电路3、等效负载C L和外接牵引负载电容C1、C2的关系CL≈ C PCB+C1C2/(C1+C2)其中:C PCB是指其电路的分布电容,约为4~6PF,其PCB的元器件的分布密度越大,C PCB也越大。

4、等效负载电容C L和负载频率变化量△F L的关系△F L≈△C L*T S=(C L2-C L1)*T S其中:①△F L是指同一频率点下的等效负载电容变化值△C L (C L1、C L2)的频率变化值。

②△C L=C L2-C L1③TS值是指牵引量,其单位PPM/PF,其晶体的频率不同,TS值不同。

1.举例说明:如果电路中的C1、C2是20PF的负载电容,那么计算晶振的等效负载电容CL≈C PCB+ C1C2/(C1+C2)=6.0PF+20*20/(20+20)=16PF象17.734475MHz ,CL=20PF的晶体TS=12PPM/PF可以计算频率△L*T S=(C L2-C L1)*T S=(20-16)*12=48PPM,此变化△L≈C的变化量F量已经超出本身产品要求的调整+/-20PPM的变化范围,因牵引负载的偏移,造成负载频率的偏移,形成部分产品的频率超出边沿。

2.建议:晶振的外接电容C1、C2换成30PF,可以计算出CL≈20PF,能与已生产的17.734475MHz,CL=20PF的等效负载电容相匹配。

请实验。

如何计算晶振的负载电容(CL )公式:Load Cap (CL) = C1.C2 / (C1+C2) + Cstray (分布电容)影响Cstray值的因素主要有下列情况:1. IC(微处理器)脚与脚之间的分布电容.2. PCB Layout3. IC输入回路与IC连接距离.4. IC内部参数变化.5. 其它因素.晶振上标注的频率值均是加上负载电容后的计算值,当然,这个负载电容的大小是由电子工程师计算得出来的,如果实际的负载电容配置不当, 它会影响到晶振的谐振频率和输出幅度.根据以上公式计算出来的值与实际还是存在差异的,最好的做法是做试验,在PCB板上用不同的电容或者用可变电容调试,直到调出最佳波形。

晶振负载电容及电阻晶振是晶体振荡器的简称,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以频率的高低分其中较低的频率是串联谐振,较高的频率是并联谐振。

由于晶体自身的特性致使这两个频率的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感,所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路。

这个并联谐振电路加到一个负反馈电路中就可以构成正弦波振荡电路,由于晶振等效为电感的频率范围很窄,所以即使其他元件的参数变化很大,这个振荡器的频率也不会有很大的变化。

晶振有一个重要的参数,那就是负载电容值,选择与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率。

一般的晶振振荡电路都是在一个反相放大器(注意是放大器不是反相器)的两端接入晶振,再有两个电容分别接到晶振的两端,每个电容的另一端再接到地,这两个电容串联的容量值就应该等于负载电容,请注意一般IC的引脚都有等效输入电容,这个不能忽略。

一般的晶振的负载电容为15p或12.5p ,如果再考虑元件引脚的等效输入电容,则两个22p的电容构成晶振的振荡电路就是比较好的选择。

晶振是为电路提供频率基准的元器件,通常分成有源晶振和无源晶振两个大类,无源晶振需要芯片内部有振荡器,并且晶振的信号电压根据起振电路而定,允许不同的电压,但无源晶振通常信号质量和精度较差,需要精确匹配外围电路(电感、电容、电阻等),如需更换晶振时要同时更换外围的电路。

有源晶振不需要芯片的内部振荡器,可以提供高精度的频率基准,信号质量也较无源晶振要好。

每种芯片的手册上都会提供外部晶振输入的标准电路,会表明芯片的最高可使用频率等参数,在设计电路时要掌握。

与计算机用CPU 不同,单片机现在所能接收的晶振频率相对较低,但对于一般控制电路来说足够了。

另外说明一点,可能有些初学者会对晶振的频率感到奇怪,12M、24M之类的晶振较好理解,选用如11.0592MHZ的晶振给人一种奇怪的感觉,这个问题解释起来比较麻烦,如果初学者在练习串口编程的时候就会对此有所理解,这种晶振主要是可以方便和精确的设计串口或其它异步通讯时的波特率。

率。

晶体旁边的两个电容接地,实际上就是电容三点式电路的分压电

容,接地点就是分压点。

以接地点即分压点为参考点,振荡引脚的输

入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一

个正反馈以保证电路持续振荡。

在芯片设计时,这两个电容就已经形

成了,一般是两个容量相等的,容量大小依工艺和版图而不同,但终

归是比较小,不一定适合很宽的频率范围。

外接时大约是数pF到数十pF,依频率和石英晶体的特性而定。

这两个电容串联的值是并联在谐

振回路上的,会影响振荡频率。

当两个电容量相等时,反馈系数是

0.5,一般是可以满足振荡提交的,但如果不易起振或振荡不稳定可以

减小输入端对地电容量,而增加输出端的值以提高反馈量。

•并联电阻取值影响波形的脉冲。

•并联电阻降低谐振阻抗,使谐振器易启动;

•并联电阻配合IC内部电路组成负反馈、移相,使放大器工作在线性区;

•串联电阻限流防止谐振器被过驱。

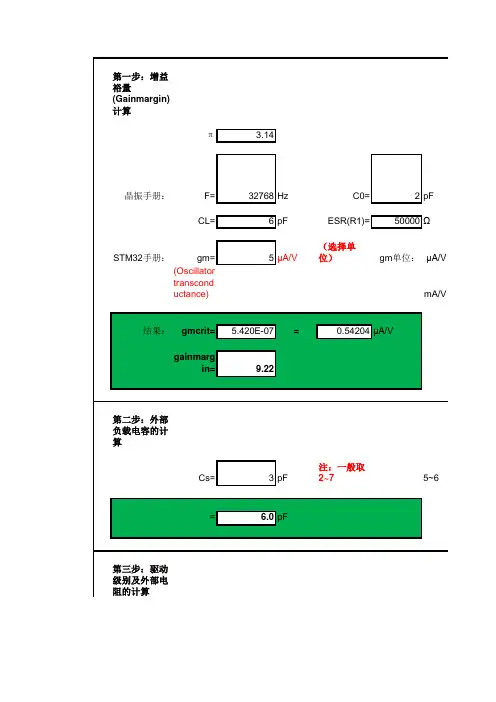

第一步:增益裕量(Gainmargin)计算π 3.14晶振手册:F=32768Hz C0=2pFCL=6pF ESR(R1)=50000ΩSTM32手册:gm=5μA/V(选择单位)gm单位:μA/V(Oscillator transconductance)mA/V结果:gmcrit= 5.420E-07=0.54204μA/Vgainmargin=9.22第二步:外部负载电容的计算Cs=3pF注:一般取2~75~6CL1=CL2= 6.0pF第三步:驱动级别及外部电阻的计算对于32kHz的振荡器来说,一般不推荐使用外部限流电阻(译注:因为LSE的常见问题是振荡器ESR是指晶振的等效串联电阻(其值由晶振制造商给出):IQ是流过晶振电流的均方根有效值,使用示波器可观测到其波形为正弦波。

电流值可使用峰-峰值(IPP)。

当使用电流探头时(如图6),示波器的量程比例可能需要设置为1m 图6 使用电流探头检测晶振驱动电流。

注:分路电容(shunt capacitance)低频(32K)高频SE的常见问题是振荡器驱动能力不足而非晶振被过分驱动)比例可能需要设置为1mA/1mV。

IQMAX均方根有效值(假设流过晶振的电流波形为正弦波)。

AXPP 表达式如下:荡器起振条件将得不到满足从而无法正常工作。

重新计算Gainmargin 。

重新回到第一步。

确保振荡器的起振点在基频上,而不是在其他晶振制造商的给定值,外部电阻RExt是必需的,用以推荐使用RExt了,它的值可以是0Ω。

意到RExt和CL2构成了一个分压/滤波器,考虑通带宽度用电位器来代替RExt,RExt值可预设为CL2的位器的值即是CL2值。

t值对起振条件没有影响。

例如,RExt值的值。

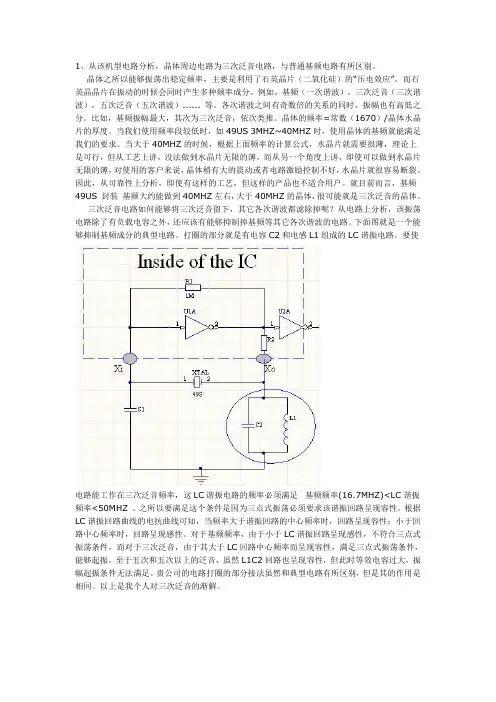

1、从该机型电路分析,晶体周边电路为三次泛音电路,与普通基频电路有所区别。

晶体之所以能够振荡出稳定频率,主要是利用了石英晶片(二氧化硅)的“压电效应”。

而石英晶晶片在振动的时候会同时产生多种频率成分。

例如,基频(一次谐波),三次泛音(三次谐波),五次泛音(五次谐波)...... 等。

各次谐波之间有奇数倍的关系的同时,振幅也有高低之分。

比如,基频振幅最大,其次为三次泛音,依次类推。

晶体的频率=常数(1670)/晶体水晶片的厚度。

当我们使用频率段较低时,如49US 3MHZ~40MHZ时,使用晶体的基频就能满足我们的要求。

当大于40MHZ的时候,根据上面频率的计算公式,水晶片就需要很薄,理论上是可行,但从工艺上讲,没法做到水晶片无限的薄,而从另一个角度上讲,即使可以做到水晶片无限的薄,对使用的客户来说,晶体稍有大的震动或者电路激励控制不好,水晶片就很容易断裂。

因此,从可靠性上分析,即使有这样的工艺,但这样的产品也不适合用户。

就目前而言,基频49US 封装基频大约能做到40MHZ左右,大于40MHZ的晶体,很可能就是三次泛音的晶体。

三次泛音电路如何能够将三次泛音留下,其它各次谐波都滤除掉呢?从电路上分析,该振荡电路除了有负载电容之外,还应该有能够抑制掉基频等其它各次谐波的电路。

下面图就是一个能够抑制基频成分的典型电路。

打圈的部分就是有电容C2和电感L1组成的LC谐振电路。

要使电路能工作在三次泛音频率,这LC谐振电路的频率必须满足基频频率(16.7MHZ)<LC谐振频率<50MHZ 。

之所以要满足这个条件是因为三点式振荡必须要求该谐振回路呈现容性。

根据LC谐振回路曲线的电抗曲线可知,当频率大于谐振回路的中心频率时,回路呈现容性;小于回路中心频率时,回路呈现感性。

对于基频频率,由于小于LC谐振回路呈现感性,不符合三点式振荡条件,而对于三次泛音,由于其大于LC回路中心频率而呈现容性,满足三点式振荡条件,能够起振。

晶振频率计算

晶振频率是指晶体振荡器发出的振荡信号频率,通常用赫兹(Hz)作为单位进行表示。

计算晶振频率可以通过以下步骤完成:

1. 确定晶振器的晶体谐振频率。

晶体谐振频率是指晶体在无耗损情况下振动系统的固有频率。

该值通常由晶振器制造商提供,也可以通过实验测量获得。

2. 计算晶振器的负载电容。

负载电容是指晶振器在运行时需要连接的外部电容。

该值通常由晶振器制造商提供,也可以通过实验测量获得。

3. 计算晶振频率。

晶振频率的计算公式为:f = 1 / (2π√(LC)),其中f为晶振频率,L为晶体谐振电感,C为负载电容。

需要注意的是,实际上晶振器的频率可能受到外界干扰以及温度变化等因素的影响,因此计算出的频率仅供参考。

同时,为保证晶振器的正常工作,需要根据实际需求选择适合的晶振器型号和负载电容。

晶振工作原理电容计算

晶振(Crystal Oscillator)是一种常用的电子元件,它能够产

生稳定的高频振荡信号。

其工作原理是利用晶体的压电效应和谐振现象。

晶振的基本结构由晶体元件和放大电路组成。

晶体元件一般采用石英晶体,其具有压电效应,即当施加压力或电压时,晶体会发生尺寸变化,从而引起电位能的变化。

当交流信号施加在晶体上时,由于晶体的压电效应,将产生对应的电势变化。

放大电路将晶体产生的微弱信号进行放大,使其达到可以驱动其他电子元件的程度。

通常使用反馈放大电路来实现这一目的。

在反馈放大电路中,部分输出信号被反馈到输入端,形成正反馈。

通过适当的电路设计,反馈使晶振达到自激振荡状态,即能够持续地产生输出信号。

计算晶振所需的电容值时,需要考虑晶体的谐振频率和晶体的等效电容。

晶体的谐振频率是晶体元件固有的频率,它决定了晶振的输出频率。

晶体的等效电容由晶体的压电效应和串联电容等效组成,它表示了晶体元件的电容特性。

根据晶体的等效电容以及所需的谐振频率,可以使用以下公式计算晶振所需的电容值:

C = 1 / (4π²f²L₁ - 1 / C₁)

其中,C是所需的电容值,f是晶振的谐振频率,L₁是晶体元

件的等效电感,C₁是晶体元件的等效电容。

需要注意的是,计算得到的电容值是理论值,实际应用中可能会进行微调和选取合适的标准电容值。

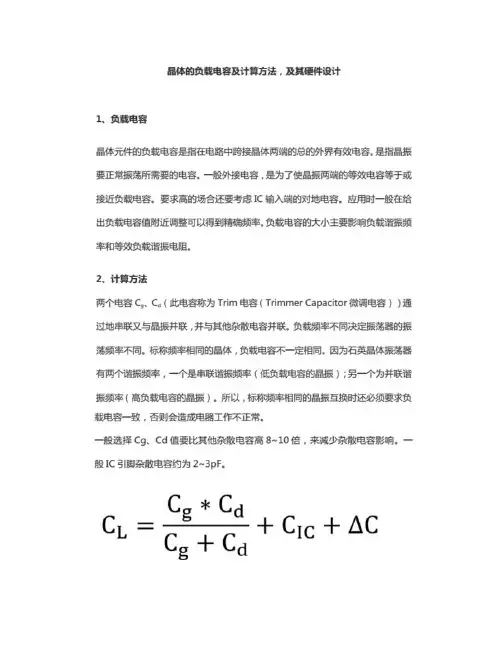

负载电容晶体元件的负载电容是指在电路中跨接晶体两端的总的外界有效电容。

是指晶振要正常震荡所需要的电容。

一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。

要求高的场合还要考虑ic输入端的对地电容。

应用时一般在给出负载电容值附近调整可以得到精确频率。

此电容的大小主要影响负载谐振频率和等效负载谐振电阻。

计算方法:晶振的负载电容=[(Cd*Cg)/(Cd+Cg)]+Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C (PCB上电容)。

一般Cic+△C取2-5pF外挂电容=[CL-(2~5)]*2外接负载电容与振荡频率的关系:因此外接负载电容能够微调振荡频率,增大外接负载电容减小振荡频率,减小外接负载电容增大振荡频率。

•••••••••••••••••【唯美句子】走累的时候,我就到升国旗哪里的一角台阶坐下,双手抚膝,再闭眼,让心灵受到阳光的洗涤。

懒洋洋的幸福。

顶 3 收藏 2•【唯美句子】一个人踮着脚尖,在窄窄的跑道白线上走,走到很远的地方又走回来。

阳光很好,温暖,柔和。

漫天的安静。

顶7 收藏7•【唯美句子】清风飘然,秋水缓淌。

一丝云起,一片叶落,剔透生命的空灵。

轻轻用手触摸,就点碎了河面的脸。

落叶舞步婀娜不肯去,是眷恋,是装点?瞬间回眸,点亮了生命精彩。

顶11 收藏9•【唯美句子】几只从南方归来的燕子,轻盈的飞来飞去,“几处早莺争暖树,谁家新燕啄春泥,”其乐融融的山林气息,与世无争的世外桃源,让人心旷神怡。

顶0 收藏 2•【唯美句子】流年清浅,岁月轮转,或许是冬天太过漫长,当一夜春风吹开万里柳时,心情也似乎开朗了许多,在一个风轻云淡的早晨,踏着初春的阳光,漫步在碧柳垂青的小河边,看小河的流水因为解开了冰冻而欢快的流淌,清澈见底的的河水,可以数得清河底的鹅软石,偶尔掠过水面的水鸟,让小河荡起一层层的涟漪。

河岸换上绿色的新装,刚刚睡醒的各种各样的花花草草,悄悄的露出了嫩芽,这儿一丛,那儿一簇,好像是交头接耳的议论着些什么,又好象是在偷偷地说着悄悄话。

晶振手册中的负载电容晶振的负载电容是指晶振电路中用来对晶体振荡器的振动特性进行调整的电容器。

在晶振电路中,负载电容是非常重要的,它直接影响着晶振器的频率稳定性和振荡幅度。

晶振的频率主要取决于晶振器内部的振动特性和外部电路的负载特性。

在实际应用中,为了使晶振器的工作频率稳定,通常会在晶振器的输出引脚和地之间串联一个负载电容C1和串联一个反馈电容C2。

负载电容的作用是增加晶振电路的负载,从而保证振荡幅度稳定。

当晶振器输出信号经过负载电容时,负载电容所形成的电容网络就对晶体振荡器的振动特性进行调整。

如果负载电容的大小不合适,振荡信号就会出现频率偏移,导致晶振器的频率稳定性降低。

负载电容的大小可以通过实验和计算来确定。

实验方法是通过改变负载电容的大小,观察晶振器的输出波形,确定稳定频率的大小。

计算方法是通过计算晶振器的特性参数,根据公式来计算出负载电容的大小。

一般来说,负载电容的大小和晶振器的频率有关,因此在选择负载电容时要考虑晶振器的频率范围。

此外,还要考虑晶振器的工作环境和应用要求。

例如,一些应用场合需要晶振器具有较高的频率稳定性和抗震能力,因此需要使用高精度的负载电容和抗震负载电容。

在实际应用中,负载电容的选择和布局也非常重要。

一般来说,负载电容应该尽量靠近晶振器,以减小电路中的干扰和噪声。

此外,还应该选择尽量小的负载电容,以减少负载电容对信号的衰减和延迟。

总之,负载电容是晶振电路中非常重要的组成部分,直接关系到晶振器的性能和稳定性。

因此,在选用和布局负载电容时,应该根据实际应用要求和晶振器的特性进行调整,以保证晶振器的工作性能和稳定性。

晶振的负载电容怎么计算?常规的负载电容20pF,负载电容就是32pF比较匹配晶振的负载电容公式=[(Cd*Cg)/(Cd+Cg)]+Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C (PCB上电容)经验值为3至5pf。

因此,晶振的数据表中规定12pF的有效负载电容要求在每个引脚XIN 与 XOUT上具有22pF(2 * 12pF = 24pF = 22pF + 2pF 寄生电容)。

两边电容为Cg,Cd,负载电容为Cl, cl=cg*cd/(cg+cd)+a就是说负载电容15pf的话,两边两个接27pf的差不多了,各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器。

晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联。

在晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十M 欧之间. 很多芯片的引脚内部已经包含了这个电阻, 引脚外部就不用接了。

这个电阻是为了使反相器在振荡初始时处于线性状态, 反相器就如同一个有很大增益的放大器, 以便于起振. 石英晶体也连接在晶振引脚的输入和输出之间, 等效为一个并联谐振回路, 振荡频率应该是石英晶体的并联谐振频率. 晶体旁边的两个电容接地, 实际上就是电容三点式电路的分压电容, 接地点就是分压点. 以接地点即分压点为参考点, 振荡引脚的输入和输出是反相的, 但从并联谐振回路即石英晶体两端来看, 形成一个正反馈以保证电路持续振荡. 在芯片设计时, 这两个电容就已经形成了, 一般是两个的容量相等, 容量大小依工艺和版图而不同, 但终归是比较小, 不一定适合很宽的频率范围. 外接时大约是数 PF 到数十 PF, 依频率和石英晶体的特性而定. 需要注意的是: 这两个电容串联的值是并联在谐振回路上的, 会影响振荡频率. 当两个电容量相等时, 反馈系数是 0.5, 一般是可以满足振荡条件的, 但如果不易起振或振荡不稳定可以减小输入端对地电容量, 而增加输出端的值以提高反馈量. . 一般芯片的 Data sheet 上会有说明。

晶振的负载电容与晶振频率的牵引关系深圳市兴精振电子有限公司发布时间 2011-03-17今天我们给大家讲讲晶振的负载电容与晶振频率的牵引关系以及计算在实际运用中串联并联对应的晶体负载电容值和频率值。

在许多应用中,都有用一负载电抗元件来牵引晶体频率的要求,这在锁相环回路及调频应用中非常必要,大多数情况下,这个负载电抗呈容性,当该电容值为CL时,则相对负载谐振频率偏移量为:公式 DL=C1/[2(CO+CL)]而以CL作为可调元件由DL1调至DL2时,相对频率牵引为:公式 DL1,L2=C1(CL1-CL2)/[2(CO+CL1)(CO+CL2)].下面我再来讲讲负载电容与晶体元件串联并联的关系:无论是负载电容与晶体元件串联还是并联,负载电容对负载谐振频率的影响都是相同的,下式能算出相对负载谐振频率偏移其中fL 某一负载电容下的负载频率, fr负载电容CL=∞的晶体谐振频率(图8a)。

有时用牵引灵敏度表示负载电容对频率的调节能力:下表是典型条件的牵引灵敏度(不同的型号的晶体盒的值会有不同)表2 在标称负载电容值时的典型牵引灵敏度10-6/pf切型 CL=20pF CL=30pF CL=50pFAT切基频 10~20 4~12 2~5AT切三次泛音 1.5~2.5 1~1.5 0.3~0.6AT切五次泛音 0.2~1 0.1~0.5 0.04~0.2AT切七次泛音△f/PF太小,没有什么用处BT切 6~14 3~8 1~3通常负载电容的值越大对频率所产生的牵引越小,负载电容的优选值见表3,需要注意的是,如果负载电容过小则可能造成振荡电路起振困难,同时使用小的负载电容时,电容值稍有变化时会造成频率产生较大的漂移。

如采用10pF的负载电容的基音每pF可以牵引50×10-6的频率变化,对元件频率测量时,频率测量的准确度会比较难以控制。

如果确有需要应与供应商进行频率的比对,确保满足使用要求。

下面的标准值是IEC的推荐值,建议选用。

晶振电容的选取和计算

在电子电路中,晶振和电容是常用的元件。

晶振用于产生稳定的时钟信号,而电容则用于调整晶振的频率和稳定性。

选择合适的晶振电容对于电路的性能至关重要。

晶振电容的选取需要考虑以下几个因素:

1. 频率:晶振的频率决定了所需的电容值。

一般来说,电容值与晶振频率成反比。

较高频率的晶振需要较小的电容值,而较低频率的晶振则需要较大的电容值。

2. 容差:电容的容差会影响晶振的频率稳定性。

一般来说,选择容差较小的电容可以提高晶振的频率稳定性。

3. 温度系数:电容的温度系数也会影响晶振的频率稳定性。

选择温度系数较小的电容可以降低温度对晶振频率的影响。

4. 成本:不同容值和精度的电容价格不同,需要在满足性能要求的前提下考虑成本因素。

在实际应用中,可以使用以下公式计算晶振电容的值:

C = 1 / (2 * π * f * T)

其中,C 表示晶振电容的值,f 表示晶振的频率,T 表示电容的温度系数。

总之,选择合适的晶振电容需要考虑频率、容差、温度系数和成本等因素。

在实际应用中,可以根据具体情况进行计算和选择。

单片机晶振电路电容计算单片机晶振电路电容计算是单片机设计中的重要环节,它直接关系到系统的稳定性和准确性。

本文将详细介绍单片机晶振电路电容计算的方法和步骤,帮助读者了解并掌握此技术。

首先,让我们来了解一下晶振电路的基本原理。

晶振电路由晶体振荡器和负载电容组成。

晶体振荡器是一种能够稳定振荡的元件,其频率由振荡电路中的晶体谐振频率决定。

负载电容用于提供足够的电荷储存和放出以维持晶体振荡。

在实际应用中,我们需要根据系统要求选择合适的晶体振荡频率和负载电容。

晶体振荡频率一般由晶振器厂商提供,在数据手册中可以找到。

而负载电容则需要根据晶振器的频率和系统电路的情况进行计算。

首先,我们需要确定晶振电路的输入电容和输出电容。

输入电容是指振荡器输出端到芯片的输入端之间的电容,而输出电容则是指振荡器输入端到芯片的输出端之间的电容。

这两个电容分别由晶振器和芯片的引脚电容以及板上布线电容组成。

接下来,我们需要计算输入电容和输出电容的值。

计算公式如下:输入电容 = 输入引脚电容 + 板布线电容 + 芯片引脚电容输出电容 = 输出引脚电容 + 板布线电容 + 芯片引脚电容其中,输入引脚电容和输出引脚电容可以在芯片的数据手册中找到。

板布线电容一般为1-2pF,可以根据实际情况进行调整。

在具体计算过程中,我们需要注意保留有效位数,并进行四舍五入。

同时,需要注意单位的转换,通常晶振电路的电容单位为pF(皮法)。

最后,将计算得到的输入电容和输出电容作为参考值,在实际布线过程中根据需要适当调整,以满足系统设计要求。

总之,单片机晶振电路电容计算是一项重要且复杂的任务,需要结合实际系统情况和设计要求来进行。

通过合理选择和计算,可以保证系统的稳定性和准确性,提高单片机系统的性能。

读者在使用本文提供的方法时,应根据实际情况进行合理调整和应用。

希望本文能为读者在单片机晶振电路设计中提供指导和帮助。

什么是晶振的负载电容?(ZT)

晶体元件的负载电容是指在电路中跨接晶体两端的总的外界有效电容。

是指晶振要正常震荡所需要的电容。

一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。

要求高的场合还要考虑ic输入端的对地电容。

应用时一般在给出负载电容值附近调整可以得到精确频率。

此电容的大小主要影响负载谐振频率和等效负载谐振电阻。

晶振的负载电容=[(Cd*Cg)/(Cd+Cg)]+Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上电容).就是说负载电容15pf的话,两边个接27pf的差不多了,一般a为6.5~13.5pF

各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器. 晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联. 在晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十 M 欧之间. 很多芯片的引脚内部已经包含了这个电阻, 引脚外部就不用接了. 这个电阻是为了使反相器在振荡初始时处与线性状态, 反相器就如同一个有很大增益的放大器, 以便于起振.

石英晶体也连接在晶振引脚的输入和输出之间, 等效为一个并联谐振回路, 振荡频率应该是石英晶体的并联谐振频率. 晶体旁边的两个电容接地, 实际上就是电容三点式电路的分压电容, 接地点就是分压点. 以接地点即分压点为参考点,

振荡引脚的输入和输出是反相的, 但从并联谐振回路即石英晶体两端来看, 形成一个正反馈以保证电路持续振荡. 在芯片设计时, 这两个电容就已经形成了, 一般是两个的容量相等, 容量大小依工艺和版图而不同, 但终归是比较小, 不一定适合很宽的频率范围.

外接时大约是数 PF 到数十 PF, 依频率和石英晶体的特性而定. 需要注意的是: 这两个电容串联的值是并联在谐振回路上的, 会影响振荡频率. 当两个电容量相等时, 反馈系数是 0.5, 一般是可以满足振荡条件的, 但如果不易起振或振荡不稳定可以减小输入端对地电容量, 而增加输出端的值以提高反馈量.

设计考虑事项:

1.使晶振、外部电容器(如果有)与 IC之间的信号线尽可能保持最短。

当非常低的电流通过IC晶振振荡器时,如果线路太长,会使它对 EMC、ESD 与串扰产生非常敏感的影响。

而且长线路还会给振荡器增加寄生电容。

2.尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

3.当心晶振和地的走线

4.将晶振外壳接地

如果实际的负载电容配置不当,第一会引起线路参考频率的误差.另外如在发射接收电路上会使晶振的振荡幅度下降(不在峰点),影响混频信号的信号强度与信噪.

当波形出现削峰,畸变时,可增加负载电阻调整(几十K到几百K).要稳定波形是并联一个1M左右的反馈电阻.

晶振电路中如何选择电容C1C2

(1):因为每一种晶振都有各自的特性,所以最好按制造厂商所提供的数值选择外部元器件。

(2):在许可范围内,C1,C2值越低越好。

C值偏大虽有利于振荡器的稳定,但将会增加起振时间。

(3):应使C2值大于C1值,这样可使上电时,加快晶振起振。

在石英晶体谐振器和陶瓷谐振器的应用中,需要注意负载电容的选择。

不同厂家生产的石英晶体谐振器和陶瓷谐振器的特性和品质都存在较大差异,在选用时,要了解该型号振荡器的关键指标,如等效电阻,厂家建议负载电容,频率偏差等。

在实际电路中,也可以通过示波器观察振荡波形来判断振荡器是否工作在最佳状态。

示波器在观察振荡波形时,观察OSCO 管脚(Oscillator output),应选择100MHz带宽以上的示波器探头,这种探头的输入阻抗高,容抗小,对振荡波形相对影响小。

(由于探头上一般存在10~20pF的电容,所以观测时,适当减小在OSCO管脚的电容可以获得更接近实际的振荡波形)。

工作良好的振荡波形应该是一个漂亮的正弦波,峰峰值应该大于电源电压的70%。

若峰峰值小于70%,可适当减小OSCI及OSCO管脚上的外接负载电容。

反之,若峰峰值接近电源电压且振荡波形发生畸变,则可适当增加负载电容。

用示波器检测OSCI(Oscillator input)管脚,容易导致振荡器停振,原因是:部分的探头阻抗小不可以直接测试,可以用串电容的方法来进行测试。

如常用的4MHz石英晶体谐振器,通常厂家建议的外接负载电容为10~30pF左右。

若取中心值15pF,则C1,C2各取30pF 可得到其串联等效电容值15pF。

同时考虑到还另外存在的电路板分布电容,芯片管脚电容,晶体自身寄生电容等都会影响总电容值,故实际配置C1,C2时,可各取20~15pF左右。

并且C1,C2使用瓷片电容为佳。

问:如何判断电路中晶振是否被过分驱动?

答:电阻RS常用来防止晶振被过分驱动。

过分驱动晶振会渐渐损耗减少晶振的接触电镀,这将引起频率的上升。

可用一台示波器检测OSC输出脚,如果检测一非常清晰的正弦波,且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动;相反,如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动。

这时就需要用电阻RS来防止晶振被过分驱动。

判断电阻RS值大小的最简单的方法就是串联一个5k或10k的微调电阻,从0开始慢慢调高,一直到正弦波不再被削平为止。

通过此办法就可以找到最接近的电阻RS值。