第19讲 移位寄存器-3

- 格式:ppt

- 大小:381.50 KB

- 文档页数:16

5.3.3 移位寄存器指令移位寄存器指令又称自定义位移位指令。

移位寄存器指令格式如下:其中:DATA 为移位寄存器数据输入端,即要移入的位;S_BIT 为移位寄存器的最低位;N 为移位寄存器的长度和移位方向。

注意:1)移位寄存器的操作数据由移位寄存器的长度N (N 的绝对值≦64)任意指定。

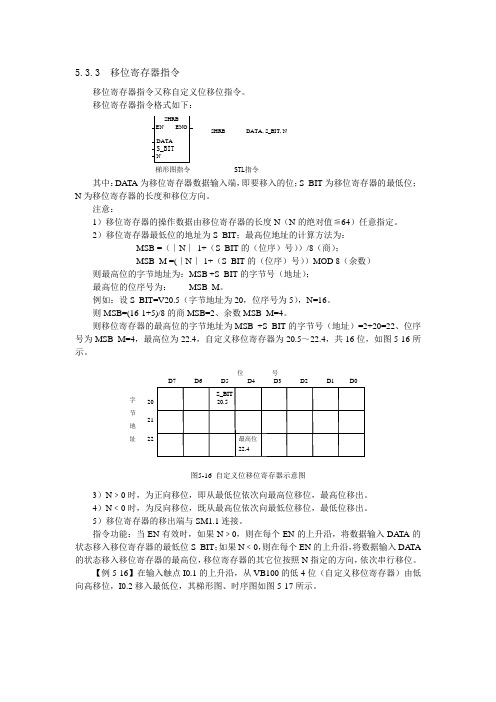

2)移位寄存器最低位的地址为S_BIT ;最高位地址的计算方法为: MSB =(∣N ∣-1+(S_BIT 的(位序)号))/8(商); MSB_M =(∣N ∣-1+(S_BIT 的(位序)号))MOD 8(余数) 则最高位的字节地址为:MSB +S_BIT 的字节号(地址); 最高位的位序号为: MSB_M 。

例如:设S_BIT=V20.5(字节地址为20,位序号为5),N=16。

则MSB=(16-1+5)/8的商MSB=2、余数MSB_M=4。

则移位寄存器的最高位的字节地址为MSB +S_BIT 的字节号(地址)=2+20=22、位序号为MSB_M=4,最高位为22.4,自定义移位寄存器为20.5~22.4,共16位,如图5-16所示。

图5-16 自定义位移位寄存器示意图3)N ﹥0时,为正向移位,即从最低位依次向最高位移位,最高位移出。

4)N ﹤0时,为反向移位,既从最高位依次向最低位移位,最低位移出。

5)移位寄存器的移出端与SM1.1连接。

指令功能:当EN 有效时,如果N ﹥0,则在每个EN 的上升沿,将数据输入DA TA 的状态移入移位寄存器的最低位S_BIT ;如果N ﹤0,则在每个EN 的上升沿,将数据输入DA TA 的状态移入移位寄存器的最高位,移位寄存器的其它位按照N 指定的方向,依次串行移位。

【例5-16】在输入触点I0.1的上升沿,从VB100的低4位(自定义移位寄存器)由低向高移位,I0.2移入最低位,其梯形图、时序图如图5-17所示。

EN DATANENO SHRB S_BIT梯形图指令STL指令SHRBDATA, S_BIT, N图5-17 移位寄存器应用示例本例工作过程:1)建立移位寄存器的位范围为V100.0~V100.3, 长度N=+4。

移位寄存器移位寄存器是暂时存放数据的部件,同时它还具有移位功能。

一、特点和分类从逻辑结构上看,移位寄存器有以下两个显著特征:(1)移位寄存器是由相同的寄存单元所组成。

一般说来,寄存单元的个数就是移位寄存器的位数。

为了完成不同的移位功能,每个寄存单元的输出与其相邻的下一个寄存单元的输入之间的连接方式也不同。

(2)所有寄存单元共用一个时钟。

在公共时钟的作用下,各个寄存单元的工作是同步的。

每输入一个时钟脉冲,寄存器的数据就顺序向左或向右移动一位。

通常可按数据传输方式的不同对CMOS移位寄存器进行分类。

移位寄存器的数据输入方式有串行输入和并行输入之分。

串行输入就是在时钟脉冲作用下,把要输入的数据从一个输入端依次一位一位地送入寄存器;并行输入就是把输入的数据从几个输入端同时送入寄存器。

在CMOS移位寄存器中,有的品种只具有串行或并行中的一种输入方式,但也有些品种同时兼有串行和并行两种输入方式。

串行输入的数据加到第一个寄存单元的D端,在时钟脉冲的作用下输入,数据传送速度较慢;并行输入的数据一般由寄存单元的R、S端送入,传送速度较快。

移位寄存器的移位方向有右移和左移之分。

右移是指数据由左边最低位输入,依次由右边的最高位输出;左移时,右边的第一位为最低位,最左边的则为最高位,数据由低位的右边输入,由高位的左边输出。

移位寄存器的输出也有串行和并行之分。

串行输出就是在时钟脉冲作用下,寄存器最后一位输出端依次一位一位地输出寄存器的数据;并行输出则是寄存器的每个寄存单元均有输出。

CMOS移位寄存器有些品种只有一种输出方式,但也有些品种兼具两种输出方式。

实际上,并行输出方式也必然具有串行输出功能。

表1表1是CMOS移位寄存器的分类。

二、常用CMOS移位寄存器简介1.串入-串出移位寄存器CD4006图1是18位移位寄存器CD4006的逻辑框图和引脚功能图。

由图可见,CD4006由四组移位寄存器组成,其中的两组为4位,每组有一输出端,由最高位引出。