数字逻辑课程设计基于FPGA的简单运算器

- 格式:docx

- 大小:557.14 KB

- 文档页数:33

基于FPGA的计算器设计基于FPGA(可编程逻辑门阵列)的计算器设计是一种使用FPGA开发板和硬件描述语言来实现的计算器。

它可以进行基本的数学运算,如加法、减法、乘法和除法等。

FPGA计算器不仅具有快速的运算速度和高度的可靠性,还具有较小的体积和低功耗。

FPGA计算器通常由输入、控制单元、运算单元和输出组成。

输入可以通过按钮、键盘或其他输入设备来实现。

控制单元负责解析输入并发出相应的控制信号。

运算单元是FPGA计算器的核心组件,它负责接收控制信号,并执行相应的运算操作。

输出单元将运算结果显示在计算器的屏幕上。

使用硬件描述语言(HDL)来实现FPGA计算器的设计可以提供高度的灵活性和可扩展性。

HDL允许开发人员通过编程方式定义逻辑门和电路功能,而不是通过物理硬件组件来实现。

这意味着开发人员可以根据需要添加新的运算功能,并且可以很容易地在FPGA计算器上进行修改和更新。

FPGA计算器可以通过对数据进行二进制表示来实现各种数学运算。

例如,加法可以通过将两个二进制数相加来实现。

具体实现可以使用查找表(Look-up Table)或全加器等组合逻辑电路来完成。

除法则比较复杂,通常需要使用除法算法来实现。

除了基本的数学运算,FPGA计算器还可以实现其他功能,如逻辑运算、位操作和存储器操作等。

逻辑运算可以用于实现条件语句和循环语句等流程控制功能。

位操作可以用于提取和修改数据的特定位。

存储器操作可以用于存储和读取数据。

基于FPGA的计算器设计有许多优点。

首先,FPGA计算器具有非常快的运算速度,比软件计算器更加高效。

其次,FPGA计算器具有较小的体积和低功耗,适合嵌入式系统或低功耗应用场景。

此外,由于FPGA计算器的硬件实现,它也具有较高的稳定性和可靠性。

然而,基于FPGA的计算器设计也存在一些挑战。

首先,硬件描述语言的学习成本较高,需要开发人员具备一定的硬件设计知识。

其次,FPGA 计算器的开发过程相对复杂,需要编写和调试大量的HDL代码。

【关键字】设计毕业设计(论文)题目: 基于FPGA 的计算器设计The design of calculator based on FPGA基于FPGA的计算器设计研究生:XX 指导老师:XX摘要本文介绍了一个简单计算器的设计,基于硬件描述语言VHDL采用了现场可编程逻辑器件FPGA进行设计,并在Altera公司的Quartus Ⅱ软件上实现仿真。

系统由键控模块、运算、保存模块和译码显示模块四个部分组成,计算部分为加法器、减法器、乘法器和除法器,保存部分需要3个保存器来实现:内部累加器(acc)、输入寄存器(reg)以及结果暂存器(ans)。

显示部分由四个七段译码管组成,分别来显示输入数字,输入部分采用外接键盘,外部的8个按键他们能以单键和组合键的形式完成0~9999之内的‘加’、‘减’、‘乘’、‘除’、‘符号变换’、‘保存数据’和‘读取数据’等七种功能运算其结构简单,易于实现。

关键词:FPGA;VHDL;计算器;设计The design of calculator based on FPGAGraduate Student: Dongdong Fan Supervisor: Shuxiang SongAbstractThis article describes the design of a simple calculator, the design uses Field Programmable Gate Array FPGA based on VHDL hardware description language to design and Altera's Quartus Ⅱ in software for emulation. This system is componented by the key control module, computing, storage and decoding display module of the four parts, the computing part include adder, subtractor, multiplier and divider,Storage part needs three memory to help achieved: internal accumulator (acc), input register (reg) as well as the results of registers (ans). Display part is made up four decoder of 7 sections, respectively to show the number of input. The 8 keys they can by single combined key forms to be completed addition, multiplication, division arithmetic operator and symbol transform,stored data and read seven function of operation within 0 to 9999 numbers.its structure is simple and easy to implement.Key words:FPGA; VHDL; calclute ; design目录第1章引言1.1 课程设计的目的与意义在人类学会交易的时候,计算也随之产生,而算盘作为计算最实用的工具存在了几千年。

基于fpga的简单课程设计一、课程目标知识目标:1. 学生能理解FPGA的基本概念,掌握FPGA的基本结构和原理;2. 学生能描述数字电路的基本组成,了解数字电路在FPGA中的应用;3. 学生能掌握Verilog HDL语言的基本语法和编程方法,并运用其设计简单的数字电路。

技能目标:1. 学生能运用FPGA设计软件进行电路设计和仿真;2. 学生能通过Verilog HDL编程实现基本的数字电路功能;3. 学生能对设计的FPGA电路进行调试和优化,提高电路性能。

情感态度价值观目标:1. 培养学生积极主动探索新知识、新技术,增强其对电子工程领域的兴趣;2. 培养学生具备团队协作精神,学会与他人共同解决问题,提高沟通与表达能力;3. 培养学生具备工程素养,关注工程伦理,认识到科技发展对社会的重要意义。

课程性质:本课程为实践性课程,注重培养学生的动手能力和创新能力。

学生特点:学生具备一定的电子技术基础,对FPGA技术有一定了解,具备基本的计算机操作能力。

教学要求:教师需结合学生特点和课程性质,采用任务驱动、案例教学等方法,引导学生主动参与课堂实践,提高学生的实际操作能力。

同时,注重培养学生的自主学习能力和团队合作精神,提高学生的综合素质。

通过课程目标的分解与实施,使学生在知识、技能和情感态度价值观方面取得具体的学习成果。

二、教学内容1. 数字电路基础- 数字逻辑基础:逻辑门、逻辑函数、逻辑代数;- 组合逻辑电路:编码器、译码器、多路选择器、算术逻辑单元;- 时序逻辑电路:触发器、计数器、寄存器。

2. FPGA基本原理- FPGA结构:逻辑单元、查找表、寄存器、布线资源;- FPGA编程原理:配置、重配置、上电配置;- FPGA设计流程:设计输入、综合、布局布线、仿真、下载。

3. Verilog HDL编程- 基本语法:模块、端口、信号、数据类型;- 语句结构:顺序语句、并行语句;- 基本数字电路设计:组合逻辑电路、时序逻辑电路、状态机。

摘要本次课程设计的任务是设计一个具有加减运算功能的简易计算器,并通过合适的方式来显示最后的计算结果。

此次设计电路的完成主要是利用简单的数字电路和电路逻辑运算来进行的。

简易加减计算器电路主要是对数据的输入与显示,数据的加减运算,数据的输出与显示三个主要的方面来设计研究完成的。

在输入电路的部分,我们通过开关的闭合与断开来实现数据的输入,开关闭合接入高电平“1”,断开接入低电平“0”。

而输入的数据将通过显示译码管以十进制的形式显示出来。

由于输入二进制的位数较多,我们采用个位十位分别输入的方式来简化电路。

加减运算电路则主要通过加法器来实现的。

设计电路时,我们将个位和个位、十位和十位分别接入一片加法器。

在进行加法运算时我们所选择的加法器是完全符合要求的,但是在进行减法运算时加法器就不能满足我们的设计要求了。

因此我们将减法转换为加法进行运算,运算时采用补码的形式。

在进行减法时通过异或门将减数的原码全部转换为补码,输入加法器中进行相加。

最后将进位信号加到十位的运算电路上就实现了加减法的运算电路。

在显示电路中,由加法器输出的数据是二进制码。

这些码可能表示超过十的数字,所以显示译码管就不能正确的显示出数字了。

此时要将二进制转化成BCD码,再将BCD 码送到显示译码管中就可以将计算所得的数字显示出来了。

概述1.1设计题目:简易加减计算器1.2设计任务和要求:1)用于两位以下十进制数的加减运算。

2)以合适的方式显示输入数据及计算结果。

1.3设计方案比较:方案一:输入十进制的数字,再通过编码器对十进制的数字进行编码,输出二进制的数据。

运用显示译码器对输入的数字以十进制的形式进行显示。

在进行加减计算的时候将二进制数字运用数模转换,然后再进行相加减。

然后将这些模拟信号再次转换成数字信号转换成数字信号,再将数字信号输入到显示译码管中来显示数剧。

这个方案中要进行数模转换和模数转换所需要的电路器件有些复杂,并且转换的时候需要很长的时间,而且转换以后数值的精度不高。

数字逻辑原理与FPGA设计课程设计一、前言数字逻辑与FPGA设计是电子信息工程领域中重要的基础课程。

本课程设计旨在让学生深入理解数字逻辑原理并将其应用于FPGA设计的实践中,提高学生的实践能力、创新能力和综合素质。

二、任务概述本次课程设计任务是设计一个8位计数器,能够实现自动计数和手动计数两种方式,并且实现在计数到特定值时自动停止计数的功能。

具体任务要求如下:2.1 模块设计设计一个包含以下五个模块的组合电路:•输入接口模块:包括计数器启动信号和计数方式选择信号两个输入信号。

•表计数模块:显示当前的计数值。

•计数控制模块:控制计数器的计数方向和停止计数。

•8位计数器模块:实现8位计数器的核心功能。

•自动重置模块:当计数值达到特定值时,自动重置计数器。

具体每个模块的设计需要根据具体需求来实现。

2.2 输入接口设计输入接口包括计数器启动信号和计数方式选择信号两个输入信号。

计数器启动信号为高电平有效信号,当计数器启动信号为高电平时,计数器开始工作。

计数方式选择信号为二进制信号,其中最低位选择自动计数或手动计数,次低位选择计数方向。

2.3 表计数模块设计表计数模块用于显示当前的计数值,以方便用户观察和使用。

计数值将以BCD码输出,同时显示在两个不同数码管上。

2.4 计数控制模块设计计数控制模块用于实现计数器的计数方向控制和停止计数功能。

计数方向控制信号包括加法计数和减法计数,停止计数信号表示计数器停止计数。

2.5 8位计数器模块设计8位计数器模块是本次课程设计的核心功能模块,用于实现基本的计数功能。

计数器顺序计数或者逆序计数,每次计数值递增或递减1。

2.6 自动重置模块设计当计数值达到特定值时,自动重置计数器。

这样可以方便地实现周期性计数功能。

三、实验流程3.1 硬件设计1.根据任务需求,完成每个模块的硬件设计。

2.所有硬件设计完成后,根据各模块的输入输出端口连接实现各个模块的组合电路设计。

3.2 Verilog代码实现1.根据硬件设计,编写各模块的Verilog代码。

基于FPGA的计算器设计引言:FPGA(Field-Programmable Gate Array)是一种现场可编程门阵列,它能够被重新编程以适应不同的电路设计需求。

基于FPGA的计算器设计具有很大的灵活性和可扩展性,可以实现不同类型的计算功能。

本文将介绍基于FPGA的计算器设计的原理、实现方法和一些相关应用。

一、基本原理1.输入部分:用于输入待计算的数字和操作符。

2.各种算术和逻辑运算电路:根据输入的操作符和数字,进行相应的计算操作。

3.结果显示部分:用于显示计算的结果。

二、实现方法1.设计算术和逻辑运算电路:根据计算器的需求,设计加法、减法、乘法、除法等算术运算电路,同时还要设计逻辑运算电路,如与门、或门、非门等。

2.设计输入模块:通过按键或其他输入方式输入待计算的数字和操作符。

3.设计控制模块:根据输入的操作符,控制算术和逻辑运算电路的工作顺序和时序。

4.设计结果显示模块:将计算结果显示在数码管或LCD屏幕上。

三、设计思路及具体实现方法1.输入模块设计:可以采用按键输入方式,数字键用于输入待计算的数字,功能键用于输入操作符。

2.算术与逻辑运算电路设计:通过组合逻辑电路设计实现各种算术和逻辑运算,如加法电路、乘法电路等。

将输入信号与操作符信号传入相应的运算电路,经过计算后得到结果。

3.控制模块设计:根据输入的操作符,控制算术和逻辑运算电路的工作顺序和时序。

可以使用状态机或者组合逻辑电路实现。

4.结果显示模块设计:将计算结果显示在数码管或LCD屏幕上。

根据计算结果的位数设计相应的显示模块。

四、应用领域基于FPGA的计算器设计可以用于各种计算任务,包括科学计算、金融计算、矩阵计算等。

除了基本的四则运算,还可以实现复杂函数的计算,如三角函数、指数函数等。

FPGA计算器还可以应用于数字信号处理、图像处理等领域,用于实时计算和数据处理。

五、设计优势与局限性1.优势:(1)灵活性高:FPGA可编程性强,可以根据需要重新编程,实现各种不同类型的计算功能。

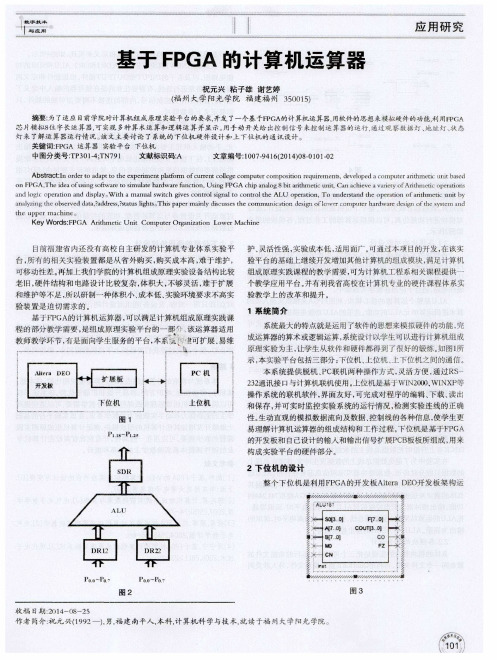

运算器摘要设计一个简单运算器。

由顶层电路、运算器、按键输入、控制信号产生、修正结果、显示等模块构成。

用Quartus II绘制原理图或编写VHDL程序,然后封装画出电路图,该简单运算器可以实现加、减法算数运算和与、异或逻辑运算,且该运算器设计完之后经过了Quartus II软件和FPGA实验板的下载验证。

关键词:运算器,Quartus II,VHDL程序1目录第一章系统原理 (5)1.1系统功能 (5)1.2系统原理图 (6)1.3电路设计原理 (6)第二章系统组成 (7)2.1按键模块 (7)2.1.1按键模块VHDL程序 (7)2.1.2按键模块仿真波形 (11)2.1.3按键模块电路封装图 (12)2.1.4按键模块功能 (12)2.2控制信号产生模块 (12)2.2.1控制模块VHDL程序 (12)2.2.2控制模块仿真波形 (15)2.2.3控制模块电路封装图 (15)2.2.4控制模块功能 (16)2.3修正模块 (16)2.3.1修正模块VHDL程序 (16)2.3.2修正模块仿真波形 (20)2.3.3修正模块电路封装图 (20)2.3.4修正模块功能 (21)2.4显示模块 (21)2.4.1显示模块VHDL程序 (21)2.4.2显示模块电路封装图 (24)2.4.3显示模块功能 (25)2.5运算器模块 (25)2.5.1运算器模块功能 (25)2.5.2运算器模块电路图 (25)第三章定制选择器 (26)3.1定制选择器 (26)3.2用VHDL符号图画运算器顶层电路图 (28)第四章下载验证及调试 (30)4.1器件选择及引脚设置 (30)4.2配置文件下载 (31)结论 (32)参考文献 (33)前言随着FPGA性能的不断完善,FPGA器件的种类日益丰富,受到世界范围内电子设计人员的普遍欢迎,并占据了较大的市场,其生产厂家也由原来的Xilinx公司一家增加到Altera、Actel、lattice等十几家公司。

基于FPGA的算术逻辑单元设计1. 引言随着计算机科学与技术的快速发展,人们对于高性能计算的需求越来越迫切。

在这个背景下,FPGA(Field-Programmable Gate Array)作为一种灵活可编程的硬件平台,被广泛应用于各种领域中。

本文将重点介绍基于FPGA的算术逻辑单元(ALU)设计。

2. 算术逻辑单元概述算术逻辑单元是计算机中负责执行各种算术和逻辑运算的核心模块。

它通常由多个逻辑门电路组成,可以实现加法、减法、乘法、除法等基本运算,同时还可以执行与、或、非等逻辑运算。

3. FPGA架构简介FPGA是一种可编程逻辑设备,其核心是由大量可编程的逻辑单元(Logic Element, LE)和存储器单元(Memory Element, ME)组成。

每个LE包含一个Look-UpTable(LUT)、一个触发器以及与其他LE和ME之间进行数据传输的开关。

通过对FPGA芯片进行编程,我们可以将LE和ME按照需要连接起来形成不同的电路结构,从而实现各种功能。

这种可编程性使得FPGA成为一种非常灵活和高效的硬件平台。

4. 基于FPGA的ALU设计在FPGA上设计ALU的过程可以分为以下几个步骤:4.1 确定功能需求首先,我们需要明确设计ALU的功能需求,包括支持的算术运算(如加法、减法、乘法、除法)、逻辑运算(如与、或、非)以及其他特殊功能(如移位操作、比较操作等)。

4.2 设计电路结构根据功能需求,我们可以设计ALU的电路结构。

这涉及到选择合适的逻辑门电路以及它们之间的连接方式。

在FPGA中,我们可以使用Look-Up Table(LUT)来实现逻辑门电路,并通过编程将LUT连接起来形成所需的电路。

4.3 实现电路连接在FPGA上进行编程时,我们需要将设计好的电路连接起来。

这包括将输入信号与LUT进行映射,以及将LUT之间的输出信号进行连接。

通过编程语言(如Verilog 或VHDL),我们可以指定这些连接关系。

运算器摘要设计一个简单运算器。

由顶层电路、运算器、按键输入、控制信号产生、修正结果、显示等模块构成。

用Quartus II绘制原理图或编写VHDL程序,然后封装画出电路图,该简单运算器可以实现加、减法算数运算和与、异或逻辑运算,且该运算器设计完之后经过了Quartus II软件和FPGA实验板的下载验证。

关键词:运算器,Quartus II,VHDL程序1目录第一章系统原理 (5)1.1系统功能 (5)1.2系统原理图 (6)1.3电路设计原理 (6)第二章系统组成 (7)2.1按键模块 (7)2.1.1按键模块VHDL程序 (7)2.1.2按键模块仿真波形 (11)2.1.3按键模块电路封装图 (12)2.1.4按键模块功能 (12)2.2控制信号产生模块 (12)2.2.1控制模块VHDL程序 (12)2.2.2控制模块仿真波形 (15)2.2.3控制模块电路封装图 (15)2.2.4控制模块功能 (16)2.3修正模块 (16)2.3.1修正模块VHDL程序 (16)2.3.2修正模块仿真波形 (20)2.3.3修正模块电路封装图 (20)2.3.4修正模块功能 (21)2.4显示模块 (21)2.4.1显示模块VHDL程序 (21)2.4.2显示模块电路封装图 (24)2.4.3显示模块功能 (25)2.5运算器模块 (25)2.5.1运算器模块功能 (25)2.5.2运算器模块电路图 (25)第三章定制选择器 (26)3.1定制选择器 (26)3.2用VHDL符号图画运算器顶层电路图 (28)第四章下载验证及调试 (30)4.1器件选择及引脚设置 (30)4.2配置文件下载 (31)结论 (32)参考文献 (33)前言随着FPGA性能的不断完善,FPGA器件的种类日益丰富,受到世界范围内电子设计人员的普遍欢迎,并占据了较大的市场,其生产厂家也由原来的Xilinx公司一家增加到Altera、Actel、lattice等十几家公司。

Altera公司的主要产品有:属于FPGA的FLEX、ACEX、APEX、Mercury、Excalibur、Stratix和Cyclone等系列;属于CPLD的MAX和Classic系列。

开发工具有,被普遍认为是最优秀PLD 开发平台之一的MAX+Plus II和支持APEX、Mercury、Excalibur、Stratix和Cyclone系列器件的Quartus II开发软件。

Cyclone系列器件是Altera公司推出的低价位FPGA产品,是Stratix系列的简化版,分为Cyclone I和Cyclone II两个系列。

Cyclone I系列产品为基于1.5V、采用0.13um全铜SRAM工艺的低成本FPGA。

Cyclone II 系列产品基于1.2V,采用0.09um全铜CMOS工艺,SRAM编程技术,其成本更低、容量更高、速度更快。

它和高性能的Stratix II系列的FPGA是目前Altera公司主流产品。

我的简单运算器主要是用VHDL语言编写,以Cyclone器件为依托,并下载到Altera仿真工具箱Cyclone-EP1C6Q240C8验证功能成功,能够初步完成简单运算器的雏形。

随着大规模集成电路技术和计算机技术的高速发展,在涉及通信、国防、工业自动化、计算机设计与应用、仪器仪表等领域的电子系统设计工作中,FPGA技术的含量正以惊人的速度提升。

电子类的新技术项目的开发也更多地依赖于FPGA技术的应用,特别是随着HDL等硬件描述语言综合功能和性能的提高,计算机中许多重要的元件(包括CPU)都用硬件描述语言来设计和表达,许多微机CPU、硬核嵌入式系统(如ARM、MIPS)、软核嵌入式系统(如NiosII)、大型CPU,乃至整个计算机系统都用FPGA来实现,即所谓的单片系统SOC或SOPC(System On a Chip、System On a Programmerable Chip)。

计算机和CPU的设计技术及其实现途径进入了一个全新的时代!不但如此,传统的CPU结构模式,如冯诺依曼结构和哈佛结构正在接受巨大的挑战。

例如美国Wincom Systems 公司推出一款令人惊叹的服务器,其核心部分是由FPGA完成的超强功能CPU。

该系统工作能力超过50台DELL或IBM计算机,或SUN Microsystems 公司的服务器。

该服务器的处理速度要比传统服务器快50到300倍。

我们知道,传统的PC机及服务器通常采用诸如Intel公司的奔腾处理器或SUN公司的SPARC芯片作为中央处理单元,而Wincom Systems的这款产品却没有采用微处理器,而是由FPGA芯片驱动。

FPGA芯片的运行速度虽比奔腾处理器慢,但可并行处理多项任务,而微处理器一次仅能处理一项任务。

因此,Wincom Systems的服务器只需配置几个价格仅为2000多美元的FPGA芯片,便可击败SUN公司的服务器或采用Intel处理器的计算机。

50多年前,匈牙利数学家冯诺依曼提出了计算机的设计构想:通过中央处理器从储存器中存取数据,并逐一处理各项任务。

然而现在,却采用FPGA取代传统微处理器获得了更高的性能,致使美国Xilinx公司的首席执行官Willem Roelandts认为:“由冯诺依曼提出的电脑架构已经走到尽头”,“可编程芯片将掀起下一轮应用高潮”。

FPGA芯片操作灵活,可以重复擦写无限次,而微处理器均采用固定电路,只能进行一次性设计。

设计人员可通过改变FPGA中晶体管的开关状态对电路进行重写,即重配置,从而尽管FPGA芯片的时钟频率要低于奔腾处理器,但是由于FPGA芯片可并行处理各种不同的运算,所以可以完成许多复杂的任务。

正如Willem Roelandts所说的,“我们认为下一代超级电脑将基于可编程逻辑器件”,他声称,这种机器的功能比目前最大的超级电脑还要强大许多倍。

EDA 专家William Carter认为,只要EDA开发工具的功能允许,将有无数的证据证明FPGA 具有这种神奇的能力,进而实现基于FPGA的超级电脑的开发。

此外,美国加州大学伯克利分校和杨百翰大学的研究人员也正在设计基于FPGA的电脑,这些电脑可在运行中实现动态重配置。

这对定位危险目标等军事应用和面容识别之类的计算密集型安全应用十分有用。

由此看来,在计算机应用领域和计算机系统设计领域中,EDA技术和FPGA的应用方兴未艾!硬件描述语言HDL(Hardware Description Language)是EDA技术的另一重要组成部分,常见的HDL有:VHDL、Verilog HDL、System Verilog和SystemC。

其中VHDL、Verilog在现在EDA设计中使用最多,也得到几乎所有的主流EDA工具的支持。

而后两种HDL 语言尚处于完善过程中。

VHDL语言具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大简化了硬件设计任务,提高了设计效率和可靠性。

V HDL具有与具体硬件电路无关和与设计平台无关的特性,并且具有良好的电路行为描述和系统描述能力,在语言易读性和层次化结构设计方面表现了强大的生命力和应用潜力。

因此,VHDL支持各种模式的设计方法:自顶向下与自底向上或混合方法,在面对当今许多电子产品生命周期缩短,需要多次重新设计以融入最新技术、改变工艺等方面, VHDL都表现了良好的适应性。

第一章系统原理1.1系统功能该系统是基于FPGA设计的简单运算器,可以实现简单的-7到+7范围内的加、减、与、以及异或四则运算。

将设计好的系统电路图与硬件实验板相连接,进行运算验证。

该实验板由一个8按键电路和一个32位LCD显示器组成,通过相应的按键输入把运算结果显示在LCD显示器上。

1.2系统原理图1.3电路设计原理该运算器电路由按键输入、控制、修正、显示和运算五大模块组成,来实现加、减、与、异或运算功能。

首先按键模块用于输入两个数和运算符,通过控制模块传送到运算器模块进行运算,再连接到修正模块,通过修正模块对“溢出”的数值进行修正,最后显示模块功能实现把运算过程反应到LCD显示器上。

第二章系统组成2.1按键模块2.1.1按键模块VHDL程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY KEY ISPORT(EN:OUT STD_LOGIC;YSF:OUT STD_LOGIC_VECTOR(1 DOWNTO 0);RSTN,CLK:IN STD_LOGIC;KEYA,KEYB:IN STD_LOGIC;KADD,KSUB,KAND,KXOR,KEQU:IN STD_LOGIC;A,B,C,D:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);XSYSF:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);XA,XB:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END KEY;ARCHITECTURE ARCH OF KEY ISSIGNAL TKADD,TKSUB,TKAND,TKXOR,TKEQU :STD_LOGIC;SIGNAL TA,TB:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGIN----保存A------PROCESS (KEYA,RSTN)BEGINIF RSTN='0' THEN TA<="0000";ELSIF (KEYA'EVENT AND KEYA='1')THENTA<=TA+1;END IF;END PROCESS;-----保存B------PROCESS (KEYB,RSTN)BEGINIF RSTN='0' THEN TB<="0000";ELSIF(KEYB'EVENT AND KEYB='1')THENTB<=TB+1;END IF;END PROCESS;------获取信号------PROCESS(RSTN,KADD)BEGINIF RSTN='0' THEN TKADD<='0';ELSIF (KADD'EVENT AND KADD='1')THEN TKADD<='1';END IF; END PROCESS;------------------PROCESS(RSTN,KSUB)BEGINIF RSTN='0' THEN TKSUB<='0';ELSIF (KSUB'EVENT AND KSUB='1')THEN TKSUB<='1';END IF; END PROCESS;--------PROCESS(RSTN,KAND)BEGINIF RSTN='0' THEN TKAND<='0';ELSIF (KAND'EVENT AND KAND='1')THEN TKAND<='1';END IF; END PROCESS;PROCESS(RSTN,KXOR)BEGINIF RSTN='0' THEN TKXOR<='0';ELSIF (KXOR'EVENT AND KXOR='1')THEN TKXOR<='1';END IF;END PROCESS;-------------PROCESS(RSTN,KEQU)BEGINIF RSTN='0' THEN TKEQU<='0';ELSIF (KEQU'EVENT AND KEQU='1')THEN TKEQU<='1';END IF;END PROCESS;PROCESS(RSTN,CLK,TKADD,TKSUB,TKAND,TKXOR,TKEQU,TA,TB)BEGINIF RSTN='0' THEN YSF<="00";EN<='0';XSYSF<="00100000";ELSIF(CLK'EVENT AND CLK='1') THENIF TKADD='1' THEN YSF<="00";XSYSF<="00101011";A<=TA;B<=TB;END IF;IF TKSUB='1' THEN YSF<="01";XSYSF<="00101101";A<=TA;B<=TB;END IF;IF TKAND='1' THEN YSF<="10";XSYSF<="00101010";A<=TA;C<=TB;END IF;IF TKEQU='1' THEN EN<='1';END IF;END IF;END PROCESS;PROCESS(TA,TB,CLK)BEGINIF(CLK'EVENT AND CLK='1')THENCASE TA ISWHEN "0000"=>XA<="00110000";WHEN "0001"=>XA<="00110001";WHEN "0010"=>XA<="00110010";WHEN "0011"=>XA<="00110011";WHEN "0100"=>XA<="00110100";WHEN "0101"=>XA<="00110101";WHEN "0110"=>XA<="00110110";WHEN "0111"=>XA<="00110111";WHEN "1000"=>XA<="00111000";WHEN "1001"=>XA<="00111001";WHEN "1010"=>XA<="01000001";WHEN "1011"=>XA<="01000010";WHEN "1100"=>XA<="01000011";WHEN "1101"=>XA<="01000100";WHEN "1110"=>XA<="01000101";WHEN "1111"=>XA<="01000110";WHEN OTHERS =>NULL;END CASE;CASE TB ISWHEN "0000"=>XB<="00110000";WHEN "0001"=>XB<="00110001";WHEN "0010"=>XB<="00110010";WHEN "0011"=>XB<="00110011";WHEN "0100"=>XB<="00110100";WHEN "0101"=>XB<="00110101";WHEN "0110"=>XB<="00110110";WHEN "0111"=>XB<="00110111";WHEN "1000"=>XB<="00111000";WHEN "1001"=>XB<="00111001";WHEN "1010"=>XB<="01000001";WHEN "1011"=>XB<="01000010";WHEN "1100"=>XB<="01000011";WHEN "1101"=>XB<="01000110";WHEN "1110"=>XB<="01000101";WHEN "1111"=>XB<="01000110";WHEN OTHERS=>NULL;END CASE;END IF;END PROCESS;END ARCH;2.1.2按键模块仿真波形2.1.3按键模块电路封装图2.1.4按键模块功能实现对按键的设定及控制,得以把运算数据输入电路。