数字方法中频信号相干检波实现

- 格式:pdf

- 大小:298.66 KB

- 文档页数:9

相干解调的方法和过程

相干解调是一种常用的信号处理技术,它可以将信号从高频转换为低频,从而方便信号的处理和分析。

相干解调的方法和过程如下:

1. 信号混频

相干解调的第一步是将信号混频,即将信号与一个高频信号相乘。

这个高频信号通常称为本振信号,它的频率比原信号高得多。

混频后,原信号的频率被转换为中频,方便后续处理。

2. 中频滤波

混频后得到的中频信号包含了原信号和本振信号的和与差,需要进行滤波以去除不需要的部分。

中频滤波器通常采用带通滤波器,只保留原信号的频率范围,去除其他频率的干扰。

3. 相干检波

经过中频滤波后,得到的信号仍然是一个复数信号,需要进行相干检波,将其转换为实数信号。

相干检波的方法是将中频信号与本振信号相乘,然后进行低通滤波,只保留信号的直流分量。

4. 解调输出

经过相干检波后,得到的信号就是原信号的解调输出。

这个信号可以进行进一步的处理和分析,例如进行数字信号处理、频谱分析等。

相干解调的方法和过程比较复杂,需要使用专门的电路和算法来实现。

但是,相干解调具有高精度、高灵敏度、高抗干扰性等优点,被广泛应用于通信、雷达、医学等领域。

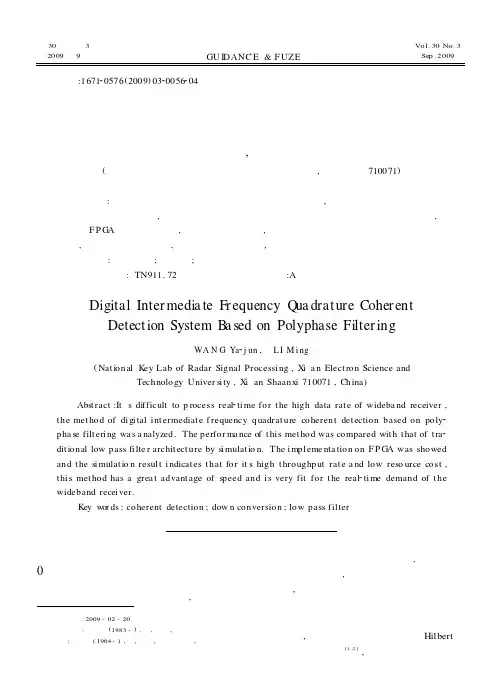

第30卷 第3期2009年9月制 导 与 引 信GU I DANC E &F UZEVol.30No.3Sep.2009文章编号:167120576(2009)0320056204基于多相滤波的数字中频正交相干检波系统王亚军, 李 明(西安电子科技大学雷达信号处理国家重点实验室,陕西西安710071) 摘 要:针对宽带接收机数据率高而难以实时处理的问题,分析了基于多相滤波的数字中频正交相干检波方法,仿真比较了该方法与基于传统结构低通滤波器的实现方法的性能,给出了在F P G A 中的实现结构,并进行了仿真验证,证明了该方法可以在不增加资源消耗量的同时,大大提高系统吞吐率,具有明显的速度优势,能较好地满足宽带接收机的实时性要求。

关键词:相干检波;下变频;低通滤波器中图分类号:TN911.72 文献标识码:ADigital Inter media te Fr equency Q ua drature Coher entDetection System B a sed on Polyphase Filter ingWA N G Ya 2j un , L I M i ng(Nat ional K ey Lab of Radar Signal Processi ng ,X i ’a n Elect ron Science andTechnology Univer si ty ,X i ’an Shaanxi 710071,China) Abst ract :It ’s difficult to p rocess real 2ti me for t he high data rat e of wideba nd receiver ,t he met hod of di gi tal i nt ermediat e f requency quadrat ure coherent det ection based on poly 2pha se filt eri ng wa s a nalyzed.The perfor ma nce of t hi s met hod was compared wit h t hat of t ra 2dit ional low pass fi lte r archit ect ure by si mulat io n.The i mpl eme nta tion on F P G A was showed and t he si mulat io n resul t i ndicat es t hat for it s high t hroughput rat e a nd low reso urce cost ,t hi s met hod has a grea t advant age of speed and i s very fit for t he real 2ti me demand of t he wideband recei ver.K ey w or ds :coherent detection ;dow n conversion ;low pass fil ter收稿日期:2009-02-20作者简介王亚军(3),男,硕士,主要从事实时信号处理的研究;李 明(6),男,教授,博士生导师,主要从事雷达系统设计、雷达信号处理与监测、高速实时信号处理等的研究。

数字中频信号处理

数字中频信号处理主要包括以下步骤:

1.数字下变频:将数字中频信号(通常是经过A/D采样后的信号)

下变频至基带或低通滤波器的带宽。

这可以通过数字混频器实现,其中数字混频器将数字中频信号和数控振荡器(NCO)产生的正交本振信号相乘,将感兴趣的信号下变频至零中频。

2.低通滤波:在下变频过程中,带外信号会被滤除,只保留有用的

信号。

这是通过低通滤波器实现的。

3.采样速率转换:降低采样速率,以利于后续信号处理。

这可以通

过采样速率转换器实现。

4.取模检波:在某些情况下,可能需要从下变频后的信号中提取有

用的信息。

这可以通过取模检波模块实现。

在处理数字中频信号时,需要注意以下几点:

1.频率分辨率:在数字下变频过程中,需要选择合适的滤波器带宽

和采样速率,以确保频率分辨率足够高,能够准确地表示信号的频率成分。

2.抗干扰能力:数字中频信号处理对干扰比较敏感,因此需要采取

措施提高系统的抗干扰能力。

例如,可以增加信号的信噪比(SNR),或者使用抗干扰算法来减小干扰的影响。

3.处理速度:数字中频信号处理的计算量较大,需要使用高速处理

器或者专门的数字信号处理器(DSP)进行计算。

4.稳定性:数字中频信号处理要求系统稳定可靠,避免因处理过程

中出现问题而导致信号失真或者出现其他问题。

matlab中频正交检波函数-回复Matlab中频正交检波函数是一种常用的数字信号处理方法,用于将频域信号转换为时域信号。

它在通信系统、雷达系统、无线电系统等领域中被广泛使用。

本文将详细介绍频正交检波函数的原理、实现方法以及应用。

文章将分为以下几个部分进行阐述。

第一部分:频正交检波函数的原理及背景介绍(300字)在数字通信中,频率是指信号在单位时间内波动的次数。

频率可以用于描述信号的周期性,是信号最基本的特征之一。

频率正交检波(Frequency Orthogonal Demodulation, FOD)是一种将频域信号转换为时域信号的方法。

在频正交检波中,信号经过傅里叶变换得到频谱,然后通过正交变换将频谱转换为时域信号。

这种信号处理方法可以帮助我们更好地分析和处理信号。

第二部分:频正交检波函数的基本原理(500字)频正交检波函数的基本原理是将频域信号进行正交变换,使其转换为时域信号。

具体步骤如下:1. 首先,将待处理的信号通过傅里叶变换转换为频谱信号。

2. 然后,通过正交变换将频谱信号转换为时域信号。

常用的正交变换方法包括快速傅里叶变换(FFT)和离散余弦变换(DCT)等。

3. 最后,对转换后的时域信号进行去噪、解调、调制等处理,得到我们需要的信号。

频正交检波函数的基本原理就是通过频谱信号和正交变换将频域信号转换为时域信号,从而方便我们对信号进行进一步处理和分析。

第三部分:频正交检波函数的实现方法(500字)在Matlab中,可以使用一些内置的函数来实现频正交检波。

首先,通过fft函数将信号进行傅里叶变换得到频谱信号。

然后,通过ifft函数将频谱信号进行逆傅里叶变换,得到时域信号。

具体实现代码如下:matlab将信号进行傅里叶变换得到频谱信号spectrum = fft(signal);将频谱信号进行逆傅里叶变换得到时域信号reconstructed_signal = ifft(spectrum);通过上述代码,我们可以实现将频域信号转换为时域信号的功能。

基于FPGA的数字正交检波的实现作者:靳鹏来源:《电子世界》2014年第06期【摘要】阐述了数字正交检波的基本原理,设计完成了数字正交检波在FPGA中的实现,最后给出了测试结果,验证了设计的正确性。

【关键词】正交检波;FPGAImplementation of Digital Orthogonal Demodulation based on FPGAJin PengAbstract:The basic principle of digital orthogonal demodulation is ter,it expounds the implementation of digital orthogonal demodulation in FPGA.Finally,the measurement is performed to verify the correctness of the design.Keywords:Orthogonal Demodulation;FPGA随着软件无线电技术的发展,传统的模拟接收机已经被数字接收机所取代。

相对于模拟接收机中所使用的模拟正交检波,现在的数字接收机中普遍使用数字正交检波,直接对中频信号进行采样,将模拟中频信号转换为数字信号,之后在数字域对信号进行处理,得到两路正交的基带信号[1]。

这种方法相较于传统的模拟正交检波方法,具有非常高的精度和稳定性,并且可以提高系统的灵活性。

目前,数字正交检波主要是通过使用专用可编程芯片、DSP和FPGA 这三种方式来实现。

FPGA具有出色的并行处理能力,适用于相关运算和滤波等各种复杂的数字信号处理运算。

此外,FPGA的可编程性使其具有极大的灵活性,非常便于系统的功能扩充和升级,是目前被普遍采用的一种数字正交检波实现方法。

本文基于Altera公司的StratixⅢ系列中的EP3SE110F1152来实现对一中频窄带信号的数字正交检波及后续处理。

来源:电子科技作者:何光明黄云介绍一种利用带通采样定理及多相滤波的方式实现数字相干检波的方法,由于采用数字信号处理的方式获取I、Q基带信号,因此具有镜频抑制能力强、线性动态范围大、系统设备简单、一致性好等优点。

文章主要从理论及工程实现两个方面展开论述。

1 基本原理设某一数字滤波器的脉冲响应为h(n),则其Z变换H(z)定义为对式(1)展开变换后,可得令则式(2)即为数字滤波器H(z)多相滤波结构,显然H(z)由D个EK(z),K=0,1,2,…,D-1分支滤波器构成,并且每个滤波器的阶数为H(z)阶数的1/D,这种多相滤波的结构不仅能够提高系统实时处理能力,而且可以降低传统滤波器滤波运算后的累计误差。

下面对多相滤波技术在数字相干检波中的应用进行理论分析。

通常,对于载频为fo的带限(带宽B)中频信号,若以采样率为fs=4fo/(2m+1),m=O,1,2,…,且fs≥2B对其采样,通过符号修正及多相滤波的方式可准确获得正交的两路基带信号,如图1所示。

设信号x(t)=a(t)cos[2πfot+φ(t)],若以采样率为fs=4fo/(2m+1),m=0,1,2,…,且fs≥2B 对x(t)采样后得到的采样序列为式中,分别为信号的同向分量和正交分量,对x(n)进行奇偶分路和符号变换,可以得到显然,和分别为同向分量和正交分量的2倍抽取序列,容易证明和的数字谱为式(7)和式(8)描述了正交解调后同向I及正交Q支路的频谱,但二者的数字谱相差一个延迟因子,这相当于在时域上相差O.5个采样点,需要两个延迟滤波器校正,这两个滤波器需要满足,两路延迟滤波器需要具有相似的幅度或相位特性,保证、支路严格匹配。

理论分析知,可以采用多相滤波的方式从一原型低通滤波器中取出数字谱相差的两个支路分别对I、Q两路延迟滤波,由于两个滤波器是从同一个原型滤波器中抽取出来的两个分支,因此具有相似的幅度及相位特性。

设原型滤波器的冲击响应为h(n),由(1)式知,其多相结构第K条支路的冲击响应为则EK(z)频率响应为令D=4,则式中除i=0项不为零外,其余均为零,所以求得提取K=3及K=1作为式(7)及式(8)I、Q两路延迟滤波,得由此可见,经过滤波,两个正交得基带信号在时间上完全对齐,满足数字正交相干检波的要求。

75. 信号传输中的相干检测技术是什么?75、信号传输中的相干检测技术是什么?在当今的信息时代,信号传输技术的发展日新月异,其中相干检测技术作为一种重要的手段,在通信、雷达、光通信等众多领域发挥着关键作用。

那么,到底什么是信号传输中的相干检测技术呢?要理解相干检测技术,我们首先得从信号本身说起。

信号,简单来讲,就是承载着信息的一种物理量,比如电磁波、光或者电脉冲等。

在传输过程中,这些信号可能会受到各种干扰和衰减,导致信息的准确性和完整性受到影响。

相干检测技术的核心在于“相干”这两个字。

所谓“相干”,就是指参与作用的信号之间存在着确定的相位关系。

通俗地说,就好像是一群步伐整齐的士兵,他们的行动有着明确的节奏和规律。

在信号传输中,相干检测利用了信号的相位、频率和幅度等信息。

与传统的非相干检测相比,它能够提供更精确、更灵敏的检测性能。

想象一下,我们要从一个嘈杂的环境中接收并解读一个微弱的信号。

如果使用非相干检测,就好比是闭着眼睛听声音,只能大概判断有没有声音,而对于声音的细节,比如是高音还是低音,节奏的快慢等,就很难分辨清楚。

但相干检测就像是睁开了眼睛,不仅能听到声音,还能看清声音的各种特征,从而更准确地理解所传递的信息。

具体来说,相干检测通常需要一个本地振荡器,它产生的信号与接收的信号具有相同的频率和稳定的相位关系。

这个本地振荡器就像是一把“标准的尺子”,用来与接收到的信号进行比较和测量。

通过将接收到的信号与本地振荡器产生的信号进行混频、滤波等处理,我们可以提取出信号中包含的相位和频率信息。

这就好比是用一把精准的天平来称量物品的重量,能够得到非常精确的结果。

相干检测技术在通信领域的应用十分广泛。

比如在无线通信中,它可以提高信号的接收灵敏度,增加通信距离,改善通信质量。

在光通信中,相干检测能够实现更高的数据传输速率和更远的传输距离。

在雷达系统中,相干检测有助于更准确地测量目标的距离、速度和方向等参数。

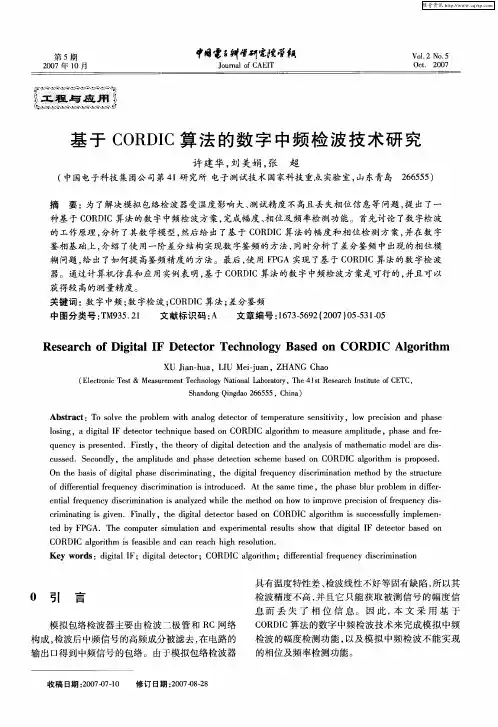

数字方法中频信号相干检波实现中航雷达与电子设备研究院陈斌陈文俊[摘要]本文阐述了雷达中频信号相干检波的原理,根据该原理使用FPGA对特定的雷达中频信号进行采样来实现正交数字相干检波,设计所使用软件是Mentor Graphics的FPGA Advantage,完成了从计算机仿真到硬件实现全过程并且获得了较高的性能,目前已投入实际应用中。

一、引言现代雷达大多采用全相参体制,因而相参信号处理是现代雷达中不可缺少的一部分。

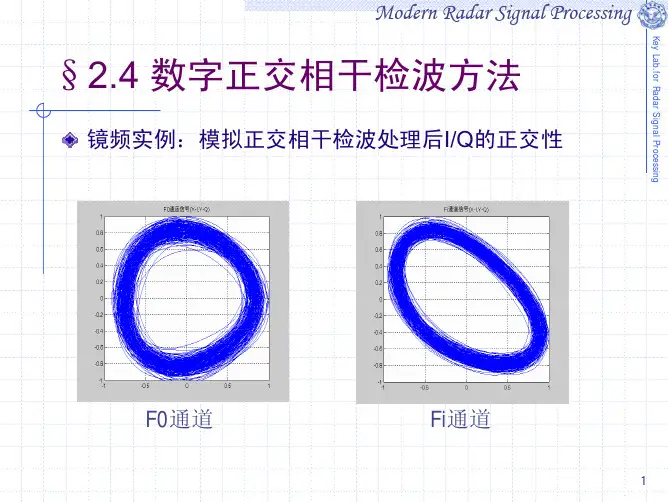

传统的正交I﹑Q通道检波器处理如图1所示,雷达接收到的中频信号分别用正交的两路相参信号混频,然后通过低通滤波器,得到I﹑Q两路基带信号,并用两路A/D变换器转换成数字信号送出。

图1 传统正交相干解调处理框图在雷达接收系统中,I﹑Q两个通道间的幅度不一致性以及相位正交误差是影响系统性能的重要因素。

模拟相干检波由于使用模拟乘法器﹑低通滤波器,器件本身存在不一致性﹑不稳定性,使I﹑Q两路通道存在较大的误差,所造成的镜频虚假信号电平很难低于-30dB,幅度误差一般只能达到0.5dB,而相位误差高达°3。

这极大限制了系统性能的提高,如导致雷达副瓣较高,对高性能的信号处理(如数字波束形成)已远远不能满足要求。

为了克服I﹑Q支路的幅相不平衡,可以用一路A/D变换器直接对中频带限信号进行采样,经数字处理产生零中频数字信号。

采用数字技术进行检波,I ﹑Q 两路信号的一致性好,精度高,但受A/D 芯片性能和后续数字信号处理能力的限制,目前提出的实现方法均要先将雷达中频信号下变频到一个便于处理的低中频,通过抗混迭滤波器限制带宽后送给A/D 变换电路进行数字化,由于前端预处理仍采用模拟乘法器和滤波器,其零点漂移和插入损耗对系统的性能仍会有一定的影响。

随着电子技术的高速发展,目前的器件水平和信号处理能力已经完全可以直接将雷达中频信号进行数字化,从而方便灵活的进行后端的信号处理。

二、基本原理雷达中频信号相干检波数字实现的原理为:根据窄带信号抽样定理选定f S =)12/(40−M f (M 为正整数),且(f S ≥2B )。

以采样率f S 对信号进行A/D 变换,再在数字域内用数字信号处理的办法进行正交检波得到正交的两路基带信号。

如图2所示。

图2 中频信号采样及数字相干检波的原理框图设信号)](cos[()()(0t t t A t S φω+=,以时间间隔T S =1/f S 对信号进行进行采样后2/)12(4/)12(2000ππω−=−=M M f f T S ,如果取M=1,则 S ()nT S =)](cos[()(0T T T S S S n n n A φω+=)2/cos()(cos )(πφn n n A T T S S-)2/sin()(sin )(πφn n n A T T S S=)2/sin()()2/cos()(ππn n Q n n I −=⎪⎩⎪⎨⎧−−+为奇数为偶数n n Q n n I n n ),(),()1()1(2/12/ (2.1)中频信号经上述采样之后,可以交替得到)(n I 和)(n Q 之值,但是在时间上差一个采样周期T S ,若要得到完整的正交I ﹑Q 两路信号,则需后续数字信号处理来实现。

根据雷达系统中对信号处理的要求,后继信号处理采用插值滤波法是比较合适的选择,插值滤波法采用了多相滤波结构的实时处理结构,既可以将信号速率在处理前降低1/D (D 为抽取倍数),又可以将滤波器的每一个分支滤波器的系数降为原型滤波器的N/D ,可以减少滤波运算的积累误差。

三、数字方法实现图5 数字电路实现框图具体的硬件电路主要由A/D 转换电路,FIFO ,FIR 滤波电路和时序控制电路等几个部分组成。

A/D 转换电路以24MHz 的采样率对扫频信号进行采样,两个FIFO 暂存数据流,以便后面的处理。

从第一个FIFO 出来的数据按奇偶分开,分别送给奇路和偶路的延时滤波器滤波,最后经过1/2抽取,数据流降为6MHz 。

整个电路如图5所示。

其中,A/D 转换器选用12位,典型信噪比68dB ,采样率可达65MSPS 的AD6640。

中频信号与A/D 的接口采用交流耦合,避免了模拟电路中难以克服的零漂的影响。

滤波电路的核心是延时滤波器的设计与实现,由于设计电路的实时性对滤波器的速度要求很高,本次设计中选用了Xilinx 公司的VII250 FPGA 实现,并将A/D和FIFO控制电路做到了FPGA中。

为了使得FPGA时序仿真和实现更为方便并且确保设计芯片的性能和质量可靠性,使用了Mentor公司先进高性能的FPGA设计工具套件FPGA Advantage来完成设计。

四、Mentor公司FPGA Advantage介绍Mentor Graphics公司的FPGA Advantage软件是业界公认的一款优秀的FPGA设计、仿真、综合和管理软件。

该软件为设计建立、管理、仿真调试与综合提供了一个完整的作业环境,使设计人员能够在最短的时间内将设计成功转化为实际产品。

该软件有几部分组成:HDL Designer、ModelSim、Precision RTL Synthesis。

其中,HDL Designer是设计创建和流程管理系列工具,支持HDL语言或原理图输入格式,通过图形化、文本或两者的组合,结合IP的引入,快速高效的创建设计,为提高设计效率和设计质量提供了不少帮助。

HDL可视化和统一的HDL 风格和文档能力,全面的VHDL、Verilog和mixed-HDL。

与仿真工具如ModelSim 和综合工具如Precision结合提供完整的FPGA设计流程。

ModelSim是仿真工具,具有快速的仿真性能和最先进的调试能力。

Precision RTL Synthesis是综合工具,随着新一代FPGA性能和复杂度的提高,时序收敛问题越来越严重,物理和逻辑层面的脱节成为FPGA设计的最大障碍。

传统的综合算法采用扇出负载来估计互连延时,在门级延时占主导的时候工作良好,但最新器件的互连延时逐渐成为主导,甚至达到总延时的70%以上,综合器如果不能准确估算互连延时,将造成设计的多次反复。

Precision Physical充分利用布线规则和延时信息对逻辑和布局同时优化,是业界唯一把逻辑、时序、物理视图集成在一个单一直观的环境里来控制时序的工具。

五、详细设计流程5.1 HDL设计输入图6 HDL语言设计输入界面首先将算法模块和控制部分模块编制完成,这里选择了VHDL语言实现几个部分的设计输入。

由于HDL Designer系列软件的设计输入界面对各种HDL语言的语法检查和编译后的错误定位功能十分强大,可以帮助设计者在设计的初期阶段轻松的排除语法错误。

顺利的进行下一步的模块集成。

图7 总框架下模块结构图如图7所示,整个逻辑设计分为三个主要部分,FIFO控制逻辑、1/2抽取电路、双路8级FIR电路,由于软件支持Mix-HDL编程方式,故算法实现用了VHDL 语言而测试向量选择了Verilog语言。

将测试向量文件test_bench.v和上述三个模块在TOP层的原理图界面上集成。

生成总原理框图。

见图8。

图8 TOP层原理框图其中从AD传入的数据(由test_bench模块生成)进入1/2抽取逻辑模块,完成对送入数据进行奇偶分离,并完成-1,0,1,0交替相乘的功能;双路8级FIR电路完成数据的滤波功能,最后处理的数据由送入DSP进行采集,再传回PC机中作FFT频谱分析;为了数据流缓冲需要,在数据输出端加入了FIFO器件,并在逻辑上加以控制使得数据能够不丢失的以DMA方式传入DSP。

5.2 ModelSim仿真调试由于仿真的是滤波器的输入端,仿真数据的选择真实性比较重要。

由于ModelSim软件支持直接将真实数据导入测试向量中作为测试激励。

所以这里使用的仿真数据是直接由AD公司AD6640评估板采集到的一组数据,通过Matlab 进行一些数据预处理后导入测试向量中的DATA数组中,以对算法进行检测。

如图9:图9 ModelSim仿真图由仿真结果测试算法流程工作正常,在八组奇偶数据输入滤波器后得出输出数据。

ModelSim杰出的仿真调试性能为实际工作的调试和差错带来极大的便利,在ModelSim仿真调试环境中把输出数据导出致数组中保存,并返回Matlab进行仿真。

证明设计的系统功能正确。

5.3Precision综合仿真完成后,用Precision综合器对设计进行到物理器件的综合。

图10 综合界面由于滤波器阶数较多,并且选择的是VII250速度等级最低的芯片。

AD芯片的采样最高速度65M,因此期望工作频率在75M以上即可以满足系统性能要求。

而经过Precision综合后实际工作频率可达89.1MHz,完全满足系统指标。

具体资源利用结果如下:IOs 69 172 40.12%Global Buffers 2 16 12.50%Function Generators 998 3072 32.49%CLB Slices 499 1536 32.49%Dffs or Latches 269 3588 7.50%时钟综合结果:Clock : FrequencyDesign_Clock : 322.9 MHzGlobel_clkREG/OUT :MHz89.1CLK : 237.0 MHz六、结论将实际板级产品的输出数据导入MatLab中分析,得到该方法对带内镜频抑制可以达到80db以上,完全满足系统的要求。

输入信号位数12bits,最后经过12bits*12bits运算得到24bits的乘法,再经过加法运算,在保证最后数据不溢出的情况下,数据位变成了27位,所以对应不同幅度的信号,最后数据位的取舍将决定信号的质量。

此处,最后的输出选定了第23-12位。

不同的输入信号(以dbm为单位),对应的输出如下所示。

(图中FFT 256点)图11 1dbm输入信号的最后输出数据仿真图图12 0dbm输入信号的最后输出数据仿真图设计实践证明,FPGA Advantage是一款非常优秀的设计工具,在实际设计项目中的应用可以确保产品的质量、可靠性并且提升设计效率。