曼彻斯特编码的verilog实现

- 格式:doc

- 大小:29.50 KB

- 文档页数:2

现代计算机2010.11基于FPGA 的曼彻斯特编解码器设计与实现刘远峰(暨南大学信息技术研究所,广州510075关键词:曼彻斯特编解码器;Verilog HDL ;ModelSim ;仿真收稿日期:2010-10-14修稿日期:2010-10-24作者简介:刘远峰(1969-,男,湖南株洲人,硕士,工程师,研究方向为自动化介绍基于Verilog HDL 设计的曼彻斯特编解码器模块,对曼彻斯特编解码器的原理进行介绍和分析,解决其编码和解码的同步问题,能够使解码器数据采样结果正确可靠,实现其编码和解码模块化,使用Verilog HDL 语言实现曼彻斯特编解码器的核心功能,并且在ModelSim 上实现其功能仿真。

摘要:0引言曼彻斯特编码(Manchester Encoding ,也叫做相位编码(PE,是一个同步时钟编码技术,被物理层使用来编码一个同步位流的时钟和数据。

曼彻斯特编码被用在以太网媒介系统中。

曼彻斯特编码提供一个简单的方式给编码简单的二进制序列而没有长的周期和转换级别,因而防止时钟同步的丢失,或来自低频率位移在贫乏补偿的模拟链接位错误。

1曼彻斯特码原理曼彻斯特码是将NRZ 普通二进制数据与其位率时钟信号相异或而得,解决了传输数据没有时钟的问题。

当传送信号为“1”,曼彻斯特编码由高电平跳变为低电平;若传送的信息为“0”;曼彻斯特编码由低电平转变为高电平;如果有连续的“1”或“0”信息出现时,则曼彻斯特编码保持“1”或“0”的跳变,即编码后,信息“0”与时钟一致,信息“1”与时钟反相(相位相差180度。

曼彻斯特编码是一种相位调制,有时钟的180度相位代表NRZ 信号的逻辑“1”电平。

2曼彻斯特码编码器设计由于曼彻斯特编码是将NRZ 普通二进制数据与其位率时钟信号相异或而得,因此,首先要产生位率时钟信号,同时,要解决位率时钟与NRZ 码的同步问题,保证NRZ 每个码元宽度占用一个周期的位率时钟信号,并且保证NRZ 码元输入时,立即产生位率时钟,这样就可以保证位率时钟与NRZ 码的同步。

合肥学院课程设计报告题目:基于FPGA的曼彻斯特编译码设计与实现系别:电子信息与电气工程系专业:通信工程班级: 10通信工程1班学号:07 01 12姓名:柯望吕烨邓超导师:段慧敏成绩:________________________2021年12月9日一、前言 ............................................................................................................................. 错误!未定义书签。

二、方案论证及选择 ....................................................................................................... 错误!未定义书签。

方案一........................................................................................................................... 错误!未定义书签。

方案二........................................................................................................................... 错误!未定义书签。

三、理论分析............................................................................................................... 错误!未定义书签。

伪随机序列模块........................................................................................................... 错误!未定义书签。

1.5.什么叫“综合”?一般“综合”包含哪些过程?答:在电子设计领域中“综合”的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

综合包含的过程:对VHDL或Verilog HDL进行处理分析,并将其转换成电路结构或模块,这时不考虑实际器件实现,即完全与硬件无关,这个过程是一个通用电路原理图形成的过程:第2步,对实际实现目标器件的结构进行优化,并使之满足各种约束条件,优化关键路径,等等。

2.10 使用Quartus II的 Mega Wizard Plug-In Manager宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0为电路的主频输入端,频率为50MHz;areset为异步置位端,c2和主频inclk0同频率。

c1为主频inclk0的倍频输出信号。

C0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

( 2014am)3.20 试用VHDL 语言设计一个曼彻斯特编码器。

已知有时钟信号clk_d、时钟的倍频信号clk及时钟的反相信号clk_dn。

串行数据输入为data_s,编码输出为mcode_out,输出使能信号为clk_lock_in,高电平有效(2012am)(2013am)(2014am)提示:曼彻斯特码(Manchester Code)又称为数字双相码或分相码(Split-phase Code)。

它的编码规则是:用分别持续半个码元周期的正(高)、负(低)电平组合表示信码“1”;用分别持续半个码元周期的负(低)、正(高)电平组合表示信码“0”。

图题3.20 用倍频时钟设计Manchester Code图题3.20 用双时钟设计Manchester Code 的仿真结果hsu_manchester_code_vmodule hsu_manchester_code_v ( clk,clk_d,clk_dn,data_s,clk_lock_in,mcode_out); input clk,clk_d,clk_dn,data_s,clk_lock_in;output mcode_out;reg mcode_out;reg temp_mcode_out;reg temp_mcode_out_ddn;always ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b1)temp_mcode_out<=clk_d;elsetemp_mcode_out<=1'b0;elsetemp_mcode_out=1'b0;endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b0)temp_mcode_out_ddn<=clk_dn;elsetemp_mcode_out_ddn<=1'b0;elsetemp_mcode_out_ddn=1'b0;Endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)mcode_out<=temp_mcode_out;temp_mcode_out_ddn;elsemcode_out<=1'b0;endendmodule3.21 试用VHDL 语言设计一个求两个数中最大值的程序,要求用函数调用的方法设计。

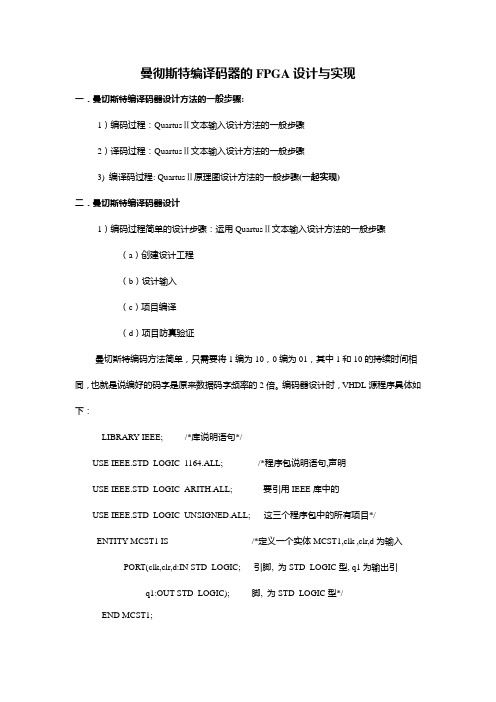

曼彻斯特编译码器的FPGA设计与实现一.曼切斯特编译码器设计方法的一般步骤:1)编码过程:QuartusⅡ文本输入设计方法的一般步骤2)译码过程:QuartusⅡ文本输入设计方法的一般步骤3) 编译码过程: QuartusⅡ原理图设计方法的一般步骤(一起实现)二.曼切斯特编译码器设计1)编码过程简单的设计步骤:运用QuartusⅡ文本输入设计方法的一般步骤(a)创建设计工程(b)设计输入(c)项目编译(d)项目防真验证曼切斯特编码方法简单,只需要将1编为10,0编为01,其中1和10的持续时间相同,也就是说编好的码字是原来数据码字频率的2倍。

编码器设计时,VHDL源程序具体如下:LIBRARY IEEE; /*库说明语句*/USE IEEE.STD_LOGIC_1164.ALL; /*程序包说明语句,声明USE IEEE.STD_LOGIC_ARITH.ALL; 要引用IEEE库中的USE IEEE.STD_LOGIC_UNSIGNED.ALL; 这三个程序包中的所有项目*/ENTITY MCST1 IS /*定义一个实体MCST1,clk ,clr,d为输入PORT(clk,clr,d:IN STD_LOGIC; 引脚, 为STD_LOGIC型, q1为输出引q1:OUT STD_LOGIC); 脚, 为STD_LOGIC型*/END MCST1;ARCHITECTURE divcnt OF MCST1 IS /*根据MCST1定义一个结构体名为divcnt*/ BEGINPROCESS(clk,clr) /*当clk, clr改变时,执行下面的进程*/BEGINIF(clr='1')THEN /*如果clr='1'*/q1<='0'; /* q1清0*/ELSEq1<=NOT(clk XOR d); /* clk与d的同或送q1*/END IF;END PROCESS;END divcnt;原理:当clr为1时,q1为0,则当clr为1时,把clk与d的同或送q1,若d在一个周期内为高电平时,所得的波形为clk波形。

MIL-STD-1553B总线曼彻斯特编解码器的FPGA实现张吉康; 刘恩海; 魏宏刚; 赵汝进【期刊名称】《《电子设计工程》》【年(卷),期】2019(027)015【总页数】5页(P103-107)【关键词】MIL-STD-553B总线; 曼彻斯特II型码; FPGA; VerilogHDL【作者】张吉康; 刘恩海; 魏宏刚; 赵汝进【作者单位】中国科学院光电技术研究所四川成都610209; 中国科学院大学北京100049【正文语种】中文【中图分类】TN79+1MIL-STD-1553B总线简称1553B总线,是一种集中式的时分制、命令/响应、多路传输的半双工串行数据总线标准[1]。

由于1553B总线具有应用灵活、可靠性高等优势,其已经在航空航天等军事领域有着广泛地应用[2],现在它同样广泛地应用在商业和工业系统中。

目前1553B应用主要采用专用的1553B协议芯片[3],比如DDC公司的BU-61580等。

系列专用芯片虽然实现了协议的功能,但在某些特定应用环境下芯片功能的冗余造成极大的资源浪费,且芯片使用灵活性较差,价格昂贵,占用PCB面积大[4],在一定程度上限制了设计者的应用开发。

1553B协议规定总线上传输的数据编码采用的是曼彻斯特II型双相码,曼彻斯特编解码器的性能会直接影响1553B总线的通信质量[5]。

1553B总线编解码器工作频率需达到兆赫兹以上,对时序的要求高;目前主流的FPGA器件集成了丰富的可编程逻辑门电路,具有精确高速的时序处理能力,在高速信号处理领域应用广泛。

因此,本文根据1553B总线具体的应用环境,为了降低工程成本、提高资源利用率及提高应用开发的灵活性,基于FPGA设计并实现了1553B总线中曼彻斯特II型码的编解码器。

1 曼彻斯特II型码原理1.1 1553B总线MIL-STD-1553B总线其全称是“飞机内部时分制指令/响应型多路传输数据总线”,数据编码采用曼彻斯特II型双相码,传输速率为1 Mb/s[6]。

基于 Verilog 的曼彻斯特Ⅱ型码解码器设计吴昊;周越文;毛东辉;翟颖烨【期刊名称】《计算机测量与控制》【年(卷),期】2012(20)7【摘要】In order to develop a 1553B bus convert board, a Manchester decoder was designed base on hardware description language. Firstly, few logic elements was described in verilog language to form logic blocks, secondly, constructed the decoder with it. In order to enhance the ability of anti —jamming, two methods has been proposed, one is the indentify sync header and find out benchmark of clock by edge — detecting method, the othe r is decode the Manchester type Ⅱ by a rule named of majority determining. Logic blocks coordination also been studied. The efficiency of this design has been proved by the timing stimulation in EDA environment, which can successful identify the sync header and decode the Manchester Ⅱ .%为研制1553B总线转换卡,给出了一种基于硬件描述的曼彻斯特Ⅱ型码解码器设计方案;该方案先利用Verilog语言描述少量逻辑单元(LE),构成逻辑处理模块,继而搭建出解码器;针对干扰问题,提出了边缘检测法识别同步头并寻找时钟基准和多数判定法解码曼彻斯特Ⅱ型码两种方法,并对不同模块之间同步等问题进行了研究;经过在EDA开发环境中进行时序仿真,结果显示设计满足需求,正确识别了状态/命令同步头,且曼彻斯特Ⅱ型码解码正确无误.【总页数】3页(P1989-1991)【作者】吴昊;周越文;毛东辉;翟颖烨【作者单位】空军工程大学自动测试实验室,西安 710038;空军工程大学自动测试实验室,西安 710038;空军工程大学自动测试实验室,西安 710038;空军工程大学自动测试实验室,西安 710038【正文语种】中文【中图分类】TP302【相关文献】1.基于FPGA的曼彻斯特码编解码器的实现 [J], 王铁男2.由LPC2104构成的曼彻斯特码解码器 [J], 张红兵3.1553B接口的曼彻斯特码解码器设计 [J], 李奕恒4.基于FPGA的曼彻斯特编解码器的设计 [J], 董毅;何刚强;梁汉文;倪凯诚;黄秋月5.基于Verilog HDL语言的一种奇偶校验码与极化码级联的编码器设计与仿真 [J], 彭逸飞因版权原因,仅展示原文概要,查看原文内容请购买。

//---------曼切斯特编码------------`timescale 1ns/1psmodule match( fifo_rd, //the enable single of superior fifo readfifo_out, //the out data of superior fifofifo_out_vaild, // the effective single of the out datafifo_empty, // the empty single of superior fifomach_out, //machester datai_clk_2, // double of hdlc clki_rst_n,clk);input i_rst_n;input fifo_out;input fifo_out_vaild;input fifo_empty;input i_clk_2;input clk;output fifo_rd;output mach_out;reg [5:0]out_count;reg [5:0]rd_count;reg fifo_rd;reg mach_out;reg [5:0]out_reg;reg [5:0]so_on;reg one;reg zero;reg temp;parameter rd_fifo_count=4'b1010;parameter mach_out_count=6'b010100;//20parameter rest=10;//-------控制fifo读---------------always @(posedge clk or negedge i_rst_n)beginif(!i_rst_n)fifo_rd<=0;else if(!fifo_empty && rd_count<rd_fifo_count && rd_count>0)fifo_rd<=1;else if(!fifo_empty && rd_count==0 && out_count==0)fifo_rd<=1;else if(rd_count==rd_fifo_count)fifo_rd<=0;elsefifo_rd<=0;end//----------fifo输出数据计?-----------always @(posedge clk or negedge i_rst_n)beginif(!i_rst_n)rd_count<=0;else if(fifo_rd && rd_count<rd_fifo_count)rd_count<=rd_count+1;elserd_count<=0;end//-----------manch数据输出-------------always @(posedge i_clk_2 or negedge i_rst_n )beginif(!i_rst_n)beginout_reg<=6'b111000;endelse if(fifo_out_vaild && out_count==0 )out_reg<=6'b111000;else if(out_count>0 && out_count<mach_out_count+8 ||out_count==mach_out_count+8)out_reg<={out_reg[4:0],temp};end//-------------控制输出mach------------always @(posedge i_clk_2 or negedge i_rst_n )beginif(!i_rst_n)begintemp<=0;zero<=0;one<=0;endelse if(fifo_out_vaild && fifo_out && zero==0)begintemp<=1;zero<=1;one<=0;endelse if(zero && fifo_out_vaild && fifo_out)begintemp<=0;zero<=0;one<=0;endelse if(fifo_out_vaild && !fifo_out && one==0)begintemp<=0;zero<=0;one<=1;endelse if(one && fifo_out_vaild && !fifo_out)begintemp<=1;one<=0;zero<=0;endelsebegintemp<=0;one<=0;zero<=0;endend//---------mach输出计数器--------------always @(posedge i_clk_2 or negedge i_rst_n)beginif(!i_rst_n)out_count<=0;else if(out_count==mach_out_count+8)out_count<=0;else if (fifo_out_vaild==1 && out_count==0)out_count<=out_count+1;else if(out_count>0 && out_count<mach_out_count+8)out_count<=out_count+1;endalways @(posedge i_clk_2 or negedge i_rst_n)beginif(!i_rst_n)mach_out<=1;elsemach_out<=out_reg[5];end endmodule。

NRZ(不归零码)转换位Manchester码的verilog实现码字转换器能够将数据流变换成⼀种已编码的格式,使接受机能够恢复数据。

接下来介绍四种常⽤的串⾏编码⽅法。

如果⾮归零码(NRZ)格式的数据流中,没有1或0的长序列,那么采⽤锁相环电路PLL就可以从该线数据中恢复出时钟(即将其⾃⾝与数据时钟同步);如果⾮归零反转码(NRZI)或者归零码(RZ)格式的数据流中不存在0的长序列,时钟就可以从数据流中恢复出来。

由于曼彻斯特(Manchester)码从数据中恢复时钟时与数据⽆关,因⽽很有吸引⼒,不过它需要更⼤的带宽。

⾸先给出Mealy型状态机表⽰的转换器代码及其测试代码/*Mealy型状态机输出不仅与当前状态有关,还与输⼊有关*/module NRZ_to_Manchester_Mealy(output reg B_out,input B_in, clk, reset_b);parameter S_0=2'd0,S_1=2'd1,S_2=2'd2,dont_care_state=2'bx,dont_care_out=1'bx;reg[1:0] state, next_state;always@(posedge clk or negedge reset_b)if(!reset_b)state<=S_0;elsestate<=next_state;always @(state, B_in)begin//这⾥的敏感列表最好不要包含B_in,否则会有⽆效输出//Mealy型状态机输出虽然与输⼊有关,但不⼀定因输⼊⽽变化,只会//因输⼊有不同的变化B_out=0;case(state)S_0:if(B_in)beginB_out=1;next_state=S_1;endelsenext_state=S_2;S_1:next_state=S_0;S_2:beginnext_state=S_0;B_out=1;enddefault:beginnext_state=dont_care_state;B_out=dont_care_out;endendcaseendendmodule测试代码:module NRZ_to_Manchester_Mealy_tb;reg clk, reset_b;reg B_in;wire B_out;reg count;initial beginclk=0;reset_b=1;B_in=0;count=0;#20 reset_b=0;#10 reset_b=1;#10000 $finish;endinitial begin$dumpfile("dump.lxt");$dumpvars(0,NRZ_to_Manchester_Mealy_tb);endinitialforever #10 clk=!clk;always @(posedge clk)count=count+1;always @(negedge clk)if(count)B_in={$random}%2;NRZ_to_Manchester_Mealy uut(.B_out(B_out),.B_in(B_in),.clk(clk),.reset_b(reset_b));endmodule对于Moore型状态机所表⽰的转换器,输出只与状态有关,⽽与输⼊⽆关。