DDR3引角定义

- 格式:pdf

- 大小:73.90 KB

- 文档页数:1

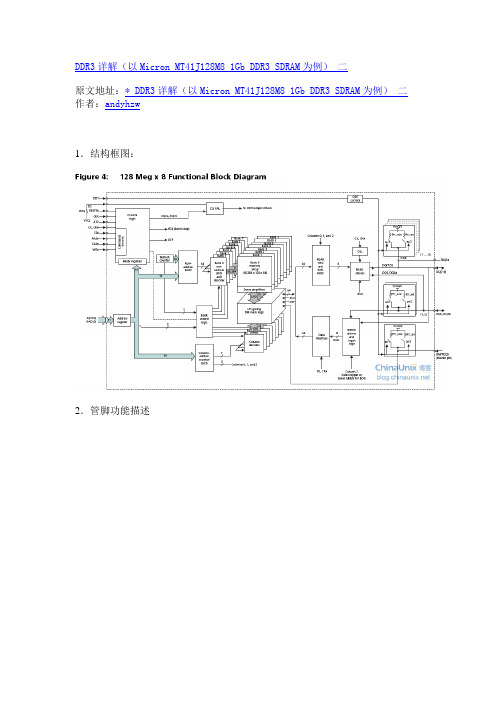

DDR3详解DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)⼆原⽂地址:* DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)⼆作者:andyhzw 1.结构框图:2.管脚功能描述3.状态图:Power on: 上电Reset Procedure: 复位过程Initialization: 初始化ZQCL: 上电初始化后,⽤完成校准ZQ电阻。

ZQCL会触发DRAM内部的校准引擎,⼀旦校准完成,校准后的值会传递到DRAM 的IO管脚上,并反映为输出驱动和ODT阻值。

ZQCS: 周期性的校准,能够跟随电压和温度的变化⽽变化。

校准需要更短的时间窗⼝,⼀次校准,可以有效的纠正最⼩0.5%的RON和RTT电阻。

Al:Additive latency.是⽤来在总线上保持命令或者数据的有效时间。

在ddr3允许直接操作读和写的操作过程中,AL是总线上的数据出现到进⼊器件内部的时间。

下图为DDR3标准所⽀持的时间操作。

Write Leveling:为了得到更好的信号完整性,DDR3存储模块采取了FLY_BY 的拓扑结构,来处理命令、地址、控制信号和时钟。

FLY_BY的拓扑结构可以有效的减少stub的数量和他们的长度,但是却会导致时钟和strobe信号在每个芯⽚上的flight time skew,这使得控制器(FPGA或者CPU)很难以保持Tdqss ,tdss和tdsh这些时序。

这样,ddr3⽀持write leveling这样⼀个特性,来允许控制器来补偿倾斜(flight time skew)。

存储器控制器能够⽤该特性和从DDR3反馈的数据调整DQS和CK之间的关系。

在这种调整中,存储器控制器可以对DQS信号可调整的延时,来与时钟信号的上升边沿对齐。

控制器不停对DQS进⾏延时,直到发现从0到1之间的跳变出现,然后DQS的延时通过这样的⽅式被建⽴起来了,由此可以保证tDQSS。

SD内存插槽及测试点一、实物图上图中,黑色插槽就是SD内存插槽二、测试点SD内存插槽测试点:1个供电、4个时钟、6个信号测试点VCC:供电测试点,正常电压3.3V,由场管或橙色线提供CLK0、CLK1、CLK2、CLK3:时钟测试点,频率66/100/133MHZ,电压1.1V-1.6V,由北桥或时钟芯片提供6个信号测试点:CAS#:列选信号RAS#:行选信号/WE#:允许信号(高电平允许读,低电平允许写)/CS#:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压DDR内存插槽及测试点一、实物图上图就是DDR内存插槽实物图二、测试点DDR内存插槽测试点:2个供电、6个时钟、6个信号测试点VCC=2.5V,1.25V:供电测试点CLK0、CLK1、CLK2、CLK3、CLK4、CLK5:时钟测试点,频率266/333/400MHZ,电压1.1V-1. 6V,如果主板有两块时钟芯片,内存时钟由靠近内存的时钟芯片提供;如果只有一个时钟芯片,内存的时钟由北桥提供6个信号测试点:CAS:列选信号RAS:行选信号WE:允许信号(高电平允许读,低电平允许写)CS:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压D58、D56、D18等:是数据线,对地打阻值正常值300-800DDR2内存插槽测试点2009-10-2 10:37:43文/xiaowang 出处:电脑维修家园DDR2内存插槽实物图如下:1、时钟信号点,共有8个时钟信号点,分别位于52、137、138、171、185、186、220、221针脚,正常进,时钟信号点工作电压为1.1V。

2、电压信号点,DDR2内存插槽有2种电压,其中238针脚为3.3V供电脚,51、53、56、59、62、64、69、72、75、78、170、172、175、1 78、181、187、189、191、194针脚为1.8V供电脚。

DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)二原文地址:* DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)二作者:andyhzw1.结构框图:2.管脚功能描述3.状态图:Power on: 上电Reset Procedure: 复位过程Initialization: 初始化ZQCL: 上电初始化后,用完成校准ZQ电阻。

ZQCL会触发DRAM内部的校准引擎,一旦校准完成,校准后的值会传递到DRAM的IO管脚上,并反映为输出驱动和ODT阻值。

ZQCS: 周期性的校准,能够跟随电压和温度的变化而变化。

校准需要更短的时间窗口,一次校准,可以有效的纠正最小0.5%的RON和RTT电阻。

Al:Additive latency.是用来在总线上保持命令或者数据的有效时间。

在ddr3允许直接操作读和写的操作过程中,AL是总线上的数据出现到进入器件内部的时间。

下图为DDR3标准所支持的时间操作。

Write Leveling:为了得到更好的信号完整性,DDR3存储模块采取了FLY_BY 的拓扑结构,来处理命令、地址、控制信号和时钟。

FLY_BY的拓扑结构可以有效的减少stub的数量和他们的长度,但是却会导致时钟和strobe信号在每个芯片上的flight time skew,这使得控制器(FPGA或者CPU)很难以保持Tdqss ,tdss和tdsh这些时序。

这样,ddr3支持write leveling这样一个特性,来允许控制器来补偿倾斜(flight time skew)。

存储器控制器能够用该特性和从DDR3反馈的数据调整DQS和CK之间的关系。

在这种调整中,存储器控制器可以对DQS信号可调整的延时,来与时钟信号的上升边沿对齐。

控制器不停对DQS进行延时,直到发现从0到1之间的跳变出现,然后DQS的延时通过这样的方式被建立起来了,由此可以保证tDQSS。

带图对比详解DDR3,DDR2,DDR内存条的区别【武汉电脑维修培训】课前热身图1就是三代内存的全家照,从上到下分别是DDR3、DDR2、DDR。

大家牢牢记住它们的样子,因为后面的内容会提到这幅图。

(图1)DDR3,DDR2,DDR外观区别防呆缺口:位置不同防插错图1红圈圈起来的就是我们说的防呆缺口,目的是让我们安装内存时以免插错。

我们从图1可以看见三代内存上都只有一个防呆缺口,大家注意一下这三个卡口的左右两边的金属片,就可以发现缺口左右两边的金属片数量是不同的。

比如DDR 内存单面金手指针脚数量为92个(双面184个),缺口左边为52个针脚,缺口右边为40个针脚;DDR2 内存单面金手指120个(双面240个),缺口左边为64个针脚,缺口右边为56个针脚;DDR3内存单面金手指也是120个(双面240个),缺口左边为72个针脚,缺口右边为48个针脚。

芯片封装:浓缩是精华在不同的内存条上,都分布了不同数量的块状颗粒,它就是我们所说的内存颗粒。

同时我们也注意到,不同规格的内存,内存颗粒的外形和体积不太一样,这是因为内存颗粒“包装”技术的不同导致的。

一般来说,DDR内存采用了TSOP(Thin Small Outline Package,薄型小尺寸封装)封装技术,又长又大。

而DDR2和DDR3内存均采用FBGA(底部球形引脚封装)封装技术,与TSOP相比,内存颗粒就小巧很多,FBGA封装形式在抗干扰、散热等方面优势明显。

TSOP是内存颗粒通过引脚(图2黄色框)焊接在内存PCB上的,引脚由颗粒向四周引出,所以肉眼可以看到颗粒与内存PCB接口处有很多金属柱状触点,并且颗粒封装的外形尺寸较大,呈长方形,其优点是成本低、工艺要求不高,但焊点和PCB的接触面积较小,使得DDR内存的传导效果较差,容易受干扰,散热也不够理想。

(图2)一颗DDR现代内存芯片焊接细节-黄色部分为焊接引脚FBGA封装把DDR2和DDR3内存的颗粒做成了正方形(图3),而且体积大约只有DDR内存颗粒的三分之一,内存PCB上也看不到DDR内存芯片上的柱状金属触点,因为其柱状焊点按阵列形式分布在封装下面,所有的触点就被“包裹”起来了,外面自然看不到。

DDR2上有三根--ODT\CAS\OCD的作用除了以上所说的区别外,DDR2还引入了三项新的技术,它们是OCD、ODT和Post CAS。

OCD(Off-Chip Driver):也就是所谓的离线驱动调整,DDR II通过OCD可以提高信号的完整性。

DDR II通过调整上拉(pull-up)/下拉(pull-down)的电阻值使两者电压相等。

使用OCD通过减少DQ-DQS的倾斜来提高信号的完整性;通过控制电压来提高信号品质。

不过,OCD技术在普通的应用领域所发挥的作用并不明显,而在服务器上使用,它的功能才能被充分发挥出来。

ODT:ODT是内建核心的终结电阻器。

我们知道使用DDR SDRAM的主板上面为了防止数据线终端反射信号需要大量的终结电阻。

它大大增加了主板的制造成本。

实际上,不同的内存模组对终结电路的要求是不一样的,终结电阻的大小决定了数据线的信号比和反射率,终结电阻小则数据线信号反射低但是信噪比也较低;终结电阻高,则数据线的信噪比高,但是信号反射也会增加。

因此主板上的终结电阻并不能非常好的匹配内存模组,还会在一定程度上影响信号品质。

DDR2可以根据自已的特点内建合适的终结电阻,这样可以保证最佳的信号波形。

使用DDR2不但可以降低主板成本,还得到了最佳的信号品质,这是DDR不能比拟的。

Post CAS:它是为了提高DDR II内存的利用效率而设定的。

在Post CAS操作中,CAS信号(读写/命令)能够被插到RAS信号后面的一个时钟周期,CAS命令可以在附加延迟(Additive Latency)后面保持有效。

原来的tRCD(RAS到CAS和延迟)被AL(Additive Latency)所取代,AL可以在0,1,2,3,4中进行设置。

由于CAS信号放在了RAS信号后面一个时钟周期,因此ACT和CAS信号永远也不会产生碰撞冲突。

不过要注意的是,Posted CAS功能的优势只有在那些读写命令非常频繁的运作环境下才能体现,对于一般的应用来说,开启Posted CAS功能反而会降低系统的整体性能。

DDR3内存引脚功能定义

1.VDDQ:电源电压引脚,提供内存模块的电源。

2.VSS:地引脚,为内存模块提供地连接。

3.DQ[0:63]:数据引脚,用于传输数据。

4.DM[0:7]:差分引脚,用于传输数据。

5.DQS[0:7]:数据时钟引脚,用于接收和发送数据。

6.DQS#:数据时钟反相引脚。

7.CLK:频率引脚,用于DDR3内存控制器的时钟输入。

8.RAS#:行地址选通引脚,用于指示访问的行地址。

9.CAS#:列地址选通引脚,用于指示访问的列地址。

10.WE#:写使能引脚,用于指示写操作。

11.CS#:片选引脚,用于选择内存芯片。

12.CKE:时钟使能引脚,用于控制内存芯片的时钟。

13.ODT:输出驱动器强制引脚,用于控制输出阻抗。

14.RESET#:复位引脚,用于将内存芯片复位到初始状态。

15.VREFCA:输入和输出引脚,用于提供中心对齐参考电压。

16.VREFDQ:数据引脚的输入和输出引脚,用于提供数据对齐参考电压。

17.ZQ:零电阻引脚,用于控制内存模块的电阻值。

18.SA[0:1]:副功能地址引脚,用于选择内存模块的副功能。

以上是DDR3内存引脚功能定义的主要内容。

每个引脚的具体功能可能会有一些变化,取决于内存模块的制造商和具体型号。

在使用DDR3内存时,正确连接和使用各个引脚是非常重要的,以确保内存模块的正常运行和性能。

FPGA BANK选择页面中的图是所选部件物理表示的架构视图。

默认情况下, MIG 将使用推荐的选择,地址/控制BANK和数据BANK是根据V6对不同频率的规则限定的。

选择您想要使用的BANK for内存接口,你用不着选择的实际的引脚。

默认情况下MIG将使用所选bank中的任意引脚for内存接口。

设计规则:∙设计最大频率:o-1 FPGA 速度级器件: 400 MHzo-2 和-3 FPGA 速度级器件: 533 MHzo只有-2 FPGA 速度等级的 CXT 设备只要303 MHz支持o低功耗V6设备只需303303 MHz∙频率超过333 MHz,只有数据宽度低于72位被容许。

频率低于333 MHz 数据宽度低于144 位被允许∙内存类型、内存部件和数据宽度被限制基于所选的 FPGA 器件、 FPGA 器件速度等级和设计频率BANK的选择规则:∙地址/控制组只能选择在内部列BANK∙第一个选定的地址/控制组将有 CK [0] 和 CK #[0] 引脚∙包含CK [0] 和 CK #[0]的BANK,会有该MMCM应用与该H-Row∙对于设计频率400 MHz或更高,只有内部列BANK被允许用于数据组的选择。

对于设计频率为400 MHz以下,内部和外部列BANK被允许数据组的选择o内部或外部列BANK被唯一的允许for选择∙位于,包含CK [0]和CK #[0] 的BANK的上面一行、下面一行和同一行,的内外侧BANK,是可用的for数据组引脚选择∙此限制被一个称为vicinity box的边界箱描述∙系统时钟组只能被选择在包含GC引脚的BANK或者位于,和分配的MMCM 同一H-ROW的内部BANK。

∙控制和状态引脚即sys_rst,error等,在系统时钟BANK中分配.∙由于采用不同的电压标准,系统时钟组与其余的设计组针脚(地址/控制组和数据组)不能共存于同一BANK。

∙一个主BANK必须被选择for每个列,假如系统时钟BANK不能作为主BANK引脚分配规则:∙地址/控制组:o包含 A、BA、 CK、 CK #、 CKE、 CS #、 RAS #、 CAS #、 WE#、 ODT, RESET #o只能选择内部列BANKo内存时钟信号(CK [0] 和 CK#[0]) 分配给差分对引脚(P Npair)o VRN/VRP 引脚若被用于引脚分配,DCI级联应该被采用,用以支持地址/时钟的 DCI 标准PS: XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚。

1.结构框图:2.管脚功能描述管脚符号类型描述A0-A9,A10/AP,A11,A12/BC#,A13 Input 地址输入。

为ACTIVATE命令提供行地址,和为READ/WRITE命令的列地址和自动预充电位(A10),以便从某个bank的内存阵列里选出一个位置。

A10在PRECHARGE命令期间被采样,以确定PRECHARGE是否应有于某个bank:A10为低,这个bank由BA[2:0]来选择,或者A10为高,对所有bank。

在LOADMODE命令期间,地址输入提供了一个操作码。

地址输入的参考是VREFCA。

A12/BC#:在模式寄存器(MR)使能的时候,A12在READ和WRITE命令期间被采样,以决定burst chop(on-the-fly)是否会被执行(HIGH=BL8执行burst chop),或者LOW-BC4不进行burst chop。

BA0,BA1,BA2 Input Bank地址输入。

定义ACTIVATE、READ、WRITE或PRECHARGE命令是对那一个bank操作的。

BA[2:0]定义在LOAD MODE命3.状态图:ACT = ACTIVATE PREA = PRECHARGE ALL SRX = 自刷新推出MPR = 多用处寄存器READ = RD,RDS4,RDS8 WRITE=WR,WRS4,WRS8MRS=模式寄存器集 READAP=RDAP,RDAPS4,RDAPS8 WRITE=WRAP,WRAPS4,WRAPS8PDE=掉电进入REF=REFRESH ZQCL=ZQ LONG CALIBRATIONPDX=掉电推出RESET=启动复位过程ZACS=ZA SHORT CALIBTATIONPRE=预充电SRE=自刷新进入4. 基本功能DDR3 SDRAM是高速动态随机存取存储器,内部配置有8个BANK。

DDR3 SDRAM使用8n预取结构,以获得高速操作。

DDR3电路是一种动态随机存取存储器(DRAM)的电路,它使用差分信号技术来实现数据的传输。

与DDR2相比,DDR3具有更高的数据传输速率和更低的功耗。

DDR3电路的基本组成包括存储单元、地址解码器、数据缓冲器、控制逻辑和时钟发生器。

存储单元用于存储数据,地址解码器用于解码地址信号,数据缓冲器用于缓冲读写数据,控制逻辑用于控制读写操作,而时钟发生器用于产生时钟信号。

在DDR3电路中,数据以时钟的上升沿或下降沿进行传输,使用差分信号技术可以有效地提高数据的传输速率。

DDR3电路的控制逻辑包括时序发生器、命令解码器和数据路径控制器。

时序发生器用于产生时序信号,命令解码器用于解码命令信号,数据路径控制器用于控制数据的传输路径。

DDR3电路的引脚包括地址引脚、数据引脚和控制引脚。

地址引脚用于输入地址信号,数据引脚用于输入输出数据,控制引脚用于输入控制信号。

在DDR3电路中,数据是以8位或16位的方式进行传输的,而地址是2的10次方,这意味着可以寻址2的10次方个存储单元。

DDR3电路的特点包括高速传输、低功耗、差分信号技术和时钟发生器等。

高速传输可以提供更高的数据传输速率,低功耗可以降低功耗和发热量,差分信号技术可以提高信号的抗干扰能力,而时钟发生器可以产生稳定的时钟信号。

总之,DDR3电路是一种高性能、低功耗的DRAM电路,适用于

各种计算机和电子设备中。