IC工艺课程设计 答辩题目

- 格式:doc

- 大小:31.50 KB

- 文档页数:3

单片机课程设计答辩单片机课程设计答辩参考参考参考题目题目答辩记录的第二部分要记录2、3个问题个问题。

在在A 类题类题中选一中选一中选一、、两题作答两题作答((所有带框的问题带框的问题只能选一题只能选一题只能选一题));在B 类题中根据自己课题选一类题中根据自己课题选一、、两题作答作答。

注意所选的问题不要太相近注意所选的问题不要太相近,,同一同一个个问题问题在一个在一个在一个班内不要班内不要班内不要重复重复重复选选。

一、 A 类题类题((通用通用题题) 1、 课题设计中你使用了哪些软件,这些软件各自的主要作用是什么?2、 说说Keil 软件的主要功能和作用。

3、 Proteus 软件的主要功能是什么?4、 你所使用的Keil 软件是哪个版本的?如果要编译时生成hex 文件,应该如何设置?5、 在keil 中对C 语言源程序调试时,若要启动调试时直接进入到main 函数,要如何设置?6、 课题中你是用C 语言编程的,使用C 语言编程有什么好处,说说你的看法。

7、 课题中你是用MCS51单片机的汇编语言编程的,使用汇编语言编程有何特点,说说你的看法。

8、 51单片机的C 语言(C51)与标准ANSI C 有何不同,简单谈谈你的体会?9、 51单片机C 语言编程,XBYTE 关键字有什么作用?试举例说明。

10、 C51语言中,如何来定义一个中断服务子程序?11、 C51语言中,中断服务子程序是如何与各自的中断类型对应的(如外部中断0)?试举例说明。

12、 能实现电子电路仿真的软件有很多,如Multisim 、PSPICE 、OrCAD 、EWB 等,Proteus 相对这些软件来说有什么特点?13、 Proteus 仿真软件中,要使用一个+9V 的POWER 电源,要在从哪个工具箱(绘图工具栏)中选取哪个部件,要如何设置成+9V ?14、 Proteus 仿真软件中,如果要使用一个多通道示波器,该从哪个工具箱(绘图工具栏)中选取哪个部件?15、 Proteus 软件中,从元器件库中调出的元件有的不能仿真,为什么?16、 Proteus 仿真时,如何指定单片机所用的程序代码?说说操作方法。

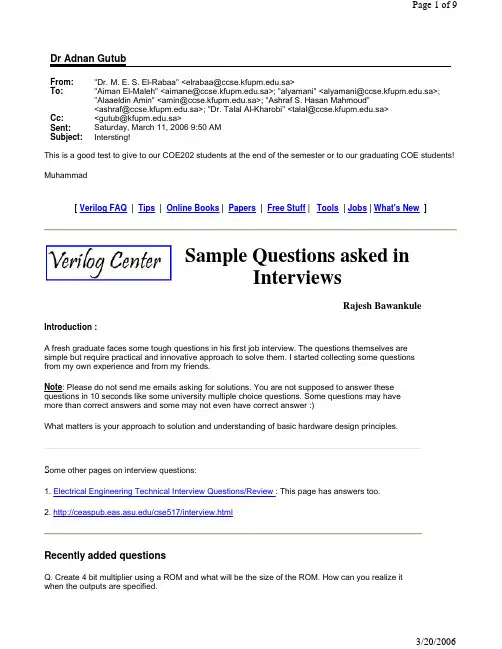

Dr Adnan GutubFrom:"Dr. M. E. S. El-Rabaa" <elrabaa@.sa>To:"Aiman El-Maleh" <aimane@.sa>; "alyamani" <alyamani@.sa>;"Alaaeldin Amin" <amin@.sa>; "Ashraf S. Hasan Mahmoud"<ashraf@.sa>; "Dr. Talal Al-Kharobi" <talal@.sa>Cc:<gutub@.sa>Sent:Saturday, March 11, 2006 9:50 AMSubject:Intersting!This is a good test to give to our COE202 students at the end of the semester or to our graduating COE students! Muhammad[ Verilog FAQ | Tips | Online Books | Papers | Free Stuff | Tools | Jobs | What's New ]Sample Questions asked inInterviewsRajesh Bawankule Introduction :A fresh graduate faces some tough questions in his first job interview. The questions themselves aresimple but require practical and innovative approach to solve them. I started collecting some questionsfrom my own experience and from my friends.Note: Please do not send me emails asking for solutions. You are not supposed to answer thesequestions in 10 seconds like some university multiple choice questions. Some questions may havemore than correct answers and some may not even have correct answer :)What matters is your approach to solution and understanding of basic hardware design principles.S ome other pages on interview questions:1. Electrical Engineering Technical Interview Questions/Review : This page has answers too.2. /cse517/interview.htmlRecently added questionsQ. Create 4 bit multiplier using a ROM and what will be the size of the ROM. How can you realize itwhen the outputs are specified.Q. How can you swap 2 integers a and b, without using a 3rd variableQ. Which one is preferred? 1's complement or 2's complement and why?Q. Which one is preferred in FSM design? Mealy or Moore? Why?Q. Which one is preferred in design entry? RTL coding or Schematic? Why?Q. Design a 2 input OR gate using a 2:1 mux.Q. Design a 2 input AND gate using a 2 input XOR gate.Old QuestionsQ. Design a logic which mimics a infinite width register. It takes input serially 1 bit at a time. Output is asserted high when this register holds a value which is divisible by 5.For example:Input Sequence Value Output11100102011015101010101110101210(Hint: Use a FSM to create this)Q. Design a block which has 3 inputs as followed.1. system clock of pretty high freq2. asynch clock input P3. asynch clock input QP and Q clocks have 50% duty cycle each. Their frequencies are close enough and theyhave phase difference. Design the block to generate these outputs.1. PeqQ : goes high if periods of P and Q are same2. PleQ : goes high if P's period is less than that of Q.3. PgrQ : goes high if P's period is greater than that of Q.Q. What's the difference between a latch and a flip-flop? Write Verilog RTL code for each. (This is one of the most common questions but still some EE's don't know how to explain it correctly!)Q. Design a black box whose input clock and output relationship as shown in diagram.__ __ __ __ __ __ __ __ __clk __| |__| |__| |__| |__| |__| |__| |__| |__| |____ __ __ __ __Output __| |________| |________| |________| |________| |__Q. Design a digital circuit to delay the negative edge of the inputsignal by 2 clock cycles.______________________input ________| |______________ _ _ _ _ _ _ _ _ _ _ _ _clock _| |_| |_| |_| |_| |_| |_| |_| |_| |_| |_| |_| |_| |____________________________output _________| |___________Q. Design a Pattern matching block- Output is asserted if pattern "101" is detected in last 4 inputs.- How will you modify this design if it is required to detect same "101" pattern anywhere in last8 samples?Questions:Q.The digital circuit is shown with logic delay (dly3) and two clock buffer delays (dly1, dly2). - How will you fix setup timing violations occurring at pin B?- How will you fix hold violations occurring at pin B?(Hint: Change the values of three delays to get desired effect)Q.Sender sends data at the rate of 80 words / 100 clocksReceiver can consume at the rate of 8 words / 10 clocksCalculate the depth of FIFO so that no data is dropped.Assumptions: There is no feedback or handshake mechanism. Occurrence of data in that time period is guaranteed but exact place in those clock cycles is indeterminate.QOptical sensors A and B are positioned at 90 degrees to each other as shown in Figure. Half od the disc is white and remaining is black. When black portion is under sensor it generates logic 0 and logic 1 when white portion is under sensor.Design Direction finder block using digital components (flip flops and gates) to indicate speed. Logic 0 for clockwise and Logic 1 for counter clockwise.QWill this design work satisfactorily?Assumptions: thold = tsetup = tclock_out = tclock_skew = 1ns.After reset A = 0, B = 1Q. Design a 4:1 mux in Verilog.z Multiple styles of coding. e.g.Using if-else statementsif(sel_1 == 0 && sel_0 == 0) output = I0;else if(sel_1 == 0 && sel_0 == 1) output = I1;else if(sel_1 == 1 && sel_0 == 0) output = I2;else if(sel_1 == 1 && sel_0 == 1) output = I3;Using case statementcase ({sel_1, sel_0})00 : output = I0;01 : output = I1;10 : output = I2;11 : output = I3;default : output = I0;endcasez What are the advantages / disadvantages of each coding style shown above?z How Synthesis tool will give result for above codes?z What happens if default statement is removed in case statement?z What happens if combination 11 and default statement is removed? (Hint Latch inference) (Comments : Though this questions looks simple and out of text books, the answers tosupporting questions can come only after some experience / experimentation.)Q. Design a FSM (Finite State Machine) to detect a sequence 10110.z Have a good approach to solve the design problem.z Know the difference between Mealy, Moore, 1-Hot type of state encoding.z Each state should have output transitions for all combinations of inputs.z All states make transition to appropriate states and not to default if sequence is broken. e.g. S3 makes transition to S2 in example shown.z Take help of FSM block diagram to write Verilog code.Q. One more sequence detector:Design a FSM (Finite State Machine) to detect more than one "1"s in last 3 samples.For example: If the input sampled at clock edges is 0 1 0 1 0 1 1 0 0 1then output should be 0 0 0 1 0 1 1 1 0 0 as shown in timing diagram. And yes, you have to design this FSM using not more than 4 states!!Q. Design a state machine to divide the clock by 3/2.(Hint: 2 FSMs working on posedge and negedge)Q. Draw timing diagrams for following circuit.z What is the maximum frequency at which this circuit can operate?z What is the minimum width of input pulse and position?z Problem can be given interesting twist by specifying all delays in min and max types.Q. Design a Digital Peak Detector in Verilog.Q. Design a RZ (return to zero )circuit. Design a clock to pulse circuit in Verilog / hardware gates.Q. Miscellaneous Basic Verilog Questions:z What is the difference between Behavior modeling and RTL modeling?z What is the benefit of using Behavior modeling style over RTL modeling?z What is the difference between blocking assignments and non-blocking assignments ?z How do you implement the bi-directional ports in Verilog HDLz How to model inertial and transport delay using Verilog?z How to synchronize control signals and data between two different clock domains?[ Verilog FAQ | Tips | Online Books | Papers | Free Stuff | Tools | Jobs | What's New ]Copyright Rajesh Bawankule 1997-2005。

电子课程设计答辩问题一、教学目标本课程的教学目标是使学生掌握电子课程的基本知识和技能,能够运用所学知识进行电子设计与实践。

具体目标如下:1.知识目标:学生能够理解电子元器件的基本原理和特性,掌握电子电路的设计方法,了解电子工程领域的最新发展。

2.技能目标:学生能够熟练使用电子工具和设备,进行电子电路的搭建和调试,具备一定的电子项目设计与实施能力。

3.情感态度价值观目标:学生能够认识到电子技术在现代社会中的重要性,培养对电子工程的兴趣和热情,树立正确的科学态度和创新精神。

二、教学内容本课程的教学内容主要包括电子元器件、电子电路设计、电子项目实践等。

具体安排如下:1.电子元器件:介绍电子元器件的基本原理和特性,包括电阻、电容、电感、二极管、晶体管等。

2.电子电路设计:讲解电子电路的设计方法,包括放大电路、滤波电路、稳压电路等。

3.电子项目实践:安排一定的实践项目,让学生动手搭建和调试电子电路,提高实际操作能力。

三、教学方法为了实现教学目标,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法、实验法等。

具体运用如下:1.讲授法:用于讲解电子元器件的基本原理和特性,以及电子电路的设计方法。

2.讨论法:引导学生对电子工程领域的最新发展进行讨论,培养学生的思考能力和团队协作精神。

3.案例分析法:通过分析具体的电子项目案例,让学生学会将理论知识应用于实际问题中。

4.实验法:安排实践项目,让学生动手操作,提高实际操作能力和创新能力。

四、教学资源为了支持教学内容和教学方法的实施,本课程将准备以下教学资源:1.教材:选用权威、实用的电子教材,为学生提供系统、科学的学习资料。

2.参考书:提供相关的电子技术参考书籍,丰富学生的知识储备。

3.多媒体资料:制作精美的电子课件和教学视频,提高课堂教学效果。

4.实验设备:准备充足的实验设备,确保每个学生都能动手实践,提高实际操作能力。

五、教学评估为了全面、客观地评估学生的学习成果,本课程将采用多种评估方式,包括平时表现、作业、考试等。

工艺过程课程设计问题答辩一、课程目标知识目标:1. 让学生掌握工艺过程的基本概念,理解其在实际生产中的应用。

2. 使学生了解不同类型的工艺流程及其特点,能分析工艺过程中的关键环节。

3. 帮助学生了解工艺参数对产品质量的影响,能运用相关知识优化工艺过程。

技能目标:1. 培养学生运用工艺流程图表达实际生产过程的能力。

2. 提高学生分析工艺问题、提出改进措施的能力。

3. 培养学生团队合作和沟通表达的能力。

情感态度价值观目标:1. 培养学生热爱科学、积极探索工艺知识的兴趣。

2. 增强学生的环保意识,使其关注工艺过程对环境的影响。

3. 培养学生严谨认真、勇于创新的精神,提高对工艺过程的敬畏之心。

课程性质:本课程为实践性较强的学科课程,旨在帮助学生将理论知识与实际生产相结合。

学生特点:学生处于八年级阶段,已具备一定的物理、化学知识基础,好奇心强,善于合作与探究。

教学要求:结合学生特点和课程性质,注重理论与实践相结合,充分调动学生的积极性,提高学生的实践操作能力和问题解决能力。

在教学过程中,注重目标的分解和落实,确保学生能够达到预期学习成果。

二、教学内容本章节教学内容主要包括以下几部分:1. 工艺过程基本概念:介绍工艺过程的定义、分类及其在实际生产中的应用。

教材章节:第一章第一节2. 工艺流程图的绘制:讲解工艺流程图的组成、绘制方法和注意事项。

教材章节:第一章第二节3. 常见工艺流程及其特点:分析不同类型的工艺流程,如化工、机械、电子等行业的工艺流程。

教材章节:第二章4. 工艺参数对产品质量的影响:探讨温度、压力、速度等工艺参数对产品质量的作用。

教材章节:第三章5. 工艺过程优化:介绍工艺过程优化的方法、步骤和案例。

教材章节:第四章6. 实践操作:组织学生进行工艺过程实践操作,巩固理论知识。

教材章节:第五章教学内容安排与进度:第一周:工艺过程基本概念第二周:工艺流程图的绘制第三周:常见工艺流程及其特点第四周:工艺参数对产品质量的影响第五周:工艺过程优化第六周:实践操作与总结教学内容注重科学性和系统性,结合教材章节和教学目标,确保学生能够掌握工艺过程的相关知识,提高实践操作能力。

ic工艺期末试题及答案一、选择题1. IC工艺是指()。

A. 集成电路的制造工艺B. 美术设计工艺C. 电子工艺制作D. 橡胶制品生产工艺2. IC工艺的主要流程包括以下几个步骤,下列选项中排序正确的是()。

A. 掩膜制作→晶圆清洗→光刻→扩散→化学机械抛光B. 晶圆清洗→光刻→扩散→掩膜制作→化学机械抛光C. 光刻→掩膜制作→晶圆清洗→化学机械抛光→扩散D. 扩散→化学机械抛光→晶圆清洗→掩膜制作→光刻3. IC工艺中的光刻步骤是用来()。

A. 添加金属雾化层B. 制作电子线路图案C. 清洗晶圆表面D. 进行化学机械抛光4. IC工艺中的扩散步骤是指()。

A. 将杂质掺入硅晶圆表面B. 制作遮光层C. 制作掩膜D. 使用化学溶液清洗表面5. IC工艺中,化学机械抛光是用来()。

A. 修饰晶圆表面形态B. 制作掩膜C. 添加杂质D. 清洗晶圆表面二、简答题1. 请简要介绍IC工艺的主要流程。

IC工艺的主要流程包括:晶圆清洗、掩膜制作、光刻、扩散和化学机械抛光。

晶圆清洗是为了清除晶圆表面的灰尘、污渍和其他杂质,以保证后续步骤的顺利进行。

掩膜制作是为了制作电子线路的图案。

通过使用光刻机和光刻胶,将图案转移到掩膜上。

光刻是将掩膜上的图案转移到晶圆表面,利用紫外光照射和化学反应将光刻胶固定在晶圆上,并形成线路的图案。

扩散是将杂质掺入硅晶圆表面,以改变硅晶圆的电导率,形成电子元件的结构。

化学机械抛光是用化学药液和机械研磨的方式,修饰晶圆表面的形态。

它可以去除晶圆表面的凹凸不平,以及掩膜制作和光刻步骤中产生的污渍和残留物。

2. IC工艺对电子器件的制造有何重要作用?IC工艺对电子器件的制造具有重要作用,主要体现在以下几个方面:首先,IC工艺可以使电子器件的元件尺寸更小。

随着科技的不断进步,人们对电子器件的要求越来越高。

IC工艺的发展使得芯片上可容纳的元件数量更多,尺寸更小,功耗也更低,性能更优越。

其次,IC工艺可以提高电子器件的可靠性和稳定性。

单片机毕业设计答辩问题一、选题背景及意义单片机是一种微型计算机,具有体积小、功耗低、成本低等优点,在现代电子技术中应用广泛。

因此,单片机毕业设计已成为电子信息工程专业的重要课程之一。

本文将从选题背景及意义、设计思路与方法、实现过程与结果、存在问题与改进方向等方面详细介绍单片机毕业设计答辩问题。

二、设计思路与方法1.选题思路本文选取了“基于单片机的智能家居控制系统”作为毕业设计的选题。

该选题基于当前社会对智能家居的需求,结合单片机技术实现智能家居设备的控制,具有实用性和创新性。

2.设计方法本文采用了硬件和软件相结合的方法进行系统设计。

硬件方面主要包括单片机芯片、传感器模块、继电器模块等;软件方面主要包括编写程序控制单片机芯片和传感器模块之间的通信,实现智能家居设备的控制。

三、实现过程与结果1.硬件部分硬件部分主要包括以下几个模块:(1)单片机芯片模块本文采用AT89S52单片机芯片,该芯片具有高速、低功耗、易于编程等优点。

(2)传感器模块本文采用温度传感器和光敏传感器,通过检测环境温度和光照强度来控制智能家居设备的开关。

(3)继电器模块本文采用继电器模块来控制智能家居设备的开关,通过单片机控制继电器的通断实现设备的开关。

2.软件部分软件部分主要包括以下几个方面:(1)编写程序本文采用Keil C51编写程序,通过串口通信实现单片机与传感器之间的数据交互,实现智能家居设备的控制。

(2)调试程序在编写程序后,需要进行调试。

本文采用仿真器对程序进行调试,确保程序能够正常运行。

3.结果展示经过系统测试,本设计成功实现了智能家居设备的控制。

当环境温度超过一定范围时自动打开空调或风扇;当光照强度不足时自动打开灯具等。

四、存在问题与改进方向1.存在问题(1)系统响应速度较慢,需要进一步优化程序。

(2)系统可靠性有待提高,需要增加故障检测和排除机制。

2.改进方向(1)优化程序,提高系统响应速度。

(2)增加故障检测和排除机制,提高系统可靠性。

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路Latc h up是指cmo s晶片中,在电源p owerVDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路,它的存在会使VDD和GND之间产生大电流随着IC制造工艺的发展, 封装密度和集成度越来越高,产生L atchup的可能性会越来越大La tch u p 产生的过度电流量可能会使芯片产生永久性的破坏, Latc h up的防范是I C Lay out 的最重要措施之一Q1为一垂直式PNPBJT,基极(ba se)是n well,基极到集电极(co llect or)的增益可达数百倍;Q2是一侧面式的NPN B JT,基极为P su bstra te,到集电极的增益可达数十倍;Rwel l是nwe ll的寄生电阻;Rs ub是su bstra te电阻。

以上四元件构成可控硅(SC R)电路,当无外界干扰未引起触发时,两个BJT 处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时La tch u p不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJ T,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,La tch u p由此而产生。

产生Latc h up的具体原因芯片一开始工作时VDD变化导致n well和P sub strat e间寄生电容中产生足够的电流,当VDD变化率大到一定地步,将会引起La tch u p。

当I/O的信号变化超出VDD-GND(V SS)的范围时,有大电流在芯片中产生,也会导致SC R的触发。

单片机课程设计答辩题目1.叙述单片机实现交通灯控制应用系统的开发过程设计电路图→制作电路板→程序设计→硬软件联调→程序下载→产品测试2.阐述keil软件的C51程序调试过程启动软件→建立工程文件→建立并添加源文件→配置工程属性→程序调试3.如何将综合仿真仪、微型计算机和交通灯板连接起来串口、USB4.叙述单片机应用系统软件的编制与调试过程同25.软件定时与硬件定时的优缺点和区别占用CPU时间6.交通灯系统中使黄灯闪烁的原理循环、延时7.如何使LED灯点亮和熄灭,说明电路的原理发光二极管正极接+5V,低电平有效,P1口赋值8.如何实现紧急情况时,两个方向的交通灯全为红灯外部中断0中断函数,保护现场、暂存→两个方向都是红灯→延时→恢复中断前9.叙述交通灯板的连接和结构原理电源、复位、晶振、中断、LED灯、数码管10.MCS-51程序存储器和数据存储器是如何配置的AT89S52:8KB Flash、256B RAM11.MCS-51的4个并行口各自的作用,课程设计用的哪个并行口LED灯用P1口,数码管用P0口12.MCS-51单片机有几个定时计数器,说明定时与计数的区别T0、T1,内部时钟计数、外部脉冲计数13.C51中断程序的编写方法外部中断014.MCS-51有几个中断源,说出他们的中断服务程序的入口地址外部中断0 0003H定时/计数器 000BH外部中断1 0013H定时/计数器1 001BH串行口 0023H15.改变交通灯的通行时间软件如何编写16.软件定时与硬件定时的优缺点和区别同517.单片机软件编程中,循环程序如何编写for(k=0;k<i;k++)18.说明XLISP写入程序的步骤擦除→串口、芯片检测→打开.hex文件→智能一键通(素材和资料部分来自网络,供参考。

可复制、编制,期待您的好评与关注)。

芯片的制造过程可概分为晶圆处理工序(Wafer Fabrication)、晶圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial Test and Final Test)等几个步骤。

其中晶圆处理工序和晶圆针测工序为前段(Front End)工序,而构装工序、测试工序为后段(Back End)工序。

1、晶圆处理工序:本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2、晶圆针测工序:经过上道工序后,晶圆上就形成了一个个的小格,即晶粒,一般情况下,为便于测试,提高效率,同一片晶圆上制作同一品种、规格的产品;但也可根据需要制作几种不同品种、规格的产品。

在用针测(Probe)仪对每个晶粒检测其电气特性,并将不合格的晶粒标上记号后,将晶圆切开,分割成一颗颗单独的晶粒,再按其电气特性分类,装入不同的托盘中,不合格的晶粒则舍弃。

3、构装工序:就是将单个的晶粒固定在塑胶或陶瓷制的芯片基座上,并把晶粒上蚀刻出的一些引接线端与基座底部伸出的插脚连接,以作为与外界电路板连接之用,最后盖上塑胶盖板,用胶水封死。

其目的是用以保护晶粒避免受到机械刮伤或高温破坏。

到此才算制成了一块集成电路芯片(即我们在电脑里可以看到的那些黑色或褐色,两边或四边带有许多插脚或引线的矩形小块)。

4、测试工序:芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。

经测试后的芯片,依其电气特性划分为不同等级。

而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。

IC设计基础(流程、工艺、版图、器件)笔试集锦1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA 等的概念)。

(仕兰微面试题目)什么是MCU?MCU(Micro Controller Unit),又称单片微型计算机(Single Chip Microcomputer),简称单片机,是指随着大规模集成电路的出现及其发展,将计算机的CPU、RAM、ROM、定时数器和多种I/O接口集成在一片芯片上,形芯片级的计算机。

DSP有两个意思,既可以指数字信号处理这门理论,此时它是Digital Signal Processing的缩写;也可以是Digital Signal Processor的缩写,表示数字信号处理器,有时也缩写为DSPs,以示与理论的区别。

2、FPGA和ASIC的概念,他们的区别。

答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点3、什么叫做OTP片、掩膜片,两者的区别何在?otp是一次可编程(one time programme),掩膜就是mcu出厂的时候程序已经固化到里面去了,不能在写程序进去!4、你知道的集成电路设计的表达方式有哪几种?模拟电路的电路图表达,逻辑电路的功能行为级表达,RTL和门级硬件描述语言表达5、描述你对集成电路设计流程的认识。

芯片硬件设计和软件协同设计。

芯片硬件设计包括:1.功能设计阶段。

2.设计描述和行为级验证3.逻辑综合4.门级验证(Gate-Level Netlist Verification)5.布局和布线6、简述FPGA等可编程逻辑器件设计流程。

IC 工艺课程设计答辩题目汇总

1、回答TTL电路制造流程,其中第二次氧化做什么用途?说出本次氧化你采用什么方法?

工艺参数是什么?画出紧接着的光刻掩膜板图形、和对应的光刻刻蚀后的剖面图。

2、回答平面三极管制造流程,其中第二次氧化做什么用途?说出本次氧化你采用什么方

法?工艺参数是什么?画出紧接着的光刻掩膜板图形、和对应的光刻刻蚀后的剖面图。

3、回答TTL电路制造流程,在你的流程中,其中氮化硅层做什么用途?说出制作氮化硅层

你采用什么方法?工艺参数是什么?质检参数是什么?画出发射区掺杂之前的剖面图。

4、回答平面三极管制造流程,其中第二次掺杂做什么用途?掺什么杂质?说出本次掺杂你

采用什么方法?工艺参数是什么?质检参数是什么?画出本次掺杂完成后的剖面图。

5、回答TTL电路制造流程,在你的流程中,其中第一次掺杂做什么用途?掺什么杂质?说

出本次掺杂你采用什么方法?工艺参数是什么?质检参数是什么?画出发射区掺杂完成后的剖面图。

6、回答TTL电路制造流程,其中制作氮化硅层之前的氧化膜做什么用途?说出制作该氧化

膜你采用什么方法?工艺参数是什么?要检验那些参数?画出基区掺杂之前的剖面图。

7、回答平面三极管制造流程,其中第一次掺杂做什么用途?掺什么杂质?说出本次掺杂你

采用什么方法?流程单中这一流程是如何设计的?画出本次掺杂完成后的剖面图。

8、回答TTL电路制造流程,其中制作金属膜之前的氧化做什么用途?说出本次氧化你采用

什么方法?质检参数是什么?画出隔离掺杂之前的光刻掩膜板图形和对应光刻刻蚀完成后的TTL剖面图。

9、回答TTL电路制造流程,其中第二次掺杂做什么用途?掺什么杂质?说出本次掺杂你采

用什么方法?工艺参数是什么?质检参数是什么?画出本次掺杂完成后的TTL剖面图。

10、回答TTL电路制造流程,其中第二次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,曝光后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

11、回答TTL电路制造流程,其中第三次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,显影后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

12、回答TTL电路制造流程,其中第四次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,旋转涂胶的工艺参数是什么?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

13、回答平面三极管制造流程,其中制作正面金属层用什么方法?流程单中这一流程是

如何设计的?画出正面金属层完成后的剖面图。

14、回答TTL电路制造流程,其中制作背面金属层用什么方法?工艺参数是什么?要

检查哪些参数?画出基区掺杂之前的光刻的掩膜板图、和对应刻蚀后的剖面图。

15、回答平面三极管制造流程,其中第二次氧化做什么用途?说出本次氧化你采用什么

方法?工艺参数是什么?画出紧接着的光刻掩膜板图形、和对应的光刻刻蚀后的TTL 电路剖面图。

16、回答TTL电路制造流程,其中第三次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,显影后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

17、回答平面三极管制作流程,其中第二次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,旋转涂胶的工艺参数是什么?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

18、回答TTL电路制造流程,其中制作正面金属层用什么方法?工艺参数是什么?要

检查哪些参数?画出发射区掺杂之前的光刻的掩膜板图、和对应刻蚀后的剖面图。

19、回答平面三极管制作流程,其中第三次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,显影后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

20、回答TTL电路制造流程,其中第一次光刻和刻蚀的目的是什么?显影的工艺参数

有哪些?刻蚀后要检测那些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。