一种高速数据采集卡的设计与实现.

- 格式:doc

- 大小:25.00 KB

- 文档页数:2

西北工业大学研究生创意创新种子基金作品说明书作品名称:基于FPGA的新型高速PCI采集卡的设计基于FPGA的新型高速PCI采集卡的设计摘要:从自主研发的角度,本设计通过板载FPGA实现了对16路模拟信号的采集及滤波处理,并将最终结果送入工控机。

其中关键技术是通过对FPGA编程开辟控制空间并实现具体滤波算法,上位机通过设置对应的控制空间实现对于16路AD采集通道的开启及不同滤波算法的调用。

采用PLX9052实现PCI的接口设计。

根据上述要求选用ALTERA公司的EP2C8Q208型号的FPGA。

关键词:采集卡,PCI,FPGA,滤波算法0、前言在现代工业领域,随着控制系统日益大型化,复杂的系统会给有用信号叠加许多高频噪声干扰。

如何滤除这些干扰,成为业内普遍关注的问题。

目前普遍使用的处理方式分为两种,利用硬件电路滤波和通过上位机软件滤波,但这两种方式均存在很多缺陷:(1) 通过硬件电路滤波,不仅会大大增加成本、占用宝贵的PCB面积,而且滤波效果不彻底,还会造成有用信号的相位偏移。

(2) 通过上位机软件滤波,要求具有很高的信号采集速度,一方面造成了数据传输量大的负担,另一方面在上位机执行滤波算法会占用控制资源,从而大大降低了控制效率。

为了解决以上问题,本作品设计了一种基于FPGA的新型高速PCI采集卡,通过FPGA对模拟信号进行高速的过采样,并针对信号类型进行算法可选的滤波处理,同时配合上位机的控制频率设计抽取算法,通过双端口RAM将数据通过PCI总线传至上位机。

这样既在下位机完成了滤波,又保证了信号传输速度,降低了数据传输量,从而大大减少上位机的运算量,提高控制程序的执行效率。

1、采集卡参数:1.1 AD采集:单通道采集频率可达1MSPS,可实现最多16通道的循环采集,循环采集频可达990KSPS。

采集范围为-10V~10V,采集精度实测可达到0.5‰。

AD采集内嵌滤波参数可选的8阶FIR滤波算法,截止频率在1~250KHZ之间可调,并可由软件测试界面进行设置。

基于CPLD的高速数据采集系统的设计与实现摘要:高速数据采集系统在信息科学的各个领域中应用越来越广泛,而基于单片机、ARM的数据采集技术已经很成熟,在对速度要求越来越苛刻的当代社会,这些技术已经显得有些力不从心,我们必须开发新的更高速的数据采集系统才能跟上信息产业发展的脚步,而随着可编程逻辑器件这些年来的迅猛发展,它以其极高的集成度,稳定的性能以及高速、易用的特点,在信息科学的各个领域都得到了广泛的应用,本文提出了一种基于CPLD的高速数据采集系统的设计方法。

关键词:基于CPLD;高速数据;采集系统;设计与实现1、前言数据采集技术是数字系统的重要部分,它与传感器技术、信号处理技术、计算机技术一起构成了现代检测技术的基础。

目前数据采集系统已经被广泛的应用。

在很多实际应用中,传统的采集系统已经不能满足采集要求,需要采样速度很高的甚至是超高采集系统。

本文提出了一种基于CPLD的高速数据采集系统的设计方法。

通过CPLD控制数据连续采集、缓冲,然后通过MCU(C8051F430)读取缓存在SRAM中数据,并且通过USB2.0将缓冲区数据转移到硬盘管理卡,由硬盘管理卡将数据存入海量硬盘。

再利用PC机的强大数据处理功能,MicrosoftVisualC++6.0的MFC类库,设计出一套集数据采集、处理和分析的高速数据采集的可视化系统。

2、系统结构设计本文设计的高速数据采集系统主要由数据采集、数据显示处理和数据传输接口三部分组成。

数据采集系统要解决的问题主要是数据的采集和传输问题。

为了增强设计的灵活性和可扩展性,系统采用CPLD来实现对AD转换器、数据缓存器SRAM、时钟、数据传输的控制逻辑。

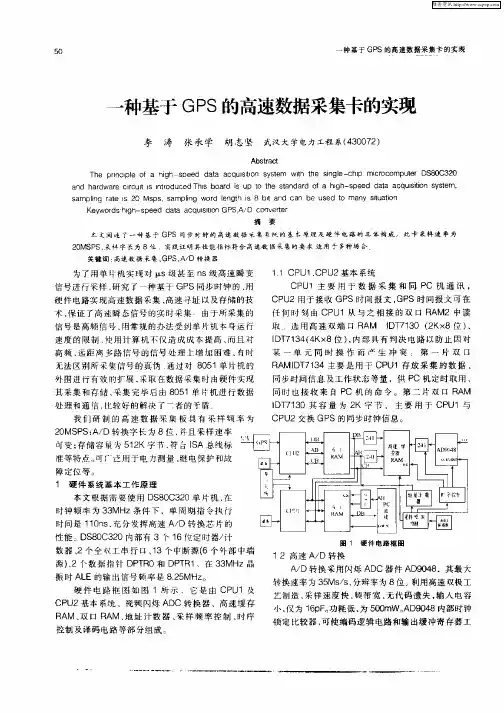

系统功能框图如图1。

图1如上图所示,数据采集方案采用的是:带USB2.0控制器的高速单片机+USB传输的方式,目前有一款非常好的自带USB2.0控制器,并且具有51内核的高效率单片机C8051F340,这款单片机的执行速度可达到25MHz,且不用分频,故选用它可高速传输数据到PC机的同时,还可以对RAM进行读取控制。

高速数据采集卡的设计

孙冀伟;祁载康;沈吉;张伟

【期刊名称】《数据采集与处理》

【年(卷),期】2003(018)003

【摘要】为了满足对雷达信号高速采集的要求,设计了一个基于16位ISA总线的30MSPS的双通道数据采集卡.该采集卡的最大特点是可以由程序设定每次同步触发后的采样延迟时间和采样的点数.本文对A/D转换及其接口电路,D/A转换电路存储器接口电路及延迟采样控制电路进行了详细论述.

【总页数】4页(P323-326)

【作者】孙冀伟;祁载康;沈吉;张伟

【作者单位】北京理工大学机电工程学院,北京,100081;北京理工大学机电工程学院,北京,100081;北京理工大学机电工程学院,北京,100081;北京理工大学机电工程学院,北京,100081

【正文语种】中文

【中图分类】TP703.3

【相关文献】

1.基于PCIe总线的高速数据采集卡设计与实现 [J], 李木国;黄影;刘于之

2.基于高速数据采集卡的输电线路故障定位系统设计 [J], 张运周

3.高速数据采集卡DDR控制器的设计与实现 [J], 王晓娇;张治中

4.PCI-e高速数据采集卡的驱动与上位机软件设计 [J], 孙文硕;赛景波

5.双通道5 GS/s高速数据采集卡设计 [J], 刘鸣;孙秀男;梁昊

因版权原因,仅展示原文概要,查看原文内容请购买。

高精度数据采集系统的设计及性能分析现代工业生产过程中往往需要涉及大量的监测和控制,而高精度数据采集系统的设计和性能分析就是为了满足这种需求而诞生的。

本文将介绍高精度数据采集系统的设计和性能分析的相关技术及应用,同时分析这些技术的应用场景和性能优劣,希望能够对读者有所帮助。

一、高精度数据采集系统的组成高精度数据采集系统是由多个部件组成的复杂系统,其中主要包括传感器、信号调理器、数据采集卡、数据处理软件等。

下面详细介绍这些部件的作用及原理:1. 传感器传感器是高精度数据采集系统中最核心的组成部分之一。

它的作用是将测量对象的物理量转换为电信号输出,常见的传感器包括温度传感器、压力传感器、角度传感器、力传感器等。

不同类型的传感器在测量的物理量和范围上存在差异,同时也有不同的转换方式和输出形式。

2. 信号调理器信号调理器是传感器信号处理的核心,主要负责将传感器输出的信号进行放大、滤波、线性化等处理,使其适合于数据采集卡进行数字化转换。

信号调理器的设计将直接影响系统的稳定性和精度。

3. 数据采集卡数据采集卡是高精度数据采集系统中另一个重要的组成部分,它起到将模拟信号转换成数字信号的作用。

数据采集卡的数字化转换精度和采样率将直接影响采集系统的精度。

4. 数据处理软件数据处理软件是高精度数据采集系统中最后一道关键工序的组成部分。

它的作用是将数据从数据采集卡中读取,并将其经过校准、滤波、标定、控制等算法处理,最终输出给用户需要的数据。

数据处理软件应当具有友好的用户界面、高效的运算能力和稳定的运行性能。

二、高精度数据采集系统的应用场景高精度数据采集系统的应用场景十分广泛,主要包括以下几个领域:1. 工业控制众所周知,现代工厂生产过程需要各种各样的传感器和数据采集设备,以保证产品质量和生产效率。

高精度数据采集系统可以应用于无污染的检测、高速电机控制、发电温度观测、高分辨率精细控制等技术领域。

2. 航空雷达航空雷达数据采集系统需要在高速行动的飞机上进行复杂的数据采集和传输,并要求精度高、稳定性好、机动性强、重量轻等特点。

基于PXI总线的高速数据采集系统的设计与实现摘要:为了满足城市轨道交通cbtc车载测控系统对数据采集的需要,使用阿尔泰公司的数据采集卡pxi8002搭建出系统的硬件平台。

软件方面在vc++环境下,利用多线程技术设计实现了基于pxi总线的多通道高速数据采集系统。

详细介绍整个系统的设计思路,对其中使用到的关键技术进行了研究,实验证明该系统具有较高的可靠性。

关键词:高速数据采集半满查询多线程 vc++中图分类号:tp274.2 文献标识码:a 文章编号:1007-3973(2013)001-082-031引言信息社会的发展,很大程度上取决于信息与信号处理技术的先进性。

数字信号处理技术的出现改变了信息与信号处理技术的整个面貌,而数据采集作为数字信号处理的必不可少的前期工作在整个数字系统中起到关键性、乃至决定性的作用,其应用已经深入到信号处理的各个领域中。

在这种情况下,高速度、高精度数据采集卡的出现,极大的简化了数据采集系统的硬件设计在数据采集系统中的应用越来越广泛。

在城市轨道交通cbtc仿真测试系统中需要采集的物理量有速度、加速度、牵引力电流等多个参数,如何实现实时连续,长时间的数据采集,并在采集的同时对采集到的数据进行及时处理、存储并动态显示,而windows并不是实时操作系统,在windows环境下开发实时测控系统需要采用一些技术。

本文主要利用阿尔泰公司的数据采集卡pxi2008搭建出系统的硬件,软件部分采用面向对象的软件设计思想,结合多线程技术和消息机制设计并实现的高速数据采集系统,完成了数据采集、数据分析处理、数据实时动态曲线显示等功能,并把该系统应用于地铁车载设备仿真测试系统中,实验证明该系统在可靠性和实时性方面具有良好的性能,能够满足系统要求。

2系统设计概述本文设计的数据采集处理系统包括前端的信号处理模块、实时数据采集模块、数据处理仿真模块。

其中信号处理模块的主要功能是对测试信号进行幅度变换、阻抗匹配等,把模拟信号调节到采集卡的量程范围内;实时数据采集模块则完成对输入模拟信号的采集和缓存,采集到的数据采用半满查询的方式通过系统总线直接读入计算机内存中自定义的缓冲区中,由相应的其他模块来完成后续处理工作;系统软件功能主要包括实时数据采集、数据处理、实时数据存储、显示模块以及车载系统仿真模型。

基于PCI总线的高速数据采集卡系统设计与实现裴喜龙(信息工程大学郑州450002)摘要:本文介绍一种基于PCI总线的高速数据采集卡系统的设计方法,讨论了设计高速数据采集系统的关键技术,给出了系统整体设计方案和PCI接口通信方式,完成了采集卡设备驱动程序及其应用程序的实现。

关键词:PCI总线数据采集卡设备驱动应用程序中图分类号:TP393.03。

Design and Implement of A High speed Data Acquisition Card Based on PCI BusPei Xilong(Information Engineering University, Zhengzhou 450002, China) Abstract: In this article, we introduce a method of how to design a high speed data acquisition card based on PCI bus, discuss pivotal technique about this system and the communication of the PCI interface, propose the whole design project and the develop the device driver and realize the app.Keywords: PCI BUS Data Acquisition Card Device Driver App1.引言数据采集技术是现代信号处理的基础,广泛应用于雷达、通信、遥测遥感等领域。

在数字信号处理工作中,实现对所需数据高速、实时、大批量采集具有重要意义。

随着信息科学的飞速发展,人们面临的信号处理任务愈来愈繁重,对数据采集系统的要求也愈来愈高。

利用PC机作为数据采集的平台,通过数据总线将采集的数据高速传输到PC机内存中,是实现采集系统数据存储的有效手段。

一种高精度中频信号数据采集卡的硬件设计一种高精度中频信号数据采集卡的硬件设计0引言传统数据采集数据采集卡的主要功能是完成对模拟信号的基带数字化。

由于数字化是在基带进行,其下变频、滤波全部采用模拟方式,因此,对于不同频段、不同调制方式的通信系统,应当对应专门的硬件结构,但这样的系统缺乏灵活性,且随着系统采样率和采样精度的提高,对数据实时性传输也带来了很大的困难。

软件无线电(software radio)是近年来随着微电子及计算机技术应运而生的一种新的无线电技术,理想的软件无线电系统强调体系结构的开放性和可编程性,专注于减少灵活性差的硬件电路,并把数字化处理(A/D)尽量靠近天线,力求通过软件的更新来改变硬件的配置结构,以求解决传统数据采集卡存在的问题。

结合软件无线电思想,可将AD 采样后得到的数据直接送入数字下变频器,然后通过FPGA程序的改变来实现对数字下变频器内部寄存器的重新配置,从而完成数字下变频功能,该方法既提高了系统的灵活性,又能很好的满足系统对数据传输的高实时性要求。

1传统数据采集卡的特点与缺陷传统数据采集卡的结构一般。

传统数据采集卡的特点是先对模拟输入信号进行模拟混频正交解调,混频后的信号经模拟低通滤波器后再进行AD采样。

由于两路模拟乘法器以及低通滤波器难以达到一致,因此,采样后得到的I、Q两路信道间的幅度往往不平衡,相位正交误差较大。

同时,随着模拟输入频率的增加,对于模拟低通滤波器、AD器件的采样率设计要求也越来越高。

另外,随着采样率和采样精度的提高,现有的PCI、PCI—E等接口规范,其数据传输速率也难以达到设计要求。

2新型数据采集卡设计思想数据采集作为数字接收机的重要组成部分,其在处理带宽和数据传输速率方面应当具有很好的灵活性和可扩展性,而传统的数据采集卡难以满足这些要求。

基于数字信号处理的优点,是将模拟中频输入先进行AD采样,采样后得到的数据再送入数字下变频器件进行数字下变频处理后,再通过PCI总线将数据读入上位机。

文章编号:1001-893X(2009)07-0077-04基于S O PC的PC I数据采集卡的设计与实现3何寅生,高 俊,娄景艺(海军工程大学电子工程学院,武汉430033)摘 要:针对传统数字接收机数据采集模块因集成化程度高而造成资源浪费且缺乏灵活性的问题,依据PC I总线支持突发传输特性和FPG A可编程的灵活性,编写了PC I接口的驱动程序,设计并实现了基于FPG A可控制的高速数据采集卡。

采用A ltera公司的可编程逻辑器件EP3C10F256C8N在S OPC Builder环境下完成PC I桥的快速开发,并利用W in D river工具在W indows XP系统下实现设备的驱动程序开发,完成从模式数据突发传输和设备中断的功能。

该数据采集卡开发周期短、开发成本低,尤其适用于用户的不同需求,具有较高的实用价值。

关键词:数字接收机;数据采集模块;PC I总线;现场可编程门阵列;片上可编程系统中图分类号:T N919;TP311 文献标识码:A doi:10.3969/j.issn.1001-893x.2009.07.018Desi gn and Reali zati on of a PC I Sampli n g Card Based on S OPCHE Yin-sheng,G AO Jun,LOU J ing-yi(Depart m ent of Electr onic Engineering,Naval University of Engineering,W uhan430033,China)Abstract:A s data sa mp ling module in traditi onal digital receiversmay waste l ogical res ource and be lack of flexibility,a high s peed data sa mp ling card based on FPG A and PC I bus is designed and realized.T o meet the request,EP3C10F256C8N is chosen as FPG A.PC IB ridge is i m p le mented quickly by S OPC Builder.U sing the devel opment t ool ofW inD river,the driver p r ogra m is devel oped f or devices running on W indows XP,which co mp letes the functi ons of data transfer in target burstmode and device interrup ti on.W ith shor2 ter devel opment cycle and l ower cost,the card can meet vari ous require ments and has p ractical value.Key words:digital receiver;data sa mp ling module;PC I bus;FPG A;S OPC1 引 言外围部件互连(Peri pheral Component I ntercon2 nect,PC I)局部总线是一个高性能的时钟同步总线结构。

本科毕业设计说明书基于FPGA的高速数据采集卡的设计DESIGN OF HIGH-SPEED DATA ACQUISITION CARDBASED ON FPGA学院(部):电气与信息工程学院专业班级:学生姓名:指导教师:年月日基于FPGA的高速数据采集卡的设计摘要论文还从宏观和微观两个方面来分析数据采集卡的各个组成部分。

从宏观上分析了采集系统中各个芯片间的数据流向、速度匹配和具体通信方式的选择等问题。

使用乒乓机制降低了数据处理的速度,来降低FPGA中的预处理难度,使FPGA处理时序余量更加充裕。

在ARM与FPGA通信方式上使用DMA传输,大大提高了数据传输的速率,并解放了后端的ARM处理器。

设计从宏观上优化数据传输的效率,充分发挥器件的性能,并提出了一些改进系统性能的方案。

从微观实现上,数据是从前端数据调理电路进入AD转换器,再由FPGA采集AD转换器输出的数据,后经过数据的触发、成帧等预处理,预处理后的数据再传输给后端的ARM处理器,最后由ARM处理器送给LCD显示。

微观实现的过程中遇到了很多问题,主要是在AD数据的采集和采集数据的传输上。

在后期的系统调试中遇到了采集数据错位、ARM与FPGA通信效率低下,还有FPGA 中预处理时序紧张等问题,通过硬件软件部分的修改,问题都得到一定程度的解决。

在整个数据采集卡的设计过程中还遇到高速PCB设计、硬件设计可靠性、设计冗余性和可扩展性等问题,这些都是硬件设计中的需要考虑和重视的问题,在论文的最后一章有详细论述。

关键词:高速数据采集,触发,高速PCB设计,高速ADC1DESIGN OF HIGH-SPEED DATA ACQUISITION CARDBASED ON FPGAABSTRACTDate acquisition is the premise of measure, the foundation of analysis and the beginning of cognition. Most precise device is based on the date acquisition. With the development of the electronic and digital technology, the speed of date transmission and the calculation of CPU are faster and faster; therefore the requirements of data acquisition and processing are more severe than before.This paper analyzes the system from Macro-and micro respect. From the macro point of view it analyzes data flowing, speed matching and the selection of specific means of communication of acquisition system and so on. We adapt ping-pong mechanism to reduce the speed of analyzing data and pre-difficult of FPGA which lead to the ease of processing Timing Margin of FPGA. DMA transfer is used as communication between ARM and FPGA which improve data transmission rates, and liberate the back-end ARM processor. From the micro point of view, data enter into the A/D converter from the front-end conditioning circuitry, FPGA collecting data on the output of A/D converter and go through the pre-operation of triggering and framing of data. After these operations, data are transmitted to the back-end of the ARM processor and then display on the LCD. A lot of difficult exited in the successful operation in the micro respect which is mainly about A/D data collection and the of transmission data. All of these issues have been settled by the revising of hardware and software.KEYWORDS:High-speed Data Acquisition, Triggering, High-speed PCB High-speed, A/D converter21绪论1.1 引言数计算机技术在飞速发展,微机应用日益普及深入,微机在通信、自动化、工业自动控制、电子测量、信息管理和信息系统等方面得到广泛的应用。

一种高速数据采集卡的设计与实现

摘要:为了实现对武器系统模拟信号的采集和数据分析,根据PC/104总线的数据采集系统的设计思想,数据采集卡以A/D转换器、CPLD和FIFO相结合来实现信号的连续采集与数据传输的控制。

A/D转换器实现信号的采样保持和模数转换,CPLD实现数据采集和存储过程的控制。

实验结果表明,该数据采集卡操作简单、实时性强、性能稳定,可实现对被测信号高速连续的数据采集。

关键词:数据采集;复杂可编程逻辑器件;FIFO;时序控制;逻辑控制

O 引言

测试设备是武器系统中最主要的子系统之一,它的工作正常与否将直接影响到整个武器系统的作战性能。

在对武器系统进行测试的过程中,需要对一系列的电压、电流等模拟量信号进行快速、实时的数据采集和分析,检查这些模拟量的指标是否符合要求,可以对武器系统是否发生故障做出诊断,保证武器系统的正常工作。

根据现代战争对武器系统的作战需求,提高快速机动保障能力,研制出体积小、结构紧凑、便携式的测试设备就成为主要的目标。

本文设计了一种基于PC/104总线的高速数据采集系统,其目的在于替代示波器在武器系统测试中的作用。

常规采集方案主要有两种:

(1)由单片机直接控制的采集方案,这是最简单最常用的控制方案。

由于每次采样都要有单片机的参与,需占用单片机的时间,影响其数据处理,而且对于多通道、多个A/D转换器的控制,因所需处理的信息更多,则更加不方便。

(2)由DMA控制的采集方案。

此方案硬件电路复杂,若与单片机配合使用,需要单片机具有总线挂起功能,否则还需要进行总线切换,影响数据的及时处理。

综合以上两种方案的优缺点,本数据采集卡自动采样硬件电路主要采用可编程逻辑器件CPLD和先进先出FIFO(First In First Out)技术设计而成,可以很好地实现高速数据采集。

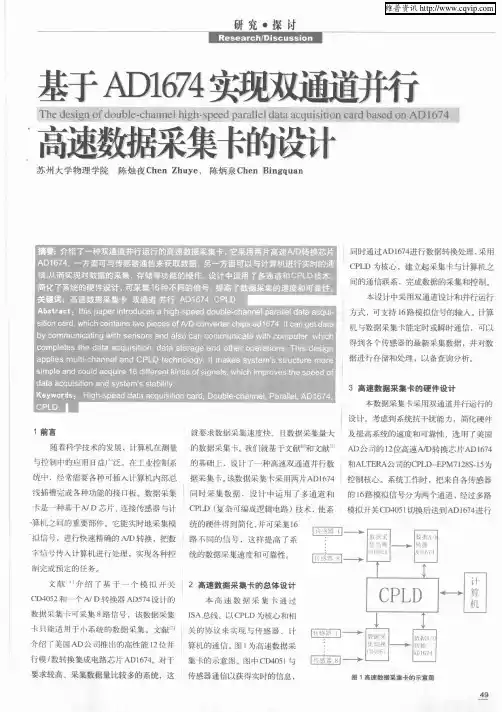

1 数据采集卡总体方案设计

数据采集卡是由信号调理电路、带采样保持器的A/D模数转换器、多路模拟开关、FIFO数据缓存、CPLD芯片及时钟电路等部分组成,具有高精度、高可靠性、高抗干扰能力等特点。

总体结构设计原理如图1所示。

2 芯片介绍

该数据采集卡采用的芯片主要有:AD9283模/数转换器、AD508A多路选择开关、EPM7128SCL84-6CPLD和CY7C4261 FIFO缓存器。

下面对以上所用芯片做一简要介绍。

2.1 AD9283模/数转换器简介

本数据采集卡选用了ANALOG DEVICE公司生产的高速8位模/数转换器AD9283。

它采用先进CMOS制作工艺,提供20脚表面贴装封装形式。

片内集成高性能采样和保持放大器,输入信号可采用单输入或差分输入;处理输入电压

峰峰值在0~1 V之间的模拟信号;采用单+3 V模拟电源和单+3 V数字电源;片内提供+1.2~+1.3 V的参考电压;最高抽样速率可达100 MSPS;具有高速并行输出接口。

2.2 EPM7128SCL84-6 CPLD芯片简介

本数据采集卡选用一片Altera公司生产的EPM7128SLC84-6CPLD作为核心处理芯片,它具有高阻抗、电可擦除等特点,可用门单元为2 500个,有64个用户可用I/O引脚,工作电压为+5 V,管脚间最大延迟为5 ns,采用PLCC-84封装,通过JTAG接口可实现在线编程。

2.3 CY7C4261 FIFO缓存器简介

本数据采集卡选用的FIFO器件是CYPRESS公司生产的高速、低功耗、先入先出存储器芯片CY7CA261。

它的容量为16K×9位,读写周期为10 ns,支持异步和同步读写操作,写数据和读数据分别具有时钟和使能信号,具有“空、满、可编程几乎空、可编程几乎满”四个状态标志位,没有绝对地址的概念,只有读指针和写指针的相对位置,只要标志不为0,就可以进行写操作,只要标志不为0,就可以进行读操作,读写操作可以同时进行。