第11章 模数数模转换(南通大学)(陈继红)

- 格式:ppt

- 大小:890.50 KB

- 文档页数:61

0引言随着通信技术及数字信号处理技术的飞速发展,作为模拟信号与数字信号界面的模数转换器(ADC)得到越来越广泛地应用.而流水线结构模数转换器因其高分辨率、高精度以及在速度与功耗之间良好的折中而倍受青睐.在流水线型ADC中,采样保持电路(S/H)是一个十分关键的部分.随着模数转换器在高分辨率图像、视频处理及无线通信等领域的广泛应用,对高速、高精度、基于标准CMOS工艺的可嵌入式采样保持电路的需求也日益迫切.此外,对于正在兴起的基于IP设计和片上系统集基于CMOS工艺流水线型模数转换器采样保持电路设计季红兵(南通大学,江苏南通226019)摘要:采样保持电路作为流水线模数转换器中的重要单元一直是高速高分辨率模数转换器研究设计者十分关注的内容.文章介绍了基于CMOS0.6μm工艺的流水线模数转换器前端采样保持电路以及运放电路的设计仿真.该电路采用电容下极板采样、折叠式共源共栅技术,有效地消除了开关管的电荷注入效应、时钟馈通效应引起的采样信号的误差,提高了采样电路的线性度,节省了芯片面积,降低了功耗.关键词:流水线;模数转换器;采样保持中图分类号:TN45文献标识码:ACMOS-basedDesignofS/HCircuitofPipelinedA/DConverterJIHong-bing(NantongUniversity,Nantong226019,China)Abstract:Asample-and-hold(S/H)circuitasthekeypartoftheanalog-to-digital(A/D)converteralwaysattractstheresearcheranddesignerofA/Dconverter.ThispaperintroducesthedesignandsimulationoftheS/HandOTAcircuitbasedonCMOS0.6umtechnique.Thesampleandholdcircuitisemployedbythecapacitancebottomplatesamplingtechnique,whichcaneliminatethechargeinjectionerrorofswitchMOSFET.Thebootstrappedswitchisusedtoimprovethelinearityoftheswitch,thereforetoimprovethelinearityofthesample/holdcircuit.Inordertoac-celeratetheamplifier′sspeed,savethechipareaandeliminatetheclockfeed-througheffect,adifferentialfoldedCas-codecommonsourcecommongateopampisdesigned.Keywords:pipeline;analog-to-digitalconverter;sample-and-hold收稿日期:2007-08-27基金项目:南通市工业科技创新计划资助项目(A4036)作者简介:季红兵(1966-),男,南通大学电子信息学院讲师,硕士,主要从事数模混合集成电路教学与研究.南通大学学报(自然科学版)JournalofNantongUniversity(NaturalScience)第6卷第4期2007年12月Vol.6No.4Dec.2007文章编号:1673-2340(2007)04-0071-04南通大学学报(自然科学版)2007年成研究来说,也要求有基于低功耗、小面积、低电压、以及可嵌入设计的采样保持电路模块.1流水线模数转换器结构分析一个通常的模数转换器由N级大致相同的结构组成,如图1所示.每一级由采样/保持电路(S/H)、低分辨率FlashA/D转换器(sub-ADC)、数模转换器(DAC)、减法电路及级间增益放大电路构成.其中,我们将每一级中的采样维持S/H、sub-DAC、减法器和级间增益集成在一个功能块内,称为增益/数模转换单元,即MDAC.流水线模数转换器采用多个较低精度的FlashA/D转换器采样信号并进行分级量化,然后将各级的量化结果使用一定的编码算法组合起来,构成一个高精度的A/D转换器.在执行中,流水线模数转换器完成一次转换的过程如下:首先,第一级电路的采样保持部分对输入信号采样,并进行一个B位分辨率的粗略模数转换,对输入的模拟信号进行初级量化;然后,用数模转换器(DAC)产生一个对应于该量化结果的模拟电平值并送至减法电路,减法电路从输入信号中扣除此模拟值,并将剩余值精确放大固定增益2B-1后送交下一级电路处理;下级电路的处理与上文所述相同.经过N级这样的处理后,将每级的输出组合起来并经过数字校验电路就得到模拟输入信号对应的高精度Y位模数转换结果.前级电路将模拟信号处理完以后会将转换的数码存储在寄存器中,在时钟的控制下,输入第2个待转换的模拟信号进行第2个信号的量化,这样每一级能同时进行独立处理.所以,一次转换只需要一个时钟周期.在这种结构中,要增加分辨率只需要增加级数,分辨率与芯片面积成正比关系.因此,流水线型模数转换器是一种高速、高分辨率的模数转换器,并且,由于采用了分级量化和数字校验技术,降低了每级电路的精度要求,简化了模数转换器的设计,降低了高分辨率A/D转换器对于高精度参考电源的高度依赖.采样保持电路是流水线结构ADC中实现级间信号传递的重要环节,该单元完成对上级信号的采样,并对前级量化的结果进行D/A转换,产生对应于该量化结果的模拟电平,然后从上级信号中减除这个模拟电平得到剩余量,并将剩余量进行固定增益2B-1的精确放大(B为每级分辨率),将放大后的剩余信号一方面送给Sub-ADC模块进行本级的量化,另一方面传递到后级进行后几位的模数转换.在高分辨率流水线ADC中,采样保持单元对输入信号采样精度、放大固定增益2B-1精度及D/A转换的线性度直接影响着整个A/D转换分辨率,同时在MDAC中信号的建立时间是决定整个流水线模数转换器转换速度的主要因素[1-3].2采样保持电路结构及原理文章中电路设计仿真分别采用Cadence和HSPICE软件.流水线模数转换器的采样保持电路采用基于电荷转移的开关电容结构如图2所示.当!1-由高变低时,M2和M3将共模电平与电路输入断开,M2、M3和M1相比尺寸要小的多,这样它们注入的电荷量就少.然后!1变低,M1断开,此时输入被采样到采样电容Cs上面来.管的电荷注入基本上在2个采样电容间平均分配,所以不会对输出有影响.然后!1+变低,M5和M6断开,因为采样电容Cs的底板浮空,电荷量保持不变,所以这2个晶体管的电荷注入不会影响到采样信号.这就是所谓的数字输出数字纠错YbitBbitB+1bit模拟输入步骤1步骤2步骤3步骤NV02B-1+-subDACsubADCBbitMADC图1流水线型模数转换器结构框图BbitBbit・72・M20M21M22BLAS1BLAS2M23BLAS3M24BLAS4BLAS5INBLASBLASM25M26M27M28M29M30M31M32M33底板采样技术.M5和M6的尺寸较大以保证足够的带宽.另外,当!1+变低的时候,M7、M8断开.然后!2由低变高,M4、M9、M10导通,采样保持电路进入保持状态,电荷从采样电容Cs转移到CF上[1,3-4].3采样保持电路中运算放大器的设计及仿真采用保持电路的性能由其中的运算放大器直接决定.因此,运算放大器的设计要求为高速、高增益、大的动态范围、低功耗.图3、图4、图5分别为运算放大器的放大级电路、共模反馈电路、偏置电路.在运放的结构上,选择三级共源共栅(TripleCascode)结构.它具有高直流增益、高带宽、低功耗、容易进行频率补偿等特点.其缺点是输出的摆幅要在电源上减去7个Vdsat,故摆幅较小.我们的解决方案是:使用5V电源、高摆幅的偏置电路、全差分结构[2,5].在流水线模数器中,由于其高精度和高速率的系统要求,所以在MDAC中其运放也相应的需要高速度和大的直流增益,由于本系统采用5V的供电电源,所以我们采用了结构简单、高速、高增益的Triple-Cscode运放结构.在流水线型模数转换器中,为了降低很多非线性效应,通常采用双端输入结构,当然在设计中要使用全差分运算放大器,并图2开关电容结构INBIASVCMM2M7M9M10M3M8M1M4M5M6!1-!1+!2!2!1+!1-INBIASVCMCFVOUTVOUTVINVINCsCs-+-+!2!1!1+!1+!1-!1!1+!2BLAS1BLAS2BLAS3BLAS4BLAS5IN+CMBLASM1M3M5M7OUT-M9M11M2M4M6OUT+M8M10IN-M12M13图3运放放大级电路图4运放共模反馈电路OUT-CMBLASBLASOUT+M14M15M16M19M18M17CMCM!1!1!1!2!2!2图5偏置电路季红兵:基于CMOS工艺流水线型模数转换器采样保持电路设计・73・南通大学学报(自然科学版)2007年且为了达到一定的采样增益精度,要求其具有很高的增益和较大的输出摆幅.而差分运放大多采用具有很大交流阻抗的恒流源作为负载以实现较高增益.但这通常会带来一个问题,即输出共模电压难以稳定.因此,需要加入能稳定共模电压的负反馈电路,从而保证运放的正常工作.对于10位精度,5MHz的流水线式模数转换器,模数转换器的转换周期为200ns,一般用于采样保持时间要小于半个转换周期,采样保持电路要在60ns的时间内达到LSB/2,所以运放的增益要大于67dB.采用无锡上华0.6!mCMOS工艺对运放电路仿真,如图6所示,得到开环增益为93.8dB,相位裕度为60度,单位增益带宽400MHz.4结论通过对流水线型模数转换器的工作原理介绍,设计了影响模数转换器系统性能的关键模块,即采样保持电路模块.并基于无锡上华0.6μmCMOS工艺库对采样保持电路的运算放大器进行了设计仿真,达到系统要求.参考文献:[1]BEHZADRazavi.DesignofAnalogCMOSIntegradedCir-cuit[M].InternationalEditions,2000.[2]EALLENPhilip,HOLBERGDouglasR.CMOSAnalogCir-cuitDesign[M].英文版.北京:电子工业出版社,2002.[3]ABOAM,GRAYPR.A1.5V10bit14.3MS/sCMOSpipelineanalog-to-digitalconverter[J].IEEEJ.Solid-StateCircuits,1999,34(5):599-666.[4]ALLENPE.SwitchedCapacitorCircuit[M].[S.l.]:VanNos-trandReinholdCo.,1984.[5]吴建辉.COMS模拟集成电路分析与设计[M].北京:电子工业出版社,2004.(责任编辑:仇慧)图6运放仿真波形10080604020180160140120100806040100!1m10m100m1101001k10k100k1x10x100x增益/dB频率/Hz・74・。

基于以太网的模数转换精度全自动修正方法

倪继锋;张程

【期刊名称】《上海师范大学学报(自然科学版)》

【年(卷),期】2013(42)5

【摘要】理想的模数转换在直角坐标轴上应是一条过零点的直线.在实际工程中,由于信号处理电路及芯片性能等因素,对转换的精度产生了影响.因此需要采用线性拟合的方法加以修正,从而提高转换精度.提出一种基于以太网的模数转换全自动修正方法,采用软硬件配合的方式,只需轻点鼠标,即可自动完成所有模数转换通道的线性修正,并且计算出误差、信噪比和有效位数等指标,同时将线性修正系数存入模数转换卡板载的EEPROM中,与传统方法相比.此方法更方便、准确和高效,具有广泛的应用前景.

【总页数】5页(P465-469)

【作者】倪继锋;张程

【作者单位】上海师范大学信息与机电工程学院,上海201418;上海航天控制技术研究所,上海200233

【正文语种】中文

【中图分类】TP29

【相关文献】

1.基于以太网通讯的全自动换电机器人决策控制系统设计与实现 [J], 罗华;燕小强;李钊

2.基于以太网总线的全自动汽车U形螺栓拧紧机设计 [J], 陈凯;边群星

3.基于以太网的高精度模数转换模块的研究 [J], 邱学武

4.基于嵌入式单片机的模数转换精度提高技术及算法 [J], 袁越阳;马小林;周超伦;刘炜;何超

5.基于以太网的高精度模数转换模块的研究和探讨 [J], 王国珺;林碧芬

因版权原因,仅展示原文概要,查看原文内容请购买。

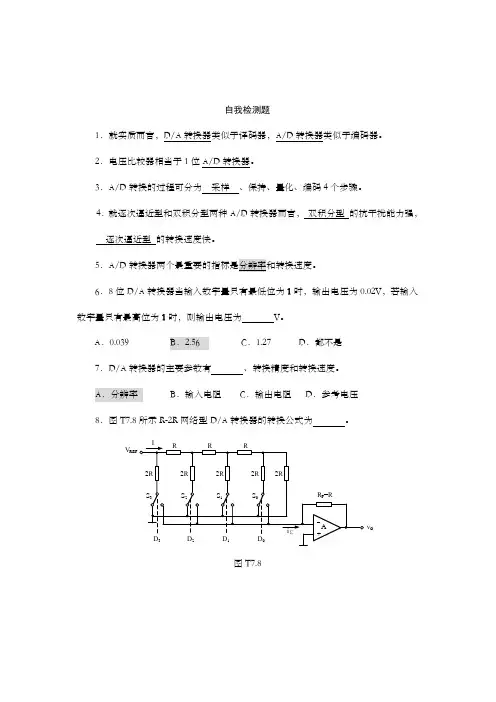

自我检测题1.就实质而言,D/A转换器类似于译码器,A/D转换器类似于编码器。

2.电压比较器相当于1位A/D转换器。

3.A/D转换的过程可分为采样、保持、量化、编码4个步骤。

4.就逐次逼近型和双积分型两种A/D转换器而言,双积分型的抗干扰能力强,逐次逼近型的转换速度快。

5.A/D6.8位D/A转换器当输入数字量只有最低位为1时,输出电压为0.02V,若输入数字量只有最高位为1时,则输出电压为V。

A.0.039 B.2.56 C.1.27 D.都不是7.D/A转换器的主要参数有、转换精度和转换速度。

A.分辨率B.输入电阻C.输出电阻D.参考电压8.图T7.8所示R-2R网络型D/A转换器的转换公式为。

V REFv O图T7.8A .∑=⨯-=303REF o 22i iiD V vB .∑=⨯-=304REFo 2232i iiD V vD .∑=⨯=34REF o 22i iiD V v9.D/A 转换器可能存在哪几种转换误差?试分析误差的特点及其产生误差的原因。

解:D/A 转换器的转换误差是一个综合性的静态性能指标,通常以偏移误差、增益误差、非线性误差等内容来描述转换误差。

偏移误差是指D/A 转换器输出模拟量的实际起始数值与理想起始数值之差。

增益误差是指实际转换特性曲线的斜率与理想特性曲线的斜率的偏差。

D/A 转换器实际的包络线与两端点间的直线比较仍可能存在误差,这种误差称为非线性误差。

10.比较权电阻型、R -2R 网络型、权电流型等D/A 转换器的特点,结合制造工艺、转换的精度和转换的速度等方面比较。

解:权电阻型D/A 转换器的精度取决于权电阻精度和外接参考电源精度。

由于其阻值范围太宽,很难保证每个电阻均有很高精度,因此在集成D/A 转换器中很少采用。

R -2R 网络型D/A 转换器电阻网络中只有R 和2R 两种阻值的电阻,且比值为2。

虽然集成电路技术制造的电阻值精度不高,但可以较精确地控制不同电阻之间的比值,从而使R -2R 网络型D/A 转换器获得较高精度。

数字系统原理与设计课程设计指导书南通大学电子信息学院2017年 2月一、课程设计要求1.完成课程设计,包括设计仿真与验证。

学生根据所选课题的任务、要求和条件进行总体的方案设计,通过论证与选择,确定总体方案。

此后运用EDA软件对方案进行程序设计、仿真分析。

2.通过本次课程设计,提高系统设计能力,增强工程实践能力和创新能力。

3.撰写总结报告。

总结报告是学生对课程设计全过程的系统总结,学生应按规定格式撰写说明书,说明书主要内容有:1)设计技术报告封面封面上应写明设计题目、学生姓名、专业、年级、指导教师姓名。

设计题目明确、简短,能反映设计的实质性内容。

2)摘要及关键词应扼要叙述设计的主要内容和特点,文字简练。

3)目录目录一般不超过3级,章节应编写所在的页码。

4)正文正文应全面、准确的反映设计的指导思想、设计进行的主要工作和所取得的结论和成果,正文应包含一下内容:(1)前言。

应说明设计的目的、意义、市场需求;阐述本设计要解决的技术难题以及解决技术难点的指导思想和要预期达到的技术效果。

(2)设计方案论证。

应说明设计原理并进行方案的选择,说明为什么要选择该设计方案(包括各种方案的分析、比较),还应阐述所采用的方案特点和设计的技术路线。

(3)计算部分。

这部分在设计说明书中占有相当大的比例。

在说明书中要列出各零件的工作条件、给定的参数、计算公式以及各主要参数计算的详细步骤和计算结果,并说明根据此计算应选用什么元器件和零部件。

对需要使用的计算机的设计还应包括各种软件的设计。

(4)结构设计部分。

这也是设计说明书的重要组成部分,应包括机械结构的设计、各种电气控制线路设计以及功能电路设计、计算机控制部件装置的设计等,以及以上各种设计所绘制的图纸。

(5)结论。

概括本设计的情况和价值,分析其特色、优点、有何创新、性能达到何种水平,并应指出其中存在的问题和今后改进的方向,特别是对设计中遇到的重要问题要重点指出并加以研究。

(6)参考文献。

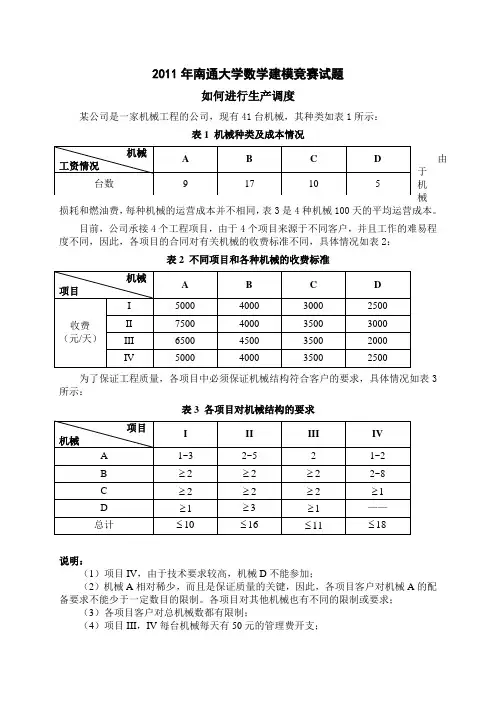

2011年南通大学数学建模竞赛试题如何进行生产调度某公司是一家机械工程的公司,现有41台机械,其种类如表1所示:表1 机械种类及成本情况由于机械损耗和燃油费,每种机械的运营成本并不相同,表3是4种机械100天的平均运营成本。

目前,公司承接4个工程项目,由于4个项目来源于不同客户,并且工作的难易程度不同,因此,各项目的合同对有关机械的收费标准不同,具体情况如表2:表2 不同项目和各种机械的收费标准为了保证工程质量,各项目中必须保证机械结构符合客户的要求,具体情况如表3所示:表3 各项目对机械结构的要求说明:(1)项目IV ,由于技术要求较高,机械D 不能参加;(2)机械A 相对稀少,而且是保证质量的关键,因此,各项目客户对机械A 的配备要求不能少于一定数目的限制。

各项目对其他机械也有不同的限制或要求;(3)各项目客户对总机械数都有限制;(4)项目III ,IV 每台机械每天有50元的管理费开支;问题一:估计4种机械的每天的费用,并估计出4种机械的每天的费用的95%的置信区间。

问题二:由于收费是按机械数计算的,而且4个项目总共同时最多需要的机械台数是10+16+11+18=55,多于公司现有机械数41台,应如何合理地分配现有的机械力量,使公司每天的直接收益最大?问题三:若由于燃油费的上涨,导致每种机械的运营成本上涨10%,请问需要调整分配方案吗?如上涨10%呢?请就不同上涨幅度进行讨论,给出一套因应预案。

2011年南通大学数学建模竞赛编号专用页参赛队员(打印并签名):队员1:,学院,电话队员2:,学院,电话队员3:,学院,电话竞赛评阅编号(由竞赛组委会评阅前进行编号):2011年南通大学数学建模竞赛题目如何进行生产调度摘要本问题是一个数据处理及目标线性优化问题。

对于问题一估计4种机械的每天费用,根据所给数据,建立一个样本模型,对样本进行均值矩估计,即将4种机械100天的费用求的平均值近似看做是4种机械的每天费结果如下表:对于问题二,4计算4种机械对应4个项目的总收益减去总的运营成本及管理开支,再根据4种机械数目总量及4个项目对机械的要求建立线性规划模型,列出目标函数以及约束条件,通过LINGO涨幅度,这里引入上涨幅度变量进行控制,并分别进行线性规划计算,得出各种涨幅下的分配方案作为一套因应预案。

基于KM教学法的软件工程教学研究

鞠小林;陈继红

【期刊名称】《计算机教育》

【年(卷),期】2010(000)020

【摘要】知识的逻辑结构描述了知识的体系结构及知识之间的内在联系,思维导图是直观的知识组织与表征工具.KM教学法是将知识的逻辑结构与思维导图相结合,通过将知识逻辑结构化,经过分类和分层组织,再经过抽点、连线、成网、扩展、概型等逻辑加工,得到反应知识本质的逻辑结构图与思维导图.本文以"软件工程"为例,探讨应用KM教学法的要点.

【总页数】4页(P107-110)

【作者】鞠小林;陈继红

【作者单位】南通大学,计算机科学与技术学院,江苏,南通,226019;南通大学,计算机科学与技术学院,江苏,南通,226019

【正文语种】中文

【中图分类】G642

【相关文献】

1.基于软件工程思想的软件测试教学研究与实践 [J], 于述春;林晶;黄斌

2.基于创新教育的"软件工程"课程教学研究 [J], 余员琴;张弘华;彭姣丽;李晨;韦荣堂

3.基于创新教育的“软件工程”课程教学研究 [J], 余员琴;张弘华;彭姣丽;李晨;韦荣堂

4.基于混合模式软件工程课程的教学研究 [J], 梁君霞

5.基于校企合作的软件工程项目实训类课程教学研究 [J], 王玉娟;赵小蕾;王先国;曹汉华

因版权原因,仅展示原文概要,查看原文内容请购买。

《试验设计与数据处理》复习要点第一章误差分析一、真值与平均值1、真值:指在某一时刻和某一状态下,某量的客观值或实际值。

2、平均值(1)算术平均值:x̅=x1+x2+⋯+x nn =∑x in同样试验条件下,多次试验值服从正态分布,算术平均值是这组等精度试验值中的最佳值或最可信赖值。

(2)加权平均值:x̅w=w1x1+w2x2+⋯+w n x nw1+w2+⋯+w n =∑w i x i∑w i(3)对数平均值:x̅L=x1−x2ln x1x2=x2−x1ln x2x1,试验数据的分布曲线具有对称性(4)几何平均值:lg x̅G=∑lg x̅in(5)调和平均值:H=n∑1x i二、误差的基本概念1、绝对误差=测得值-真值,结果可正可负。

2、相对误差=绝对误差/真值≈绝对误差/测得值,结果可正可负。

3、算术平均误差∆=∑|x i−x̅|n4、标准误差(1)样本标准差s=√∑(x i−x̅)2n−1=√∑x i2−(∑x i)2/nn−1(2)总体标准差σ=√∑(x i−x̅)2n =√∑x i2−(∑x i)2/nn三、误差来源及分类根据误差的性质或产生原因,可分为随机误差、系统误差、粗大(过失)误差。

1、随机误差:在一定试验条件下,以不可预知的规律变化着的误差;2、系统误差:在一定试验条件下,由某个或某些因素按照某一确定的规律起作用而形成的误差;3、粗大(过失)误差:一种显然与事实不符的误差。

四、试验数据的精准度1、精密度:反映随机误差大小的程度,是指在一定的试验条件下,多次试验值的彼此符合程度或一致程度;2、正确度:指大量测试结果的(算术)平均值与真值或接受参照值之间的一致程度,反映了系统误差的大小,是指在一定的试验条件下,所有系统误差的综合;3、准确度:反映系统误差和随机误差的综合,表示了试验结果与真值或标准值的一致程度。

五、试验数据误差的统计检验1、随机误差的检验随机误差的大小可用试验数据的精密程度来反映,而精密度的好坏又可用方差来度量,所以对测试结果进行方差检验,即可判断随机误差之间的关系。

改进RFM模型在房地产客户细分中的研究及应用

杜科;邓佳雯;陈继红

【期刊名称】《电脑知识与技术》

【年(卷),期】2018(014)019

【摘要】随着房地产销售市场的火爆,房地产销售企业如雨后春笋般涌现,房地产企业之间的竞争也不断加剧.本文结合客户特定的购房行为特点,在传统的RFM模型的基础上,通过属性分析构建了含购房总面积在内的RFMA模型,并使用K-means 聚类算法对客户群体细分,最终形成可抛弃客户、低价值客户、中段客户、高价值客户和会员客户五类客户群体,并详细剖析不同客户群的特征和价值.

【总页数】4页(P243-245,251)

【作者】杜科;邓佳雯;陈继红

【作者单位】南通大学计算机科学与技术学院,江苏南通226019;南通大学计算机科学与技术学院,江苏南通226019;南通大学计算机科学与技术学院,江苏南通226019

【正文语种】中文

【中图分类】TP311

【相关文献】

1.基于改进RFM模型的电子商务客户细分 [J], 徐翔斌;王佳强;涂欢;穆明

2.基于"数量-质量-效益"的金融产品客户细分——一个改进的RFM模型 [J], 刘寅;关志新;王缇

3.一种改进的RFM模型在网店客户细分中的应用 [J], 李为康; 杨小兵

4.一种改进的RFM模型在网店客户细分中的应用 [J], 李为康;杨小兵

5.改进RFM模型的汽车4S店客户细分研究 [J], 王玉凤;孙文秀;杜梦娇

因版权原因,仅展示原文概要,查看原文内容请购买。