瑞萨单片机M32C NC308WA有效的编程技术(培训资料)

- 格式:pdf

- 大小:434.99 KB

- 文档页数:26

项目二32灯电路的制作【教学目标要求】1、知识目标(1)进一步强化W A VE、PROTEUS软件的使用。

(2)掌握C语言和汇编语言的综合设计程序;熟练汇编语言的程序设计及调试、排障。

(3)掌握单片机电路的制作技能,制作32灯电路。

2、技能目标强化对W A VE、PROTEUS等软件的综合使用,加强程序的编写、调试、排障,实物电路的电子技能制作。

3、情感目标以小组协作形式开展学习,完成项目任务;养成良好的职业习惯,增强学生的分析、操作、研究创新的能力以及与小组合作、沟通能力。

4、节能、环保,健康、安全教育目标要求学生安全用电、爱护实验、实训设备,节约用电,不乱扔费弃物;培养学生良好的学习习惯。

【教学内容分析】本项目主要是单片机的综合应用实训,加强学生对软件的综合使用与提高,电路的设计、程序的编写、调试、排障等内容。

主要包括以下学习任务:任务一绘制32灯仿真电路图(2课时)任务二32灯电路制作实训1(2课时)任务三绘制32灯底板线路图(2课时)任务四32灯程序设计实训1(2课时)任务五32灯电路制作实训2(2课时)任务六32灯程序设计实训2(2课时)任务七32灯电路制作实训3(2课时)【教学重点与难点】重点:(1)电路的灵活设计与布局;(2)实训过程中的排障。

难点:(1)电路的设计;(2)汇编程序的设计与调试;(3)实物电路制作。

【教学方法和策略】布置学生5~6人为一组,分成6个学习小组。

采用实物演示、现场操作、小组合作探究、讲授等教学方法,具体教学策略是:1、书面作业先让学生自学本项目各任务的内容,收集相关资料,归纳本项目的主要知识点,初步完成书面作业。

2、展示交流各学习小组在课堂上汇报、展示前置作业成果,各小组间进行交流、质疑,小组长记录组员的表现。

教师在小组进行汇报、展示的过程中,巡视指导,并对各小组的表现进行点评并记录成绩。

3、教师评析教师根据学生掌握知识的情况,再次进行相关知识的补充、讲解。

瑞萨单片机发脉冲程序瑞萨单片机是一种常用的微控制器,广泛应用于各种电子设备中。

在很多应用中,我们需要通过单片机来发出脉冲信号,用于控制其他设备的工作。

下面,我将介绍一种简单的瑞萨单片机发脉冲程序。

首先,我们需要准备好开发环境。

瑞萨单片机的开发环境可以使用Renesas Flash Programmer (RFP)软件进行编程。

在安装好RFP软件后,我们需要连接好单片机与电脑,并确保电脑能够正确识别单片机。

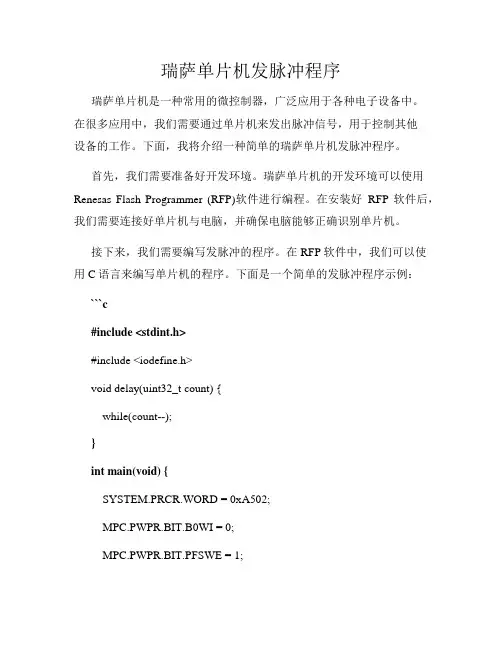

接下来,我们需要编写发脉冲的程序。

在RFP软件中,我们可以使用C语言来编写单片机的程序。

下面是一个简单的发脉冲程序示例:```c#include <stdint.h>#include <iodefine.h>void delay(uint32_t count) {while(count--);}int main(void) {SYSTEM.PRCR.WORD = 0xA502;MPC.PWPR.BIT.B0WI = 0;MPC.PWPR.BIT.PFSWE = 1;PORTA.PDR.BIT.B0 = 1;MPC.PA0PFS.BIT.PSEL = 0x01;MPC.PWPR.BYTE = 0x80;SYSTEM.PRCR.WORD = 0xA500;while(1) {PORTA.PODR.BIT.B0 = 1;delay(1000000);PORTA.PODR.BIT.B0 = 0;delay(1000000);}return 0;}```在这个程序中,我们首先定义了一个延时函数delay,用于控制脉冲的频率。

然后,在main函数中,我们对单片机的端口进行了配置,将A端口的第0位设置为输出模式。

接着,我们使用一个无限循环来不断发出脉冲信号。

在循环中,我们先将A端口的第0位设置为高电平,延时一段时间后再将其设置为低电平,再延时一段时间,如此循环。

最后,我们需要将程序下载到单片机中。

瑞萨单片机发脉冲程序1. 引言本文将介绍如何使用瑞萨单片机来编写一个发脉冲的程序。

我们将首先介绍瑞萨单片机的基本知识,然后详细讲解如何编写发脉冲的程序,并提供示例代码和详细的步骤说明。

2. 瑞萨单片机简介瑞萨单片机是一种常用的嵌入式系统开发工具,它具有高性能、低功耗、易于开发和广泛的应用领域等特点。

瑞萨单片机通常使用汇编语言或C语言进行编程,并可以通过编程器将程序下载到单片机中运行。

3. 发脉冲程序设计发脉冲程序是一种常见的应用场景,它可以用于控制外部设备的工作。

在本节中,我们将介绍如何使用瑞萨单片机编写一个简单的发脉冲程序。

3.1 硬件准备在编写发脉冲程序之前,我们需要准备以下硬件设备:•瑞萨单片机开发板•发脉冲的外部设备(例如LED、继电器等)•连接线3.2 程序设计3.2.1 引入头文件首先,在程序的开头,我们需要引入瑞萨单片机的相关头文件。

这些头文件包含了一些常用的函数和宏定义,可以方便我们进行编程。

#include <reg51.h>3.2.2 定义IO口接下来,我们需要定义用于发脉冲的IO口。

在瑞萨单片机中,IO口通常用P0、P1、P2、P3等寄存器来表示。

我们可以通过设置这些寄存器的值来控制IO口的电平。

sbit pulse_pin = P1^0; // 定义发脉冲的IO口3.2.3 编写发脉冲函数现在,我们可以编写一个发脉冲的函数。

该函数将会在IO口上产生一个脉冲信号,并控制外部设备的工作。

void pulse(){pulse_pin = 1; // IO口置高,产生脉冲信号delay(1000); // 延时1秒pulse_pin = 0; // IO口置低,停止脉冲信号delay(1000); // 延时1秒}3.2.4 主函数调用最后,在主函数中调用发脉冲函数,以便在单片机上运行该程序。

void main(){while(1){pulse(); // 调用发脉冲函数}}3.3 编译和下载程序完成程序的编写后,我们需要将程序编译并下载到瑞萨单片机中运行。

瑞萨MCU在汽车仪表及R32C/100应用中的解决方案瑞萨科技致力于提供移动通信、汽车电子以及PC/AV(数码家电)领域的半导体解决方案。

在全球汽车半导体市场中,瑞萨占有7.1%的市场份额,排名第四位;在日本市场中占据第一位,市场份额为22.3%。

其汽车半导体解决方案包含了安全、信息、动力总成、底盘以及车身五个方面,其中每个方面都有多种解决方案。

汽车仪表解决方案仪表MCU的特点分以下几个方面:1.内嵌步进电机PWM控制器:可直接控制和驱动4-6个步进电机,无需外驱动器IC,因此可以节省成本和布局空间,具有优良的EMI/EMC性能;2.内嵌LCD控制器:28/32段×4公共引脚,可以直接控制LCD,同样无需外置驱动器IC,因此可以节省成本和布局空间,具有优良的EMI/EMC性能;3.高速CPU:单指令周期,20MHz的H8S最小指令执行时间为50ns,而40MHz 的H8SX最小指令执行时间是25ns;4.强大的定时器:片上16位定时器脉冲单元有三个16位定时器通道,包括输入捕捉、输出比较、PWM和相位计算。

R32C/100特殊模块的基本功能,包括三个部分:定时器脉冲单元(TPU);步进电机PWM控制器和LCD控制器。

TPU是由3个16位定时器通道组成,包括最多8个脉冲输入/输出,可以为每个通道设置:比较匹配的波形输出;输入捕捉功能;计数器清零操作;同步运行;定时器计数器能够同时写入;可以比较匹配与输入捕捉同时清零;利用同步计数器操作实现寄存器同时输入/输出;与同步运行结合的最大7相位PWM 输出。

致芯科技最具实力的芯片解密、IC解密、单片机解密等解密服务机构,致芯科技拥有多年的解密服务经验和超高水平的解密技术,一直从客户利益出发,为每位客户提供最科学最合理最低成本的解密方案与解密服务,深受客户的信赖与喜爱。

对于LCD控制器/驱动器,其重要功能有:28/32段×4公共引脚;段输出引脚可用作11个帧频的4组端口选择;A或B波形可以用软件进行选择;内置电源分离电阻;除了待机模式和模块停止模式外,还有操作模式显示。

平凡老师的单片机教程作者:平凡第一节初学单片机几个不易掌握的概念第二节新8051教程---前言第三节单片机概述第四节单片机内、外部结构分析一第五节半导体储存器第六节单片机内、外结构分析二第七节单片机内、外结构分析三第八节单片机内、外结构分析四第九节单片机内、外结构分析五第十节寻址方式与指令系统第十一节单片机指令二数据传递类指令第十二节单片机指令三累加器A 与片外RAM 之间的数据传递类指令第十三节单片机指令四算述运算类指令第十四节单片机指令五逻辑运算类指令第十五节单片机指令六条件转移指令第十六节单片机指令七位及位操作指令第十七节计数器与定时器第十八节计时/计数器的方式控制字第十九节中断系统第二十节定时、中断练习一第二十一节定时、计时练习二第二十二节串行接口第二十三节串行接口应用编程实例第二十四节常用接口电路及基编程第二十五节动太扫描显示接口第二十六节键盘接口与编程第二十七节矩阵式键盘接口技术及编程单片机扩展一单片机扩展二单片机扩展三单片机扩展四单片机扩展五第一节初学单片机几个不易掌握的概念随着电子技术的迅速发展,计算机已深入地渗透到我们的生活中,许多电子爱好者开始学习单片机知识,但单片机的内容比较抽象,相对电子爱好者已熟悉的模拟电路、数字电路,单片机中有一些新的概念,这些概念非常基本以至于一般作者不屑去谈,教材自然也不会很深入地讲解这些概念,但这些内容又是学习中必须要理解的,下面就结合本人的学习、教学经验,对这些最基本概念作一说明,希望对自学者有所帮助。

一、总线:我们知道,一个电路总是由元器件通过电线连接而成的,在模拟电路中,连线并不成为一个问题,因为各器件间一般是串行关系,各器件之间的连线并不很多,但计算机电路却不一样,它是以微处理器为核心,各器件都要与微处理器相连,各器件之间的工作必须相互协调,所以就需要的连线就很多了,如果仍如同模拟电路一样,在各微处理器和各器件间单独连线,则线的数量将多得惊人,所以在微处理机中引入了总线的概念,各个器件共同享用连线,所有器件的8 根数据线全部接到8 根公用的线上,即相当于各个器件并联起来,但仅这样还不行,如果有两个器件同时送出数据,一个为0 ,一个为1 ,那么,接收方接收到的究竟是什么呢?这种情况是不允许的,所以要通过控制线进行控制,使器件分时工作,任何时候只能有一个器件发送数据(可以有多个器件同时接收)。

Sigmastar SSC335全功能开发板技术手册一、应用场合:1. 适用于开发以下产品:(1)200万/300万网络摄像机。

(2)300万抓拍摄像机。

(3)安防监控产品。

(4)网络音视频产品。

(5)低功耗快速启动摄像机。

(6)4G/WIFI无线传输产品。

(7)编码器。

(8)双路摄像机。

(9)运动相机。

(10)航拍摄像机。

(11)UVC相机。

2. 适用于学习linux平台、熟悉ARM开发的开发者。

3. 适用于需要熟悉sigmstar平台音视频编解码、图像处理、UVC相机、4G/WIFI无线传输的开发人员。

二、型号:CA-M3335AID-MAIN-V1三、产品特色:■主控芯片采用Sigamastar高性能多媒体处理器片上系统(SOC),,内部集成A7、FPU、NEON,主频800MHZ。

■支持WDR、多级降噪及多种图像增强和矫正算法,为客户提供专业级的图像质量。

■采用标准的H.264/H.265 High Profile压缩算法,方便在窄带上实现高清晰的图像传输。

■最大支持300万编码.最高支持2304x1296@30帧、2048*1536@30帧、1920x1080@45帧H.264/H.265编码。

■内置1Gb DDR2。

■支持MIPI、USB Sensor输入、图像质量优异。

■支持双向语音对讲。

■支持ONVIF2.4标准协议,可对接海康、大华、雄迈等NVR。

■支持GB28181协议。

■支持手机监看。

■支持4G全网通:5模或者7模。

■支持WIFI:热点和STA模式。

■支持GPS、北斗定位。

■支持POE供电,功率13W,符合IEEE802.3af/at标准■支持二次开发。

■尺寸26*24mm,邮票孔。

方便做小型化产品。

■接口全,且与本公司其他主控、平台定义一致,适合兼容多款产品。

四、技术参数:五、产品外观及接口定义:J24:音频输入1.AIN0(左)2.音频地3.AIN1(右)J5:报警/485接口1.报警输出22.报警输出13. RS485正4. RS485负4. RS485_D+J15:SD 外接接口1. SD_DATA22. SD_DATA33. SD_CMD 4. 3.3V 5. SD_CLK J2:接POE 模块脚位接口定义主控pin脚接口类型电平功能描述说明1 SD_CDZ19 输入 3.3V SD卡插入检测低电平有效2 SD_DATA1 81 输入/输出 3.3V SD卡数据13 SD_DATA0 79 输入/输出 3.3V SD卡数据04 SD_CLK 77 输出 3.3V SD卡时钟50MHz5 GND 地数字地6 SD_CMD 78 输出 3.3V SD卡命令信号7 SD_DATA3 82 输入/输出 3.3V SD卡数据38 SD_DATA2 81 输入/输出 3.3V SD卡数据29 NC10 NC11 NC12 NC13 NC14 NC15 NC16 LINK_LAN 输入/输出 3.3V 网络连接状态指示输出高,网络连接成功连接网口RJ45绿灯17 ACT_LAN 输入/输出 3.3V 网络数据传输指示高/低切换:有数据传输,切换速度指示传输速度。

![瑞萨RL78单片机和开发工具(培训教程)[RL78 Tool introduce]](https://uimg.taocdn.com/83c203c26137ee06eff918d4.webp)

瑞萨单片机入门教程本教程以R7F0C002L单片机为例一、开发环境下载安装与工程注意:该工程目录和工程名不能含有中文1.1、 CubeSuite+环境的下载:官网下载地址将安装环境下载到本地,该文件大小532M在安装过程中有提示需要填写注册码,请输入以下注册码,如果无效请联系供应商。

查看是否已经注册:在IDE环境中选择 Help->About后有下面窗口:注册码:67DCS-V3Q7L-XMGL9-FI6L9-EE1BJ该注册码有限制台数的,一旦注册了就会把MAC绑定,重装无需注册!当有以下报错时:请查看是否已经注册。

1.2、按照一般的软件安装方法安装好IDE环境,下面介绍IDE环境的配置:1、将DIF_RFP文件夹下的Device_Custom文件夹拷贝到安装目录下的C:\Program Files\Renesas Electronics\CubeSuite+下(这里是默认的安装目录,另外注意:DIF_RFP中Readme_Device_Custom.txt说将Device_Custom文件夹拷贝到C:\Program Files\Renesas Electronics\CubeSuite+\Device下,但是实际上不可以!)。

DIF_RFP文件夹安装根目录当配置成功以后会在芯片族里面多出R7F系列的单片机,如下图示:2、将DIF_RFP文件夹下的RFP_R7F0C002L_V10000子目录下面的两个文件(Device_Custom文件夹和Custom_Productlist.xml文件)拷贝到安装目录下的C:\Program Files\Renesas Electronics\Programming Tools\Renesas Flash Programmer V2.01\Device下(这里是默认安装路径)。

1.3、开发环境新建工程:1、启动CubeSuite+环境,会弹出如下启动界面:2、创建Project工程,在上述启动界面中,点击Creat New Project栏中GO按钮,将会弹出以下对话框:选择工程路径创建输入工程名选择芯片型号选择芯片族3、点击Create创建工程,会得到如下工程界面:4、通过生成工具生成一个简单的代码:5、将芯片型号换成R7F0C002单片机,并且将选项字节配置好!详细设置请参考第三章代码生成与编码。

M16C族编程技巧(M3T-NC30WA 工具链)2005年2月M3T-NC30WA 特点•支持MCU M16C 族-M16C/60, 30, 20, 10, R8C/Tiny 系列.•性能(Performance) 可以减小ROM大小的辅助功能强大的提高代码效率的优化功能•存储器型号(Memory model) 支持每个变量的near/far限定词•扩展功能(Extended functions)支持嵌入式系统的#pragma指令 •附加工具(Attached tools)IDE -TM 和HEW, 结构汇编器(Structured assembler) 和模拟器(Simulator).M3T-NC30WA存储器分配(Memory allocation )near/far#pragma ADDRESS #pragma BITADDRESS #pragma SECTION #pragma STRUCTetc减小ROM 大小(Reducing ROM size )#pragma SBDATA #pragma SPECIAL #pragma JSRA/JSRW#pragma BIT UTLxx etc 其他#pragma INTERRUPT #pragma PARAMETER #pragma ASM/ENDASM #pragma INTCALLasm( ) etcRTOS#pragma ALMHANDLER #pragma CYCHANDLER #pragma INTHANDLER #pragma TASK提高性能!减小系统消耗(Reduce OS overhead )给不同系统分配存储器!#pragma 扩展功能(Extended Functions)NEAR 修饰符–000000H ~ 00FFFFH 区域FAR 修饰符–000000H ~0FFFFFH 区域每个变量都有Near 和far指定near/far默认ROM areaSFRRAM areanear RAM far ROMFFFF1Mbytesnear areafar areaint near i;int far j;注意: 程序已固定far 属性FFFF默认是NEAR 指针j i *i int * i ;k*k int far * k;FFFFint far * far j ;*j#pragma ADDRESS port 03ECH#pragma ADDRESS base 100H extern int base;#pragma ADDRESS base2 _base+2H extern int base2;#pragma ADDRESS base3 _base+4H extern int base4;不仅对I/O 变量,对RAM 中的变量也很方便.Same as#define base *(volatile int *)0x100#pragma 地址指定变量的绝对地址 可以被用作设定SFR 区#pragma INTERRUPT /B func()Using bank registersvoid func( void ){}R0FB R1R2A0R3A1将后寄存器切换到前寄存器R0FB R1R2A0R3A1R0FBR1R2A0R3A1SB将寄存器切换到后寄存器R0FB R1R2A0R3A1SB声明中断处理器(interrupt handler) /B 使中断处理加快#pragma INTERRUPT /E func() 允许中断(FSET I) 保存寄存器获得自动变量区 释放自动变量区 恢复寄存器 REITvoid func(void){}出口入口/E 允许多个中断支持可以通过下列方式指定中断向量表号#pragma INTERRUPT Vector number Function_nameOr#pragma INTERRUPT Function_name(vect= Vector number )使用编译选项–fmake_vector_table 自动生成变量中断表.#pragma INTERRUPT timerA0(vect=21)void timerA0(void){}.section __NC_rvector,ROMDATA .rvector 21,_timerA0asm function汇编语言可以被直接包含在C 程序中格式是asm(““). 例如: asm(“FSETI”); 使用“$$, $b, $@”来参考参数或自动变量.用户不需要考虑变量的存储类(storage class).asm(“mov.w R0,$@”, value );FB offsetSymbol Register-2[FB]_value R0对于变量:对于位字段:asm(“bset $b”, bit.b1 );Bit position,Symbol1,_bit可以在C 中编写长汇编源代码.int asmRoutine(int arg){return work;分配工作区供汇编代码使用.int work;将工作区的偏移(offset)设置在堆栈上asm (“在#pragma ASM 和#pragma ENDASM 之间编写长汇编源程序.#pragma ASMmov.w R0,work[FB]...#pragma ENDASM注意1 : 不要破坏asm 函数中的寄存器.int func(long arg){register int ret=0;#pragma ASMmov.l #00000000H,R2R0mov.l #_addr,A0mov.l #_addr2,A1mov.w _counter,R3rmpa.wmov.l R2R0,_result #pragma ENDASM………..return ret;}参考并修改寄存器保存寄存器恢复寄存器pushm R0,R2,R3,A0,A1popm R0,R2,R3,A0,A1注意2 : 不要写入会引起汇编源程序控制流混乱的转移(branch)指令。

单片机培训华清远见(一)引言概述:华清远见单片机培训是一门系统性的培训课程,旨在帮助学员快速入门并掌握单片机的基本原理与应用。

通过本培训,学员将学习到单片机的硬件结构、编程语言、电子系统设计以及实际应用案例等方面的知识。

本文将分五个大点详细阐述单片机培训华清远见的内容。

正文:一、单片机基础知识1. 单片机的定义和分类2. 单片机的工作原理和基本架构3. 单片机常用的编程语言和开发工具4. 单片机的输入输出方式和中断处理机制5. 单片机的时钟源和时序控制二、单片机编程技术1. 单片机常用编程语言的基本语法和数据类型2. 单片机的程序结构和调试技巧3. 单片机的位操作和存储器管理4. 单片机的中断编程和定时器计数器应用5. 单片机与外设的通信和控制技术三、单片机硬件设计1. 单片机的外部器件和电路连接2. 单片机的IO口电平转换和电源管理3. 单片机的AD/DA转换和PWM输出4. 单片机的串行通信接口和总线控制5. 单片机的外设扩展和程序存储器扩展四、单片机应用案例1. 单片机在智能家居系统中的应用2. 单片机在工业自动化控制中的应用3. 单片机在汽车电子系统中的应用4. 单片机在医疗设备中的应用5. 单片机在网络通信系统中的应用五、单片机培训总结通过华清远见单片机培训,学员将全面了解单片机的基本原理和应用技术,具备独立设计和开发单片机应用系统的能力。

无论是从理论知识,还是从实践案例,本培训都将为学员提供充分的学习资源和实践机会。

掌握单片机技术将为学员在相关行业的就业和职业发展提供有力的支持。

总结:本文针对华清远见单片机培训进行了详细的阐述。

通过系统的培训内容,学员将全面掌握单片机的基本原理、编程技术、硬件设计和应用案例等方面的知识。

这将为学员提供丰富的学习资源和实践机会,使他们具备独立设计和开发单片机应用系统的能力,为未来的职业发展打下坚实基础。