4_触发器的状态转换图

- 格式:ppt

- 大小:651.50 KB

- 文档页数:24

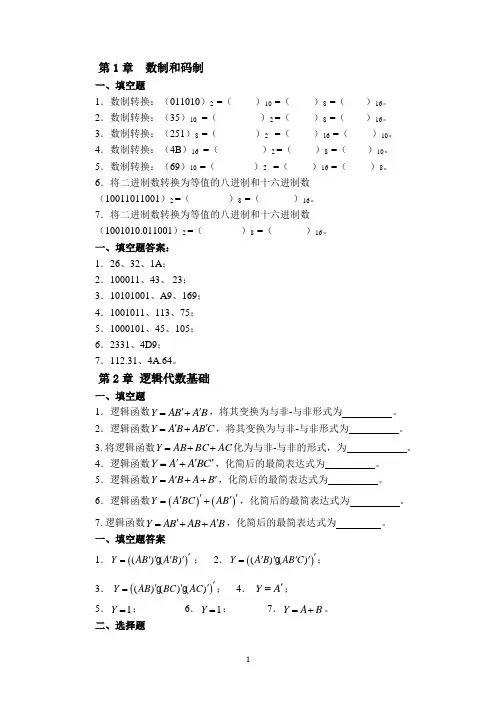

第1章 数制和码制一、填空题1.数制转换:(011010)2 =( )10 =( )8 =( )16。

2.数制转换:(35)10 =( )2 =( )8 =( )16。

3.数制转换:(251)8 =( )2 =( )16 =( )10。

4.数制转换:(4B )16 =( )2 =( )8 =( )10。

5.数制转换:(69)10 =( )2 =( )16 =( )8。

6.将二进制数转换为等值的八进制和十六进制数(10011011001)2 =( )8 =( )16。

7.将二进制数转换为等值的八进制和十六进制数(1001010.011001)2 =( )8 =( )16。

一、填空题答案:1.26、32、1A ;2.100011、43、 23;3.10101001、A9、169;4.1001011、113、75;5.1000101、45、105;6.2331、4D9;7.112.31、4A.64。

第2章 逻辑代数基础一、填空题1.逻辑函数Y AB A B ''=+,将其变换为与非-与非形式为 。

2.逻辑函数Y A B AB C ''=+,将其变换为与非-与非形式为 。

3. 将逻辑函数AC BC AB Y ++=化为与非-与非的形式,为 。

4.逻辑函数Y A A BC '''=+,化简后的最简表达式为 。

5.逻辑函数Y A B A B ''=++,化简后的最简表达式为 。

6.逻辑函数()()Y A BC AB ''''=+,化简后的最简表达式为 。

7. 逻辑函数Y AB AB A B ''=++,化简后的最简表达式为 。

一、填空题答案1.()()()Y AB A B '''''= ; 2.()()()Y A B AB C '''''=;3. ()()()()Y AB BC AC ''''=; 4. Y A '=;5.1Y =; 6.1Y =; 7.Y A B =+。

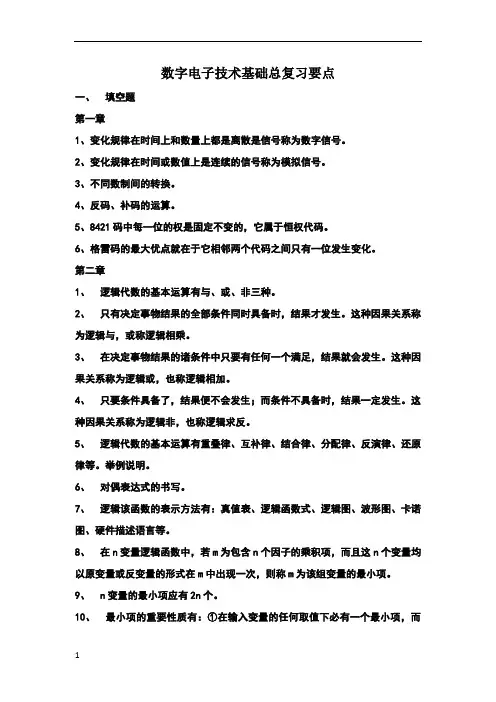

数字电子技术基础总复习要点一、填空题第一章1、变化规律在时间上和数量上都是离散是信号称为数字信号。

2、变化规律在时间或数值上是连续的信号称为模拟信号。

3、不同数制间的转换。

4、反码、补码的运算。

5、8421码中每一位的权是固定不变的,它属于恒权代码。

6、格雷码的最大优点就在于它相邻两个代码之间只有一位发生变化。

第二章1、逻辑代数的基本运算有与、或、非三种。

2、只有决定事物结果的全部条件同时具备时,结果才发生。

这种因果关系称为逻辑与,或称逻辑相乘。

3、在决定事物结果的诸条件中只要有任何一个满足,结果就会发生。

这种因果关系称为逻辑或,也称逻辑相加。

4、只要条件具备了,结果便不会发生;而条件不具备时,结果一定发生。

这种因果关系称为逻辑非,也称逻辑求反。

5、逻辑代数的基本运算有重叠律、互补律、结合律、分配律、反演律、还原律等。

举例说明。

6、对偶表达式的书写。

7、逻辑该函数的表示方法有:真值表、逻辑函数式、逻辑图、波形图、卡诺图、硬件描述语言等。

8、在n变量逻辑函数中,若m为包含n个因子的乘积项,而且这n个变量均以原变量或反变量的形式在m中出现一次,则称m为该组变量的最小项。

9、n变量的最小项应有2n个。

10、最小项的重要性质有:①在输入变量的任何取值下必有一个最小项,而且仅有一个最小项的值为1;②全体最小项之和为1;③任意两个最小项的乘积为0;④具有相邻性的两个最小项之和可以合并成一项并消去一对因子。

11、若两个最小项只有一个因子不同,则称这两个最小项具有相邻性。

12、逻辑函数形式之间的变换。

(与或式—与非式—或非式--与或非式等)13、化简逻辑函数常用的方法有:公式化简法、卡诺图化简法、Q-M法等。

14、公式化简法经常使用的方法有:并项法、吸收法、消项法、消因子法、配项法等。

15、卡诺图化简法的步骤有:①将函数化为最小项之和的形式;②画出表示该逻辑函数的卡诺图;③找出可以合并的最小项;④选取化简后的乘积项。

1 : 对于JK触发器,输入J=0,K=1,CLK脉冲作用后,触发器的次态应为()。

(2分)A:0B:1C:Q'D:不确定您选择的答案: 正确答案: A知识点:JK触发器的特性为:J=1,K=1时,Q状态为翻转,即Q= Q’2 : 已知Y=A+AB´+A´B,下列结果中正确的是()(2分)A:Y=AB:Y=BC:Y=A+BD:Y=A´+B´您选择的答案: 正确答案: C知识点:利用公式A+AB´=A和A+A´B=A+B进行化简3 : (1001111)2的等值十进制数是()(2分)A:97B:15.14C:83D:79您选择的答案: 正确答案:D知识点:把二进制数转换为等值的十进制数,只需将二进制数按多项式展开,然后把所有各项的数值按十进制数相加。

4 : 图中为CMOS门电路,其输出为()状态(2分)(对于CMOS门电路,输入端接负载时,输入电平不变)A:高电平B:低电平C:高阻态D:不确定您选择的答案: 正确答案: A知识点:对于CMOS门电路,输入端接负载时,输入电平不变5 : 四选一数据选择器的数据输出Y与数据输入Di和地址码Ai之间的逻辑表达式为Y=()(2分)A:A1´A0´D0+ A1´A0D1+ A1A0´D2+ A1A0D3B:A1´A0´D0C: A1´A0D1D:A1A0´D2您选择的答案: 正确答案: A知识点:四选一数据选择器的Y= A1´A0´D0+ A1´A0D1+ A1A0´D2+ A1A0D6 : 一个同步时序逻辑电路可用()三组函数表达式描述(2分)A:最小项之和、最大项之积和最简与或式B:逻辑图、真值表和逻辑式C:输出方程、驱动方程和状态方程D:输出方程、特性方程和状态方程您选择的答案: 正确答案: C知识点:时序逻辑电路的逻辑关系需用三个方程即输出方程、驱动方程及状态方程来描述。

1 : VOL表示什么含义(2分)A:输出低电平B:输入高电平C:输出高电平D:输入低电平您选择的答案: 正确答案: A知识点:O即output,表示输出;L即low,表示低电平----------------------------------------------------------------------------2 : 下列说法不正确的是()(2分)A:同一个逻辑函数的不同描述方法之间可相互转换B:任何一个逻辑函数都可以化成最小项之和的标准形式C:具有逻辑相邻性的两个最小项都可以合并为一项D:任一逻辑函数的最简与或式形式是唯一的您选择的答案: 正确答案:D知识点:一个逻辑函数的最简与或式形式不是唯一的----------------------------------------------------------------------------3 : 二—十进制译码器输入为()(2分)A:BCD代码B:三位二进制数C:十进制数D:二十进制数您选择的答案: 正确答案: A知识点:二—十进制译码器的逻辑功能是将输入BCD码的10个代码译成10个高、低电平输出信号----------------------------------------------------------------------------4 : 触发器的状态转换图如下,则它是:()(5分)A:T触发器B:SR触发器C:JK触发器D:D触发器您选择的答案: 正确答案: A知识点:见T触发器状态转换图----------------------------------------------------------------------------5 : 分析图中所示输入、输出Q的波形。

则该触发器为( ) (5分)A:上升沿触发的JK触发器B: 上升沿触发的SR触发器C:下降沿触发的JK触发器D:下降沿触发的SR触发器您选择的答案: 正确答案: C知识点:参考JK触发器和SR触发器的特性表----------------------------------------------------------------------------6 : +17的8位二进制补码是()(2分)A:11110001B:11101111C:01101111D:00010001您选择的答案: 正确答案:D知识点:符号位用0表示正号,后面的数转换为七位等值的二进制数。

0 1 A =1 A=1 A=0 A=0 《数字电子技术》模拟题一一、单项选择题(2×10分)1.下列等式成立的是( )A 、 A ⊕1=AB 、 A ⊙0=AC 、A+AB=AD 、A+AB=B2.函数F=(A+B+C+D)(A+B+C+D)(A+C+D)的标准与或表达式是( )A 、F=∑m(1,3,4,7,12)B 、F=∑m(0,4,7,12)C 、F=∑m(0,4,7,5,6,8,9,10,12,13,14,15)D 、F=∑m(1,2,3,5,6,8,9,10,11,13,14,15)3.属于时序逻辑电路的是( )。

A 、寄存器B 、ROMC 、加法器D 、编码器4.同步时序电路和异步时序电路比较,其差异在于后者( )A 、没有触发器B 、没有统一的时钟脉冲控制C 、没有稳定状态D 、输出只与内部状态有关,与输入无关5.将容量为256×4的RAM 扩展成1K ×8的RAM ,需( )片256×4的RAM 。

A 、 16B 、2C 、4D 、86.在下图所示电路中,能完成01=+n Q 逻辑功能的电路有( )。

A 、B 、C 、D 、7.函数F=A C+AB+B C ,无冒险的组合为( )。

A 、 B=C=1B 、 A=0,B=0C 、 A=1,C=0D 、 B=C=O8.存储器RAM 在运行时具有( )。

A 、读功能B 、写功能C 、读/写功能D 、 无读/写功能9.触发器的状态转换图如下,则它是:( )A 、T 触发器B 、RS 触发器C 、JK 触发器D 、D 触发器 10.将三角波变换为矩形波,需选用( )A 、多谐振荡器B 、施密特触发器C 、双稳态触发器D 、单稳态触发器二、判断题(1×10分)( )1、在二进制与十六进制的转换中,有下列关系:(1001110111110001)B =(9DF1)H( )2、8421码和8421BCD 码都是四位二进制代码。

2007-2008学年第2学期《数字电路》期末考试试卷(闭卷A)我以⼀名⼤学⽣的⼈格尊严保证,在本场考试中,⾃觉遵守考试纪律,服从考试管理,决不作弊或帮助别⼈作弊!签名:学院专业学号级班··················密···················封·····················线··················命题⼈签字:系主任签字:审核院长签字:共印份数:第1页共4页聊城⼤学计算机学院07—08学年第2学期期末考试2007级《数字电路》试题(闭卷 A卷)⼀、填空题(每空1分,共20分)8421BCD代码为。

2.Y=A(B+C)+CD的对偶式Y D=。

3.常⽤的逻辑函数表⽰⽅法主要有、、、波形图、卡诺图和硬件描述语⾔等。

4.逻辑函数Y=AB+BC+AC化为与⾮—与⾮形式为。

5.如果以⾼电平表⽰逻辑1,以低电平表⽰逻辑0,则这种表⽰⽅法为。

6.⼏个OD(漏极开路输出)门的输出直接相连,可以实现逻辑。

7.CMOS电路最突出的⼀⼤优点是。

(完整版)数字电⼦技术-复习选择填空题汇总(精简)⼀、选择题:1、在下列逻辑电路中,不是组合逻辑电路的是(D)A、译码器B、编码器C、全加器D、寄存器2、下列触发器中没有约束条件的是(D)A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器3、555定时器不可以组成D。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.J K触发器4、编码器(A)优先编码功能,因⽽(C)多个输⼊端同时为1。

A、有B、⽆C、允许D、不允许5、(D)触发器可以构成移位寄存器。

A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器6、某触发器的状态转换图如图所⽰,该触发器应是( C )A. J-K触发器B. R-S触发器C. D触发器D. T触发器7、⼗进制数6在8421BCD码中表⽰为-------------------------------------------------( B )A.0101B.0110C. 0111D. 10008、在图所⽰电路中,使__AY 的电路是---------------------------------------------( A )A. ○1B. ○2C. ○3D. ○49、接通电源电压就能输出矩形脉冲的电路是------------------------------------------( D )A. 单稳态触发器B. 施密特触发器C. D触发器D. 多谐振荡器10、多谐振荡器有-------------------------------------------------------------------------------( C )A. 两个稳态B. ⼀个稳态C. 没有稳态D. 不能确定11、已知输⼊A、B和输出Y的波形如下图所⽰,则对应的逻辑门电路是-------( D )A. 与门B. 与⾮门C. 或⾮门D. 异或门12、下列电路中属于时序逻辑电路的是------------------------------------------------------( B )A. 编码器B. 计数器C. 译码器D. 数据选择器13、在某些情况下,使组合逻辑电路产⽣了竞争与冒险,这是由于信号的---------( A )A. 延迟B. 超前C. 突变D. 放⼤14、电路和波形如下图,正确输出的波形是-----------------------------------------------( A )A. ○1B. ○2C. ○3D. ○415.在何种输⼊情况下,“与⾮”运算的结果是逻辑0。