5-简易数字存储示波器(电)——【全国大学生电子设计大赛】

- 格式:docx

- 大小:832.50 KB

- 文档页数:50

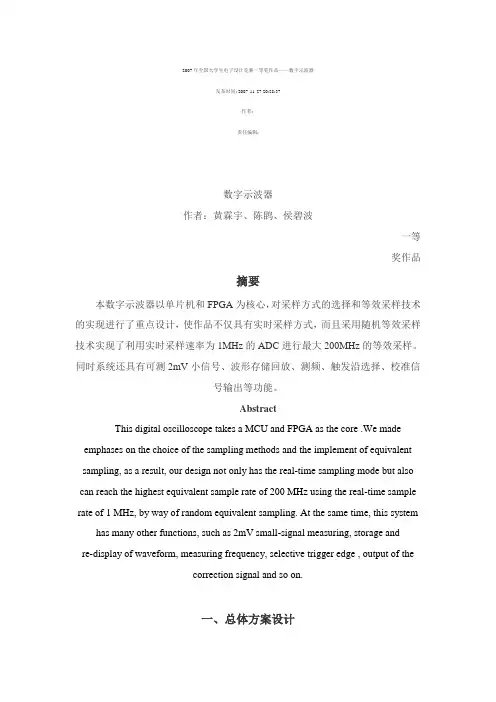

2007年全国大学生电子设计竞赛一等奖作品——数字示波器发布时间: 2007-11-27 20:28:37作者:责任编辑:数字示波器作者:黄霖宇、陈鹍、侯碧波一等奖作品摘要本数字示波器以单片机和FPGA为核心,对采样方式的选择和等效采样技术的实现进行了重点设计,使作品不仅具有实时采样方式,而且采用随机等效采样技术实现了利用实时采样速率为1MHz的ADC进行最大200MHz的等效采样。

同时系统还具有可测2mV小信号、波形存储回放、测频、触发沿选择、校准信号输出等功能。

AbstractThis digital oscilloscope takes a MCU and FPGA as the core .We made emphases on the choice of the sampling methods and the implement of equivalent sampling, as a result, our design not only has the real-time sampling mode but also can reach the highest equivalent sample rate of 200 MHz using the real-time sample rate of 1 MHz, by way of random equivalent sampling. At the same time, this system has many other functions, such as 2mV small-signal measuring, storage andre-display of waveform, measuring frequency, selective trigger edge , output of thecorrection signal and so on.一、总体方案设计1.方案比较与选择仔细分析题目要求,以实时采样速率为1MHz的ADC实现最大200MHz的等效采样,是本题的最大难点,也是设计的重点之一。

设计报告格式及要求0、页面设置每页上方必须留出3cm空白,空白内不得有任何文字,每页右下端注明页码。

纸型:A4页边距:上:3cm ,下:2cm,左:2cm,右2cm设计报告密封纸在距设计报告上端约2厘米处装订,然后将参赛队的代码(代码由赛区组委会统一编制,在发放题目时通知各参赛队)写在设计报告密封纸的最上方。

设计报告装订好后将密封纸掀起并折向报告背面,最后用胶水在后面粘牢。

设计报告上不允许出现参赛队的学校、姓名等文字。

一、报告的基本格式与层次编排0. 封面封面暂时复制例文。

1.基本格式报告题目居中3号黑体,段前段后空0.5行摘要顶格,小4宋加粗或小4黑摘要正文(300字以内)与“摘要”2字之间空1格,小4宋体关键词:…;…;…3~5个,与“摘要”2字之间空1格),顶格,小4宋体(摘要与正文之间另起一页,插入→分隔符→下一页)正文…………………………………………………………………………………………正文小四宋体,每一个自然段首起空2字。

图表的格式:表序与表题为5号黑体,表内文字为5号宋体,表下的标注为小5号宋体;图序与图题为5号黑体,图文、图注为小5号宋体。

行间距为最小值20磅,在排版过程中,若遇到图题和图不能在同一面,或页下留较多空白的问题,可通过适当调整行间距来解决。

图和表与正文之间段前段后空0.5行。

(图和图名,表和表名看成一个整体,之间不空行)参考文献居中,4号黑体,段前段后空0.5行[ 1 ] 作者.书名.版次.出版地:出版者,出版年. 左顶格,5号宋体序号左顶格,用阿拉伯数字加方括号标示;作者名与序号之间空1字;若有2位或3位作者,则作者之间用逗号“,”分隔,最后一位作者用句点(实心点),若超过3位,也只列3位,然后加等。

(正文与参考文献之间另起一页,插入→分隔符→下一页)2.层次划分与编排根据需要可以将正文划分成若干层次,拟定若干级标题,一般三级就可以了。

标题单独占行,末尾不加标点,标题编号与标题文字之间空1格。

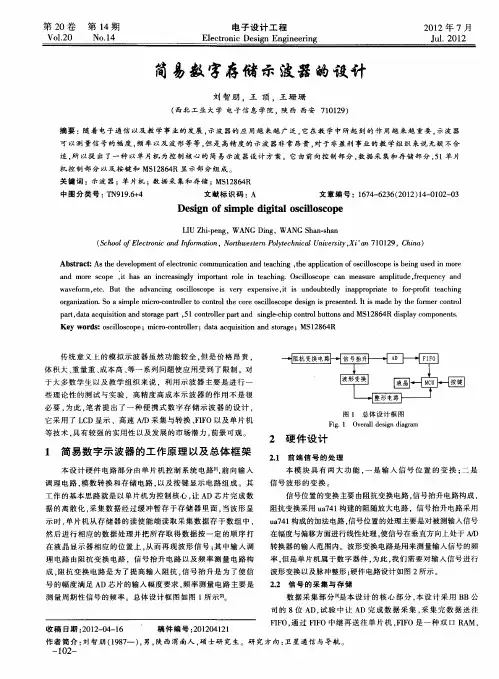

简易数字存储示波器摘要本系统基于示波器原理,以单片机为核心,结合CPLD和FPGA的数据处理能力,实现了波形的实时采样存储和实时显示功能,做到了波形的单踪采集与显示,并且能够对波形进行以下处理:频率、峰-峰值和平均值测量,AUTO SCALE,上下左右平移。

系统达到了较高的性能指标。

但也存在以下不足:不能做到双踪显示,平均值测量不准确等。

电子信息工程李知周张辉全杨光义一、方案论证与选择1、总体方案方案一:纯粹的单片机方式。

由单片机、A/D、D/A以及存储器等构建系统。

这种方式下单片机除了完成基本处理和分析外,还需要完成信号的采集、存储显示等控制工作与变换。

其优点在于系统规模小,有一定的灵活性,但是受到单片机本身指令速度的影响,A/D采样速率受到限制,实时采样性差,示波器的带宽受到很大限制,不适宜于显示高速和复杂的信号,无法满足要求。

方案二:FPGA/CPLD或带有IP核的FPGA/CPLD方式。

即用FPGA/CPLD完成数据的采集、存储、显示及A/D 、D/A等功能,由IP核实现人机交互及信号测量分析等功能。

这种方案的优点在于系统结构紧凑、可以实现复杂测量与控制、操作方便;缺点是调试过程繁琐,而且控制难度大,可视化效果也较差。

方案三:单片机与CPLD结合方式。

即用单片机完成人机界面、系统控制、信号分析、处理、变换功能,用CPLD完成采集控制逻辑及显示控制逻辑功能。

此方案由可编程逻辑器件CPLD和单片机构成主要控制部件,在CPLD内部构造DMA控制单元和地址计数器,可实现高带宽、高速度的要求,在此方案中,示波器的带宽不会受到C51的指令速度的限制,可达到A/D最大采样速率的一半;系统可以对任意波形进行实时采样,实现波形的存储回放。

这种方案兼有前两个方案的优点,且避开了它们的缺点,所以我们采用方案三。

该方案总体框图如下:单片机和CPLD控制的数字存储示波器2、前级信号处理方案一:程控放大由运算放大器AD844、模拟开关CD4051配合精密电位器实现。

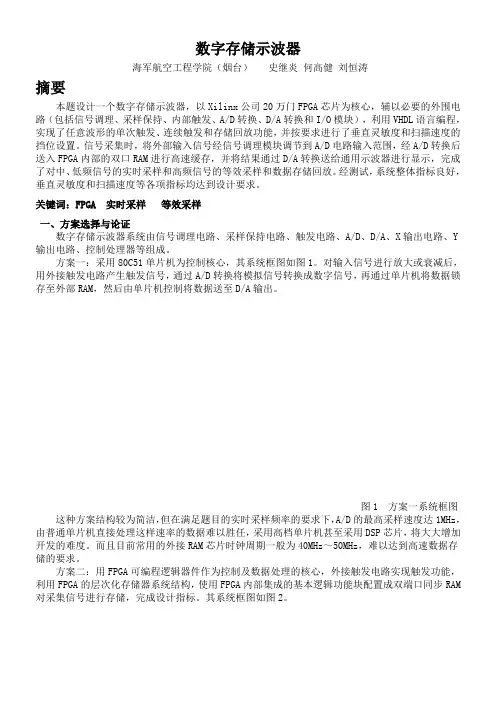

数字存储示波器海军航空工程学院(烟台)史继炎何高健刘恒涛摘要本题设计一个数字存储示波器,以Xilinx公司20万门FPGA芯片为核心,辅以必要的外围电路(包括信号调理、采样保持、内部触发、A/D转换、D/A转换和I/O模块),利用VHDL语言编程,实现了任意波形的单次触发、连续触发和存储回放功能,并按要求进行了垂直灵敏度和扫描速度的挡位设置。

信号采集时,将外部输入信号经信号调理模块调节到A/D电路输入范围,经A/D转换后送入FPGA内部的双口RAM进行高速缓存,并将结果通过D/A转换送给通用示波器进行显示,完成了对中、低频信号的实时采样和高频信号的等效采样和数据存储回放。

经测试,系统整体指标良好,垂直灵敏度和扫描速度等各项指标均达到设计要求。

关键词:FPGA 实时采样等效采样一、方案选择与论证数字存储示波器系统由信号调理电路、采样保持电路、触发电路、A/D、D/A、X输出电路、Y 输出电路、控制处理器等组成。

方案一:采用80C51单片机为控制核心,其系统框图如图1。

对输入信号进行放大或衰减后,用外接触发电路产生触发信号,通过A/D转换将模拟信号转换成数字信号,再通过单片机将数据锁存至外部RAM,然后由单片机控制将数据送至D/A输出。

图1 方案一系统框图这种方案结构较为简洁,但在满足题目的实时采样频率的要求下,A/D的最高采样速度达1MHz,由普通单片机直接处理这样速率的数据难以胜任,采用高档单片机甚至采用DSP芯片,将大大增加开发的难度。

而且目前常用的外接RAM芯片时钟周期一般为40MHz~50MHz,难以达到高速数据存储的要求。

方案二:用FPGA可编程逻辑器件作为控制及数据处理的核心,外接触发电路实现触发功能,利用FPGA的层次化存储器系统结构,使用FPGA内部集成的基本逻辑功能块配置成双端口同步RAM 对采集信号进行存储,完成设计指标。

其系统框图如图2。

图2 方案二系统框图由于FPGA可在线编程,因此大大加快了开发速度。

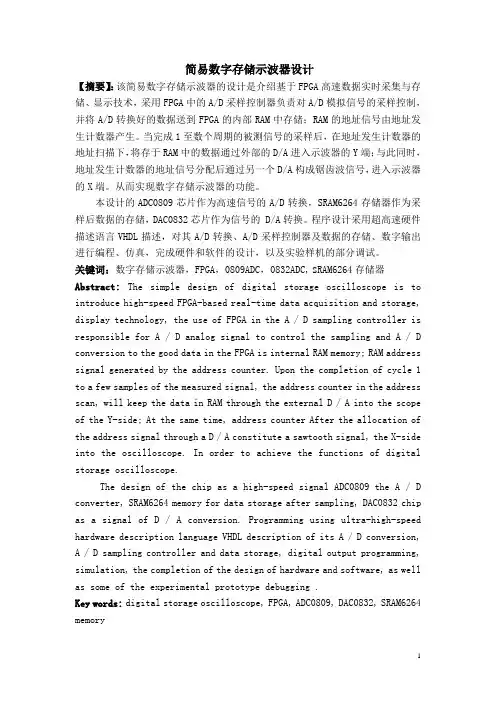

简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于FPGA高速数据实时采集与存储、显示技术,采用FPGA中的A/D采样控制器负责对A/D模拟信号的采样控制,并将A/D转换好的数据送到FPGA的内部RAM中存储;RAM的地址信号由地址发生计数器产生。

当完成1至数个周期的被测信号的采样后,在地址发生计数器的地址扫描下,将存于RAM中的数据通过外部的D/A进入示波器的Y端;与此同时,地址发生计数器的地址信号分配后通过另一个D/A构成锯齿波信号,进入示波器的X端。

从而实现数字存储示波器的功能。

本设计的ADC0809芯片作为高速信号的A/D转换,SRAM6264存储器作为采样后数据的存储,DAC0832芯片作为信号的 D/A转换。

程序设计采用超高速硬件描述语言VHDL描述,对其A/D转换、A/D采样控制器及数据的存储、数字输出进行编程、仿真,完成硬件和软件的设计,以及实验样机的部分调试。

关键词:数字存储示波器,FPGA,0809ADC,0832ADC, S RAM6264存储器Abstract:The simple design of digital storage oscilloscope is to introduce high-speed FPGA-based real-time data acquisition and storage, display technology, the use of FPGA in the A / D sampling controller is responsible for A / D analog signal to control the sampling and A / D conversion to the good data in the FPGA is internal RAM memory; RAM address signal generated by the address counter. Upon the completion of cycle 1 to a few samples of the measured signal, the address counter in the address scan, will keep the data in RAM through the external D / A into the scope of the Y-side; At the same time, address counter After the allocation of the address signal through a D / A constitute a sawtooth signal, the X-side into the oscilloscope. In order to achieve the functions of digital storage oscilloscope.The design of the chip as a high-speed signal ADC0809 the A / D converter, SRAM6264 memory for data storage after sampling, DAC0832 chip as a signal of D / A conversion. Programming using ultra-high-speed hardware description language VHDL description of its A / D conversion, A / D sampling controller and data storage, digital output programming, simulation, the completion of the design of hardware and software, as well as some of the experimental prototype debugging .Key words:digital storage oscilloscope, FPGA, ADC0809, DAC0832, SRAM6264 memory目录【摘要】 1【Abstract】:错误!未定义书签。

数字示波器摘要:本系统基于数字存储示波器的基本原理,以单片机和FPGA组成的最小系统为控制核心,具有实时采样方式和等效采样方式,其实时采样速率≤1MSa/s,并采用顺序等效采样的方式使等效采样速率达到200MSa/s。

系统输入频率范围为10Hz~10MHz,输入幅值范围为4mvVpp~8vVpp,周期测量精度优于0.1%,幅值测量误差小于5%。

系统具有三档垂直灵敏度和七档水平灵敏度,采用内触发方式,触发电平可通过外部旋钮进行调节,同时也具有单次触发功能。

能够对波形进行存储,并且能在需要时调出存储波形进行回放。

系统在模拟示波器上显示波形和刻度,并且借助于128*64点阵液晶显示示波器参数及波形信息,功能稳定,波形清晰,人机界面友好。

关键词:数字存储示波器,实时采样,等效采样,取样保持一、方案论证与选择1. 采样方式选择一般示波器有两种采样方式,实时采样和等效时间采样。

方案一:实时采样。

实时采样是在信号存在周期对其采样,故都是在信号经历的实际时间内显示信号波形。

根据采样定理,采样速率必须高于信号最高频率分量的2倍。

对于周期的正弦信号,一个周期内至少应该有2个采样点。

为了不失真的恢复原被测信号,通常一个周期内就需要采样8个点以上。

其优点是采样时间较短,缺点是对A/D 转换其的速度和精度要求很高。

方案二:等效时间采样。

使用等效采样法的前提是被测信号是周期出现的,因此,为了重建原信号,可以每一个周期内等效地等间隔地抽取少量的样本,最后将多个周期抽取的样本集合到同一个周期内,这样就可以等效成在一个被测信号周期内采样效果。

该方案的优点是采样频率不需要太高,与被采样信号频率相当即可,缺点是要求被测信号是周期的,而且采样过程较慢,比较耗时。

根据题目要求我们选择实时采样和等效采样相结合的方式,实时采样速率≤1MSa/s,即限制了A/D转换器的速率为≤1MSa/s,题目要求水平分辨率至少为20点/div,故我们50KHz以下采用实时采样方式,50KHz~10MHz采用等效时间采样方式,最高等效采样速率可达到200MSa/s。

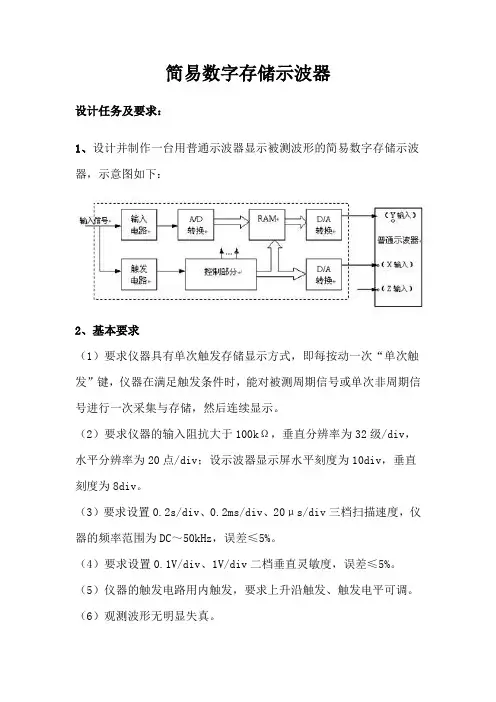

简易数字存储示波器设计任务及要求:1、设计并制作一台用普通示波器显示被测波形的简易数字存储示波器,示意图如下:2、基本要求(1)要求仪器具有单次触发存储显示方式,即每按动一次“单次触发”键,仪器在满足触发条件时,能对被测周期信号或单次非周期信号进行一次采集与存储,然后连续显示。

(2)要求仪器的输入阻抗大于100kΩ,垂直分辨率为32级/div,水平分辨率为20点/div;设示波器显示屏水平刻度为10div,垂直刻度为8div。

(3)要求设置0.2s/div、0.2ms/div、20μs/div三档扫描速度,仪器的频率范围为DC~50kHz,误差≤5%。

(4)要求设置0.1V/div、1V/div二档垂直灵敏度,误差≤5%。

(5)仪器的触发电路用内触发,要求上升沿触发、触发电平可调。

(6)观测波形无明显失真。

3、发挥部分(1)增加连续触发存储显示方式,在这种方式下,仪器能连续对信号进行采集、存储并实时显示,且具有锁存(按“锁存”键即可存储当前波形)功能。

(2)增加双踪示波功能,能同时显示两路被测信号波形。

(3)增加水平移动扩展显示功能,要求存储深度增加一倍,并且能通过操作“移动”键显示被存储信号波形的任一部分。

(4)垂直灵敏度增加0.01V/div档,以提高仪器的垂直灵敏度,并尽力减小输入短路时的输出噪声电压。

方案选择及设计理念:数字存储示波器系统由信号调理电路、采样保持电路、触发电路、A/D、D/A、X输出电路、Y输出电路、控制处理器等组成。

下图所示为数字存储示波器的原理框图。

每隔一端时间对输入的模拟信号进行采样然后经过A/D转换,把这些数字化后的信息按一定的顺序存入RAM中,当采样频率走高时,就可以实现信号的不失真存储。

当需要观察这些信息时,只要以合适的频率把这些信息从存储器RAM中按原顺序取出,经D/A转化和LPF滤波后送至示波器就可以观察到稳定的还原后的波形。

方案讨论:采样方式的选择本题要求的单次信号测量,需采用实时采样;要求最高信号频率为50KHZ,为使该频率下每个周期内有20个采样点,就要求最高采样速率为1MHZ,A/D转换速率1Ms/s,在目前市场条件下满足1MHZ采样速率的A/D无论技术条件还是价格都不是困难的。

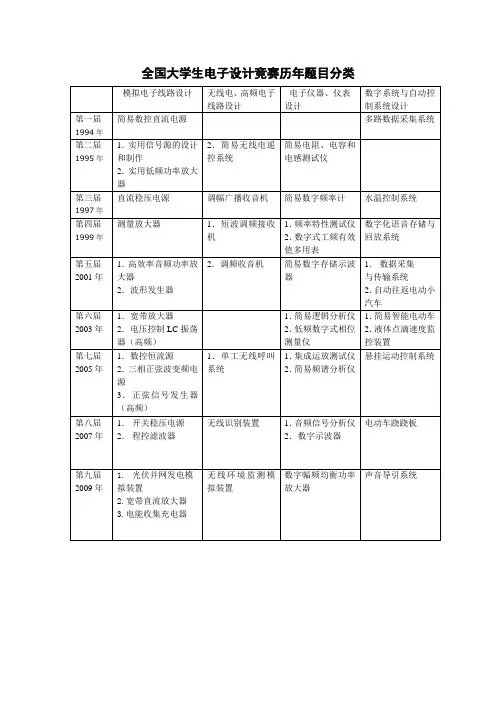

全国大学生电子设计竞赛题目分析全国大学生电子设计竞赛题目类型简介由国家教委高教司倡导并组织的全国大学生电子设计竞赛从1994年的首届试点到2003年已经成功地举办了6届。

从6届电子设计竞赛的试题来看,可以归纳成7类,即:(1)电源类:简易数控直流电源(第一届),直流稳压电源(第三届);(2)信号源类:实用信号源的设计和制作(第二届),波形发生器(第五届),电压控制LC振荡器(A题)(第六届);(3)高频无线电类:简易无线电遥控系统(第二届),调幅广播收音机(第三届),短波调频接收机(第四届),调频收音机(第五届);(4)放大器类:实用低频功率放大器(第二届),高效率音频功率放大器(第五届),宽带放大器(B题)(第六届);(5)仪器仪表类:简易电阻、电容和电感测试仪(第二届),简易数字频率计(第三届),频率特性测试仪(第四届),数字式工频有效值多用表(第四届),简易数字存储示波器(第五届),低频数字式相位测量仪(C题)(第六届),简易逻辑分析仪(D题)(第六届);(6)数据采集与处理类:多路数据采集系统(第一届),数字化语音存储与回放系统(第四届),数据采集与传输系统(第五届)。

(7)控制类:水温控制系统(第三届),自动往返电动小汽车(第五届);简易智能电动车(E题)(第六届);液体点滴速度监控装置(F题)(第六届)。

从以上试题可见,试题具有实用性强、综合性强、技术水平发挥余地大的特点。

涉及到的电子信息类专业的课程有:低频电路、高频电路、数字电路、微机原理、电子测量、单片机、可编程逻辑器件、EDA设计等;实践性教学环节有:电子线路实验课、微机原理实验课、课程设计、生产实习等;可选用的器件有:晶体管、集成电路、大规模集成电路、单片机、可编程逻辑器件等;设计手段必须采用现代电子设计方法与开发工具,如VHDL语言、Xilinx Foundation Series EDA工具、单片机编程器等。

不难看出,电子设计竞赛的试题既反映了电子技术的先进水平,又引导高校在教学改革中应注重培养学生的工程实践能力和创新设计能力。

全国大学生电子设计竞赛介绍一、竞赛基本信息1.竞赛名称(中文):全国大学生电子设计竞赛竞赛名称(英文):National Undergraduate Electronic Design Contest 2.竞赛层次/性质:学科竞赛/选修3.竞赛参与对象:在校电气信息大类专业本科生4. 竞赛官方网站:/二、竞赛目的与定位全国大学生电子设计竞赛是教育部高教司、工业和信息化部人教司共同主办的全国性大学生科技竞赛活动,目的在于按照紧密结合教学实际,着重基础、注重前沿的原则,促进电子信息类专业和课程的建设,引导高等学校在教学中注重培养大学生的创新能力、协作精神;加强学生动手能力的培养和工程实践的训练,提高学生针对实际问题进行电子设计、制作的综合能力;吸引、鼓励广大学生踊跃参加课外科技活动,为优秀人才脱颖而出创造条件。

全国大学生电子设计竞赛是大学生创新计划活动的重要内容,是学生将专业基础知识与实践动手能力实现结合的平台,其知识支撑是电气信息大类专业基础与实践类课程。

其任务是使大学生熟练掌握综合电子系统的设计方法和技术,能够将电子系统设计、DSP技术、嵌入式系统等技术进行有机融合,为培养大学生基本具备科学研究的能力奠定良好的基础,为大学生的就业或继续深造提供可持续发展的潜力。

大学生通过该项竞赛应能达到:1.掌握多种技术集成的设计方法;2. 掌握查阅国内外相关技术手册和资料的基本方法;3. 掌握选择相关技术和优化系统的方法;4. 掌握综合系统实验的测试方法和技术;5. 具有良好的协作的团队精神;6. 基本具备独立从事科学研究的能力。

三、参加竞赛基本要求及流程(一)组织方式竞赛的组织、命题、评审与宣传工作由全国及赛区组织委员会和专家组负责。

1.全国竞赛组委会负责全国竞赛的组织领导、协调与宣传工作。

全国竞赛专家组负责竞赛命题、评审工作。

2.原则上每个参赛的省(自治区)、直辖市为一个赛区,各赛区竞赛组委会由省(自治区)、直辖市教育厅、局(教委)、高校代表及电子信息类专家及相关人士组成,负责本赛区的组织领导、协调与宣传工作。

2011年全国大学生电子设计竞赛F P GA预赛课题项目2011年07月15日内容摘要为更好的备战2011年全国大学生电子设计竞赛,经FPGA小组讨论决定,从历年全国电子竞赛的课题项目入手,由FPGA小组成员整理收集历年竞赛课题;采用逐个击破的方法,边学习,边练习,使能够掌握和运用各个不同的模块,将所学到的用到实际。

FPGA小组FPGA小组:唐从学韦稳稳聂先敏邹海军彭剑目录项目一:LED点阵书写显示屏(H题)——2009年第九届全国大学生电子设计竞赛一、任务设计并制作一个基于32×32 点阵LED 模块的书写显示屏,其系统结构如图1 所示。

在控制器的管理下,LED 点阵模块显示屏工作在人眼不易觉察的扫描微亮和人眼可见的显示点亮模式下;当光笔触及LED点阵模块表面时,先由光笔检测触及位置处LED 点的扫描微亮以获取其行列坐标,再依据功能需求决定该坐标处的LED 是否点亮至人眼可见的显示状态(如图1 中光笔接触处的深色LED 点已被点亮),从而在屏上实现“点亮、划亮、反显、整屏擦除、笔画擦除、连写多字、对象拖移”等书写显示功能。

图1 LED 点阵书写显示屏系统结构示意图二、要求1.基本要求(1)在“点亮”功能下,当光笔接触屏上某点LED 时,能即时点亮该点LED,并在控制器上同步显示该点LED 的行列坐标值(左上角定为行列坐标原点)。

(2)在“划亮”功能下,当光笔在屏上快速划过时,能同步点亮划过的各点LED,其速度要求2s内能划过并点亮40 点LED。

(3)在“反显”功能下,能对屏上显示的信息实现反相显示(即:字体笔画处不亮,无笔画处高亮)。

(4)在“整屏擦除”功能下,能实现对屏上所显示信息的整屏擦除。

2.发挥部分(1)在“笔画擦除”功能下,能用光笔擦除屏上所显汉字的笔画。

(2)在“连写多字”功能下,能结合自选的擦除方式,在30s 内在屏上以“划亮”方式逐个写出四个汉字(总笔画数不大于30)且存入机内,写完后再将所存四字在屏上逐个轮流显示。

摘要示波器是使用广泛的测量仪器,传统的模拟示波器在观察周期性、重复频率较高的波形时比较精准,但是在测量不能重复出现的单次信号、持续的非周期信号以及重复频率较低的周期信号时却表现不佳。

数字示波器正是根据上述要求而被提出来的。

目前数字示波器主要有独立仪器、附加仪器及虚拟仪器等工作形式。

本设计是附加仪形式的数字示波器。

本设计以89S52单片机和CPLD为控制核心,配合触发滤波电路、前级信号放大电路、取样保持电路、数据采集电路和后级信号处理电路等外围电路处理模块,完成信号波形数据处理及显示的功能。

本系统遵循智能化、操作方便、测量精准等思想。

可以完成以实时采样和等效采样方式对输入频率在10Hz-10MHz范围内的信号进行采样和处理并在水平和垂直方向分别分档显示的功能。

此系统还可以实现单次触发、波形存储等功能。

关键词数字示波器单片机CPLD X-Y显示方式一、方案论证与比较示波器是使用广泛的测量仪器,是观察和测量信号波形不可缺少的工具。

传统的模拟示波器在观察周期性、重复频率较高的波形时比较精准,但是在测量不能重复出现的单次信号、持续的非周期信号以及重复频率较低的周期信号时却表现不佳。

数字示波器正是根据上述要求而被提出来的。

随着科学技术的不断发展,人们对测量仪器的精度要求越来越高,数字示波器性能也不断取得新的突破。

目前数字示波器主要有独立仪器、附加仪器及虚拟仪器等工作形式。

本设计是附加仪形式的数字示波器。

(一)数据采集数字示波器采样方式包括实时采样、等效采样。

等效采样又分为随机采样和顺序采样。

实时采样对每个采集周期的采样点按时间顺序采取,对这些采样点的数据进行顺序表达就可以再现信号波形。

根据奈奎斯特采样定理采样频率必须至少是被测信号的2倍。

为了避免产生混选现象,目前实时采样DSO的采样频率一般为带宽的4-5倍,同时还必须采用适当的内插算法,否则采样速率还要更高才能达到要求。

随机采样是指每个采样周期采集一定量的样点,经过多个采样周期的样点积累,最终恢复出被测波形。

第一部分电源与信号源类

课题1 简易数控直流电源

课题2 直流稳定电源

课题3 数控直流电流源

课题4 实用信号源的设计和制作

课题5 三相正弦波变频电源

课题6 开关稳压电源

第二类仪器仪表及放大器类

课题1 实用低频功率放大器

课题2 简易电阻、电容和电感测试仪课题3 简易数字频率计

课题4 测量放大器

课题5 数字式工频有效值多用表

课题6 频率特性测试仪

课题7 波形发生器

课题8 高效率音频功率放大器

课题9 电压控制LC振荡器

课题10 宽带放大器

课题11 低频数字式相位测量仪

课题12 简易逻辑分析仪

课题13 正弦信号发生器

课题14 集成运放参数测试仪

课题15 简易频谱分析仪

课题16 音频信号分析仪

课题17 数字示波器

课题18 程控滤波器

第三类数据采集与处理类

课题1 多路数据采集系统

课题2 简易数字存储示波器

课题3 数据采集与传输系统

第四类高频电子线路(无线电)类课题1 简易无线电遥控系统

课题2 调幅广播收音机

课题3 短波调频接收机

课题4 调频收音机

课题5 单工无线呼叫系统

课题6 无线识别装置

第五类控制类

课题1 水温控制系统

课题2 自动往返电动小汽车

课题3 简易智能电动车

课题4 液体点滴速度监控装置

课题5 悬挂运动控制系统

课题6 电动车跷跷板。

简易数字存储示波器

摘要

我们设计制作的简易数字示波器以附加仪器的形式工作。

该仪器以89C52单片机为核心,由前端处理,触发,采集,数据融合处理,波形显示和操作面板等功能模块组成。

在系统的设计中,遵循智能化、操作方便、功能完备等思想。

我们采用CPLD实现控制逻辑,并使该仪器在示波器的XY方式下显示。

为了提高系统的性能和可操作性,我们扩充了触

101

发系统,如可选择通道1、通道2、外部三个触发源,以及自动、正常、单次、三种触发方式,具有边沿和最大幅度的条件触发功能等。

设置了掉电保护、水平/垂直自动设置、波形打印等功能,并制作了供系统使用的线性稳压电源,完成了设计任务。

关键词:数字存储示波器CPLD X-Y显示方式

一、总体方案设计

示波器是用量最多、用途最广的测量仪器之一,是观察和测量电子波形不可缺少的工具。

传统的模拟示波器在观测周期性重复频率较高的波形方面仍然得到普遍使用,但对于不能重复出现的单次信号、持续的非周期信号以及重复频率较低的周期信号则显得无能为力。

数字存储示波器正是基于上述要求而出现的。

目前的数字存储示波器以独立仪器、附加仪器以及虚拟仪器等形式

102

工作。

本设计中的数字存储示波器定位于附加仪器工作模式。

1、设计思想

附加装置模式的数字存储示波器:

●应充分利用模拟示波器的原有功能电路及部件,如使用其

CRT并在XY方式下显示且使之尽量与模拟示波器融为一体,成为附加仪器方式工作的数字存储示波器。

●应具备较完备的数字存储示波器功能、灵活的触发方式,如

智能人机交互、信号存储、分析、处理、测量、显示等。

●应符合传统示波器的使用习惯,并且具有灵活方便的操作、

演示方法。

2.总体设计方案选择

根据题目要求,本系统可选择以下方案实现:

方案一:纯单片机方案。

即系统由单片机、A/D、D/A存储器等组成。

这种方案要求单片机除了完成基本处理分析外,还需要完成信号的采集、存储、显示等控制与变换工作。

这种方案的优点在于系统规模较小,有一定灵活性,但是不适宜于观察高速

103

信号或复杂信号,难以达到题目要求,并且系统的软硬件工作量分配不平衡,难以在4天内发挥各人的全部智慧。

图1-1给出了该系统的总体框图:

图1-1

方案二:FPGA/CPLD方式。

即用FPGA/CPLD完成数字存储示波器的采集、存储、显示等以及A/D、D/A等操作。

这种方案的优点在于系统紧凑,操作方便,尤其适合于对固定信号的观测显示场合;缺点是难以实现复杂功能,尤其是信号分析测量功能。

图1-2给出了该系统的总体框图:

图1-2

104。