makefile 语法

- 格式:doc

- 大小:14.13 KB

- 文档页数:6

Makefile⽂件语法概述本⽂将介绍Makefile种注释、回显、通配符、变量、循环判断、函数注释Makefile中只有单⾏注释,没有多⾏注释,注释以 # 开头。

以下Makefile注释⽚段节选⾃的Makefile# Makefile for installing Lua# See doc/readme.html for installation and customization instructions.# == CHANGE THE SETTINGS BELOW TO SUIT YOUR ENVIRONMENT =======================# Your platform. See PLATS for possible values.PLAT= noneechoing(回显)通常,make在执⾏命令⾏之前会把要执⾏的命令⾏进⾏输出。

我们称之为“回显”,就好像我们输⼊命令执⾏⼀样。

@如果要执⾏的命令⾏以字符“@”开始,则make在执⾏时这个命令就不会被回显。

典型的⽤法是我们在使⽤“echo”命令输出⼀些信息时。

如:@echo 开始编译XXX模块......当make执⾏时,将输出“开始编译XXX模块......”这个信息。

如果在命令⾏之前没有字符“@”,那么,make的输出就是:echo编译XXX模块......编译XXX模块......“-n”或“--just-print”如果使⽤make的命令⾏参数“-n”或“--just-print”,那么make执⾏时只显⽰所要执⾏的命令,但不会真正的去执⾏这些命令。

只有在这种情况下make才会打印出所有make需要执⾏的命令,其中也包括了使⽤“@”字符开始的命令。

这个选项对于我们调试Makefile⾮常有⽤,使⽤这个选项我们可以按执⾏顺序打印出Makefile中所有需要执⾏的命令。

“-s”或“--slient”make参数“-s”或“--slient”则是禁⽌所有执⾏命令的显⽰,就好像所有的命令⾏均使⽤“@”开始⼀样。

makefile正则表达式makefile是一种常用的工具,可以用于自动化构建和管理项目。

在makefile中,正则表达式是一个强大的工具,可以帮助我们更方便地匹配和处理文本内容。

makefile中常用的正则表达式包括:1. ^(起始符):匹配字符串的开头。

2. $(结束符):匹配字符串的结尾。

3. .(点号):匹配除了换行符外的任意一个字符。

4. *(星号):匹配前面的字符出现0个或多个。

5. +(加号):匹配前面的字符出现1个或多个。

6. ?(问号):匹配前面的字符出现0个或1个。

7. [ ](中括号):匹配中括号中任意一个字符。

8. [^ ](中括号取反):匹配不在中括号中的任意一个字符。

9. ( )(圆括号):将括号中的内容视为一个整体,可以和其他正则表达式一起使用。

除了这些常用的正则表达式外,还有一些特殊的符号和语法可以帮助我们更精确地匹配文本内容,比如:1. (反斜杠):转义符,可以将特殊字符转义为普通字符。

2. |(竖线):或运算符,可以匹配多个表达式中的一个。

3. { }(花括号):重复次数符号,可以指定一个字符或表达式的重复次数。

在使用正则表达式时,我们需要注意一些事项,比如:1. 正则表达式是区分大小写的。

2. 正则表达式中的空格和换行符也会被匹配。

3. 正则表达式可能会匹配到我们不需要的内容,因此需要通过进一步筛选和处理来达到我们的目的。

总之,正则表达式在makefile中的应用非常广泛,可以帮助我们更方便地编写自动化构建和管理脚本。

熟练掌握正则表达式的使用方法,可以极大地提高我们的工作效率。

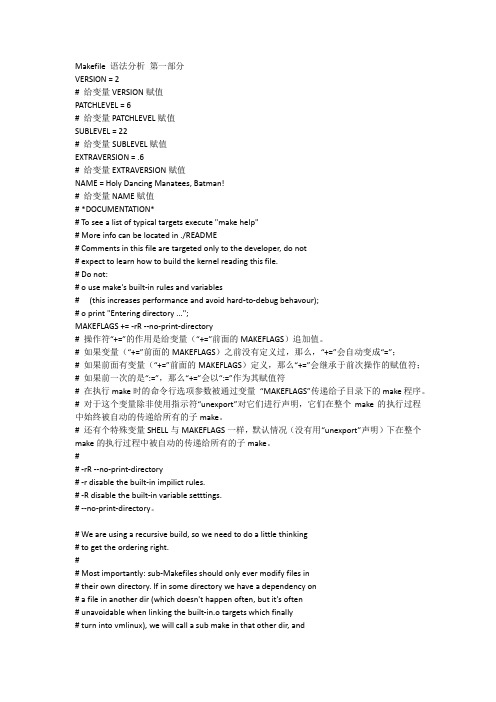

Makefile 语法分析第一部分VERSION = 2# 给变量VERSION赋值PATCHLEVEL = 6# 给变量PATCHLEVEL赋值SUBLEVEL = 22# 给变量SUBLEVEL赋值EXTRAVERSION = .6# 给变量EXTRAVERSION赋值NAME = Holy Dancing Manatees, Batman!# 给变量NAME赋值# *DOCUMENTATION*# To see a list of typical targets execute "make help"# More info can be located in ./README# Comments in this file are targeted only to the developer, do not# expect to learn how to build the kernel reading this file.# Do not:# o use make's built-in rules and variables# (this increases performance and avoid hard-to-debug behavour);# o print "Entering directory ...";MAKEFLAGS += -rR --no-print-directory# 操作符“+=”的作用是给变量(“+=”前面的MAKEFLAGS)追加值。

# 如果变量(“+=”前面的MAKEFLAGS)之前没有定义过,那么,“+=”会自动变成“=”;# 如果前面有变量(“+=”前面的MAKEFLAGS)定义,那么“+=”会继承于前次操作的赋值符;# 如果前一次的是“:=”,那么“+=”会以“:=”作为其赋值符# 在执行make时的命令行选项参数被通过变量“MAKEFLAGS”传递给子目录下的make程序。

makefile文件语法Makefile是一种用于自动化构建过程的工具,它使用一种特定的语法来定义构建规则和依赖关系。

下面是一些Makefile的基本语法规则:1. 目标(Target):目标是指要构建的程序或文件。

它通常以冒号(:)开头,后面跟着一个或多个依赖项(dependencies)。

```makefiletarget: dependenciescommands```2. 依赖项(Dependencies):依赖项是指要构建目标所必需的文件或目标。

在Makefile中,依赖项以空格分隔。

3. 命令(Commands):命令是指在构建目标时执行的命令行指令。

这些命令可以是编译、链接或其他任何必要的操作。

4. 变量(Variables):Makefile允许使用变量来存储值,以便在构建过程中重复使用。

变量以符号开头,后面跟着变量名。

```makefileVAR = value```5. 模式规则(Pattern Rules):模式规则允许根据文件模式匹配来构建目标。

它们使用通配符来匹配文件名,并在匹配的文件上执行相应的命令。

```makefiletargets : patterncommands```6. 条件语句(Conditionals):Makefile支持条件语句,可以根据条件执行不同的命令或规则。

条件使用ifdef、ifndef、ifeq等关键字定义。

7. 注释(Comments):Makefile使用井号()作为注释标记,任何在该符号之后的内容都会被视为注释,并被忽略。

8. 自动变量(Automatic Variables):Makefile提供了一些自动变量,可以在命令中使用,以获取有关目标、依赖项或文件名的信息。

例如,$表示当前目标,$<表示第一个依赖项等。

这些是Makefile的一些基本语法规则,但还有更多高级特性和用法,可以参考Make工具的文档或相关教程进行深入学习。

makefile if用法Makefile 是一种常用的构建工具,用于自动化构建软件项目。

在Makefile 中,if 语句能够根据条件来选择不同的命令或变量赋值。

本文将逐步介绍Makefile 中if 语句的用法,包括条件判断、变量赋值、嵌套使用等方面的内容。

首先,我们需要了解Makefile 中if 语句的基本语法。

if 语句可以写在任何位置,但通常我们将其放在文件的顶部,用于设置全局变量或选择不同的命令。

if 语句的基本结构如下:ifeq (条件,值)# 条件成立时执行的命令或变量赋值else# 条件不成立时执行的命令或变量赋值endif在这个基本结构中,ifeq 为条件判断语句,它用于判断条件是否等于某个值。

若条件成立,则执行if 代码块内的命令或进行变量赋值,否则执行else 代码块内的命令或变量赋值。

endif 表示if 语句的结束。

接下来,我们来看一些具体的示例,以帮助理解if 语句的用法。

1. 条件判断:在Makefile 中,我们可以使用各种条件进行判断。

以下是一些常用的判断方式:- 变量是否为空:ifeq ((VAR),)# VAR 为空时执行的命令或变量赋值else# VAR 不为空时执行的命令或变量赋值endif- 变量是否等于某个值:ifeq ((VAR),某个值)# VAR 等于某个值时执行的命令或变量赋值else# VAR 不等于某个值时执行的命令或变量赋值endif- 多个条件判断:ifeq ((VAR),某个值)# VAR 等于某个值时执行的命令或变量赋值else ifeq ((VAR),另一个值)# VAR 等于另一个值时执行的命令或变量赋值else# VAR 既不等于某个值,也不等于另一个值时执行的命令或变量赋值endif2. 变量赋值:在if 语句中,我们可以根据条件选择不同的变量赋值,使得程序更具有灵活性。

以下示例展示了如何根据条件选择不同的变量赋值:ifeq ((OS),Linux)# OS 等于Linux 时,执行以下变量赋值CC = gccelse# OS 不等于Linux 时,执行以下变量赋值CC = clangendif根据上述示例,当操作系统为Linux 时,CC 的值将被赋为gcc,否则为clang。

makefile中if then写法如何在Makefile 中使用if-then 写法Makefile 是一种软件构建工具,广泛用于管理和构建软件项目。

它使用一系列规则和命令来指导构建过程。

其中,条件语句if-then 是Makefile 中常用的控制语句之一。

在本文中,我们将逐步介绍如何在Makefile 中使用if-then 写法,以及它的用途和常见示例。

一、if-then 写法的基本语法在Makefile 中,if-then 语句的基本语法如下所示:ifeq (条件, 值)#条件为真时执行的命令else#条件为假时执行的命令endif在上述语法中,ifeq 是条件语句的关键字,用于判断一个条件是否为真。

条件是通过与指定的值进行比较来确定的。

若条件为真,则执行ifeq 和else 之间的命令块;若条件为假,则执行else 和endif 之间的命令块。

二、if-then 语句的使用场景if-then 语句在Makefile 中具有广泛的应用场景。

它可以用于实现以下功能:1. 根据不同的条件选择性地执行命令。

2. 根据环境变量的值选择性地执行命令。

3. 根据文件存在与否选择性地执行命令。

4. 根据命令执行结果选择性地执行不同的命令。

下面让我们逐步来看每个使用场景的示例。

三、根据不同的条件选择性地执行命令首先,我们来看一个根据不同的条件选择性地执行命令的示例。

假设我们有一个变量MODE,它的值可以是release 或debug。

根据MODE 的不同,我们可以选择性地执行不同的命令。

makefileMODE := releaseifeq ((MODE), release)# release 模式下执行的命令(info Building release version...)gcc -O3 -o myprogram main.celse# debug 模式下执行的命令(info Building debug version...)gcc -g -o myprogram main.cendif在上述示例中,(info ...) 是一个内置函数,用于在Makefile 执行过程中打印文本消息。

Makefile是一种简单的配置文件,用于描述如何编译和链接源代码文件,以及生成可执行文件的过程。

Makefile通常用于C、C++和其他编程语言的项目中。

Makefile的基本语法格式如下:

target: prerequisites

command

其中,target是要生成的目标文件或目录,prerequisites是生成目标文件所需的源文件或目录,command是执行的命令,用于编译和链接源文件生成目标文件。

例如,以下是一个简单的Makefile,它描述了如何将名为“main.c”的C源代码文件编译成可执行文件“main”:

main: main.o

gcc -o main main.o

main.o: main.c

gcc -o main.o main.c

在这个Makefile中,main是目标文件,main.o是其对应的源文件,gcc -o main main.o是执行的命令,用于将main.c编译成main.o文件,然后链接成可执行文件main。

需要注意的是,Makefile中的命令必须以tab键开头,而不是空格键。

同时,Makefile中还可以使用变量、函数、条件判断等高级语法,用于更灵活地描述编译和链接的过程。

makefile中使用cp命令摘要:1.Makefile 简介2.CP 命令的作用3.Makefile 中CP 命令的语法4.CP 命令的实例应用5.CP 命令的注意事项正文:1.Makefile 简介Makefile 是一种用于自动构建和编译源代码的文本文件,通常用于编写软件项目。

它包含了一系列的规则和指令,用于描述如何编译、链接和构建软件项目。

Makefile 的主要目的是自动化构建过程,以提高开发效率。

2.CP 命令的作用在Makefile 中,CP 命令用于复制文件或目录。

它可以将一个文件或目录从一个位置复制到另一个位置,这对于构建过程中需要用到的资源文件、库文件等非常有用。

3.Makefile 中CP 命令的语法在Makefile 中,CP 命令的语法如下:```cp <source> <destination>```其中,`<source>`是要复制的文件或目录,`<destination>`是目标位置。

4.CP 命令的实例应用例如,假设我们有一个名为`src`的目录,其中包含了名为`main.c`的源代码文件。

现在,我们需要将这个文件复制到名为`build`的目录中,以便进行编译。

可以使用以下Makefile 规则来实现这个需求:```cp src/main.c build/```这条规则表示,将`src`目录下的`main.c`文件复制到`build`目录下。

5.CP 命令的注意事项在使用CP 命令时,需要注意以下几点:- 目标位置必须存在,否则复制操作无法完成。

- 如果要复制的文件或目录不存在,需要确保源位置正确,并检查路径是否正确。

- 在Makefile 中,可以多个CP 命令一起使用,以实现批量复制文件或目录。

总之,在Makefile 中使用CP 命令可以方便地实现文件或目录的复制操作,从而提高构建过程的自动化程度。

Makefile使⽤总结1. Makefile 简介Makefile 是和 make 命令⼀起配合使⽤的.很多⼤型项⽬的编译都是通过 Makefile 来组织的, 如果没有 Makefile, 那很多项⽬中各种库和代码之间的依赖关系不知会多复杂. Makefile的组织流程的能⼒如此之强, 不仅可以⽤来编译项⽬, 还可以⽤来组织我们平时的⼀些⽇常操作. 这个需要⼤家发挥⾃⼰的想象⼒.本篇博客是基于⽽整理的, 有些删减, 追加了⼀些⽰例.⾮常感谢 gunguymadman_cu 提供如此详尽的Makefile介绍, 这正是我⼀直寻找的Makefile中⽂⽂档.1.1 Makefile 主要的 5个部分 (显⽰规则, 隐晦规则, 变量定义, ⽂件指⽰, 注释)Makefile基本格式如下:target ... : prerequisites ...command......其中,target - ⽬标⽂件, 可以是 Object File, 也可以是可执⾏⽂件prerequisites - ⽣成 target 所需要的⽂件或者⽬标command - make需要执⾏的命令 (任意的shell命令), Makefile中的命令必须以 [tab] 开头1. 显⽰规则 :: 说明如何⽣成⼀个或多个⽬标⽂件(包括⽣成的⽂件, ⽂件的依赖⽂件, ⽣成的命令)2. 隐晦规则 :: make的⾃动推导功能所执⾏的规则3. 变量定义 :: Makefile中定义的变量4. ⽂件指⽰ :: Makefile中引⽤其他Makefile; 指定Makefile中有效部分; 定义⼀个多⾏命令5. 注释 :: Makefile只有⾏注释 "#", 如果要使⽤或者输出"#"字符, 需要进⾏转义, "\#"1.2 GNU make 的⼯作⽅式1. 读⼊主Makefile (主Makefile中可以引⽤其他Makefile)2. 读⼊被include的其他Makefile3. 初始化⽂件中的变量4. 推导隐晦规则, 并分析所有规则5. 为所有的⽬标⽂件创建依赖关系链6. 根据依赖关系, 决定哪些⽬标要重新⽣成7. 执⾏⽣成命令2. Makefile 初级语法2.1 Makefile 规则2.1.1 规则语法规则主要有2部分: 依赖关系和⽣成⽬标的⽅法.语法有以下2种:target ... : prerequisites ...command...或者target ... : prerequisites ; commandcommand...*注* command太长, 可以⽤ "\" 作为换⾏符2.1.2 规则中的通配符* :: 表⽰任意⼀个或多个字符:: 表⽰任意⼀个字符[...] :: ex. [abcd] 表⽰a,b,c,d中任意⼀个字符, [^abcd]表⽰除a,b,c,d以外的字符, [0-9]表⽰ 0~9中任意⼀个数字~ :: 表⽰⽤户的home⽬录2.1.3 路径搜索当⼀个Makefile中涉及到⼤量源⽂件时(这些源⽂件和Makefile极有可能不在同⼀个⽬录中),这时, 最好将源⽂件的路径明确在Makefile中, 便于编译时查找. Makefile中有个特殊的变量VPATH就是完成这个功能的.指定了VPATH之后, 如果当前⽬录中没有找到相应⽂件或依赖的⽂件, Makefile 回到VPATH指定的路径中再去查找.. VPATH使⽤⽅法:vpath <directories> :: 当前⽬录中找不到⽂件时, 就从<directories>中搜索vpath <pattern> <directories> :: 符合<pattern>格式的⽂件, 就从<directories>中搜索vpath <pattern> :: 清除符合<pattern>格式的⽂件搜索路径vpath :: 清除所有已经设置好的⽂件路径# ⽰例1 - 当前⽬录中找不到⽂件时, 按顺序从 src⽬录 ../parent-dir⽬录中查找⽂件VPATH src:../parent-dir# ⽰例2 - .h结尾的⽂件都从 ./header ⽬录中查找VPATH %.h ./header# ⽰例3 - 清除⽰例2中设置的规则VPATH %.h# ⽰例4 - 清除所有VPATH的设置VPATH2.2 Makefile 中的变量2.2.1 变量定义 ( = or := )OBJS = programA.o programB.oOBJS-ADD = $(OBJS) programC.o# 或者OBJS := programA.o programB.oOBJS-ADD := $(OBJS) programC.o其中 = 和 := 的区别在于, := 只能使⽤前⾯定义好的变量, = 可以使⽤后⾯定义的变量测试 =# Makefile内容OBJS2 = $(OBJS1) programC.oOBJS1 = programA.o programB.oall:@echo $(OBJS2)# bash中执⾏make, 可以看出虽然 OBJS1 是在 OBJS2 之后定义的, 但在 OBJS2中可以提前使⽤$ makeprogramA.o programB.o programC.o测试 :=# Makefile内容OBJS2 := $(OBJS1) programC.oOBJS1 := programA.o programB.oall:@echo $(OBJS2)# bash中执⾏make, 可以看出 OBJS2 中的 $(OBJS1) 为空$ makeprogramC.o2.2.2 变量替换# Makefile内容SRCS := programA.c programB.c programC.cOBJS := $(SRCS:%.c=%.o)all:@echo "SRCS: " $(SRCS)@echo "OBJS: " $(OBJS)# bash中运⾏make$ makeSRCS: programA.c programB.c programC.cOBJS: programA.o programB.o programC.o2.2.3 变量追加值 +=# Makefile内容SRCS := programA.c programB.c programC.cSRCS += programD.call:@echo "SRCS: " $(SRCS)# bash中运⾏make$ makeSRCS: programA.c programB.c programC.c programD.c2.2.4 变量覆盖 override作⽤是使 Makefile中定义的变量能够覆盖 make 命令参数中指定的变量语法:override <variable> = <value>override <variable> := <value>override <variable> += <value>下⾯通过⼀个例⼦体会 override 的作⽤:# Makefile内容 (没有⽤override)SRCS := programA.c programB.c programC.call:@echo "SRCS: " $(SRCS)# bash中运⾏make$ make SRCS=nothingSRCS: nothing################################################## Makefile内容 (⽤override)override SRCS := programA.c programB.c programC.call:@echo "SRCS: " $(SRCS)# bash中运⾏make$ make SRCS=nothingSRCS: programA.c programB.c programC.c2.2.5 ⽬标变量作⽤是使变量的作⽤域仅限于这个⽬标(target), ⽽不像之前例⼦中定义的变量, 对整个Makefile都有效.语法:<target ...> :: <variable-assignment><target ...> :: override <variable-assignment> (override作⽤参见变量覆盖的介绍)⽰例:# Makefile 内容SRCS := programA.c programB.c programC.ctarget1: TARGET1-SRCS := programD.ctarget1:@echo "SRCS: " $(SRCS)@echo "SRCS: " $(TARGET1-SRCS)target2:@echo "SRCS: " $(SRCS)@echo "SRCS: " $(TARGET1-SRCS)# bash中执⾏make$ make target1SRCS: programA.c programB.c programC.cSRCS: programD.c$ make target2 <-- target2中显⽰不了 $(TARGET1-SRCS)SRCS: programA.c programB.c programC.cSRCS:2.3 Makefile 命令前缀Makefile 中书写shell命令时可以加2种前缀 @ 和 -, 或者不⽤前缀.3种格式的shell命令区别如下:不⽤前缀 :: 输出执⾏的命令以及命令执⾏的结果, 出错的话停⽌执⾏前缀 @ :: 只输出命令执⾏的结果, 出错的话停⽌执⾏前缀 - :: 命令执⾏有错的话, 忽略错误, 继续执⾏⽰例:# Makefile 内容 (不⽤前缀)all:echo"没有前缀"cat this_file_not_existecho"错误之后的命令" <-- 这条命令不会被执⾏# bash中执⾏make$ makeecho"没有前缀" <-- 命令本⾝显⽰出来没有前缀 <-- 命令执⾏结果显⽰出来cat this_file_not_existcat: this_file_not_exist: No such file or directorymake: *** [all] Error 1############################################################ Makefile 内容 (前缀 @)all:@echo "没有前缀"@cat this_file_not_exist@echo "错误之后的命令" <-- 这条命令不会被执⾏# bash中执⾏make$ make没有前缀 <-- 只有命令执⾏的结果, 不显⽰命令本⾝cat: this_file_not_exist: No such file or directorymake: *** [all] Error 1############################################################ Makefile 内容 (前缀 -)all:-echo"没有前缀"-cat this_file_not_exist-echo"错误之后的命令" <-- 这条命令会被执⾏# bash中执⾏make$ makeecho"没有前缀" <-- 命令本⾝显⽰出来没有前缀 <-- 命令执⾏结果显⽰出来cat this_file_not_existcat: this_file_not_exist: No such file or directorymake: [all] Error 1 (ignored)echo"错误之后的命令" <-- 出错之后的命令也会显⽰错误之后的命令 <-- 出错之后的命令也会执⾏2.4 伪⽬标伪⽬标并不是⼀个"⽬标(target)", 不像真正的⽬标那样会⽣成⼀个⽬标⽂件.典型的伪⽬标是 Makefile 中⽤来清理编译过程中中间⽂件的 clean 伪⽬标, ⼀般格式如下: .PHONY: clean <-- 这句没有也⾏, 但是最好加上clean:-rm -f *.o2.5 引⽤其他的 Makefile语法: include <filename> (filename 可以包含通配符和路径)⽰例:# Makefile 内容all:@echo "主 Makefile begin"@make other-all@echo "主 Makefile end"include ./other/Makefile# ./other/Makefile 内容other-all:@echo "other makefile begin"@echo "other makefile end"# bash中执⾏make$ lltotal 20K-rw-r--r-- 1 wangyubin wangyubin 125 Sep 2316:13 Makefile-rw-r--r-- 1 wangyubin wangyubin 11K Sep 2316:15 <-- 这个⽂件不⽤管drwxr-xr-x 2 wangyubin wangyubin 4.0K Sep 2316:11 other$ ll other/total 4.0K-rw-r--r-- 1 wangyubin wangyubin 71 Sep 2316:11 Makefile$ make主 Makefile beginmake[1]: Entering directory `/path/to/test/makefile'other makefile beginother makefile endmake[1]: Leaving directory `/path/to/test/makefile'主 Makefile end2.6 查看C⽂件的依赖关系写 Makefile 的时候, 需要确定每个⽬标的依赖关系.GNU提供⼀个机制可以查看C代码⽂件依赖那些⽂件, 这样我们在写 Makefile ⽬标的时候就不⽤打开C源码来看其依赖那些⽂件了.⽐如, 下⾯命令显⽰内核源码中 virt/kvm/kvm_main.c 中的依赖关系$ cd virt/kvm/$ gcc -MM kvm_main.ckvm_main.o: kvm_main.c iodev.h coalesced_mmio.h async_pf.h <-- 这句就可以加到 Makefile 中作为编译 kvm_main.o 的依赖关系2.7 make 退出码Makefile的退出码有以下3种:0 :: 表⽰成功执⾏1 :: 表⽰make命令出现了错误2 :: 使⽤了 "-q" 选项, 并且make使得⼀些⽬标不需要更新2.8 指定 Makefile,指定特定⽬标默认执⾏ make 命令时, GNU make在当前⽬录下依次搜索下⾯3个⽂件 "GNUmakefile", "makefile", "Makefile",找到对应⽂件之后, 就开始执⾏此⽂件中的第⼀个⽬标(target). 如果找不到这3个⽂件就报错.⾮默认情况下, 可以在 make 命令中指定特定的 Makefile 和特定的⽬标.⽰例:# Makefile⽂件名改为 MyMake, 内容target1:@echo "target [1] begin"@echo "target [1] end"target2:@echo "target [2] begin"@echo "target [2] end"# bash 中执⾏make$ lsMakefile$ mv Makefile MyMake$ lsMyMake$ make <-- 找不到默认的 Makefilemake: *** No targets specified and no makefile found. Stop.$ make -f MyMake <-- 指定特定的Makefiletarget [1] begintarget [1] end$ make -f MyMake target2 <-- 指定特定的⽬标(target)target [2] begintarget [2] end2.9 make 参数介绍make 的参数有很多, 可以通过 make -h 去查看, 下⾯只介绍⼏个我认为⽐较有⽤的.参数含义--debug[=<options>]输出make的调试信息, options 可以是 a, b, v-j --jobs同时运⾏的命令的个数, 也就是多线程执⾏ Makefile-r --no-builtin-rules禁⽌使⽤任何隐含规则-R --no-builtin-variabes禁⽌使⽤任何作⽤于变量上的隐含规则-B --always-make假设所有⽬标都有更新, 即强制重编译2.10 Makefile 隐含规则这⾥只列⼀个和编译C相关的.编译C时,<n>.o 的⽬标会⾃动推导为 <n>.c# Makefile 中main : main.ogcc -o main main.o#会⾃动变为:main : main.ogcc -o main main.omain.o: main.c <-- main.o 这个⽬标是隐含⽣成的gcc -c main.c2.11 隐含规则中的命令变量和命令参数变量2.11.1 命令变量, 书写Makefile可以直接写 shell时⽤这些变量.下⾯只列出⼀些C相关的变量名含义RM rm -fAR arCC ccCXX g++⽰例:# Makefile 内容all:@echo $(RM)@echo $(AR)@echo $(CC)@echo $(CXX)# bash 中执⾏make, 显⽰各个变量的值$ makerm -farccg++2.11.2 命令参数变量变量名含义ARFLAGS AR命令的参数CFLAGS C语⾔编译器的参数CXXFLAGS C++语⾔编译器的参数⽰例: 下⾯以 CFLAGS 为例演⽰# test.c 内容#include <stdio.h>int main(int argc, char *argv[]){printf ("Hello Makefile\n");return 0;}# Makefile 内容test: test.o$(CC) -o test test.o# bash 中⽤make来测试$ lltotal 24K-rw-r--r-- 1 wangyubin wangyubin 69 Sep 2317:31 Makefile-rw-r--r-- 1 wangyubin wangyubin 14K Sep 2319:51 <-- 请忽略这个⽂件-rw-r--r-- 1 wangyubin wangyubin 392 Sep 2317:31 test.c$ makecc -c -o test.o test.ccc -o test test.o <-- 这个是⾃动推导的$ rm -f test test.o$ make CFLAGS=-Wall <-- 命令中加的编译器参数⾃动追加⼊下⾯的编译中了cc -Wall -c -o test.o test.ccc -o test test.o2.12 ⾃动变量Makefile 中很多时候通过⾃动变量来简化书写, 各个⾃动变量的含义如下:⾃动变量含义$@⽬标集合$%当⽬标是函数库⽂件时, 表⽰其中的⽬标⽂件名$<第⼀个依赖⽬标. 如果依赖⽬标是多个, 逐个表⽰依赖⽬标$?⽐⽬标新的依赖⽬标的集合$^所有依赖⽬标的集合, 会去除重复的依赖⽬标$+所有依赖⽬标的集合, 不会去除重复的依赖⽬标$*这个是GNU make特有的, 其它的make不⼀定⽀持3. Makefile ⾼级语法3.1 嵌套Makefile在 Makefile 初级语法中已经提到过引⽤其它 Makefile的⽅法. 这⾥有另⼀种写法, 并且可以向引⽤的其它 Makefile 传递参数.⽰例: (不传递参数, 只是调⽤⼦⽂件夹 other 中的Makefile)# Makefile 内容all:@echo "主 Makefile begin"@cd ./other && make@echo "主 Makefile end"# ./other/Makefile 内容other-all:@echo "other makefile begin"@echo "other makefile end"# bash中执⾏make$ lltotal 28K-rw-r--r-- 1 wangyubin wangyubin 104 Sep 2320:43 Makefile-rw-r--r-- 1 wangyubin wangyubin 17K Sep 2320:44 <-- 这个⽂件不⽤管drwxr-xr-x 2 wangyubin wangyubin 4.0K Sep 2320:42 other$ ll other/total 4.0K-rw-r--r-- 1 wangyubin wangyubin 71 Sep 2316:11 Makefile$ make主 Makefile beginmake[1]: Entering directory `/path/to/test/makefile/other'other makefile beginother makefile endmake[1]: Leaving directory `/path/to/test/makefile/other'主 Makefile end⽰例: (⽤export传递参数)# Makefile 内容export VALUE1 := export.c <-- ⽤了 export, 此变量能够传递到 ./other/Makefile 中VALUE2 := no-export.c <-- 此变量不能传递到 ./other/Makefile 中all:@echo "主 Makefile begin"@cd ./other && make@echo "主 Makefile end"# ./other/Makefile 内容other-all:@echo "other makefile begin"@echo "VALUE1: " $(VALUE1)@echo "VALUE2: " $(VALUE2)@echo "other makefile end"# bash中执⾏make$ make主 Makefile beginmake[1]: Entering directory `/path/to/test/makefile/other'other makefile beginVALUE1: export.c <-- VALUE1 传递成功VALUE2: <-- VALUE2 传递失败other makefile endmake[1]: Leaving directory `/path/to/test/makefile/other'主 Makefile end*补充* export 语法格式如下:export variable = valueexport variable := valueexport variable += value3.2 定义命令包命令包有点像是个函数, 将连续的相同的命令合成⼀条, 减少 Makefile 中的代码量, 便于以后维护.语法:define <command-name>command...endef⽰例:# Makefile 内容define run-hello-makefile@echo -n "Hello"@echo " Makefile!"@echo "这⾥可以执⾏多条 Shell 命令!"endefall:$(run-hello-makefile)# bash 中运⾏make$ makeHello Makefile!这⾥可以执⾏多条 Shell 命令!3.3 条件判断条件判断的关键字主要有 ifeq ifneq ifdef ifndef语法:<conditional-directive><text-if-true>endif# 或者<conditional-directive><text-if-true>else<text-if-false>endif⽰例: ifeq的例⼦, ifneq和ifeq的使⽤⽅法类似, 就是取反# Makefile 内容all:ifeq ("aa", "bb")@echo "equal"else@echo "not equal"endif# bash 中执⾏make$ makenot equal⽰例: ifdef的例⼦, ifndef和ifdef的使⽤⽅法类似, 就是取反# Makefile 内容SRCS := program.call:ifdef SRCS@echo $(SRCS)else@echo "no SRCS"# bash 中执⾏make$ makeprogram.c3.4 Makefile 中的函数Makefile 中⾃带了⼀些函数, 利⽤这些函数可以简化 Makefile 的编写.函数调⽤语法如下:$(<function> <arguments>)# 或者${<function> <arguments>}<function> 是函数名<arguments> 是函数参数3.4.1 字符串函数字符串替换函数: $(subst <from>,<to>,<text>)功能: 把字符串<text> 中的 <from> 替换为 <to>返回: 替换过的字符串# Makefile 内容all:@echo $(subst t,e,maktfilt) <-- 将t替换为e# bash 中执⾏make$ makemakefile模式字符串替换函数: $(patsubst <pattern>,<replacement>,<text>)功能: 查找<text>中的单词(单词以"空格", "tab", "换⾏"来分割) 是否符合 <pattern>, 符合的话, ⽤ <replacement> 替代.返回: 替换过的字符串# Makefile 内容all:@echo $(patsubst %.c,%.o,programA.c programB.c)# bash 中执⾏make$ makeprogramA.o programB.o去空格函数: $(strip <string>)功能: 去掉 <string> 字符串中开头和结尾的空字符返回: 被去掉空格的字符串值# Makefile 内容VAL := " aa bb cc "all:@echo "去除空格前: " $(VAL)@echo "去除空格后: " $(strip $(VAL))# bash 中执⾏make去除空格前: aa bb cc去除空格后: aa bb cc查找字符串函数: $(findstring <find>,<in>)功能: 在字符串 <in> 中查找 <find> 字符串返回: 如果找到, 返回 <find> 字符串, 否则返回空字符串# Makefile 内容VAL := " aa bb cc "all:@echo $(findstring aa,$(VAL))@echo $(findstring ab,$(VAL))# bash 中执⾏make$ makeaa过滤函数: $(filter <pattern...>,<text>)功能: 以 <pattern> 模式过滤字符串 <text>, *保留* 符合模式 <pattern> 的单词, 可以有多个模式返回: 符合模式 <pattern> 的字符串# Makefile 内容all:@echo $(filter %.o %.a,program.c program.o program.a)# bash 中执⾏make$ makeprogram.o program.a反过滤函数: $(filter-out <pattern...>,<text>)功能: 以 <pattern> 模式过滤字符串 <text>, *去除* 符合模式 <pattern> 的单词, 可以有多个模式返回: 不符合模式 <pattern> 的字符串# Makefile 内容all:@echo $(filter-out %.o %.a,program.c program.o program.a)# bash 中执⾏make$ makeprogram.c排序函数: $(sort <list>)功能: 给字符串 <list> 中的单词排序 (升序)返回: 排序后的字符串# Makefile 内容all:@echo $(sort bac abc acb cab)# bash 中执⾏make$ makeabc acb bac cab取单词函数: $(word <n>,<text>)功能: 取字符串 <text> 中的第<n>个单词 (n从1开始)返回: <text> 中的第<n>个单词, 如果<n> ⽐ <text> 中单词个数要⼤, 则返回空字符串# Makefile 内容all:@echo $(word 1,aa bb cc dd)@echo $(word 5,aa bb cc dd)@echo $(word 4,aa bb cc dd)# bash 中执⾏make$ makeaadd取单词串函数: $(wordlist <s>,<e>,<text>)功能: 从字符串<text>中取从<s>开始到<e>的单词串. <s>和<e>是⼀个数字.返回: 从<s>到<e>的字符串# Makefile 内容all:@echo $(wordlist 1,3,aa bb cc dd)@echo $(word 5,6,aa bb cc dd)@echo $(word 2,5,aa bb cc dd)# bash 中执⾏make$ makeaa bb ccbb单词个数统计函数: $(words <text>)功能: 统计字符串 <text> 中单词的个数返回: 单词个数# Makefile 内容all:@echo $(words aa bb cc dd)@echo $(words aabbccdd)@echo $(words )# bash 中执⾏make$ make41⾸单词函数: $(firstword <text>)功能: 取字符串 <text> 中的第⼀个单词返回: 字符串 <text> 中的第⼀个单词# Makefile 内容all:@echo $(firstword aa bb cc dd)@echo $(firstword aabbccdd)@echo $(firstword )# bash 中执⾏make$ makeaaaabbccdd3.4.2 ⽂件名函数取⽬录函数: $(dir <names...>)功能: 从⽂件名序列 <names> 中取出⽬录部分返回: ⽂件名序列 <names> 中的⽬录部分# Makefile 内容all:@echo $(dir /home/a.c ./bb.c ../c.c d.c)# bash 中执⾏make$ make/home/ ./ ../ ./取⽂件函数: $(notdir <names...>)功能: 从⽂件名序列 <names> 中取出⾮⽬录部分返回: ⽂件名序列 <names> 中的⾮⽬录部分# Makefile 内容all:@echo $(notdir /home/a.c ./bb.c ../c.c d.c)# bash 中执⾏make$ makea.c bb.cc.cd.c取后缀函数: $(suffix <names...>)功能: 从⽂件名序列 <names> 中取出各个⽂件名的后缀返回: ⽂件名序列 <names> 中各个⽂件名的后缀, 没有后缀则返回空字符串# Makefile 内容all:@echo $(suffix /home/a.c ./b.o ../c.a d)# bash 中执⾏make$ make.c .o .a取前缀函数: $(basename <names...>)功能: 从⽂件名序列 <names> 中取出各个⽂件名的前缀返回: ⽂件名序列 <names> 中各个⽂件名的前缀, 没有前缀则返回空字符串# Makefile 内容all:@echo $(basename /home/a.c ./b.o ../c.a /home/.d .e)# bash 中执⾏make$ make/home/a ./b ../c /home/加后缀函数: $(addsuffix <suffix>,<names...>)功能: 把后缀 <suffix> 加到 <names> 中的每个单词后⾯返回: 加过后缀的⽂件名序列# Makefile 内容all:@echo $(addsuffix .c,/home/a b ./c.o ../d.c)# bash 中执⾏make$ make/home/a.c b.c ./c.o.c ../d.c.c加前缀函数: $(addprefix <prefix>,<names...>)功能: 把前缀 <prefix> 加到 <names> 中的每个单词前⾯返回: 加过前缀的⽂件名序列# Makefile 内容all:@echo $(addprefix test_,/home/a.c b.c ./d.c)# bash 中执⾏make$ maketest_/home/a.c test_b.c test_./d.c连接函数: $(join <list1>,<list2>)功能: <list2> 中对应的单词加到 <list1> 后⾯返回: 连接后的字符串# Makefile 内容all:@echo $(join a b c d,1234)@echo $(join a b c d,12345)@echo $(join a b c d e,1234)# bash 中执⾏make$ makea1 b2 c3 d4a1 b2 c3 d4 5a1 b2 c3 d4 e3.4.3 foreach语法:$(foreach <var>,<list>,<text>)⽰例:# Makefile 内容targets := a b c dobjects := $(foreach i,$(targets),$(i).o)all:@echo $(targets)@echo $(objects)# bash 中执⾏make$ makea b c da.ob.oc.od.o3.4.4 if这⾥的if是个函数, 和前⾯的条件判断不⼀样, 前⾯的条件判断属于Makefile的关键字语法:$(if <condition>,<then-part>)$(if <condition>,<then-part>,<else-part>)⽰例:# Makefile 内容val := aobjects := $(if $(val),$(val).o,nothing)no-objects := $(if $(no-val),$(val).o,nothing)all:@echo $(objects)@echo $(no-objects)# bash 中执⾏make$ makea.onothing3.4.5 call - 创建新的参数化函数语法:$(call <expression>,<parm1>,<parm2>,<parm3>...)⽰例:# Makefile 内容log = "====debug====" $(1) "====end===="all:@echo $(call log,"正在 Make")# bash 中执⾏make$ make====debug==== 正在 Make ====end====3.4.6 origin - 判断变量的来源语法:$(origin <variable>)返回值有如下类型:类型含义undefined<variable> 没有定义过default<variable> 是个默认的定义, ⽐如 CC 变量environment<variable> 是个环境变量, 并且 make时没有使⽤ -e 参数file<variable> 定义在Makefile中command line<variable> 定义在命令⾏中override<variable> 被 override 重新定义过automatic<variable> 是⾃动化变量⽰例:# Makefile 内容val-in-file := test-fileoverride val-override := test-overrideall:@echo $(origin not-define) # not-define 没有定义@echo $(origin CC) # CC 是Makefile默认定义的变量@echo $(origin PATH) # PATH 是 bash 环境变量@echo $(origin val-in-file) # 此Makefile中定义的变量@echo $(origin val-in-cmd) # 这个变量会加在make的参数中@echo $(origin val-override) # 此Makefile中定义的override变量@echo $(origin @) # ⾃动变量, 具体前⾯的介绍# bash 中执⾏make$ make val-in-cmd=val-cmdundefineddefaultenvironmentfilecommand lineoverrideautomatic3.4.7 shell语法:$(shell <shell command>)它的作⽤就是执⾏⼀个shell命令, 并将shell命令的结果作为函数的返回.作⽤和 `<shell command>` ⼀样, ` 是反引号3.4.8 make 控制函数产⽣⼀个致命错误: $(error <text ...>)功能: 输出错误信息, 停⽌Makefile的运⾏# Makefile 内容all:$(error there is an error!)@echo "这⾥不会执⾏!"# bash 中执⾏make$ makeMakefile:2: *** there is an error!. Stop.输出警告: $(warning <text ...>)功能: 输出警告信息, Makefile继续运⾏# Makefile 内容all:$(warning there is an warning!)@echo "这⾥会执⾏!"# bash 中执⾏make$ makeMakefile:2: there is an warning!这⾥会执⾏!3.5 Makefile中⼀些GNU约定俗成的伪⽬标如果有过在Linux上, 从源码安装软件的经历的话, 就会对 make clean, make install ⽐较熟悉.像 clean, install 这些伪⽬标, ⼴为⼈知, 不⽤解释就⼤家知道是什么意思了.下⾯列举⼀些常⽤的伪⽬标, 如果在⾃⼰项⽬的Makefile合理使⽤这些伪⽬标的话, 可以让我们⾃⼰的Makefile看起来更专业, 呵呵 :)伪⽬标含义all所有⽬标的⽬标,其功能⼀般是编译所有的⽬标clean删除所有被make创建的⽂件install安装已编译好的程序,其实就是把⽬标可执⾏⽂件拷贝到指定的⽬录中去print列出改变过的源⽂件tar把源程序打包备份. 也就是⼀个tar⽂件dist创建⼀个压缩⽂件, ⼀般是把tar⽂件压成Z⽂件. 或是gz⽂件TAGS更新所有的⽬标, 以备完整地重编译使⽤check 或 test⼀般⽤来测试makefile的流程。

makefile的if语句Makefile是用于编译、链接和构建软件的工具,它使用一种特殊的语法来描述编译过程中的依赖关系和命令。

在Makefile中,我们可以使用if语句来进行条件判断,根据不同的条件执行不同的命令。

下面是关于Makefile中if语句的一些例子:1. 判断操作系统类型:```makefileifeq ($(shell uname), Linux)CC = gccelse ifeq ($(shell uname), Darwin)CC = clangelseCC = unknownendif```上述代码通过调用uname命令获取操作系统类型,并根据不同的操作系统类型设置不同的编译器。

2. 判断环境变量是否定义:```makefileifndef JAVA_HOME$(error JAVA_HOME is not set)```上述代码判断JAVA_HOME环境变量是否定义,如果没有定义,则输出错误信息。

3. 判断目标文件是否存在:```makefileifneq ($(wildcard $(TARGET)),)@echo "Target exists"else@echo "Target does not exist"endif```上述代码使用wildcard函数判断目标文件是否存在,并根据结果输出相应的信息。

4. 判断编译选项:```makefileifeq ($(DEBUG), 1)CFLAGS += -gelseCFLAGS += -O2endif上述代码根据DEBUG变量的值设置不同的编译选项,如果DEBUG为1,则添加-g选项,否则添加-O2选项。

5. 判断文件是否更新:```makefileifneq ($(shell find $(SRC_DIR) -name "*.c" -newer $(OBJ_DIR)),)@echo "Source files have been modified"else@echo "Source files have not been modified"endif```上述代码使用find命令判断源文件是否有修改,并根据结果输出相应的信息。

makefile 语法

makefile是一种常用的自动化构建工具,它可以帮助我们将源

代码编译、链接、打包等一系列操作自动化完成。

在软件开发中,makefile 已经成为了不可或缺的工具之一。

本文将介绍 makefile

的语法及其用法,希望能够帮助读者更好地理解和使用 makefile。

一、makefile 的基本语法

makefile 的基本语法包括目标、依赖、命令三个要素。

下面我

们来逐一介绍。

1. 目标

目标是指要生成的文件,也就是 makefile 的最终输出。

目标通常是一个可执行文件、一个库文件或者一个归档文件。

在 makefile 中,目标通常以文件名的形式出现。

例如:

```

app: main.c func.c

```

这里的“app”就是目标。

2. 依赖

依赖是指生成目标所需要的文件或者其他目标。

在 makefile 中,依赖通常以文件名的形式出现。

例如:

```

app: main.c func.c

```

这里的“main.c”和“func.c”就是依赖。

3. 命令

命令是指生成目标所需要执行的命令。

在 makefile 中,命令通常以“TAB”键开头,并且必须与目标或者依赖之间有一个空格。

例如:

```

app: main.c func.c

gcc main.c func.c -o app

```

这里的命令是“gcc main.c func.c -o app”。

二、makefile 的实例

了解了 makefile 的基本语法后,我们来看一个简单的makefile 实例:

```

app: main.c func.c

gcc main.c func.c -o app

```

这个 makefile 的作用是将“main.c”和“func.c”编译成一个可执行文件“app”。

如果我们在命令行中执行“make”命令,make 就会自动根据 makefile 中的规则来生成目标文件“app”。

三、makefile 的高级语法

除了基本语法之外,makefile 还有一些高级语法,如变量、函

数、条件语句等。

下面我们来逐一介绍。

1. 变量

变量是指可以重复使用的值,它可以是一个字符串、一个文件名或者一个目录名等。

在 makefile 中,变量通常以“变量名=变量值”的形式定义。

例如:

```

CC=gcc

```

这里的“CC”就是变量名,而“gcc”就是变量值。

在 makefile 中,我们可以通过“$(变量名)”来引用变量。

例如:

```

app: main.c func.c

$(CC) main.c func.c -o app

```

这里的“$(CC)”就会被替换成“gcc”。

2. 函数

函数是指可以完成特定功能的代码块,它可以接收参数并返回值。

在 makefile 中,函数通常以“$(函数名参数)”的形式调用。

例如: ```

app: main.c func.c

$(call compile,main.c func.c,app)

compile = $(CC) $1 -o $2

```

这里的“compile”就是一个函数名,它接收两个参数“main.c func.c”和“app”。

在函数定义中,我们可以使用“$1”和“$2”来引用函数的参数。

3. 条件语句

条件语句是指根据条件来选择不同的操作。

在 makefile 中,条件语句通常以“ifeq”或“ifneq”开头,并以“endif”结尾。

例如: ```

ifeq ($(DEBUG),yes)

CFLAGS=-g

else

CFLAGS=-O2

endif

```

这个条件语句的意思是,如果变量“DEBUG”的值为“yes”,则将“CFLAGS”变量的值设为“-g”,否则将“CFLAGS”变量的值设为“-O2”。

四、makefile 的常用命令

除了“make”命令之外,makefile 还有一些常用的命令,如“clean”、“install”等。

下面我们来逐一介绍。

1. clean 命令

clean 命令用于删除生成的目标文件和中间文件。

在 makefile

中,我们可以定义一个“clean”目标来实现这个功能。

例如:

```

clean:

rm -f *.o app

```

这个“clean”目标的作用是删除所有的“.o”文件和“app”文件。

2. install 命令

install 命令用于将生成的目标文件安装到指定位置。

在makefile 中,我们可以定义一个“install”目标来实现这个功能。

例如:

```

install:

cp app /usr/local/bin

```

这个“install”目标的作用是将“app”文件复制到

“/usr/local/bin”目录下。

五、总结

本文介绍了 makefile 的基本语法、实例、高级语法和常用命令。

makefile 是一种非常强大的自动化构建工具,它可以帮助我们大大提高软件开发的效率。

希望本文能够帮助读者更好地理解和使用makefile。