fpga DDR_SDRAM IP核的调用

- 格式:docx

- 大小:641.67 KB

- 文档页数:15

网络处理器中的DDRSDRAM控制器的设计与实现的开题报告1.课题背景随着网络技术的不断发展,网络设备的处理能力和稳定性要求越来越高。

网络处理器是一类专用于网络应用的高性能处理器。

网络处理器的核心是其内置的DDR SDRAM控制器。

DDR SDRAM控制器是网络处理器内部的一个重要模块,它完成了在处理器与外部存储器之间的数据传输、存储和读取等功能。

2.研究内容和目标本项目旨在探究基于FPGA的网络处理器中DDR SDRAM控制器的设计与实现方法。

主要研究内容包括:(1)DDR SDRAM控制器的架构和原理(2)DDR SDRAM控制器的时序控制和数据传输(3)FPGA中DDR SDRAM控制器的实现方法(4)性能测试和验证研究目标是实现一个高效的DDR SDRAM控制器,能够满足网络处理器的数据传输要求,并具有较高的性能。

3.研究方法和步骤本项目将采用以下研究方法和步骤:(1)阅读相关文献,了解DDR SDRAM控制器的基本原理和FPGA 中DDR SDRAM控制器的实现方法。

(2)根据DDR SDRAM的时序和数据传输要求,设计DDR SDRAM 控制器的架构和接口。

(3)使用Verilog语言实现DDR SDRAM控制器的模块。

(4)在FPGA上进行验证和性能测试。

(5)对实现的DDR SDRAM控制器进行性能测试和优化,以达到更高的性能。

4.研究意义和预期成果本项目的意义在于探究网络处理器中DDR SDRAM控制器的设计和实现方法,并且实现一个高效的DDR SDRAM控制器。

该控制器可用于各种网络设备中,提高网络设备的运行效率和稳定性。

预期成果包括:(1)DDR SDRAM控制器的设计与实现文档(2)基于 FPGA 的网络处理器中 DDR SDRAM 控制器模块的Verilog 代码(3)DDR SDRAM 控制器在 FPGA 上的验证和性能测试报告(4)论文发表和技术报告5.存在的问题和风险存在的问题:(1)DDR SDRAM控制器的设计和实现需要充分考虑时序和数据传输的要求,因此需要仔细分析和设计。

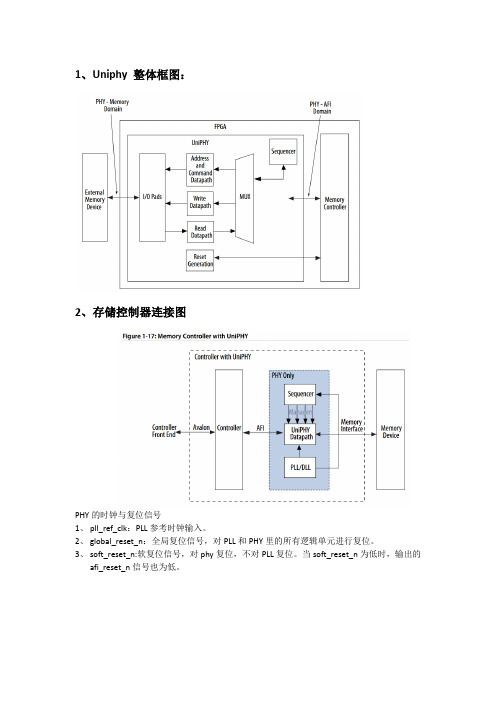

1、Uniphy 整体框图:2、存储控制器连接图PHY的时钟与复位信号1、pll_ref_clk:PLL参考时钟输入。

2、global_reset_n:全局复位信号,对PLL和PHY里的所有逻辑单元进行复位。

3、soft_reset_n:软复位信号,对phy复位,不对PLL复位。

当soft_reset_n为低时,输出的afi_reset_n信号也为低。

3、各个模块间的接口信号3、1控制器与用户接口间使用的Avalon相关信号线:下表是本地接口信号,在altera例化的IP核里,本地用户接口使用的是avalon总线➢Local_addr:指的是用户接口端的地址线,位宽计算方法如下:1)当只使用1pcs 外部存储器时:位宽=bank位宽+行位宽+列位宽-1;2)当使用多片片外存储器时:位宽=芯片位宽+bank位宽+行位宽+列位宽-1;计算位宽时减1 是因为用户数据接口宽度是memory侧数据宽度的两倍(memory侧是在时钟的上升和下降沿都收发数据,而用户侧只在时钟的上升沿收发数据,假如用户读写数据的时钟频率与memory侧的数据频率相同,那么,在时钟上升沿来时,用户侧发送的数据位宽应是memory 侧数据位宽的两倍)。

➢local_be:字节使能信号(用于向控制器写数据时),与memory侧的DM(data mask )信号作用一样,比如,当想使local_data的某8位数据无效,将local_be的对应位置0即可。

➢local_burstbegin:本地突发开始信号,当avalon总线开始突发读写时,将此信号置位‘1’。

(使用条件:本地接口是avalon总线,且memory侧的突发长度大于2)➢local_size:本地突发长度,即连续读或写的local_data个数。

长度不能超过ddr ip核里配置的maximum avalon- mm burst length的长度。

➢local_wdata:本地写数据。

基于FPGA 的DDR2SDRAM 存储器用户接口设计杨斌,段哲民,高峰(西北工业大学电子信息学院,陕西西安710129)摘要:使用功能强大的FPGA 来实现一种DDR2SDRAM 存储器的用户接口。

该用户接口是基于XILINX 公司出产的DDR2SDRAM 的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,可知本设计具有很大的使用前景。

本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速率很高,基本可以满足所有设计需要。

关键词:DDR2SDRAM ;FPGA ;用户接口;DDR2SDRAM 存储控制器中图分类号:TN919.8文献标识码:A文章编号:1674-6236(2012)23-0147-03Design of DDR2SDRAM memory user interface based on FPGAYANG Bin ,DUAN Zhe -min ,GAO Feng(School of Electronic Information ,Northwestern Polytechnical University ,Xi ’an 710129,China )Abstract:The user interface of a DDR2SDRAM memory is implemented by using the powerful FPGA .The user interface is based on DDR2SDRAM memory controller produced by the XILINX company .The company produced such memory controllers with high efficiency and used widely .So that this design has great prospects .Through the simulation of multi -channel high -speed data read and write operations we can know that it can fully meet the timing requirements .Through the synthesis results we can know that the use of logic resources is very little ,run rate is high .It can basically meet all design needs.Key words:DDR2SDRAM ;FPGA ;user interface ;DDR2SDRAM memory controller收稿日期:2012-08-06稿件编号:201208014作者简介:杨斌(1981—),男,陕西佳县人,硕士研究生。

1、Uniphy 整体框图:2、存储控制器连接图PHY的时钟与复位信号1、pll_ref_clk:PLL参考时钟输入。

2、global_reset_n:全局复位信号,对PLL和PHY里的所有逻辑单元进行复位。

3、soft_reset_n:软复位信号,对phy复位,不对PLL复位。

当soft_reset_n为低时,输出的afi_reset_n信号也为低。

3、各个模块间的接口信号3、1控制器与用户接口间使用的Avalon相关信号线:下表是本地接口信号,在altera例化的IP核里,本地用户接口使用的是avalon总线➢Local_addr:指的是用户接口端的地址线,位宽计算方法如下:1)当只使用1pcs 外部存储器时:位宽=bank位宽+行位宽+列位宽-1;2)当使用多片片外存储器时:位宽=芯片位宽+bank位宽+行位宽+列位宽-1;计算位宽时减1 是因为用户数据接口宽度是memory侧数据宽度的两倍(memory 侧是在时钟的上升和下降沿都收发数据,而用户侧只在时钟的上升沿收发数据,假如用户读写数据的时钟频率与memory侧的数据频率相同,那么,在时钟上升沿来时,用户侧发送的数据位宽应是memory侧数据位宽的两倍)。

➢local_be:字节使能信号(用于向控制器写数据时),与memory侧的DM(data mask )信号作用一样,比如,当想使local_data的某8位数据无效,将local_be的对应位置0即可。

➢local_burstbegin:本地突发开始信号,当avalon总线开始突发读写时,将此信号置位‘1’。

(使用条件:本地接口是avalon总线,且memory侧的突发长度大于2)➢local_size:本地突发长度,即连续读或写的local_data个数。

长度不能超过ddr ip 核里配置的maximum avalon- mm burst length的长度。

➢local_wdata:本地写数据。

毕业设计学生姓名:洪雷学号: 09xxxxxxxx 专业:电子科学与技术题目:基于FPGA的DDR2存储器控制器设计指导教师:安国臣(讲师评阅教师:武瑞红(副教授2013年6月毕业设计中文摘要随着消费电类电子产品以及便携式通讯产品向多功能、高性能和低功耗方向的飞快发展,而随之带来的是对大量的数据处理,而产品的系统对其主要的存储设备的要求也越来越高。

目前,DDR2凭着其及其高的数据传输速率和低廉的成本则越来越多的被用到一些高档类的消费类电子和便携式产品中。

对DDR2 SDRAM的控制器处理的设计变得也就非常有必要。

使用FPGA技术设计数字电路,不仅可以简化设计过程,而且还可以减低整个系统的体积和成本,增加系统的可靠性。

本次设计则使用Altear公司的Cyclone V 代器件,经行开发的最小系统。

本次设计使用的是Mircon公司的MT47系列的芯片,借助Altera公司提供的IP 核所自动生成PHY接口。

由于DDR2的读写驱动的要求,多次设计了电压的要求。

本文对DDR2 SDRAM基本结构和原理进行了简单的介绍。

并且阐述基于FIFO和PHY接口的DDR2设计方法。

关键词DDR2 FPGA 存储器控制器 FIFO毕业设计外文摘要Title DDR2 Memory Controller Design based on FPGAAbstractAs consumer electric class electronic products and portable communication products to multi-functional, high performance and low power consumption direction of rapid development, and then brings about a lot of data processing, the product of the system to the main storage device requirements more and more higher. At present, the DDR2 with its and high data transfer rate and low cost are more and more used in some high-end consumer electronics and portable products. Processing of DDR2 SDRAM controller design becomes and is very necessary.Digital circuit design using FPGA technology, not only can simplify the design process, but also can reduce the size and cost of the whole system, increase the reliability of the system. This design USES Altear company Cyclone V generation device, the smallest system development. This design USES the Mircon MT47 series chips, and IP core provided by Altera corporation how can automatically generate the PHY interface. Driven requirements due to DDR2, speaking, reading and writing, and design the voltage requirements for many times.in this paper, the basic structure and principle of DDR2 SDRAM has carried on the simple introduction. And in this paper, the DDR2 design method based on FIFO and PHY interfaceKey Words DDR2 FPGA memory controlle FIFO目录1 绪论 (12 动态随机存储器 (32.1 同步动态随机存储器原理与结构 (32.2 双倍动态随机存储器原理与特点 (32.3 DDR2随机存储器的简介 (43 可编程逻辑器件原理 (73.1 FPGA原理 (73.2 FPGA结构 (73.3 FPGA器件开发的优点 (94 外围电路设计 (114.1芯片的选择和介绍 (114.2 FPGA电源设计 (154.3 FPGA时钟和复位设计 (164.4 FPGA的配置设计 (175 软件设计与仿真 (185.1 FPGA的设计开发流程 (18 5.2 系统设计软件介绍 (195.3 VHDL语言的介绍 (195.4 系统设计 (20结论 (29致谢 (30参考文献 (311 绪论随着大规模、甚大规模的集成电路的设计技术的飞速发展,科技的日益更新,跟随而来的是各种的芯片的弄能不段的变复杂,而同时,数字产品例如掌上电脑、网络设备、音频设备、高清电视等,对高性能的内存的需求也越来越高。

1、Uniphy 整体框图:2、存储控制器连接图PHY的时钟与复位信号1、pll_ref_clk:PLL参考时钟输入。

2、global_reset_n:全局复位信号,对PLL和PHY里的所有逻辑单元进行复位。

3、soft_reset_n:软复位信号,对phy复位,不对PLL复位。

当soft_reset_n为低时,输出的afi_reset_n信号也为低。

3、各个模块间的接口信号3、1控制器与用户接口间使用的Avalon相关信号线:下表是本地接口信号,在altera例化的IP核里,本地用户接口使用的是avalon总线 Local_addr:指的是用户接口端的地址线,位宽计算方法如下:1)当只使用1pcs 外部存储器时:位宽=bank位宽+行位宽+列位宽-1;2)当使用多片片外存储器时:位宽=芯片位宽+bank位宽+行位宽+列位宽-1;计算位宽时减1 是因为用户数据接口宽度是memory侧数据宽度的两倍(memory 侧是在时钟的上升和下降沿都收发数据,而用户侧只在时钟的上升沿收发数据,假如用户读写数据的时钟频率与memory侧的数据频率相同,那么,在时钟上升沿来时,用户侧发送的数据位宽应是memory侧数据位宽的两倍)。

local_be:字节使能信号(用于向控制器写数据时),与memory侧的DM(data mask )信号作用一样,比如,当想使local_data的某8位数据无效,将local_be的对应位置0即可。

local_burstbegin:本地突发开始信号,当avalon总线开始突发读写时,将此信号置位‘1’。

(使用条件:本地接口是avalon总线,且memory侧的突发长度大于2)local_size:本地突发长度,即连续读或写的local_data个数。

长度不能超过ddr ip 核里配置的maximum avalon- mm burst length的长度。

local_wdata:本地写数据。

fpga对ram的操作FPGA对RAM的操作在计算机系统中,RAM(Random Access Memory)是一种常见的存储器件,用于临时存储数据和指令。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以根据需要重新配置其内部电路,使其能够执行各种不同的任务。

本文将详细介绍FPGA对RAM的操作方法和原理。

一、RAM的基本原理RAM是一种随机访问存储器,它具有读取和写入数据的能力。

RAM由多个存储单元组成,每个存储单元可以存储一个或多个位的数据。

每个存储单元都有一个唯一的地址,通过地址可以访问和操作相应的数据。

FPGA中通常使用的是静态RAM(SRAM),它由触发器和多路选择器构成。

每个存储单元由一个触发器组成,触发器的状态决定了存储单元中存储的数据。

通过选择器,可以选择要读取或写入的存储单元。

二、FPGA对RAM的读操作FPGA可以通过以下步骤对RAM进行读操作:1. 输入要读取的存储单元的地址。

2. 通过地址选择器选中要读取的存储单元。

3. 将选中的存储单元的数据读取到FPGA内部的寄存器中。

4. 将寄存器中的数据输出。

读操作的关键是地址选择器的正确配置。

FPGA内部有多个地址选择器,通过配置这些选择器的参数,可以选择要读取的存储单元。

读操作是非破坏性的,即读取数据不会改变存储单元中原有的数据。

三、FPGA对RAM的写操作FPGA可以通过以下步骤对RAM进行写操作:1. 输入要写入的存储单元的地址。

2. 输入要写入的数据。

3. 通过地址选择器选中要写入的存储单元。

4. 将输入的数据写入选中的存储单元。

写操作的关键也是地址选择器的正确配置。

通过配置选择器的参数,可以选择要写入的存储单元。

写操作是破坏性的,即写入数据会覆盖存储单元中原有的数据。

四、FPGA对RAM的初始化在使用FPGA之前,需要对RAM进行初始化,即给RAM中的存储单元赋初值。

初始化可以通过以下步骤实现:1. 设置FPGA的初始化状态。

FPGA和DDR之间的接口标准主要涉及到两个方面:电气特性和协议规范。

以下是一些常见的接口标准和协议:1. 电气特性:- 电压标准: DDR内存通常采用低电压标准,如DDR3和DDR4采用1.35V或1.2V。

FPGA需要确保其IO电压兼容DDR内存的电压标准。

- 时钟频率: DDR接口的时钟频率通常很高,需要确保FPGA 的时钟管理和布线能够满足DDR的要求。

2. 协议规范:- DDR标准:需要遵循DDR SDRAM的标准规范,如DDR3、DDR4等。

这些标准定义了时序、命令和数据传输的方式。

- PHY层: FPGA内部需要包含DDR PHY层,用于处理与DDR 内存之间的电气信号。

PHY层的设计需要符合DDR标准,以确保稳定和高性能的通信。

- 控制器: FPGA还需要一个DDR控制器,负责管理和调度DDR内存的访问。

控制器的设计需要符合DDR标准,并与PHY层协同工作。

3. 总线协议:- AXI(Advanced eXtensible Interface): AXI是一种常见的总线协议,用于连接FPGA内部的不同模块,包括与外部DDR 内存的连接。

AXI提供了一种高性能、可扩展且灵活的总线接口。

4. IP核:- Memory Interface Generator(MIG): FPGA供应商通常提供MIG工具,用于自动生成与DDR内存接口通信所需的PHY和控制器。

这样的IP核有助于简化接口设计和提高开发效率。

5. JEDEC标准: JEDEC定义了DDR SDRAM的标准规范。

确保FPGA 和DDR内存的设计符合JEDEC标准,以确保互操作性。

在开始设计时,建议查阅FPGA供应商的文档、DDR内存的规格书以及相关的标准规范,以确保正确配置接口并满足性能和可靠性的要求。

fpga和ddr的接口标准FPGA和DDR的接口标准引言在现代计算机系统中,为了实现高性能和高速度的数据传输,FPGA(现场可编程门阵列)和DDR(双倍数据率)内存之间的接口标准变得尤为重要。

本文将详细讨论FPGA和DDR接口的标准,并分析它们的特点和优势。

一、FPGA和DDR的概述1. FPGAFPGA是一种可编程逻辑器件,具有灵活的配置能力,可以根据特定应用需求实现复杂的数字逻辑电路。

FPGA通过重新配置逻辑单元和内部互连来更新硬件,因此具有灵活性和可重构性的特点。

在许多计算应用中,FPGA常用来加速特定的任务,并优化整个系统的性能。

2. DDRDDR是一种存储器技术,DDR内存通过一种双倍数据率的传输方式,实现高速的数据读写操作。

DDR内存广泛应用于计算机系统的内存子系统,包括个人电脑、服务器和嵌入式系统。

DDR内存在系统性能和带宽方面提供了显著的改进。

二、FPGA和DDR的接口标准在FPGA和DDR之间建立接口时,需要一种标准来确保他们之间的正常通信和数据传输。

以下是一些常用的FPGA和DDR接口标准:1. DDR3/DDR4 SDRAMDDR3和DDR4 SDRAM是DDR接口中最常用的标准之一。

它们定义了内存模块和控制器之间的物理和电气规范,包括时序、电压和信号级别。

DDR3和DDR4的主要区别在于其时钟频率和吞吐量的提升。

2. LPDDR低功耗DDR(LPDDR)是一种专为移动设备设计的DDR标准。

它具有较低的功耗和较小的封装尺寸,在手机、平板电脑和其他便携式设备中广泛使用。

LPDDR的特点是低功耗和高带宽。

3. HMC高效存储器互连(HMC)是一种新兴的高性能DDR接口标准。

HMC通过堆叠多个存储器芯片来实现高密度和高带宽的存储器系统。

它提供了更快的数据传输速度和更低的延迟,并通过更高的并行通信通道实现更高的带宽。

三、FPGA和DDR接口的优点和特点1. 高带宽和低延迟FPGA和DDR接口的主要优势之一是提供高带宽和低延迟的数据传输。

公司在最新的Spartan6中集成了MCB硬核,它可以支持到DDR3-800,而且对于大多数厂家的存储芯片都支持(Micron、Elpida、Hynix.....)。

对于工程来讲,其MCB硬核优秀的误码校验和偏移时钟校验,以及PLL_ADV工作时的稳定、高精度都大大保证了研发产品的质量。

而对于用户控制接口又是以通用FIFO的读写方式,代替复杂的DDR/DDR2/DDR3读写逻辑。

以SRAM的地址映射方式代替复杂的行列地址选择。

可见spartan6—MCB硬核控制器的诞生是值得大家推崇的。

一,

在工程中添加IP

1、

打开工程,添加新的源文件,

选择版本,这里以3.6为例(尽量选择最新版本),进入Xilinx Memory Interface Generator 界面,单击Next,进入下一步;

3、

选择输出项,输入自定义模块名;

单击Next,注意:如果你是修改一个核而不是第一次生成核,会出现如下对话框,单击Yes,这时会覆盖掉一些文件,因此无论你在接下来的步骤中有没有对核的选项进行修改,最后必须点击Generator;

4、

单击Next,选择Memory Type;

注意到图中有个C1、C3,这是因为Xilinx的MCB有部分是属于硬核,引脚是固定的,分别存在于FPGA芯片的BANK1和BANK3,在代码中将看到很多的信号名是以C1_XXX和C3_XXX开头的,这很容易区分是哪个DDR芯片对应的信号名,注意与后面的端口(Port)混淆;

5、

单击Next,进入DDR2芯片选项模块,先选择存储器,再输入时钟;

这里的Memory Part 选择的是自定义的芯片,单击,输入一个自定义的DDR2芯片名,尽量输入芯片的实名而不是自定义名,这样有利于重复使用,不至于将来使用时不知所云,下面的参数可以在你所选的DDR2芯片DATASHEET中找到,输入参数值,

保存,这样就可以在

找到自定义的存储器了,单击Next;

6、

选择同上,单击Next;

7、

设置端口的一些参数,主要是根据自己板子的实际情况稍微做一些修改即可。

8、

进入端口配置,

(1)选择配置模式,单向与双向的意思是指端口是可读、可写,还是既可读又可写,

将端口配置成一个读一个写,其他不用;

(2)选择存储器的地址映射方式,可根据自己程序设计方便选择,这里默认;9、

Next;接着

10、进入FPGA选项,这里注意系统时钟的方式,根据实际情况选择单端还是差分,这里选择单端。

还有就是要注意下这里debug选项,建议选择”Disable”.

其他默认;

11、Next,同上;

12、Next;

13、选择

Next;

14、Next;

二,

IP中的文件

打开生成的文件夹(一般在工程的ipcore_dir目录下),四个文件夹分别是参数配置、RTL 代码、仿真库和综合脚本。

其中RTL文件夹内的文件是我们主要关注的。

这里的DDR667(建立IP时取的名字)是顶层文件,另外两个分别是“管理时钟”和“管理端口”的描述文件。

打开“管理时钟”的infrastrcture.v,需要注意的几点

(1)

如果MCB的输入时钟是经过IBFG处理的,那么这里的IBFG就需要注释掉,IBFG是全局输入时钟的缓冲,一个工程中有一个即可。

(2)u_pll_adv模块就是Xilinx的PLL核,并没有什么特殊之处,而MCB只用了其中的4个时钟输出,其中一个还是提供给用户逻辑使用,因此完全可以对该PLL的3个时钟输出做自定义,这样可以减少系统所用PLL个数。

对于自定义的PLL输出根据需要最好加上BUFG,

然后将这些时钟添加到模块输出项,经顶层模块输出。

(3) 对于BUFPLL_MCB的详细解释,读者可参见ug382手册.输出文件和对应的关系图如下:

打开作为顶层文件的DDR667,可以看到在IP设置时所选择的参数都在这里了

,如果需要做改动,可以在这里的parameter下修改。

这里的参数有最高的权限,会覆盖所调用模块的默认值。

三, IP的使用

(1)在par文件夹下面有系统默认的UCF(约束文件),默认情况下会使用该UCF文件。

笔者在使用中发现一个奇怪的问题,就是在自己重新定义UCF,且确认所有的管脚都映射正确后,在MAP阶段一直报错,主要是报DQS、UDQS、DQS_N、UDQS_N这四个pin 脚的分布有问题,尝试了很多办法都无效。

最终的解决办法是从工程中移除顶层的DDR2_test.XCO文件(备注:这里DDR2_test是笔者为IP所取的名字),手动添加所有的RTL源文件,编译后顺利通过map,不知道是bug 还是其他的什么原因。

(2) 由于spartan6系统是最新的FPGA,xilinx官方一直在更新ISE软件,FPGA的内核也会有所变动,在期间选型时需要留意DS162文件中不同器件所需要的软件版本。

同时,对于使用-2速度的朋友需要注意下在XCN10024中XILINX队MCB的性能做了一些小小的修正,在内核电压较低(1.14~1.26)的情况下,速度由原来的667降低至625.

(3)由于系统默认是将整个DDR按8bit来重新对地址编码,这样对于X16、X8和X4就需要根据下图经行重新的映射,具体可以参看UG388

(4)在设置FIFO的位宽时,需要注意几个速度问题。

比如DDR3-800,如果器件是X8模式的,那么每个时钟可以触发16bit数据(DDR是双沿触发),假设FIFO是64bit,那么系统时钟至少需要(16/64)*400=100MHZ才能跟上DDR的速度,同理如果是32bit的FIFO,那么至少需要200MHZ的系统时钟,这个在系统规划时需要注意。

另外FIFO最多可以到64级,每一级大小等于位宽。

(5)由于整个IP中定义的参数和系统调用模块比较多,为了防止软件将一些信号优化掉,需要设置Hierarchy为soft

(6)如果系统中不止一个DDR,可以参考XAPP496中相关设计思路。