nRF24LE1 schematic and PCB layout

- 格式:pdf

- 大小:41.05 KB

- 文档页数:3

PCB LAYOUT技术大全2020-06-08 10:24PCB LAYOUT技术大全2020-03-12 11:48PCB LAYOUT技术大全1.原理图常见错误:(1)ERC报告管脚没有接入信号:a. 创建封装时给管脚概念了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c. 创建元件时pin方向反向,必需非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部份调入pcb:生成netlist时没有选择为global。

(4)当利用自己创建的多部份组成的元件时,万万不要利用annotate.中常见错误:(1)网络载入时报告NODE没有找到:a. 原理图中的元件利用了pcb库中没有的封装;b. 原理图中的元件利用了pcb库中名称不一致的封装;c. 原理图中的元件利用了pcb库中pin number不一致的封装。

如三极管:sch中pin number 为e,b,c, 而pcb中为1,2,3。

(2)打印时老是不能打印到一页纸上:a. 创建pcb库时没有在原点;b. 多次移动和旋转了元件,pcb板界外有隐藏的字符。

选择显示所有隐藏的字符,缩小pcb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部份:表示那个网络没有连通,看报告文件,利用选择CONNECTED COPPER查找。

另外提示朋友尽可能利用WIN2000, 减少蓝屏的机遇;多几回导出文件,做成新的DDB 文件,减少文件尺寸和PROTEL僵死的机遇。

若是作较复杂得设计,尽可能不要利用自动布线。

在PCB设计中,布线是完成产品设计的重要步骤,能够说前面的预备工作都是为它而做的,在整个PCB中,以布线的设计进程限定最高,技术最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,能够用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应幸免相邻平行,以避免产生反射干扰。

PCB Layout and SI 问答PCB Layout and SI 问答1.如何实现高速时钟信号的差分布线?在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?专家解答:信号完整性基本上是阻抗匹配的问题。

而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。

解决的方式是靠端接(termination)与调整走线的拓朴。

差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。

平行的方式有两种,一为两条线走在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。

一般以前者side-by-side实现的方式较多。

要用差分布线一定是信号源和接收端也都是差分信号才有意义。

所以对只有一个输出端的时钟信号是无法使用差分布线的2.关于高速差分信号布线.在pcb上靠近平行走高速差分信号线对的时候,在阻抗匹配的情况下,由于两线的相互耦合,会带来很多好处。

但是有观点认为这样会增大信号的衰减,影响传输距离。

是不是这样,为什么?我在一些大公司的评估板上看到高速布线有的尽量靠近且平行,而有的却有意的使两线距离忽远忽近,我不懂那一种效果更好。

我的信号1GHz以上,阻抗为50欧姆。

在用软件计算时,差分线对也是以50欧姆来计算吗?还是以100欧姆来算?接收端差分线对之间可否加一匹配电阻?谢谢!专家解答:会使高频信号能量衰减的原因一是导体本身的电阻特性(conductor loss), 包括集肤效应(skin effect), 另一是介电物质的dielectric loss。

这两种因子在电磁理论分析传输线效应(transmission line effect)时, 可看出他们对信号衰减的影响程度。

cadence allegro pcb layout详细教程

本文为大家带来cadence allegro pcb layout详细教程。

一、用Design Entry CIS(Capture)设计原理图1、创建工程file--》new--》project ;输入工程名称,指定工程放置路径;

2、设置操作环境OpTIons--》Preferencses:颜色:colors/Print

格子:Grid Display

杂项:Miscellaneous

常取默认值

3、配置设计图纸:设定模板:OpTIons--》Design Template:(应用于新图)

设定当前图纸OpTIons--》SchemaTIc Page Properities

4、创建元件及元件库File--》New Library --》选择要添加到的工程

Design --》New Part.(或者在Library处右击选择New Part)

(1)Homogeneous:复合封装元件中(多个元件图组成时)每个元件图都一样(default 适用于标准逻辑)

(2)Heterogeneous:复合封装元件(多个元件图组成时)中使用不一样的元件图(较适用于大元件)

一个封装下多个元件图,以View ext part(previous part)切换视图元器件封装:

(1)place --》line画线,用来画封装外形;

(2)place--》pin放置管脚;放单个或多个;

不同类型的管脚选择的type不同;

5、绘制原理图(1)放置电器。

PCBLayout基础必学知识点以下是PCB布局基础必学的知识点:1. PCB布局软件:了解并熟悉主流的PCB布局软件,如Altium Designer、Cadence Allegro等。

2. 元器件选型:根据设计需求选择合适的元器件,包括尺寸、功耗、特性等。

3. 片上布线规则:根据芯片厂商提供的设计指南,了解片上布线规则,如禁止区域、差分信号布线等。

4. 封装库管理:熟悉PCB封装库的使用,包括添加、编辑、创建封装符号等。

5. 杂散信号管理:合理引导与管理高速信号、地和电源信号的传输路径,避免信号互相干扰。

6. 信号完整性:了解信号完整性的概念和影响因素,如反射、串扰等,设计合理的终端匹配和阻抗控制。

7. 热管理:根据设计需求和元器件的热特性,合理布局散热元件,如散热片、散热孔等。

8. 电源管理:合理布局电源元件,降低电源噪声,确保供电稳定。

9. 关键信号布线:关键信号如时钟、复位等需要特殊布线,如避免交叉、降低噪声等。

10. 纹理规则:根据PCB制造厂商提供的纹理要求,了解合理规划纹理布局。

11. 设计规范:遵循相关的设计规范和标准,如IPC规范,确保设计的可靠性和可制造性。

12. DFM(Design For Manufacturability)设计:考虑到PCB制造过程中的制造要求和限制,设计合理的布局并优化PCB制造流程。

13. EMI(Electromagnetic Interference)控制:合理布局和布线,减小电磁干扰,确保设计的EMI性能。

14. 文件输出:掌握PCB制造文件的输出,如Gerber文件、BOM表格等。

这些是PCB布局基础必学的知识点,掌握这些知识可以帮助设计师设计出高质量和可靠的PCB布局。

手机PCB Layout 与布局经验总结1.sirf reference典型的四,六层板,标准FR4材质2.所有的元件尽可能的表贴3.连接器的放置时,应尽量避免将噪音引入RF电路,尽量使用小的连接器,适当的接地4.所有的RF器件应放置紧密,使连线最短和交叉最小(关键)5.所有的pin有应严格按照reference schematic.所有IC电源脚应当有0.01uf的退藕电容,尽可能的离管脚近,而且必须要经过孔到地和电源层6.预留屏蔽罩空间给RF电路和基带部分,屏蔽罩应当连续的在板子上连接,而且应每隔100mil(最小)过孔到地层7.RF部分电路与数字部分应在板子上分开8.RF的地应直接的接到地层,用专门的过孔和和最短的线9.TCXO晶振和晶振相关电路应与高slew-rate数字信号严格的隔离10.开发板要加适当的测试点11.使用相同的器件,针对开发过程中的版本12.使RTC部分同数字,RF电路部分隔离,RTC电路要尽可能放在地层之上走线RF产品设计过程中降低信号耦合的PCB布线技巧新一轮蓝牙设备、无绳电话和蜂窝电话需求高潮正促使中国电子工程师越来越关注RF电路设计技巧。

RF电路板的设计是最令设计工程师感到头疼的部分,如想一次获得成功,仔细规划和注重细节是必须加以高度重视的两大关键设计规则。

射频(RF)电路板设计由于在理论上还有很多不确定性,因此常被形容为一种“黑色艺术”,但这个观点只有部分正确,RF电路板设计也有许多可以遵循的准则和不应该被忽视的法则。

不过,在实际设计时,真正实用的技巧是当这些准则和法则因各种设计约束而无法准确地实施时如何对它们进行折衷处理。

当然,有许多重要的RF设计课题值得讨论,包括阻抗和阻抗匹配、绝缘层材料和层叠板以及波长和驻波,不过,本文将集中探讨与RF 电路板分区设计有关的各种问题。

今天的蜂窝电话设计以各种方式将所有的东西集成在一起,这对RF 电路板设计来说很不利。

现在业界竞争非常激烈,人人都在找办法用最小的尺寸和最小的成本集成最多的功能。

AIPCBLayout规范在现代的计算机科学和人工智能领域中,数据表示和处理是至关重要的。

有效和规范的数据布局可以提高数据处理的效率和可靠性。

为了满足这一需求,AIPCBLayout规范被提出,旨在提供一种简洁、美观和通用的数据布局格式。

一、背景和目的AIPCBLayout规范是为了解决现有数据布局格式的不足而提出的。

它的主要目的是促进数据交换的一致性和互操作性,以便在各种应用程序和平台之间进行数据共享和交流。

通过定义统一的布局规范,AIPCBLayout旨在简化数据布局的设计和实施过程,并提高数据处理的效率和准确性。

二、核心原则AIPCBLayout规范遵循以下核心原则:1. 明确的数据类型定义:每个数据元素都必须有明确的数据类型定义,以确保数据的一致解释和处理。

常见的数据类型包括整数、浮点数、布尔值和字符串等。

2. 紧凑的布局格式:AIPCBLayout鼓励使用紧凑的布局格式,以减小数据的存储空间和传输开销。

这有助于提高数据处理的效率,并减少通信和存储成本。

3. 可扩展性和可兼容性:AIPCBLayout支持数据布局的可扩展性和可兼容性。

它允许向现有布局中添加新的数据元素,同时保持对旧布局的向后兼容性。

4. 结构化的数据布局:AIPCBLayout规范鼓励使用结构化的数据布局,以提高数据的可读性和可维护性。

结构化布局可以通过使用层次结构、组合和嵌套来组织数据元素。

三、AIPCBLayout格式示例下面是一个示例,展示了使用AIPCBLayout规范定义的数据布局格式:```{"type": "object","properties": {"name": {"type": "string"},"age": {"type": "integer"},"address": {"type": "object","properties": {"street": {"type": "string"},"city": {"type": "string"},"country": {"type": "string"}}}}}```在这个示例中,我们定义了一个包含姓名、年龄和地址的数据布局。

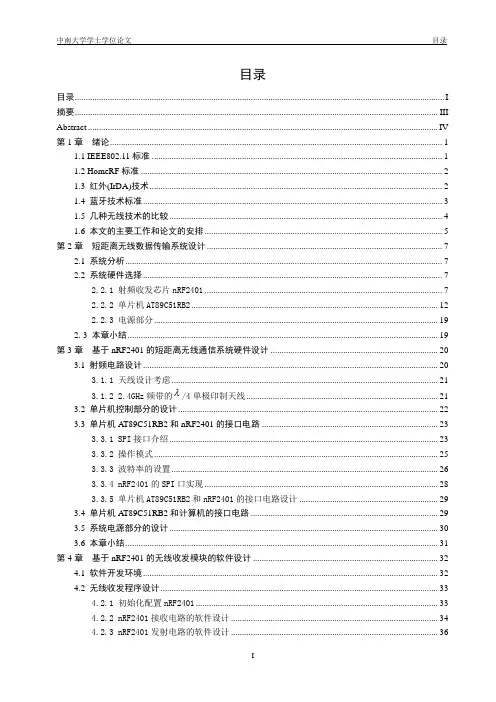

目录目录 (I)摘要 (III)Abstract (IV)第1章绪论 (1)1.1 IEEE802.11标准 (1)1.2 HomeRF标准 (2)1.3 红外(IrDA)技术 (2)1.4 蓝牙技术标准 (3)1.5 几种无线技术的比较 (4)1.6 本文的主要工作和论文的安排 (5)第2章短距离无线数据传输系统设计 (7)2.1 系统分析 (7)2.2 系统硬件选择 (7)2.2.1 射频收发芯片nRF2401 (7)2.2.2 单片机AT89C51RB2 (12)2.2.3 电源部分 (19)2. 3 本章小结 (19)第3章基于nRF2401的短距离无线通信系统硬件设计 (20)3.1 射频电路设计 (20)3.1.1 天线设计考虑 (21)3.1.2 2.4GHz频带的 /4单极印制天线 (21)3.2 单片机控制部分的设计 (22)3.3 单片机A T89C51RB2和nRF2401的接口电路 (23)3.3.1 SPI接口介绍 (23)3.3.2 操作模式 (25)3.3.3 波特率的设置 (26)3.3.4 nRF2401的SPI口实现 (28)3.3.5 单片机AT89C51RB2和nRF2401的接口电路设计 (29)3.4 单片机A T89C51RB2和计算机的接口电路 (29)3.5 系统电源部分的设计 (30)3.6 本章小结 (31)第4章基于nRF2401的无线收发模块的软件设计 (32)4.1 软件开发环境 (32)4.2 无线收发程序设计 (33)4.2.1 初始化配置nRF2401 (33)4.2.2 nRF2401接收电路的软件设计 (34)4.2.3 nRF2401发射电路的软件设计 (36)4.3 PC机串行通信接口模块设计 (37)4.3.1 MSComm控件属性及处理 (37)4.3.2 通信协议 (38)4.4 本章小结 (39)第5章制板与调试 (40)5.1 PCB板制作注意事项 (40)5.1.1 射频电路PCB设计 (40)5.1.2 单片机控制电路及RS232接口电路PCB设计 (41)5.2 印制电路板抗干扰措施 (42)5.3 调试 (43)5.4 本章小结 (43)第6章无线收发模块的改进设计 (44)6.1 USB接口简介 (44)6.2 USB接口模块选择 (44)6.2.1 USB100引脚排列和功能 (45)6.2.2 USB100模块的控制时序图 (46)6.2.3 使用USB100模块的控制电路设计 (47)6.2.4 PC端软件设计 (47)6.3 本章小结 (48)第7章结论与展望 (49)7.1 结论 (49)7.2 展望 (49)参考文献 (51)致谢 (53)翻译 (54)译文 (54)无线局域网安全 (54)摘要随着射频技术、集成电路的发展,越来越多的场合采用了无线传输技术。

All rights reserved.Reproduction in whole or in part is prohibited without the prior written permission of the copyright holder.September 2008nRF24L01+Single Chip 2.4GHz TransceiverProduct Specification v1.0Key Features•Worldwide 2.4GHz ISM band operation •250kbps, 1Mbps and 2Mbps on air data rates•Ultra low power operation•11.3mA TX at 0dBm output power •13.5mA RX at 2Mbps air data rate •900nA in power down •26µA in standby-I•On chip voltage regulator • 1.9 to 3.6V supply range •Enhanced ShockBurst™ •Automatic packet handling•Auto packet transaction handling • 6 data pipe MultiCeiver™•Drop-in compatibility with nRF24L01•On-air compatible in 250kbps and 1Mbps with nRF2401A, nRF2402, nRF24E1 and nRF24E2•Low cost BOM•±60ppm 16MHz crystal •5V tolerant inputs•Compact 20-pin 4x4mm QFN packageApplications•Wireless PC Peripherals•Mouse, keyboards and remotes •3-in-1 desktop bundles•Advanced Media center remote controls •VoIP headsets •Game controllers•Sports watches and sensors•RF remote controls for consumer electronics •Home and commercial automation •Ultra low power sensor networks •Active RFID•Asset tracking systems •ToysnRF24L01+ Product SpecificationLiability disclaimerNordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.All application information is advisory and does not form part of the specification.Limiting valuesStress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the specifications are not implied. Exposure to limiting values for extended periods may affect device reliability.Life support applicationsThese products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA cus-tomers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.Contact detailsVisit www.nordicsemi.no for Nordic Semiconductor sales offices and distributors worldwideMain office:Otto Nielsens vei 127004 TrondheimPhone: +47 72 89 89 00 Fax: +47 72 89 89 89www.nordicsemi.noData sheet statusObjective product specificationThis product specification contains target specifications for product development.Preliminary product specification This product specification contains preliminary data; supplementarydata may be published from Nordic Semiconductor ASA later.Product specification This product specification contains final product specifications. NordicSemiconductor ASA reserves the right to make changes at any time without notice in order to improve design and supply the best possibleproduct.nRF24L01+ Product Specification Writing ConventionsThis product specification follows a set of typographic rules that makes the document consistent and easy to read. The following writing conventions are used:•Commands, bit state conditions, and register names are written in Courier .•Pin names and pin signal conditions are written in Courier bold .•Cross references are underlined and highlighted in blue .Revision HistoryAttention!DateVersion DescriptionSeptember 2008 1.0Observe precaution for handling Electrostatic Sensitive Device. HBM (Human Body Model) > 1Kv MM (Machine Model) > 200VnRF24L01+ Product Specification Contents1Introduction (7)1.1Features (8)1.2Block diagram (9)2Pin Information (10)2.1Pin assignment (10)2.2Pin functions (11)3Absolute maximum ratings (12)4Operating conditions (13)5Electrical specifications (14)5.1Power consumption (14)5.2General RF conditions (15)5.3Transmitter operation (15)5.4Receiver operation (16)5.5Crystal specifications (19)5.6DC characteristics (20)5.7Power on reset (20)6Radio Control (21)6.1Operational Modes (21)6.1.1State diagram (21)6.1.2Power Down Mode (22)6.1.3Standby Modes (22)6.1.4RX mode (23)6.1.5TX mode (23)6.1.6Operational modes configuration (24)6.1.7Timing Information (24)6.2Air data rate (25)6.3RF channel frequency (25)6.4Received Power Detector measurements (25)6.5PA control (26)6.6RX/TX control (26)7Enhanced ShockBurst™ (27)7.1Features (27)7.2Enhanced ShockBurst™ overview (27)7.3Enhanced Shockburst™ packet format (28)7.3.1Preamble (28)7.3.2Address (28)7.3.3Packet control field (28)7.3.4Payload (29)7.3.5CRC (Cyclic Redundancy Check) (30)7.3.6Automatic packet assembly (31)7.3.7Automatic packet disassembly (32)7.4Automatic packet transaction handling (33)7.4.1Auto acknowledgement (33)7.4.2Auto Retransmission (ART) (33)nRF24L01+ Product Specification7.5Enhanced ShockBurst flowcharts (35)7.5.1PTX operation (35)7.5.2PRX operation (37)7.6MultiCeiver™ (39)7.7Enhanced ShockBurst™ timing (42)7.8Enhanced ShockBurst™ transaction diagram (45)7.8.1Single transaction with ACK packet and interrupts (45)7.8.2Single transaction with a lost packet (46)7.8.3Single transaction with a lost ACK packet (46)7.8.4Single transaction with ACK payload packet (47)7.8.5Single transaction with ACK payload packet and lost packet (47)7.8.6Two transactions with ACK payload packet and the firstACK packet lost (48)7.8.7Two transactions where max retransmissions is reached (48)7.9Compatibility with ShockBurst™ (49)7.9.1ShockBurst™ packet format (49)8Data and Control Interface (50)8.1Features (50)8.2Functional description (50)8.3SPI operation (50)8.3.1SPI commands (50)8.3.2SPI timing (52)8.4Data FIFO (55)8.5Interrupt (56)9Register Map (57)9.1Register map table (57)10Peripheral RF Information (64)10.1Antenna output (64)10.2Crystal oscillator (64)10.3nRF24L01+ crystal sharing with an MCU (64)10.3.1Crystal parameters (64)10.3.2Input crystal amplitude and current consumption (64)10.4PCB layout and decoupling guidelines (65)11Application example (66)11.1PCB layout examples (67)12Mechanical specifications (71)13Ordering information (73)13.1Package marking (73)13.2Abbreviations (73)13.3Product options (73)13.3.1RF silicon (73)13.3.2Development tools (73)14Glossary of Terms (74)Appendix A - Enhanced ShockBurst™ - Configuration and communication example (75)Enhanced ShockBurst™ transmitting payload (75)nRF24L01+ Product Specification Enhanced ShockBurst™ receive payload (76)Appendix B - Configuration for compatibility with nRF24XX (77)Appendix C - Constant carrier wave output for testing (78)Configuration (78)nRF24L01+ Product Specification1 IntroductionThe nRF24L01+ is a single chip 2.4GHz transceiver with an embedded baseband protocol engine (Enhanced ShockBurst™), suitable for ultra low power wireless applications. The nRF24L01+ is designed for operation in the world wide ISM frequency band at 2.400 - 2.4835GHz.To design a radio system with the nRF24L01+, you simply need an MCU (microcontroller) and a few exter-nal passive components.You can operate and configure the nRF24L01+ through a Serial Peripheral Interface (SPI). The register map, which is accessible through the SPI, contains all configuration registers in the nRF24L01+ and is accessible in all operation modes of the chip.The embedded baseband protocol engine (Enhanced ShockBurst™) is based on packet communication and supports various modes from manual operation to advanced autonomous protocol operation. Internal FIFOs ensure a smooth data flow between the radio front end and the system’s MCU. Enhanced Shock-Burst™ reduces system cost by handling all the high speed link layer operations.The radio front end uses GFSK modulation. It has user configurable parameters like frequency channel, output power and air data rate. nRF24L01+ supports an air data rate of 250 kbps, 1 Mbps and 2Mbps. The high air data rate combined with two power saving modes make the nRF24L01+ very suitable for ultra low power designs.nRF24L01+ is drop-in compatible with nRF24L01 and on-air compatible with nRF2401A, nRF2402,nRF24E1 and nRF24E2. Intermodulation and wideband blocking values in nRF24L01+ are much improved in comparison to the nRF24L01 and the addition of internal filtering to nRF24L01+ has improved the margins for meeting RF regulatory standards.Internal voltage regulators ensure a high Power Supply Rejection Ratio (PSRR) and a wide power supply range.nRF24L01+ Product Specification 1.1 FeaturesFeatures of the nRF24L01+ include:•RadioX Worldwide 2.4GHz ISM band operationX126 RF channelsX Common RX and TX interfaceX GFSK modulationX250kbps, 1 and 2Mbps air data rateX1MHz non-overlapping channel spacing at 1MbpsX2MHz non-overlapping channel spacing at 2Mbps•TransmitterX Programmable output power: 0, -6, -12 or -18dBmX11.3mA at 0dBm output power•ReceiverX Fast AGC for improved dynamic rangeX Integrated channel filtersX13.5mA at 2MbpsX-82dBm sensitivity at 2MbpsX-85dBm sensitivity at 1MbpsX-94dBm sensitivity at 250kbps•RF SynthesizerX Fully integrated synthesizerX No external loop filer, VCO varactor diode or resonatorX Accepts low cost ±60ppm 16MHz crystal•Enhanced ShockBurst™X1 to 32 bytes dynamic payload lengthX Automatic packet handlingX Auto packet transaction handlingX6 data pipe MultiCeiver™ for 1:6 star networks•Power ManagementX Integrated voltage regulatorX1.9 to 3.6V supply rangeX Idle modes with fast start-up times for advanced power managementX26µA Standby-I mode, 900nA power down modeX Max 1.5ms start-up from power down modeX Max 130us start-up from standby-I mode•Host InterfaceX4-pin hardware SPIX Max 10MbpsX3 separate 32 bytes TX and RX FIFOsX5V tolerant inputs•Compact 20-pin 4x4mm QFN packagenRF24L01+ Product Specification1.2 Block diagram ArrayFigure 1. nRF24L01+ block diagramnRF24L01+ Product Specification 2 Pin Information2.1 Pin assignment ArrayFigure 2. nRF24L01+ pin assignment (top view) for the QFN20 4x4 package2.2 Pin functionsPin Name Pin function Description1CE Digital Input Chip Enable Activates RX or TX mode2CSN Digital Input SPI Chip Select3 SCK Digital Input SPI Clock4MOSI Digital Input SPI Slave Data Input5 MISO Digital Output SPI Slave Data Output, with tri-state option6IRQ Digital Output Maskable interrupt pin. Active low7 VDD Power Power Supply (+1.9V - +3.6V DC)8VSS Power Ground (0V)9XC2Analog Output Crystal Pin 210XC1Analog Input Crystal Pin 111VDD_PA Power Output Power Supply Output (+1.8V) for the internalnRF24L01+ Power Amplifier. Must be connectedto ANT1 and ANT2 as shown in Figure 32.12ANT1RF Antenna interface 113ANT2RF Antenna interface 214VSS Power Ground (0V)15VDD Power Power Supply (+1.9V - +3.6V DC)16IREF Analog Input Reference current. Connect a 22kΩ resistor toground. See Figure 32.17VSS Power Ground (0V)18VDD Power Power Supply (+1.9V - +3.6V DC)19DVDD Power Output Internal digital supply output for de-coupling pur-poses. See Figure 32.20VSS Power Ground (0V)Table 1. nRF24L01+ pin function3 Absolute maximum ratingsNote: Exceeding one or more of the limiting values may cause permanent damage to nRF24L01+.Operating conditions Minimum Maximum Units Supply voltagesVDD-0.3 3.6V VSS0V Input voltageV I-0.3 5.25V Output voltageV O VSS to VDD VSS to VDDTotal Power DissipationP D (T A=85°C)60mW TemperaturesOperating Temperature-40+85°C Storage Temperature-40+125°CTable 2. Absolute maximum ratings4 Operating conditionsSymbol Parameter (condition)Notes Min.Typ.Max.Units VDD Supply voltage 1.9 3.0 3.6V VDD Supply voltage if input signals >3.6V 2.7 3.0 3.3V TEMP Operating Temperature -40+27+85ºCTable 3. Operating conditionsConditions: VDD = +3V, VSS = 0V, T A = - 40ºC to + 85ºC5.1 Power consumptionTable 4. Power consumptionSymbol Parameter (condition)NotesMin.Typ.Max.Units Idle modesI VDD_PD Supply current in power down900nA I VDD_ST1Supply current in standby-I modea a.This current is for a 12pF crystal. Current when using external clock is dependent on signal swing.26µA I VDD_ST2Supply current in standby-II mode 320µA I VDD_SU Average current during 1.5ms crystal oscillator startup 400µATransmitI VDD_TX0Supply current @ 0dBm output powerb b.Antenna load impedance = 15Ω+j88Ω..11.3mA I VDD_TX6Supply current @ -6dBm outputpowerb 9.0mA I VDD_TX12Supply current @ -12dBm outputpowerb 7.5mA I VDD_TX18Supply current @ -18dBm outputpowerb 7.0mA I VDD_AVG Average Supply current @ -6dBm out-put power, ShockBurst™c c.Antenna load impedance = 15Ω+j88Ω. Average data rate 10kbps and max. payload length packets.0.12mA I VDD_TXS Average current during TX settlingd d.Average current consumption during TX startup (130µs) and when changing mode from RX to TX (130µs).8.0mA ReceiveI VDD_2M Supply current 2Mbps 13.5mA I VDD_1M Supply current 1Mbps 13.1mA I VDD_250Supply current 250kbps12.6mA I VDD_RXSAverage current during RX settlinge e.Average current consumption during RX startup (130µs) and when changing mode from TX to RX (130µs).8.9mATable 5. General RF conditions5.3 Transmitter operationTable 6. Transmitter operationSymbol Parameter (condition)NotesMin.Typ.Max.Units f OP Operating frequencya a.Regulatory standards determine the band range you can use.24002525MHz PLL res PLL Programming resolution 1MHz f XTAL Crystal frequency16MHz Δf 250Frequency deviation @ 250kbps ±160kHz Δf 1M Frequency deviation @ 1Mbps ±160kHz Δf 2M Frequency deviation @ 2Mbps±320kHz R GFSKAir Data rateb b.Data rate in each burst on-air2502000kbps F CHANNEL 1M Non-overlapping channel spacing @ 250kbps/1Mbpsc c.The minimum channel spacing is 1MHz1MHz F CHANNEL 2M Non-overlapping channel spacing @ 2Mbpsc 2MHzSymbol Parameter (condition)Notes Min.Typ.Max.Units P RF Maximum Output Powera a.Antenna load impedance = 15Ω+j88Ω0+4dBm P RFC RF Power Control Range 161820dB P RFCR RF Power Accuracy±4dB P BW220dB Bandwidth for Modulated Carrier (2Mbps)18002000kHz P BW120dB Bandwidth for Modulated Carrier (1Mbps)9001000kHz P BW25020dB Bandwidth for Modulated Carrier (250kbps)700800kHz P RF1.21st Adjacent Channel Transmit Power 2MHz (2Mbps)-20dBc P RF2.22nd Adjacent Channel Transmit Power 4MHz (2Mbps)-50dBc P RF1.11st Adjacent Channel Transmit Power 1MHz (1Mbps)-20dBc P RF2.12nd Adjacent Channel Transmit Power 2MHz (1Mbps)-45dBc P RF1.2501st Adjacent Channel Transmit Power 1MHz (250kbps)-30dBc P RF2.2502nd Adjacent Channel Transmit Power 2MHz (250kbps)-45dBc5.4 Receiver operationTable 7. RX SensitivityTable 8. RX selectivity according to ETSI EN 300 440-1 V1.3.1 (2001-09) page 27Datarate Symbol Parameter (condition)Notes Min.Typ.Max.Units RX max Maximum received signal at <0.1% BER 0dBm 2Mbps RX SENS Sensitivity (0.1%BER) @2Mbps -82dBm 1Mbps RX SENS Sensitivity (0.1%BER) @1Mbps -85dBm 250kbpsRX SENSSensitivity (0.1%BER) @250kbps-94dBmDatarate Symbol Parameter (condition)Notes Min.Typ.Max.Units 2Mbps C/I CO C/I Co-channel7dBc C/I 1ST 1st ACS (Adjacent Channel Selectivity) C/I 2MHz 3dBc C/I 2ND 2nd ACS C/I 4MHz -17dBc C/I 3RD 3rd ACS C/I 6MHz-21dBc C/I Nth N th ACS C/I, f i> 12MHz-40dBc C/I Nth N th ACS C/I, f i> 36MHzaa.Narrow Band (In Band) Blocking measurements: 0 to ±40MHz; 1MHz step sizeFor Interferer frequency offsets n*2*fxtal, blocking performance is degraded by approximately 5dB com-pared to adjacent figures.-48dBc 1MbpsC/I CO C/I Co-channel 9dBc C/I 1ST 1st ACS C/I 1MHz 8dBc C/I 2ND 2nd ACS C/I 2MHz -20dBc C/I 3RD 3rd ACS C/I 3MHz -30dBc C/I Nth N th ACS C/I, f i> 6MHz-40dBc C/I Nth N th ACS C/I, f i> 25MHza-47dBc 250kbps C/I CO C/I Co-channel12dBc C/I 1ST 1st ACS C/I 1MHz -12dBc C/I 2ND 2nd ACS C/I 2MHz -33dBc C/I 3RD 3rd ACS C/I 3MHz -38dBc C/I Nth N th ACS C/I, f i> 6MHz-50dBc C/I Nth N th ACS C/I, f i> 25MHza-60dBcTable 9. RX selectivity with nRF24L01+ equal modulation on interfering signal. Measured usingPin = -67dBm for wanted signal.2MbpsC/I CO C/I Co-channel (Modulated carrier)11dBc C/I 1ST 1st ACS C/I 2MHz 4dBc C/I 2ND 2nd ACS C/I 4MHz -18dBc C/I 3RD 3rd ACS C/I 6MHz-24dBc C/I Nth N th ACS C/I, f i > 12MHz -40dBc C/I NthN th ACS C/I, f i > 36MHz a-48dBc 1MbpsC/I CO C/I Co-channel 12dBc C/I 1ST 1st ACS C/I 1MHz 8dBc C/I 2ND 2nd ACS C/I 2MHz -21dBc C/I 3RD 3rd ACS C/I 3MHz -30dBc C/I Nth N th ACS C/I, f i > 6MHz -40dBc C/I NthN th ACS C/I, f i > 25MHz a -50dBc 250kbpsC/I CO C/I Co-channel 7dBc C/I 1ST 1st ACS C/I 1MHz -12dBc C/I 2ND 2nd ACS C/I 2MHz -34dBc C/I 3RD 3rd ACS C/I 3MHz -39dBc C/I Nth N th ACS C/I, f i >6MHz -50dBc C/I NthN th ACS C/I, f i >25MHza -60dBca.Narrow Band (In Band) Blocking measurements: 0 to ±40MHz; 1MHz step sizeWide Band Blocking measurements: 30MHz to 2000MHz; 10MHz step size 2000MHz to 2399MHz; 3MHz step size 2484MHz to 3000MHz; 3MHz step size 3GHz to 12.75GHz; 25MHz step sizeWanted signal for wideband blocking measurements: -67dBm in 1Mbps and 2Mbps mode -77dBm in 250kbps modeFor Interferer frequency offsets n*2*fxtal, blocking performance are degraded by approximately 5dB compared to adjacent figures.If the wanted signal is 3dB or more above the sensitivity level then, the carrier/interferer ratio is indepen-dent of the wanted signal level for a given frequency offset.Note: Wanted signal level at Pin = -64 dBm. Two interferers with equal input power are used. Theinterferer closest in frequency is unmodulated, the other interferer is modulated equal with the wanted signal. The input power of interferers where the sensitivity equals BER = 0.1% is pre-sented. Table 10. RX intermodulation test performed according to Bluetooth Specification version 2.02Mbps P_IM(6Input power of IM interferers at 6 and 12MHz offset from wanted signal-42dBmP_IM(8)Input power of IM interferers at 8 and 16MHz offset from wanted signal-38dBmP_IM(10)Input power of IM interferers at 10 and 20MHz offset from wanted signal-37dBm1Mbps P_IM(3)Input power of IM interferers at 3 and 6MHz offset from wanted signal-36dBmP_IM(4)Input power of IM interferers at 4 and 8MHz offset from wanted signal-36dBmP_IM(5)Input power of IM interferers at 5 and 10MHz offset from wanted signal-36dBm250kbps P_IM(3)Input power of IM interferers at 3 and 6MHz offset from wanted signal-36dBmP_IM(4)Input power of IM interferers at 4 and 8MHz offset from wanted signal-36dBmP_IM(5)Input power of IM interferers at 5 and 10MHz offset from wanted signal-36dBm5.5 Crystal specificationsTable 11. Crystal specificationsThe crystal oscillator startup time is proportional to the crystal equivalent inductance. The trend in crystal design is to reduce the physical outline. An effect of a small outline is an increase in equivalent serialinductance Ls, which gives a longer startup time. The maximum crystal oscillator startup time, Tpd2stby = 1.5 ms, is set using a crystal with equivalent serial inductance of maximum 30mH. An application specific worst case startup time can be calculated as :Tpd2stby= Ls/30mH *1.5ms if Ls exceeds 30mH.Note: In some crystal datasheets Ls is called L1 or Lm and Cs is called C1 or Cm.Figure 3. Equivalent crystal componentsSymbol Parameter (condition)NotesMin.Typ.Max.Units Fxo Crystal Frequency 16MHz ΔF Tolerancea ba. Frequency accuracy including; tolerance at 25ºC , temperature drift, aging and crystal loading.b. Frequency regulations in certain regions set tighter requirements for frequency tolerance (For example, Japan and South Korea specify max. +/- 50ppm).±60ppm C 0Equivalent parallel capacitance 1.57.0pF Ls Equivalent serial inductance cc.Startup time from power down to standby mode is dependant on the Ls parameter. See Table 16. on page 24 for details.30mH C L Load capacitance81216pF ESREquivalent Series Resistance100ΩCoCs LsESR5.6 DC characteristicsTable 12. Digital input pinTable 13. Digital output pin5.7 Power on resetTable 14. Power on resetSymbol Parameter (condition)NotesMin.Typ.Max.Units V IH HIGH level input voltage 0.7VDD 5.25aa.If the input signal >3.6V, the VDD of the nRF24L01+ must be between 2.7V and 3.3V (3.0V±10%)V V ILLOW level input voltageVSS0.3VDD V SymbolParameter (condition)NotesMin.Typ.Max.Units V OH HIGH level output voltage (I OH =-0.25mA)VDD -0.3VDD V V OLLOW level output voltage (I OL =0.25mA)0.3VSymbol Parameter (condition)NotesMin.Typ.Max.Units T PUP Power ramp up time a a.From 0V to 1.9V.100ms T PORPower on resetbb.Measured from when the VDD reaches 1.9V to when the reset finishes.1100ms6 Radio ControlThis chapter describes the nRF24L01+ radio transceiver’s operating modes and the parameters used to control the radio.The nRF24L01+ has a built-in state machine that controls the transitions between the chip’s operating modes. The state machine takes input from user defined register values and internal signals.6.1 Operational ModesYou can configure the nRF24L01+ in power down, standby, RX or TX mode. This section describes these modes in detail.6.1.1 State diagramThe state diagram in Figure 4. shows the operating modes and how they function. There are three types of distinct states highlighted in the state diagram:•Recommended operating mode: is a recommended state used during normal operation.•Possible operating mode: is a possible operating state, but is not used during normal operation.•Transition state: is a time limited state used during start up of the oscillator and settling of the PLL. When the VDD reaches 1.9V or higher nRF24L01+ enters the Power on reset state where it remains in reset until entering the Power Down mode..Figure 4. Radio control state diagram6.1.2 Power Down ModeIn power down mode nRF24L01+ is disabled using minimal current consumption. All register values avail-able are maintained and the SPI is kept active, enabling change of configuration and the uploading/down-loading of data registers. For start up times see Table 16. on page 24. Power down mode is entered by setting the PWR_UP bit in the CONFIG register low.6.1.3 Standby Modes6.1.3.1 Standby-I modeBy setting the PWR_UP bit in the CONFIG register to 1, the device enters standby-I mode. Standby-I mode is used to minimize average current consumption while maintaining short start up times. In this mode only part of the crystal oscillator is active. Change to active modes only happens if CE is set high and when CE is set low, the nRF24L01 returns to standby-I mode from both the TX and RX modes.6.1.3.2 Standby-II modeIn standby-II mode extra clock buffers are active and more current is used compared to standby-I mode. nRF24L01+ enters standby-II mode if CE is held high on a PTX device with an empty TX FIFO. If a new packet is uploaded to the TX FIFO, the PLL immediately starts and the packet is transmitted after the nor-mal PLL settling delay (130µs).Register values are maintained and the SPI can be activated during both standby modes. For start up times see Table 16. on page 24.6.1.4 RX modeThe RX mode is an active mode where the nRF24L01+ radio is used as a receiver. To enter this mode, the nRF24L01+ must have the PWR_UP bit, PRIM_RX bit and the CE pin set high.In RX mode the receiver demodulates the signals from the RF channel, constantly presenting the demodu-lated data to the baseband protocol engine. The baseband protocol engine constantly searches for a valid packet. If a valid packet is found (by a matching address and a valid CRC) the payload of the packet is pre-sented in a vacant slot in the RX FIFOs. If the RX FIFOs are full, the received packet is discarded.The nRF24L01+ remains in RX mode until the MCU configures it to standby-I mode or power down mode. However, if the automatic protocol features (Enhanced ShockBurst™) in the baseband protocol engine are enabled, the nRF24L01+ can enter other modes in order to execute the protocol.In RX mode a Received Power Detector (RPD) signal is available. The RPD is a signal that is set high when a RF signal higher than -64 dBm is detected inside the receiving frequency channel. The internal RPD signal is filtered before presented to the RPD register. The RF signal must be present for at least 40µs before the RPD is set high. How to use the RPD is described in Section 6.4 on page 25.6.1.5 TX modeThe TX mode is an active mode for transmitting packets. To enter this mode, the nRF24L01+ must have the PWR_UP bit set high, PRIM_RX bit set low, a payload in the TX FIFO and a high pulse on the CE for more than 10µs.The nRF24L01+ stays in TX mode until it finishes transmitting a packet. If CE = 0, nRF24L01+ returns to standby-I mode. If CE = 1, the status of the TX FIFO determines the next action. If the TX FIFO is not empty the nRF24L01+ remains in TX mode and transmits the next packet. If the TX FIFO is empty the nRF24L01+ goes into standby-II mode. The nRF24L01+ transmitter PLL operates in open loop when in TX mode. It is important never to keep the nRF24L01+ in TX mode for more than 4ms at a time. If the Enhanced ShockBurst™ features are enabled, nRF24L01+ is never in TX mode longer than 4ms.6.1.6 Operational modes configurationThe following table (Table 15.) describes how to configure the operational modes.Table 15. nRF24L01+ main modes6.1.7 Timing InformationThe timing information in this section relates to the transitions between modes and the timing for the CE pin. The transition from TX mode to RX mode or vice versa is the same as the transition from the standby modes to TX mode or RX mode (max. 130µs), as described in Table 16.Table 16. Operational timing of nRF24L01+For nRF24L01+ to go from power down mode to TX or RX mode it must first pass through stand-by mode. There must be a delay of Tpd2stby (see Table 16.) after the nRF24L01+ leaves power down mode before the CE is set high.Note: If VDD is turned off the register value is lost and you must configure nRF24L01+ before enter-ing the TX or RX modes. ModePWR_UP register PRIM_RX register CE input pin FIFO state RX mode111-TX mode101Data in TX FIFOs. Will empty all levels in TX FIFOs a .a.If CE is held high all TX FIFOs are emptied and all necessary ACK and possible retransmits are car-ried out. The transmission continues as long as the TX FIFO is refilled. If the TX FIFO is empty whenthe CE is still high, nRF24L01+ enters standby-II mode. In this mode the transmission of a packet isstarted as soon as the CSN is set high after an upload (UL) of a packet to TX FIFO.TX mode10Minimum 10µs high pulse Data in TX FIFOs.Will empty one level in TX FIFOs b .b.This operating mode pulses the CE high for at least 10µs. This allows one packet to be transmitted.This is the normal operating mode. After the packet is transmitted, the nRF24L01+ enters standby-Imode.Standby-II101TX FIFO empty.Standby-I1-0No ongoing packet transmission.Power Down 0---Name nRF24L01+Notes Max.ments Tpd2stby Power Down Î Standby mode 150µsWith external clock a a.See Table 11. on page 19 for crystal specifications.1.5msExternal crystal, Ls < 30mH 3msExternal crystal, Ls = 60mH 4.5msExternal crystal, Ls = 90mH Tstby2a Standby modes Î TX/RX mode130µs Thce Minimum CE high10µs Tpece2csn Delay from CE positive edge to CSNlow 4µs。

射频pcb layout 设计规则-概述说明以及解释1.引言1.1 概述概述部分主要介绍了射频PCB布局设计规则这篇长文的背景和主要内容。

在现代电子设备中,无线通信技术得到了广泛的应用与发展。

射频电路作为其中的一个重要组成部分,对于无线通信的性能起到关键影响。

而射频PCB布局设计正是为了优化射频电路的性能而提出的一种设计规则。

射频PCB布局设计规则是针对射频电路在PCB板上的布局位置、布线方式以及各器件之间的互连关系等方面制定的一系列规范和原则。

通过合理的布局设计,可以减小射频电路中的信号传输损耗、最大限度地降低噪声干扰和回波等问题,从而提高射频电路的工作效率和可靠性。

本文将重点介绍射频PCB布局设计中的一些重要规则,包括组件布置、信号走线、地平面和分离布局等方面。

具体而言,我们将深入探讨射频器件的布局位置选择、射频信号走线的规则以及如何设计地平面和分离布局来最大程度地减小电磁干扰和回波。

通过详细的说明和实例示范,读者将能够更加深入地理解射频PCB布局设计规则的重要性和应用价值。

同时,本文还将展望未来射频PCB布局设计的发展方向,以期为射频电路设计提供更加详尽和准确的指导。

在本文的后续内容中,我们将逐一介绍这些规则并给出相应的设计建议,希望读者能够从中受益并应用到自己的实际工作中。

1.2 文章结构:本文将分为以下几个部分进行阐述射频PCB布局设计规则。

首先,引言部分将概述本文主要内容,并介绍文章结构。

接着,正文部分将详细探讨射频PCB布局设计的重要性,包括其对系统性能和电磁兼容性的影响。

同时,本节还将介绍射频PCB布局设计的一般原则和技巧,以帮助读者理解和应用这些规则。

最后,在结论部分,我们将对全文进行总结,并展望未来射频PCB布局设计的发展趋势。

通过本文的阐述,读者将能够深入了解射频PCB布局设计的重要性,掌握射频电路布局的基本原则和规则。

这些知识将有助于读者在实际设计中更好地应用射频技术,提高系统的性能和可靠性。

All rights reserved.Reproduction in whole or in part is prohibited without the prior written permission of the copyright holder.September 2008nRF24L01+Single Chip 2.4GHz TransceiverProduct Specification v1.0Key Features•Worldwide 2.4GHz ISM band operation •250kbps, 1Mbps and 2Mbps on air data rates•Ultra low power operation•11.3mA TX at 0dBm output power •13.5mA RX at 2Mbps air data rate •900nA in power down •26µA in standby-I•On chip voltage regulator • 1.9 to 3.6V supply range •Enhanced ShockBurst™ •Automatic packet handling•Auto packet transaction handling • 6 data pipe MultiCeiver™•Drop-in compatibility with nRF24L01•On-air compatible in 250kbps and 1Mbps with nRF2401A, nRF2402, nRF24E1 and nRF24E2•Low cost BOM•±60ppm 16MHz crystal •5V tolerant inputs•Compact 20-pin 4x4mm QFN packageApplications•Wireless PC Peripherals•Mouse, keyboards and remotes •3-in-1 desktop bundles•Advanced Media center remote controls •VoIP headsets •Game controllers•Sports watches and sensors•RF remote controls for consumer electronics •Home and commercial automation •Ultra low power sensor networks •Active RFID•Asset tracking systems •ToysnRF24L01+ Product SpecificationLiability disclaimerNordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.All application information is advisory and does not form part of the specification.Limiting valuesStress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the specifications are not implied. Exposure to limiting values for extended periods may affect device reliability.Life support applicationsThese products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA cus-tomers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.Contact detailsVisit www.nordicsemi.no for Nordic Semiconductor sales offices and distributors worldwideMain office:Otto Nielsens vei 127004 TrondheimPhone: +47 72 89 89 00 Fax: +47 72 89 89 89www.nordicsemi.noData sheet statusObjective product specificationThis product specification contains target specifications for product development.Preliminary product specification This product specification contains preliminary data; supplementarydata may be published from Nordic Semiconductor ASA later.Product specification This product specification contains final product specifications. NordicSemiconductor ASA reserves the right to make changes at any time without notice in order to improve design and supply the best possibleproduct.nRF24L01+ Product Specification Writing ConventionsThis product specification follows a set of typographic rules that makes the document consistent and easy to read. The following writing conventions are used:•Commands, bit state conditions, and register names are written in Courier .•Pin names and pin signal conditions are written in Courier bold .•Cross references are underlined and highlighted in blue .Revision HistoryAttention!DateVersion DescriptionSeptember 2008 1.0Observe precaution for handling Electrostatic Sensitive Device. HBM (Human Body Model) > 1Kv MM (Machine Model) > 200VnRF24L01+ Product Specification Contents1Introduction (7)1.1Features (8)1.2Block diagram (9)2Pin Information (10)2.1Pin assignment (10)2.2Pin functions (11)3Absolute maximum ratings (12)4Operating conditions (13)5Electrical specifications (14)5.1Power consumption (14)5.2General RF conditions (15)5.3Transmitter operation (15)5.4Receiver operation (16)5.5Crystal specifications (19)5.6DC characteristics (20)5.7Power on reset (20)6Radio Control (21)6.1Operational Modes (21)6.1.1State diagram (21)6.1.2Power Down Mode (22)6.1.3Standby Modes (22)6.1.4RX mode (23)6.1.5TX mode (23)6.1.6Operational modes configuration (24)6.1.7Timing Information (24)6.2Air data rate (25)6.3RF channel frequency (25)6.4Received Power Detector measurements (25)6.5PA control (26)6.6RX/TX control (26)7Enhanced ShockBurst™ (27)7.1Features (27)7.2Enhanced ShockBurst™ overview (27)7.3Enhanced Shockburst™ packet format (28)7.3.1Preamble (28)7.3.2Address (28)7.3.3Packet control field (28)7.3.4Payload (29)7.3.5CRC (Cyclic Redundancy Check) (30)7.3.6Automatic packet assembly (31)7.3.7Automatic packet disassembly (32)7.4Automatic packet transaction handling (33)7.4.1Auto acknowledgement (33)7.4.2Auto Retransmission (ART) (33)nRF24L01+ Product Specification7.5Enhanced ShockBurst flowcharts (35)7.5.1PTX operation (35)7.5.2PRX operation (37)7.6MultiCeiver™ (39)7.7Enhanced ShockBurst™ timing (42)7.8Enhanced ShockBurst™ transaction diagram (45)7.8.1Single transaction with ACK packet and interrupts (45)7.8.2Single transaction with a lost packet (46)7.8.3Single transaction with a lost ACK packet (46)7.8.4Single transaction with ACK payload packet (47)7.8.5Single transaction with ACK payload packet and lost packet (47)7.8.6Two transactions with ACK payload packet and the firstACK packet lost (48)7.8.7Two transactions where max retransmissions is reached (48)7.9Compatibility with ShockBurst™ (49)7.9.1ShockBurst™ packet format (49)8Data and Control Interface (50)8.1Features (50)8.2Functional description (50)8.3SPI operation (50)8.3.1SPI commands (50)8.3.2SPI timing (52)8.4Data FIFO (55)8.5Interrupt (56)9Register Map (57)9.1Register map table (57)10Peripheral RF Information (64)10.1Antenna output (64)10.2Crystal oscillator (64)10.3nRF24L01+ crystal sharing with an MCU (64)10.3.1Crystal parameters (64)10.3.2Input crystal amplitude and current consumption (64)10.4PCB layout and decoupling guidelines (65)11Application example (66)11.1PCB layout examples (67)12Mechanical specifications (71)13Ordering information (73)13.1Package marking (73)13.2Abbreviations (73)13.3Product options (73)13.3.1RF silicon (73)13.3.2Development tools (73)14Glossary of Terms (74)Appendix A - Enhanced ShockBurst™ - Configuration and communication example (75)Enhanced ShockBurst™ transmitting payload (75)nRF24L01+ Product Specification Enhanced ShockBurst™ receive payload (76)Appendix B - Configuration for compatibility with nRF24XX (77)Appendix C - Constant carrier wave output for testing (78)Configuration (78)nRF24L01+ Product Specification1 IntroductionThe nRF24L01+ is a single chip 2.4GHz transceiver with an embedded baseband protocol engine (Enhanced ShockBurst™), suitable for ultra low power wireless applications. The nRF24L01+ is designed for operation in the world wide ISM frequency band at 2.400 - 2.4835GHz.To design a radio system with the nRF24L01+, you simply need an MCU (microcontroller) and a few exter-nal passive components.You can operate and configure the nRF24L01+ through a Serial Peripheral Interface (SPI). The register map, which is accessible through the SPI, contains all configuration registers in the nRF24L01+ and is accessible in all operation modes of the chip.The embedded baseband protocol engine (Enhanced ShockBurst™) is based on packet communication and supports various modes from manual operation to advanced autonomous protocol operation. Internal FIFOs ensure a smooth data flow between the radio front end and the system’s MCU. Enhanced Shock-Burst™ reduces system cost by handling all the high speed link layer operations.The radio front end uses GFSK modulation. It has user configurable parameters like frequency channel, output power and air data rate. nRF24L01+ supports an air data rate of 250 kbps, 1 Mbps and 2Mbps. The high air data rate combined with two power saving modes make the nRF24L01+ very suitable for ultra low power designs.nRF24L01+ is drop-in compatible with nRF24L01 and on-air compatible with nRF2401A, nRF2402,nRF24E1 and nRF24E2. Intermodulation and wideband blocking values in nRF24L01+ are much improved in comparison to the nRF24L01 and the addition of internal filtering to nRF24L01+ has improved the margins for meeting RF regulatory standards.Internal voltage regulators ensure a high Power Supply Rejection Ratio (PSRR) and a wide power supply range.nRF24L01+ Product Specification 1.1 FeaturesFeatures of the nRF24L01+ include:•RadioX Worldwide 2.4GHz ISM band operationX126 RF channelsX Common RX and TX interfaceX GFSK modulationX250kbps, 1 and 2Mbps air data rateX1MHz non-overlapping channel spacing at 1MbpsX2MHz non-overlapping channel spacing at 2Mbps•TransmitterX Programmable output power: 0, -6, -12 or -18dBmX11.3mA at 0dBm output power•ReceiverX Fast AGC for improved dynamic rangeX Integrated channel filtersX13.5mA at 2MbpsX-82dBm sensitivity at 2MbpsX-85dBm sensitivity at 1MbpsX-94dBm sensitivity at 250kbps•RF SynthesizerX Fully integrated synthesizerX No external loop filer, VCO varactor diode or resonatorX Accepts low cost ±60ppm 16MHz crystal•Enhanced ShockBurst™X1 to 32 bytes dynamic payload lengthX Automatic packet handlingX Auto packet transaction handlingX6 data pipe MultiCeiver™ for 1:6 star networks•Power ManagementX Integrated voltage regulatorX1.9 to 3.6V supply rangeX Idle modes with fast start-up times for advanced power managementX26µA Standby-I mode, 900nA power down modeX Max 1.5ms start-up from power down modeX Max 130us start-up from standby-I mode•Host InterfaceX4-pin hardware SPIX Max 10MbpsX3 separate 32 bytes TX and RX FIFOsX5V tolerant inputs•Compact 20-pin 4x4mm QFN packagenRF24L01+ Product Specification1.2 Block diagram ArrayFigure 1. nRF24L01+ block diagramnRF24L01+ Product Specification 2 Pin Information2.1 Pin assignment ArrayFigure 2. nRF24L01+ pin assignment (top view) for the QFN20 4x4 package2.2 Pin functionsPin Name Pin function Description1CE Digital Input Chip Enable Activates RX or TX mode2CSN Digital Input SPI Chip Select3 SCK Digital Input SPI Clock4MOSI Digital Input SPI Slave Data Input5 MISO Digital Output SPI Slave Data Output, with tri-state option6IRQ Digital Output Maskable interrupt pin. Active low7 VDD Power Power Supply (+1.9V - +3.6V DC)8VSS Power Ground (0V)9XC2Analog Output Crystal Pin 210XC1Analog Input Crystal Pin 111VDD_PA Power Output Power Supply Output (+1.8V) for the internalnRF24L01+ Power Amplifier. Must be connectedto ANT1 and ANT2 as shown in Figure 32.12ANT1RF Antenna interface 113ANT2RF Antenna interface 214VSS Power Ground (0V)15VDD Power Power Supply (+1.9V - +3.6V DC)16IREF Analog Input Reference current. Connect a 22kΩ resistor toground. See Figure 32.17VSS Power Ground (0V)18VDD Power Power Supply (+1.9V - +3.6V DC)19DVDD Power Output Internal digital supply output for de-coupling pur-poses. See Figure 32.20VSS Power Ground (0V)Table 1. nRF24L01+ pin function3 Absolute maximum ratingsNote: Exceeding one or more of the limiting values may cause permanent damage to nRF24L01+.Operating conditions Minimum Maximum Units Supply voltagesVDD-0.3 3.6V VSS0V Input voltageV I-0.3 5.25V Output voltageV O VSS to VDD VSS to VDDTotal Power DissipationP D (T A=85°C)60mW TemperaturesOperating Temperature-40+85°C Storage Temperature-40+125°CTable 2. Absolute maximum ratings4 Operating conditionsSymbol Parameter (condition)Notes Min.Typ.Max.Units VDD Supply voltage 1.9 3.0 3.6V VDD Supply voltage if input signals >3.6V 2.7 3.0 3.3V TEMP Operating Temperature -40+27+85ºCTable 3. Operating conditionsConditions: VDD = +3V, VSS = 0V, T A = - 40ºC to + 85ºC5.1 Power consumptionTable 4. Power consumptionSymbol Parameter (condition)NotesMin.Typ.Max.Units Idle modesI VDD_PD Supply current in power down900nA I VDD_ST1Supply current in standby-I modea a.This current is for a 12pF crystal. Current when using external clock is dependent on signal swing.26µA I VDD_ST2Supply current in standby-II mode 320µA I VDD_SU Average current during 1.5ms crystal oscillator startup 400µATransmitI VDD_TX0Supply current @ 0dBm output powerb b.Antenna load impedance = 15Ω+j88Ω..11.3mA I VDD_TX6Supply current @ -6dBm outputpowerb 9.0mA I VDD_TX12Supply current @ -12dBm outputpowerb 7.5mA I VDD_TX18Supply current @ -18dBm outputpowerb 7.0mA I VDD_AVG Average Supply current @ -6dBm out-put power, ShockBurst™c c.Antenna load impedance = 15Ω+j88Ω. Average data rate 10kbps and max. payload length packets.0.12mA I VDD_TXS Average current during TX settlingd d.Average current consumption during TX startup (130µs) and when changing mode from RX to TX (130µs).8.0mA ReceiveI VDD_2M Supply current 2Mbps 13.5mA I VDD_1M Supply current 1Mbps 13.1mA I VDD_250Supply current 250kbps12.6mA I VDD_RXSAverage current during RX settlinge e.Average current consumption during RX startup (130µs) and when changing mode from TX to RX (130µs).8.9mATable 5. General RF conditions5.3 Transmitter operationTable 6. Transmitter operationSymbol Parameter (condition)NotesMin.Typ.Max.Units f OP Operating frequencya a.Regulatory standards determine the band range you can use.24002525MHz PLL res PLL Programming resolution 1MHz f XTAL Crystal frequency16MHz Δf 250Frequency deviation @ 250kbps ±160kHz Δf 1M Frequency deviation @ 1Mbps ±160kHz Δf 2M Frequency deviation @ 2Mbps±320kHz R GFSKAir Data rateb b.Data rate in each burst on-air2502000kbps F CHANNEL 1M Non-overlapping channel spacing @ 250kbps/1Mbpsc c.The minimum channel spacing is 1MHz1MHz F CHANNEL 2M Non-overlapping channel spacing @ 2Mbpsc 2MHzSymbol Parameter (condition)Notes Min.Typ.Max.Units P RF Maximum Output Powera a.Antenna load impedance = 15Ω+j88Ω0+4dBm P RFC RF Power Control Range 161820dB P RFCR RF Power Accuracy±4dB P BW220dB Bandwidth for Modulated Carrier (2Mbps)18002000kHz P BW120dB Bandwidth for Modulated Carrier (1Mbps)9001000kHz P BW25020dB Bandwidth for Modulated Carrier (250kbps)700800kHz P RF1.21st Adjacent Channel Transmit Power 2MHz (2Mbps)-20dBc P RF2.22nd Adjacent Channel Transmit Power 4MHz (2Mbps)-50dBc P RF1.11st Adjacent Channel Transmit Power 1MHz (1Mbps)-20dBc P RF2.12nd Adjacent Channel Transmit Power 2MHz (1Mbps)-45dBc P RF1.2501st Adjacent Channel Transmit Power 1MHz (250kbps)-30dBc P RF2.2502nd Adjacent Channel Transmit Power 2MHz (250kbps)-45dBc5.4 Receiver operationTable 7. RX SensitivityTable 8. RX selectivity according to ETSI EN 300 440-1 V1.3.1 (2001-09) page 27Datarate Symbol Parameter (condition)Notes Min.Typ.Max.Units RX max Maximum received signal at <0.1% BER 0dBm 2Mbps RX SENS Sensitivity (0.1%BER) @2Mbps -82dBm 1Mbps RX SENS Sensitivity (0.1%BER) @1Mbps -85dBm 250kbpsRX SENSSensitivity (0.1%BER) @250kbps-94dBmDatarate Symbol Parameter (condition)Notes Min.Typ.Max.Units 2Mbps C/I CO C/I Co-channel7dBc C/I 1ST 1st ACS (Adjacent Channel Selectivity) C/I 2MHz 3dBc C/I 2ND 2nd ACS C/I 4MHz -17dBc C/I 3RD 3rd ACS C/I 6MHz-21dBc C/I Nth N th ACS C/I, f i> 12MHz-40dBc C/I Nth N th ACS C/I, f i> 36MHzaa.Narrow Band (In Band) Blocking measurements: 0 to ±40MHz; 1MHz step sizeFor Interferer frequency offsets n*2*fxtal, blocking performance is degraded by approximately 5dB com-pared to adjacent figures.-48dBc 1MbpsC/I CO C/I Co-channel 9dBc C/I 1ST 1st ACS C/I 1MHz 8dBc C/I 2ND 2nd ACS C/I 2MHz -20dBc C/I 3RD 3rd ACS C/I 3MHz -30dBc C/I Nth N th ACS C/I, f i> 6MHz-40dBc C/I Nth N th ACS C/I, f i> 25MHza-47dBc 250kbps C/I CO C/I Co-channel12dBc C/I 1ST 1st ACS C/I 1MHz -12dBc C/I 2ND 2nd ACS C/I 2MHz -33dBc C/I 3RD 3rd ACS C/I 3MHz -38dBc C/I Nth N th ACS C/I, f i> 6MHz-50dBc C/I Nth N th ACS C/I, f i> 25MHza-60dBcTable 9. RX selectivity with nRF24L01+ equal modulation on interfering signal. Measured usingPin = -67dBm for wanted signal.2MbpsC/I CO C/I Co-channel (Modulated carrier)11dBc C/I 1ST 1st ACS C/I 2MHz 4dBc C/I 2ND 2nd ACS C/I 4MHz -18dBc C/I 3RD 3rd ACS C/I 6MHz-24dBc C/I Nth N th ACS C/I, f i > 12MHz -40dBc C/I NthN th ACS C/I, f i > 36MHz a-48dBc 1MbpsC/I CO C/I Co-channel 12dBc C/I 1ST 1st ACS C/I 1MHz 8dBc C/I 2ND 2nd ACS C/I 2MHz -21dBc C/I 3RD 3rd ACS C/I 3MHz -30dBc C/I Nth N th ACS C/I, f i > 6MHz -40dBc C/I NthN th ACS C/I, f i > 25MHz a -50dBc 250kbpsC/I CO C/I Co-channel 7dBc C/I 1ST 1st ACS C/I 1MHz -12dBc C/I 2ND 2nd ACS C/I 2MHz -34dBc C/I 3RD 3rd ACS C/I 3MHz -39dBc C/I Nth N th ACS C/I, f i >6MHz -50dBc C/I NthN th ACS C/I, f i >25MHza -60dBca.Narrow Band (In Band) Blocking measurements: 0 to ±40MHz; 1MHz step sizeWide Band Blocking measurements: 30MHz to 2000MHz; 10MHz step size 2000MHz to 2399MHz; 3MHz step size 2484MHz to 3000MHz; 3MHz step size 3GHz to 12.75GHz; 25MHz step sizeWanted signal for wideband blocking measurements: -67dBm in 1Mbps and 2Mbps mode -77dBm in 250kbps modeFor Interferer frequency offsets n*2*fxtal, blocking performance are degraded by approximately 5dB compared to adjacent figures.If the wanted signal is 3dB or more above the sensitivity level then, the carrier/interferer ratio is indepen-dent of the wanted signal level for a given frequency offset.Note: Wanted signal level at Pin = -64 dBm. Two interferers with equal input power are used. Theinterferer closest in frequency is unmodulated, the other interferer is modulated equal with the wanted signal. The input power of interferers where the sensitivity equals BER = 0.1% is pre-sented. Table 10. RX intermodulation test performed according to Bluetooth Specification version 2.02Mbps P_IM(6Input power of IM interferers at 6 and 12MHz offset from wanted signal-42dBmP_IM(8)Input power of IM interferers at 8 and 16MHz offset from wanted signal-38dBmP_IM(10)Input power of IM interferers at 10 and 20MHz offset from wanted signal-37dBm1Mbps P_IM(3)Input power of IM interferers at 3 and 6MHz offset from wanted signal-36dBmP_IM(4)Input power of IM interferers at 4 and 8MHz offset from wanted signal-36dBmP_IM(5)Input power of IM interferers at 5 and 10MHz offset from wanted signal-36dBm250kbps P_IM(3)Input power of IM interferers at 3 and 6MHz offset from wanted signal-36dBmP_IM(4)Input power of IM interferers at 4 and 8MHz offset from wanted signal-36dBmP_IM(5)Input power of IM interferers at 5 and 10MHz offset from wanted signal-36dBm5.5 Crystal specificationsTable 11. Crystal specificationsThe crystal oscillator startup time is proportional to the crystal equivalent inductance. The trend in crystal design is to reduce the physical outline. An effect of a small outline is an increase in equivalent serialinductance Ls, which gives a longer startup time. The maximum crystal oscillator startup time, Tpd2stby = 1.5 ms, is set using a crystal with equivalent serial inductance of maximum 30mH. An application specific worst case startup time can be calculated as :Tpd2stby= Ls/30mH *1.5ms if Ls exceeds 30mH.Note: In some crystal datasheets Ls is called L1 or Lm and Cs is called C1 or Cm.Figure 3. Equivalent crystal componentsSymbol Parameter (condition)NotesMin.Typ.Max.Units Fxo Crystal Frequency 16MHz ΔF Tolerancea ba. Frequency accuracy including; tolerance at 25ºC , temperature drift, aging and crystal loading.b. Frequency regulations in certain regions set tighter requirements for frequency tolerance (For example, Japan and South Korea specify max. +/- 50ppm).±60ppm C 0Equivalent parallel capacitance 1.57.0pF Ls Equivalent serial inductance cc.Startup time from power down to standby mode is dependant on the Ls parameter. See Table 16. on page 24 for details.30mH C L Load capacitance81216pF ESREquivalent Series Resistance100ΩCoCs LsESR5.6 DC characteristicsTable 12. Digital input pinTable 13. Digital output pin5.7 Power on resetTable 14. Power on resetSymbol Parameter (condition)NotesMin.Typ.Max.Units V IH HIGH level input voltage 0.7VDD 5.25aa.If the input signal >3.6V, the VDD of the nRF24L01+ must be between 2.7V and 3.3V (3.0V±10%)V V ILLOW level input voltageVSS0.3VDD V SymbolParameter (condition)NotesMin.Typ.Max.Units V OH HIGH level output voltage (I OH =-0.25mA)VDD -0.3VDD V V OLLOW level output voltage (I OL =0.25mA)0.3VSymbol Parameter (condition)NotesMin.Typ.Max.Units T PUP Power ramp up time a a.From 0V to 1.9V.100ms T PORPower on resetbb.Measured from when the VDD reaches 1.9V to when the reset finishes.1100ms6 Radio ControlThis chapter describes the nRF24L01+ radio transceiver’s operating modes and the parameters used to control the radio.The nRF24L01+ has a built-in state machine that controls the transitions between the chip’s operating modes. The state machine takes input from user defined register values and internal signals.6.1 Operational ModesYou can configure the nRF24L01+ in power down, standby, RX or TX mode. This section describes these modes in detail.6.1.1 State diagramThe state diagram in Figure 4. shows the operating modes and how they function. There are three types of distinct states highlighted in the state diagram:•Recommended operating mode: is a recommended state used during normal operation.•Possible operating mode: is a possible operating state, but is not used during normal operation.•Transition state: is a time limited state used during start up of the oscillator and settling of the PLL. When the VDD reaches 1.9V or higher nRF24L01+ enters the Power on reset state where it remains in reset until entering the Power Down mode..Figure 4. Radio control state diagram6.1.2 Power Down ModeIn power down mode nRF24L01+ is disabled using minimal current consumption. All register values avail-able are maintained and the SPI is kept active, enabling change of configuration and the uploading/down-loading of data registers. For start up times see Table 16. on page 24. Power down mode is entered by setting the PWR_UP bit in the CONFIG register low.6.1.3 Standby Modes6.1.3.1 Standby-I modeBy setting the PWR_UP bit in the CONFIG register to 1, the device enters standby-I mode. Standby-I mode is used to minimize average current consumption while maintaining short start up times. In this mode only part of the crystal oscillator is active. Change to active modes only happens if CE is set high and when CE is set low, the nRF24L01 returns to standby-I mode from both the TX and RX modes.6.1.3.2 Standby-II modeIn standby-II mode extra clock buffers are active and more current is used compared to standby-I mode. nRF24L01+ enters standby-II mode if CE is held high on a PTX device with an empty TX FIFO. If a new packet is uploaded to the TX FIFO, the PLL immediately starts and the packet is transmitted after the nor-mal PLL settling delay (130µs).Register values are maintained and the SPI can be activated during both standby modes. For start up times see Table 16. on page 24.6.1.4 RX modeThe RX mode is an active mode where the nRF24L01+ radio is used as a receiver. To enter this mode, the nRF24L01+ must have the PWR_UP bit, PRIM_RX bit and the CE pin set high.In RX mode the receiver demodulates the signals from the RF channel, constantly presenting the demodu-lated data to the baseband protocol engine. The baseband protocol engine constantly searches for a valid packet. If a valid packet is found (by a matching address and a valid CRC) the payload of the packet is pre-sented in a vacant slot in the RX FIFOs. If the RX FIFOs are full, the received packet is discarded.The nRF24L01+ remains in RX mode until the MCU configures it to standby-I mode or power down mode. However, if the automatic protocol features (Enhanced ShockBurst™) in the baseband protocol engine are enabled, the nRF24L01+ can enter other modes in order to execute the protocol.In RX mode a Received Power Detector (RPD) signal is available. The RPD is a signal that is set high when a RF signal higher than -64 dBm is detected inside the receiving frequency channel. The internal RPD signal is filtered before presented to the RPD register. The RF signal must be present for at least 40µs before the RPD is set high. How to use the RPD is described in Section 6.4 on page 25.6.1.5 TX modeThe TX mode is an active mode for transmitting packets. To enter this mode, the nRF24L01+ must have the PWR_UP bit set high, PRIM_RX bit set low, a payload in the TX FIFO and a high pulse on the CE for more than 10µs.The nRF24L01+ stays in TX mode until it finishes transmitting a packet. If CE = 0, nRF24L01+ returns to standby-I mode. If CE = 1, the status of the TX FIFO determines the next action. If the TX FIFO is not empty the nRF24L01+ remains in TX mode and transmits the next packet. If the TX FIFO is empty the nRF24L01+ goes into standby-II mode. The nRF24L01+ transmitter PLL operates in open loop when in TX mode. It is important never to keep the nRF24L01+ in TX mode for more than 4ms at a time. If the Enhanced ShockBurst™ features are enabled, nRF24L01+ is never in TX mode longer than 4ms.6.1.6 Operational modes configurationThe following table (Table 15.) describes how to configure the operational modes.Table 15. nRF24L01+ main modes6.1.7 Timing InformationThe timing information in this section relates to the transitions between modes and the timing for the CE pin. The transition from TX mode to RX mode or vice versa is the same as the transition from the standby modes to TX mode or RX mode (max. 130µs), as described in Table 16.Table 16. Operational timing of nRF24L01+For nRF24L01+ to go from power down mode to TX or RX mode it must first pass through stand-by mode. There must be a delay of Tpd2stby (see Table 16.) after the nRF24L01+ leaves power down mode before the CE is set high.Note: If VDD is turned off the register value is lost and you must configure nRF24L01+ before enter-ing the TX or RX modes. ModePWR_UP register PRIM_RX register CE input pin FIFO state RX mode111-TX mode101Data in TX FIFOs. Will empty all levels in TX FIFOs a .a.If CE is held high all TX FIFOs are emptied and all necessary ACK and possible retransmits are car-ried out. The transmission continues as long as the TX FIFO is refilled. If the TX FIFO is empty whenthe CE is still high, nRF24L01+ enters standby-II mode. In this mode the transmission of a packet isstarted as soon as the CSN is set high after an upload (UL) of a packet to TX FIFO.TX mode10Minimum 10µs high pulse Data in TX FIFOs.Will empty one level in TX FIFOs b .b.This operating mode pulses the CE high for at least 10µs. This allows one packet to be transmitted.This is the normal operating mode. After the packet is transmitted, the nRF24L01+ enters standby-Imode.Standby-II101TX FIFO empty.Standby-I1-0No ongoing packet transmission.Power Down 0---Name nRF24L01+Notes Max.ments Tpd2stby Power Down Î Standby mode 150µsWith external clock a a.See Table 11. on page 19 for crystal specifications.1.5msExternal crystal, Ls < 30mH 3msExternal crystal, Ls = 60mH 4.5msExternal crystal, Ls = 90mH Tstby2a Standby modes Î TX/RX mode130µs Thce Minimum CE high10µs Tpece2csn Delay from CE positive edge to CSNlow 4µs。

layout versus schematic工作原理

Layout与Schematic在电子设计和制造中各自扮演着不同的角色,并共同协作以实现电路的正常工作。

Schematic(原理图)是电子设计的起点,它以一种图形化的方式描述了电路的基本构成和连接方式。

原理图使用各种符号来表示电路中的不同元件,如电阻、电容、电感、二极管、三极管、集成电路等,并通过线条(代表导线)将这些元件连接起来。

原理图的主要作用是提供一个清晰、简洁的电路描述,使设计者能够快速地理解和分析电路的工作原理。

Layout(布线图)则是将原理图转化为实际物理布局的过程。

在Layout中,设计者需要考虑到元件的实际尺寸、引脚间距、布线宽度、布线间距等因素,以确保电路在实际工作中能够正常、稳定地运行。

布线图的设计需要考虑到很多因素,如信号的传输延迟、电磁干扰、热量分布等,以确保电路的性能和可靠性。

Layout与Schematic之间的关系是密切而微妙的。

原理图的设计需要考虑到实际的布线需求,以确保电路在实际制作中能够顺利地实现。

而布线图的设计则需要根据原理图的要求,进行精确的物理布局和布线。

这种相互依赖的关系使得Layout与Schematic 在电子设计中成为了一个不可分割的整体。

总的来说,Layout与Schematic都是电子设计中不可或缺的部分。

原理图提供了电路的基本框架和工作原理,而布线图则将这些原理转化为实际的物理布局。

两者的紧密

结合使得电子设计能够顺利地从理论走向实践,实现电路的正常工作。

28.3.3 Bill Of Materials (BOM)

Designator Value Footprint Comment C1, C215pF0402NP0 +/- 2%

C3 2.2nF0402X7R +/- 10%

C4Not mounted0402

C5 1.5pF0402NP0 +/-0.1pF

C6 1.0pF0402NP0 +/-0.1pF C7, C9, C11100nF0402X7R +/- 10%

C8, C1033nF0402X7R +/- 10%

L1, L2 6.8nH0402High frequency chip

inductor +/-5% L3 5.6nH0402High frequency chip

inductor +/-5% R122k04021%

U1nRF24LE1-O17Q24QFN24QFN24 4x4 mm package X116 MHz 3.2 x 2.5 mm SMD-3225, 16 MHz,

CL=9pF, +/-60ppm PCB substrate FR4 laminate14.6 x 16.6 mm 2 layer, thickness 1.6 mm Table 118. nRF24LE1 OTP, 4x4 mm QFN24 Bill of Materials

29 Ordering information 29.1 Package marking

29.1.1 Abbreviations

Table 119. Abbreviations

29.2 Product options

29.2.1 RF silicon

Table 120. nRF24LE1 OTP RF silicon options

N R F A X 24L E 1Z Y

Y W W L

L

Abbreviation

Definition

24LE1Product number

X "X" grade, that is, Engineering Samples (optional)

Z Package type."G" = 32 pin, "H" = 48 pin and “I” = 24 pin YY Two digit Year number WW Two digit week number

LL Two letter wafer lot number code

B

Build Code, that is, unique code for production sites, package type and test platform

Ordering code

Package

Container MOQ nRF24LE1-O17Q24-T

4x4mm 24-pin QFN, lead free (green)

Tray

490

nRF24LE1-O17Q24-R74x4mm 24-pin QFN, lead free (green)

Tape-and-reel 1500nRF24LE1-O17Q24-R 4x4mm 24-pin QFN, lead free (green)

Tape-and-reel 4000nRF24LE1-O17Q24-SAMPLE 4x4mm 24-pin QFN, lead free (green)

Sample box

5nRF24LE1-O17Q32-T 5x5mm 32-pin QFN, lead free (green)

Tray 490nRF24LE1-O17Q32-R75x5mm 32-pin QFN, lead free (green)

Tape-and-reel 7”1500nRF24LE1-O17Q32-R 5x5mm 32-pin QFN, lead free (green)

Tape-and-reel 13”4000nRF24LE1-O17Q32-S 5x5mm 32-pin QFN, lead free (green)

Sample box

5nRF24LE1-O17Q48-T 7x7mm 48-pin QFN, lead free (green)

Tray 260nRF24LE1-O17Q48-R77x7mm 48-pin QFN, lead free (green)

Tape-and-reel 7”1000nRF24LE1-O17Q48-R 7x7mm 48-pin QFN, lead free (green)

Tape-and-reel 13”3000nRF24LE1-O17Q48-S

7x7mm 48-pin QFN, lead free (green)

Sample box

5

29.2.2 Development tools

The nRF24LE1 OTP will not have separate development kits. For development use nRF24LE1 devices with flash memory. If multiple memory write functions are not used, code written for the flash memory ver-sions of nRF24LE1 will run on nRF24LE1 OTP without changes. Socket programming adapters for the nRF24LE1 OTP are available from Nordic Semiconductor. These are intended for use in engineering samples and pilot runs. For volume production use commercially available OTP programming tools.

Type Number Description

nRF6700nRFgo Starter Kit

nRF24LE1-F16Q24-DK nRFgo Development Kit for nRF24LE1 4x4mm 24

pin QFN (requires nRFgo Starter Kit)

nRF24LE1-F16Q32-DK nRFgo Development Kit for nRF24LE1 5x5mm 32

pin QFN (requires nRFgo Starter Kit)

nRF24LE1-F16Q48-DK nRFgo Development Kit for nRF24LE1 7x7mm 48

pin QFN (requires nRFgo Starter Kit)

nRF6701 nRFgo nRF24LE1 48-pin Flash/OTP Programming

Adapter Kit (requires nRFgo Starter Kit)

nRF6702nRFgo nRF24LE1 32-pin Flash/OTP Programming

Adapter Kit(requires nRFgo Starter Kit)

nRF6703nRFgo nRF24LE1 24-pin Flash/OTP Programming

Adapter Kit(requires nRFgo Starter Kit)

Table 121. nRF24LE1 OTP development tools。