基于内插滤波器符号同步的实现

- 格式:pdf

- 大小:417.63 KB

- 文档页数:3

《电子技术应用》2005年第6期本刊邮箱#eta@ncse.com.cn在数字通信系统中,为了限制被传输的数字信号的频谱,需要对其进行滚降升余弦滤波,形成基带波形,并对载波进行调制,以实现频带传输。

在接收端,需要对经过相干解调、匹配滤波后的基带波形进行重新采样得到相应的数字信号。

根据奈奎斯特抽样值无失真准则[1],A/D转换器若在最佳采样时刻进行采样,得到的采样值恰好是发送端所要传递的数据。

但在实际情况下,由于信道传输延时以及收发两地时钟偏移,使采样无法在最佳时刻进行,这样采集到的数据与正确的数据之间存在着偏差,需要有同步措施来调整采样时钟或对采样值进行插值修正。

目前数字接收机中的符号同步大多采用自同步法。

其主要有两种[2],一种是由定时错误检测(TED)算法加环路滤波器估算采样时钟和最佳采样时刻之间的相位差,然后通过数控振荡器NCO调整采样时钟,称为同步采样恢复;另一种也使用相同的方法估算时钟相差,但它并不调整采样时钟相位,而是通过插值算法对采样值进行修正,称为异步采样恢复。

由于后者不需要改变时钟相位,因此具有更好的稳定性,故得到广泛的应用。

异步采样恢复的符号同步设计结构如图1所示。

该方法的关键在于插值算法的准确性。

针对这一点,本文提出了一种符号同步的硬件设计方案,其插值滤波器的设计采用了理想插值算法加窗处理,与目前所采用的另一种拉格朗日插值滤波器相比,具有更好的频域特性。

1时钟相差的估算对于最佳采样时刻和采样时钟相位差的估算,本文采用定时错误检测(TED)加环路滤波器实现。

其中定时错误检测环节采用NDA-ELD算法[2],该算法是由最大似然估计法所推导的,它要求A/D转换器以两倍的符号频率对输入波形进行采样。

公式如下:e(k)=y(kT+!kT/2)×[y(kT+T/2+!kT/2)-y(kT-T/2+!k-1T/2)]=y(2kTs+!kTs)×{y[(2k+1)Ts+!kTs]-y[(2k-1)Ts+!k-1Ts]}(1)这里T是符号周期,Ts是采样间隔,Ts=T/2。

基于内插滤波器符号同步的实现陈卫东,孙 栋,张华冲(中国电子科技集团公司第五十四研究所,河北石家庄050081)摘 要:比较了同步采样和异步采样条件下符号同步实现方法的不同,在全数字接收机中需要采用内插方法来实现符号同步,内插滤波器是一种线性时变滤波器,在工程中可以采用多项式内插函数来近似,采用FARROW 结构实现。

在此基础上介绍了内插法符号同步环路的结构,组成单元,其中详细介绍了内插控制器和定时误差检测器的原理。

在AWGN 信道中针对QAM 64信号进行了仿真和实现,眼图和星座图恢复良好,该符号同步环路可以应用于侦察接收机的解调器中。

关键词:全数字接收机;内插滤波器;符号同步中图分类号:TN914.42 文献标识码:A 文章编号:1003-3114(2009)06-53-3Design of Symbol Synchronization Circuit Based on InterpolationC HE N Wei dong,SUN Dong,ZHANG Hua chong(The 54th Research Insti tute of CETC,Shijiazhuang Hebei 050081,China)Abstract :In traditional demodulator synchronization sampling is used.In all di g i tal recei ver based on the non synchronization samplin g timing recovery is achieved with the help of interpolator.Cubic interpolator,interpolation controller and Gardner Algoithm for symbol timing error detection are introduced in detail i n this paper.The performance of the design is well i n si mulation.The desi gn is implemented in XILINX FPGA and i t can be applied to demodulation for reconnaissance receiver.Key words:all digital receiver;interpolator;symbol synchronization收稿日期:2009-09-01作者简介:陈卫东(1968-),男,高级工程师。

gardner同步算法原理

Gardner同步算法是一种非判决指向方法,它基于内插法的原理,通过定时环路调整内插计算的参数,从而跟踪和锁定位同步信号。

Gardner算法的核心部分包括内插器、时钟误差提取模块、环路滤波器以及控制器模块。

在Gardner算法中,相互正交的I、Q两路信号的采样点会通过运算每个符号期间产生一个定时错误样点。

通过定时误差检测,定时错误序列经过环路滤波器后送给数控振荡器。

数控振荡器根据接收到的采样时刻信号和误差信号产生参数控制插值滤波器。

插值滤波器会根据这些信号进行采样时刻调整,从而完成整个符号同步过程。

Gardner算法的优点在于不需要改变本地采样时钟,可以适应较宽速率范围内的基带信号,因而具有传统方法不可替代的优势。

以上内容仅供参考,如需更多专业信息,建议咨询数字通信或信号处理专业人士或查阅相关文献资料。

全数字QAM解调器的设计与FPGA实现张华冲;王晓亚【摘要】正交幅度调制(QAM)是一种频谱利用率较高的调制方式.分析了影响解调性能的主要因素以及解决方法,提出了一种QAM解调器的全数字实现结构.介绍了符号同步环路的构成,在设计中采用FARROW结构立方内插器,内插控制器为内插器提供控制变量,对内插控制器的实现进行了详细介绍,定时误差提取采用Gardner 算法.采用结合均衡的载波恢复混合结构,显著提高了载波恢复的性能.所设计的解调器可以应用于通信、侦察接收机中.【期刊名称】《无线电工程》【年(卷),期】2010(040)006【总页数】4页(P27-30)【关键词】全数字接收机;内插滤波器;符号同步【作者】张华冲;王晓亚【作者单位】中国电子科技集团公司第五十四研究所,河北,石家庄,050081;中国电子科技集团公司第五十四研究所,河北,石家庄,050081【正文语种】中文【中图分类】TN9110 引言QAM是一种频谱利用率较高的调制方式。

在频谱资源日益紧张的今天,越来越多的领域采用了这一调制方式,如有线视频广播(DVB-C)、宽带接入和SDH等许多高速通信系统中。

由于收发双方本振频率存在必然的差异,这样就导致收发双方载波频率会有微小的偏差,传播延时还会造成载波相位的偏移。

在接收机中收发双方的延时一般是未知的,并且AD采样还会产生采样频偏与相偏,这些是解调器中的载波同步与符号同步需要解决的问题。

信道衰减、多径、白噪声干扰和回波叠加等非理想因素的影响使得QAM信号经过信道传输后产生了幅度、频率和相位失真,造成码间串扰(ISI),严重的码间串扰甚至使通信中断。

QAM调制信号、幅度和相位上都携带有信息,对信道失真尤其敏感,所以QAM信号的解调还应当包含自动增益控制(AGC)和均衡等环节。

1 QAM解调器总体结构随着ADC采样频率的提高以及高速数字信号处理芯片的发展,模数转换模块的位置逐渐向着射频方向移动。

专利名称:一种基于粒子滤波的符号同步方法

专利类型:发明专利

发明人:刘策伦,安建平,田露,卜祥元,卢继华,王正欢,黄彦东,柯晟

申请号:CN201210566909.4

申请日:20121224

公开号:CN103036669A

公开日:

20130410

专利内容由知识产权出版社提供

摘要:本发明涉及一种基于粒子滤波的符号同步方法,尤其涉及一种基于粒子滤波的高速卫星通信系统符号同步方法,属于通信信号处理技术领域。

输入模拟基带信号经过AD采样后,变为数字信号,数字信号首先经过一个插值滤波器,该滤波器根据输入信号和由粒子滤波器提供的定时偏差估计值计算出最佳采样时刻的值,插值滤波器的输出送入定时误差计算模块,得到测量定时误差,测量定时误差经粒子滤波即得定时偏差估计值再将送入插值滤波器以控制插值时刻,插值滤波器的输出x′(rT)中已包含了最佳采样时刻的值x′(rT),直接输出即完成符号同步。

本发明方法在不增加采样率的前提下,提高了定时误差估计精度;利用粒子滤波调整定时偏差,较传统方案降低了自噪声的影响。

申请人:北京理工大学

地址:100081 北京市海淀区中关村南大街5号

国籍:CN

更多信息请下载全文后查看。

基于内插滤波器符号同步的实现

陈卫东;孙栋;张华冲

【期刊名称】《无线电通信技术》

【年(卷),期】2009(35)6

【摘要】比较了同步采样和异步采样条件下符号同步实现方法的不同,在全教字接收机中需要采用内插方法来实现符号同步,内插滤波器是一种线性时变滤波器,在工程中可以采用多项式内插函数来近似,采用FARROW结构实现.在此基础上介绍了内插法符号同步环路的结构,组成单元,其中详细介绍了内插控制器和定时误差检测器的原理.在AWGN信道中针对QAM64信号进行了仿真和实现.眼图和星座图恢复良好,该符号同步环路可以应用于侦察接收机的解调器中.

【总页数】3页(P53-55)

【作者】陈卫东;孙栋;张华冲

【作者单位】中国电子科技集团公司第五十四研究所,河北,石家庄,050081;中国电子科技集团公司第五十四研究所,河北,石家庄,050081;中国电子科技集团公司第五十四研究所,河北,石家庄,050081

【正文语种】中文

【中图分类】TN914.42

【相关文献】

1.基于循环前缀的OFDM符号同步算法改进及其实现 [J], 乔天柱;张海滨;罗汉文;宋文涛

2.基于FPGA的OFDM-RoF符号定时同步的实现 [J], 吴金达;余方围;任宏亮;卢瑾;胡卫生

3.一种基于XILINX IP核的并行架构内插滤波器实现 [J], 贾一凡;吴兵;顾何方

4.基于短训练序列的符号同步改进算法及其实现 [J], 陈佑红;张科峰

5.一种基于模糊推理的内插滤波器设计与实现 [J], 邓军;杨银堂

因版权原因,仅展示原文概要,查看原文内容请购买。

一种基于内插法符号同步电路的设计

赵行波;张海亮;贺光辉;周祖成

【期刊名称】《微计算机信息》

【年(卷),期】2006(022)032

【摘要】提出了一种新的符号同步电路结构,采用立方插值和O&M定时误差检测相结合的算法实现符号定时同步,并通过Altera DSP Builder完成该电路的设计、仿真和分析,将设计用Altera Stratix Ⅱ FPGA实现,应用在实际的接收机中,证明其能纠正1%的定时误差,工作时钟频率最高可达到130MHz.

【总页数】4页(P274-276,264)

【作者】赵行波;张海亮;贺光辉;周祖成

【作者单位】10084,北京清华大学电子工程系;10084,北京清华大学电子工程系;10084,北京清华大学电子工程系;10084,北京清华大学电子工程系

【正文语种】中文

【中图分类】TN914.4;TN949.197

【相关文献】

1.一种基于FPGA的硬件开环位同步电路设计与实现 [J], 秦文兵;罗来源;向闻

2.一种基于符号动力学的新颖混沌A/D转换器的设计 [J], 安娜;龚成龙;苏文明

3.基于DVB-C的符号同步电路优化设计 [J], 刘昕;吴建辉;黄伟

4.一种基于FPGA帧同步电路设计 [J], 刘彦平;万国金;李迟生;胡乐

5.一种基于内插法符号同步电路的设计 [J], 赵行波;张海亮;贺光辉;周祖成

因版权原因,仅展示原文概要,查看原文内容请购买。

宽带无线通信OFDM 系统同步技术− 132 − 6.3.1 内插滤波假设接收信号为x (t ),T s 是其采样周期,内插后的信号为y (n ),T i 是内插采样周期,内插滤波器为h (t ),则将采样y (kT i )称为第k 个内插因子,其计算主要有两种方法,下面进行分析和讨论。

(1)方法1在该方法中[12~13]内插因子y (kT i )可表示为:s s ()()()i i m y kT x mT h kT mT =⋅−∑(6-21)假设i =int[k T i /T s ]−m ,int[x ]表示最大整数,m k =int[kT i /T s ],小数间隔表示为u k =kT i /T s −m k (0≤u k ≤1)。

由此可以推出:m =m k −i 和(KT i −mT s )=(i +u k )T s ,则kT i =(m k +u k )T s ,则可从已知采样x ((m k −1)T s )、x ((m k T s ))、x ((m k +1)T s )…中利用内插滤波器来计算y (kT i )如式(6-22)所示:21s s ()[()][()]I i k k i I y kT x m i T h i u T ==−⋅+∑21s 0[()]()I N lk l k i I l x m i T b i u ===−⋅∑∑21s 0()[()]I N lk l k l i I u b i x m i T ===−∑∑ 0()N lk l u v l ==∑(6-22) 其中,21s ()()[{}]I l k i I v l b i x m i T ==−∑;b l (i )是固定值,其独立于u k ,其取值只取决于内插滤波器的冲击响应h (t )。

仿真分析表明[13]:四点—三阶内插滤波器可满足很多场合的需要,且计算量较小,在实际系统中应该是最好的选择,其b l (i )取值见表6-1。

基于内插滤波器符号同步的实现陈卫东,孙 栋,张华冲(中国电子科技集团公司第五十四研究所,河北石家庄050081)摘 要:比较了同步采样和异步采样条件下符号同步实现方法的不同,在全数字接收机中需要采用内插方法来实现符号同步,内插滤波器是一种线性时变滤波器,在工程中可以采用多项式内插函数来近似,采用FARROW 结构实现。

在此基础上介绍了内插法符号同步环路的结构,组成单元,其中详细介绍了内插控制器和定时误差检测器的原理。

在AWGN 信道中针对QAM 64信号进行了仿真和实现,眼图和星座图恢复良好,该符号同步环路可以应用于侦察接收机的解调器中。

关键词:全数字接收机;内插滤波器;符号同步中图分类号:TN914.42 文献标识码:A 文章编号:1003-3114(2009)06-53-3Design of Symbol Synchronization Circuit Based on InterpolationC HE N Wei dong,SUN Dong,ZHANG Hua chong(The 54th Research Insti tute of CETC,Shijiazhuang Hebei 050081,China)Abstract :In traditional demodulator synchronization sampling is used.In all di g i tal recei ver based on the non synchronization samplin g timing recovery is achieved with the help of interpolator.Cubic interpolator,interpolation controller and Gardner Algoithm for symbol timing error detection are introduced in detail i n this paper.The performance of the design is well i n si mulation.The desi gn is implemented in XILINX FPGA and i t can be applied to demodulation for reconnaissance receiver.Key words:all digital receiver;interpolator;symbol synchronization收稿日期:2009-09-01作者简介:陈卫东(1968-),男,高级工程师。

主要研究方向:通信信号处理、软件无线电。

0 引言符号同步的主要任务是从接收到的信号中估计出恢复时钟相位与最佳采样位置的相位误差信息,并根据该信息,将本地采样时钟调整到能够对码元进行最佳检测的相位上,得到信号的最佳采样值,这些采样值中包含判决时刻的信号值。

传统的数字化解调器一般采用零中频方案,需要零中频信道单元把中频信号变换为I Q 两路零中频信号,再进行A/D 采样,定时恢复是通过调整AD 采样时钟相位来完成的,这种接收机定时恢复环路结构简单,但是环路包含模拟单元,模拟器件的非线性,稳定性较差,会对定时恢复的精度,可靠性造成影响。

在全数字接收机中,A/D 采样在中频完成,数字下变频确保了I Q 幅度、相位的一致性,定时恢复环路完全在数字域实现。

在具体实现中,整个环路可以在一片FPGA 芯片内完成,可靠性与稳定性得到了很大提高。

符号同步是全数字接收机中的一个关键技术。

传统的解调器采用同步采样方式,即符号同步环路锁定后,采样时钟频率是符号速率的整倍数,采样点中包含了判决时刻。

在全数字接收机中,采用异步采样方式,即采样时钟频率与发送端时钟频率不相关,而是一个固定时钟频率,采样点中不包含判决时刻。

由于采样不同步而引入的定时速率和相位误差,需要用数字信号处理的方法来补偿,即通过定时误差估值控制内插滤波器对采样得到的信号样本值进行插值运算,从而得到信号在最佳采样时刻的近似值。

内插滤波器即是完成这一功能必须的环节。

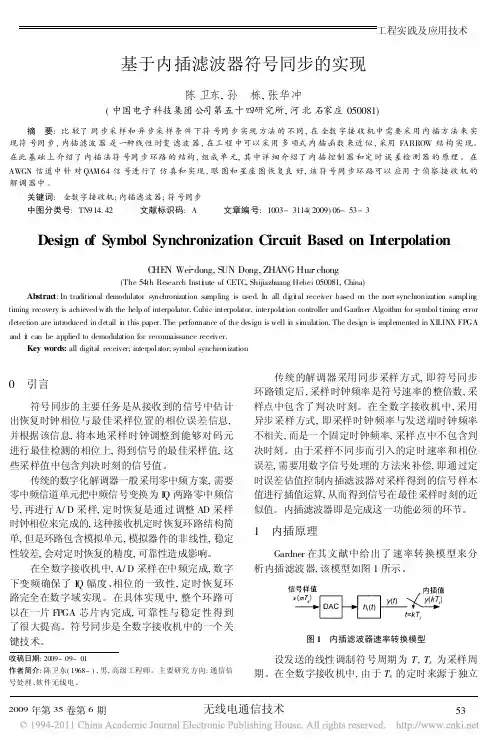

1 内插原理Gardner 在其文献中给出了速率转换模型来分析内插滤波器,该模型如图1所示。

图1 内插滤波器速率转换模型设发送的线性调制符号周期为T,T s 为采样周期。

在全数字接收机中,由于T s 的定时来源于独立工程实践及应用技术的本地振荡时钟,所以TT s的值一般情况下是无理数。

把采样值输入内插滤波器,输出的抽样值表示为y (kT i ),它是以T i 为周期的函数,因T i 与T 是同步的,所以应有T i =Tk,k 是一小整数。

然后,内插滤波器根据k 值降抽样恢复出原始数据。

对照图1可以看出,插值滤波器实际上完成了时变插值和抽取的功能。

信号样值经DAC 与模拟滤波器h I (t )后,输出信号为:y (kT i )= m x (m T s )h I (kT i -mT s )。

(1)可以用一个无限长FIR 滤波器完成理想线性内插,但在实际中滤波器通常取N 个抽头。

定义kT i =T s (kT i T s )=(m k + k )T s ,式中,m k =int [k T iT s]表示内插基点, k =int [kT iT s]-m k (0 k <1),表示分数间隔,I 2-I 1+1为内插滤波器的长度,由此得到内插公式:y (kT i )= I2i =I1x [(m k -i)T s ]h I [(i + k )T s ]。

(2)由式(2)可见,内插滤波器是一种线性滤波器,但它的内插估值点 k 随时间变化,因此数字插值滤波器脉冲响应也是随时间变化的,即数字插值滤波器是一种典型的时变线性滤波器。

在实现中,滤波器系数可以根据 k 的量化值查表得到,也可以根据 k 值实时计算得到。

在本方案中采用系数实时计算的方式。

虽然sinc 内插函数提供了平坦的通带响应和理想的阻带镜像频谱抑制性能,但是用少数几个样值点来完成估值是困难的,sinc 函数插值不容易实现,插值也是不理想的。

在全数字接收机中,可以采用多项式内插函数,如抛物线内插函数,立方内插函数。

采用立方内插函数的内插滤波器的实现结构如图2所示,完成一次插值运算需要4个采样点数据。

图2 立方内插函数的实现框图内插滤波器需要 k 、m k 两个控制量,这2个变量由内插控制器产生,内插控制器可以用NC O 或迭代的方法实现。

2 实现方案为了跟踪采样频偏和相偏,采用二阶锁相环结构,符号同步环路如图3所示,主要由内插滤波器,定时误差检测器(TED ),环路滤波器,内插控制器等组成。

定时误差检测器对经过匹配滤波后的数据提取定时误差,误差信号经过环路滤波器滤除高频噪声后送给内插控制器,内插控制器主要由一个递减NCO 组成,NC O 溢出时输出分数间隔 k ,溢出信号和 k决定内插滤波器的插值基点和滤波器系数。

图3 符号同步环路实现框图在这种实现中,有3个时钟域。

内插滤波器和内插控制器的工作时钟是采样时钟1/T s ,匹配滤波器和TE D 单元工作时钟是1/T i ,环路滤波器单元工作时钟是1/T ,上采样单元完成在不同时钟域的数据交换。

下面详细说明每部分的功能和实现。

2.1 内插滤波器完成对异步采样数据的插值运算与数据抽取功能,内插滤波器选用拉格朗日3次内插函数。

输入为数字下变频后的I Q 两路正交基带信号,采样率为1/T s ,内插滤波器后的数据采样率为k /T,k 为1、2、4等小整数,由选用的TED 算法决定,这里取为2。

2.2 定时误差提取算法定时误差提取采用Gardner 提出的定时误差检测算法,这是一种利用波形检测提取定时信息的方法,该算法不需要辅助数据,并且算法性能与载波偏差无关。

该算法可以工作在捕获和跟踪模式,每个符号只需要2个采样点。

其基本思想是:当前后2个码元发生变化或不变化,匹配滤波后的基带信号的幅度和极性都会有相应的变化,如果提取出相邻码元最佳采样点的幅度和极性变化信息,再加上相邻码元过渡点是否为零这一信息,就可以从采样信工程实践及应用技术号中提取出定时误差。

设接收端基带信号为:y(t)=y I(t)+j y Q(t)=pa P g(t-pT)。

(3)式中,a P为传输的复数数据,g(t-pT)为成型滤波滤波器基带函数,对y(t)的采样值可能产生定时偏差,Gardner算法提取的定时误差如下式所示:( )=y I((n-12)T+ )[y I(n T+ )-y I((n-1)T+ )]+y Q((n-12)T+ )[y Q(nT+ )-y Q((n-1)T+ )]。

(4)式中,y I、y Q表示同相和正交分量,T为符号周期, 为定时误差。

可以证明当接收信号中存在载波偏差时,对定时误差的提取没有影响。

2.3 环路滤波器环路滤波器采用一阶低通数字滤波器,环路为二阶数字锁相环,可以跟踪采样频偏与相位偏差。

调节环路滤波器的直通路和积分路的系数,可以改变载波环路的收敛时间、捕获带宽、稳态抖动等性能,环路的阻尼因子 通常取为0.707,此时,环路噪声带宽,收敛时间等参数取得最好的折衷。

将同步过程分为捕获和跟踪阶段,首先是捕获阶段,环路采用较大的带宽捕获时钟频率误差,这样可以使环路较快的达到频率锁定,进入跟踪阶段后,减小环路带宽,可以使环路稳态抖动减小。

通过检测环路滤波器积分路输出数据的方差可以判定环路是否进入频率锁定状态。

2.4 内插控制器内插滤波器的控制由一个基于NCO的控制器来完成。

NC O的步进由环路滤波器输出的误差信号进行跟踪调整,每次相位累加器溢出时,产生一个溢出标志ovfl,溢出标志决定内插器选择哪4个连续采样点数据x(m k-1)Ts、x m k T s、x(m k+1)T s、x(m k+2)T s进行内插运算。

ovfl 信号周期即为T i,由该信号分频即可得到符号时钟。

NC O溢出时刻的前一采样时刻的值与 0相乘,得到分数间隔 k,这里 0=T sT i,而分数间隔决定了内插滤波器的系数。

3 仿真和实现结果在64QAM调制方式,符号速率为20Msps,信号载频为140MHz,采样时钟频率为190MHz,SNR=25dB时,对符号同步环路的性能进行仿真,符号同步后的眼图和星座图如图4所示。

图4 环路锁定后眼图和星座图以XILI NX公司的FPGA为硬件平台,针对64QAM信号实现全数字解调器,其中的符号同步环路采用本文方案。

通过VHDL仿真,及综合布局布线,结果表明,符号同步环路在4000个符号处可以入锁,并且环路锁定稳定,星座图恢复良好。

4 结束语本文介绍的符号同步方案可以把异步采样数据通过内插运算得到同步采样点的数据,完全可以应用到全数字接收机中,定时误差提取采用非数据辅助的Gardner算法,可以使得符号同步环路独立于载波环,调试方便,可移植性强。