半导体后封装工艺及设备_图文

- 格式:pptx

- 大小:1.65 MB

- 文档页数:21

半导体封装制程及其设备介绍一、概述半导体芯片是一种微型电子器件,半导体封装制程是将芯片进行外层包装,从而保护芯片、方便焊接、测试等工作的过程。

比较常见的半导体封装方式有芯片贴装式、铅框式、无铅框式等。

本文将从半导体封装的制程入手,为大家介绍半导体封装制程及其设备。

二、半导体封装制程1. 粘结半导体封装的第一步是将芯片粘结到支撑贴片(Leadframe)上面。

支撑贴片是一种晶粒尺寸相对较大、但还不到电路板级别的导体片。

常用的粘接剂有黄胶、银胶等,其使用在制程时会加热到一定温度,使其能够黏合贴片和芯片。

2. 线缆连接芯片被粘接到支撑贴片上方后,需要进行内部连线。

通常使用铜线作为内部连线,常用的连线方式有金线焊接和铜线焊接。

它们的区别很大程度上取决于封装要求和芯片使用情况。

3. 包封装在连线之后,开始进行半导体封装的最后一步–包封装。

包封装是将芯片包封闭在一起,以进一步保护它。

常用的封装方式有QFP、BGA、SOIC、CHIP 贴片等。

三、半导体封装设备介绍1. 芯片粘结设备芯片粘结设备是半导体封装的第一步。

常用的芯片粘结设备包括黄胶粘合机、银胶粘合机、重合机等。

不同类型的设备适用于不同封装要求的芯片。

2. 线缆连接设备目前,铜线焊接机处于主流位置。

与金线焊接机相比,铜线焊接机具有成本更低、可靠度更高的优点。

因此,其能够更好地满足不同类型的芯片封装要求。

3. 包封装设备包封装设备是半导体封装的重要步骤。

常用的设备有 QFP 封装机、CHIP 贴片封装机等。

它们能够满足不同类型的封装要求,使芯片更加可靠。

四、半导体封装制程及其设备涉及到了许多知识点。

本文从制程和设备两个角度,为大家介绍了半导体封装制程及其设备。

不同的封装方式和设备对于产品的品质、成本以及生产效率都有很大的影响。

因此,在选择半导体封装制程和设备时,需要根据实际情况进行选择,以确保产品达到最佳性能和质量要求。

半导体封装制程及其设备介绍详解演示文稿尊敬的各位听众我将在接下来的时间中为您详解半导体封装的制程及其设备。

铭记电子发展的历史,即能明其过程,又能知其未来。

今天共划时代的创新,无一漏缺地离不开半导体封装。

首先,让我们理解什么是半导体封装。

半导体封装是一种将半导体芯片(例如CPU或内存)与外界物理连接的技术,它将半导体芯片从硅片(wafer)切割下来,封装到保护壳内,然后通过金线或铜线与焊带或引脚建立电连接,使之能够与电路板对接,实现电子器件的封装和连接。

然后是半导体封装的流程。

典型的封装流程包括:芯片切割、引脚安装、芯片粘合、线键合、模塑、切割、测试等步骤。

每一步都需要高精度的设备保障生产效率和产品品质。

现在,我们详细讨论一下封装过程中的关键设备。

首先是切割设备,使用硅切割机将硅片切成单独的芯片。

这需要极高的精度和稳定性,以确保芯片切割在正确的位置,并且每颗芯片的尺寸一致。

其次是引脚设备,通常会使用引脚机或复合机进行安装。

引脚机会安装各种类型的引脚,包括直插式、SMT式等等。

复合机则可以一次完成多个步骤,例如引脚安装、芯片粘合和线键合。

接着是芯片粘合设备,使用芯片粘合机,将芯片粘合到基板或框架上。

粘合需要高温,通常使用电热板或光源加热。

此外,粘合需要一定的压力,通常使用空气压缩机提供。

然后是线键合设备,使用线键合机,通过金线或铜线将芯片和引脚连接起来。

这也需要高精度和稳定性,以确保线键合的位置准确,连接的可靠性。

紧接着的工艺是模塑过程,它使用模塑机将塑料封装材料注入至芯片上,形成一层保护壳,保护芯片不被外界环境侵蚀。

最后的设备是测试设备,通过测试机对每一颗半导体进行电气性能和可靠性测试,确保每一颗产品都符合规格要求。

这既包括初级的模拟测试,也包括复杂的数字和混合信号测试。

半导体封装领域的设备技术不断进步,智能制造技术、精密测量技术、自动化技术等不断引入,提升了封装品质和效率,降低了成本,为推动半导体科技的发展,帮助创造出越来越多的高效实用的电子产品,充满了无尽的可能。

半导体封装制程及其设备介绍详解演示文稿一、引言二、半导体封装制程的整体流程1.设计和制备芯片:在封装过程开始之前,需要进行半导体芯片的设计和制备。

这包括设计电路、选择材料、制造芯片等步骤。

2.选型和设计封装方案:根据芯片功能和其他要求,选择合适的封装方案。

封装方案的选择包括外形尺寸、引脚数量和布局、散热设计等。

3.制备基板:选择合适的基板材料,并进行加工和制备。

基板的制备是封装制程中的核心环节之一,目的是为芯片提供支撑和连接。

4.芯片连接:将芯片连接到基板上,通常使用焊接技术或金线键合技术。

焊接是将芯片的引脚与基板的焊盘连接起来,金线键合则是用金线将芯片与基板进行连接。

5.包封:将芯片和连接线封装进封装材料中,形成最终的封装产品。

常见的封装材料有环氧树脂和塑料,也有针对特殊应用的金属封装。

6.测试和质量检验:对封装后的产品进行测试和质量检验,确保其符合设计要求和标准。

测试主要包括电性能测试、可靠性测试和环境适应性测试等。

7.封装后处理:包括喷涂标识、气密性测试、老化测试等。

这些步骤都是为了保证封装产品的质量和性能稳定。

三、半导体封装制程的关键步骤及设备介绍1.基板制备基板制备是封装制程中的核心步骤,主要包括以下设备:(1)切割机:用于将硅片切割成芯片,常见的切割机有钻石切割机和线切割机。

(2)干法清洗机:用于清洗芯片表面的杂质。

清洗机主要有氧气等离子体清洗机和干气流清洗机等。

(3)晶圆胶切割机:用于将芯片粘贴在基板上。

2.连接技术连接技术是将芯片与基板连接起来的关键步骤,常见的设备有:(1)焊接机:用于焊接芯片和基板之间的引脚和焊盘。

常见的焊接机有波峰焊机和回流焊机。

(2)金线键合机:用于将芯片与基板之间进行金线键合连接。

常见的金线键合机有球焊键合机和激光键合机等。

3.封装工艺封装工艺是将芯片和连接线封装进封装材料中的步骤,主要设备有:(1)半导体封装设备:用于将封装材料和连接线封装成最终产品。

尊敬的读者:以下是有关半导体封装后固化工艺流程的介绍:一、工艺流程概述1. 半导体封装后固化工艺,是指将封装好的半导体芯片在制程结束后,通过一系列步骤使其达到固化状态,以保证产品的稳定性和可靠性。

2. 固化工艺流程主要包括固化剂的选择、固化工艺参数的确定、固化设备的配置和工艺的优化等环节。

二、固化剂的选择1. 固化剂是固化工艺流程中的关键因素之一,其选择直接影响到产品的性能和质量。

2. 固化剂应具有良好的流动性、可溶性和高温稳定性,以确保在固化过程中能够充分覆盖芯片表面并形成均匀的固化层。

3. 固化剂还应具有较高的硬度和耐腐蚀性,以保障产品在使用过程中不易受到外界环境的损害。

三、固化工艺参数的确定1. 固化工艺参数包括固化温度、时间、压力等关键参数,其确定需要进行大量的实验和分析工作。

2. 固化温度应根据固化剂的特性和半导体芯片的材料选取合适的范围,并通过实验确定最佳数值。

3. 固化时间需结合固化剂的固化速度和芯片的尺寸进行合理设置,以确保固化层能够充分固化而不产生裂纹。

4. 固化压力影响固化过程中固化剂的流动和薄膜的形成,需根据具体工艺条件合理调整。

四、固化设备的配置1. 固化设备是固化工艺流程中的重要工具,其配置应考虑到生产的规模和产品的特性。

2. 固化设备需具备良好的温度控制能力和压力控制能力,同时还应具备自动化程度高、稳定性好的特点。

3. 固化设备还需具备较好的兼容性,能够适应不同封装结构和封装材料的需求。

五、工艺的优化1. 在固化工艺的实际应用中,不断优化工艺是提高产品质量和生产效率的关键。

2. 通过不断的实验研究和数据分析,找出固化工艺中的瓶颈和问题,采取相应的改进措施,以确保固化工艺流程的稳定和可靠。

3. 还需要不断地引入新的技术和材料,以提高固化工艺的效率和降低生产成本。

总结:以上是半导体封装后固化工艺流程的介绍,固化工艺对于半导体产品的质量和可靠性具有至关重要的作用,需要在实际生产中严格控制各个环节,不断进行优化和改进,以确保产品能够达到预期的性能和寿命要求。

最全的芯⽚封装⽅式(图⽂对照)芯⽚封装⽅式⼤全各种IC封装形式图⽚按⽤途分类集成电路按⽤途可分为电视机⽤集成电路。

⾳响⽤集成电路、影碟机⽤集成电路、录像机⽤集成电路、电脑(微机)⽤集成电路、电⼦琴⽤集成电路、通信⽤集成电路、照相机⽤集成电路、遥控集成电路、语⾔集成电路、报警器⽤集成电路及各种专⽤集成电路。

电视机⽤集成电路包括⾏、场扫描集成电路、中放集成电路、伴⾳集成电路、彩⾊解码集成电路、AV/TV转换集成电路、开关电源集成电路、遥控集成电路、丽⾳解码集成电路、画中画处理集成电路、微处理器(CPU)集成电路、存储器集成电路等。

⾳响⽤集成电路包括AM/FM⾼中频电路、⽴体声解码电路、⾳频前置放⼤电路、⾳频运算放⼤集成电路、⾳频功率放⼤集成电路、环绕声处理集成电路、电平驱动集成电路、电⼦⾳量控制集成电路、延时混响集成电路、电⼦开关集成电路等。

影碟机⽤集成电路有系统控制集成电路、视频编码集成电路、MPEG解码集成电路、⾳频信号处理集成电路、⾳响效果集成电路、RF信号处理集成电路、数字信号处理集成电路、伺服集成电路、电动机驱动集成电路等。

录像机⽤集成电路有系统控制集成电路、伺服集成电路、驱动集成电路、⾳频处理集成电路、视频处理集成电路。

1、BGA(ball grid array)球形触点陈列,表⾯贴装型封装之⼀。

在印刷基板的背⾯按陈列⽅式制作出球形凸点⽤以代替引脚,在印刷基板的正⾯装配LSI 芯⽚,然后⽤模压树脂或灌封⽅法进⾏密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI ⽤的⼀种封装。

封装本体也可做得⽐QFP(四侧引脚扁平封装)⼩。

例如,引脚中⼼距为1. 5mm 的360 引脚BGA 仅为31mm 见⽅;⽽引脚中⼼距为0.5mm 的304 引脚QFP 为40mm 见⽅。

⽽且B GA 不⽤担⼼QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,⾸先在便携式电话等设备中被采⽤,今后在美国有可能在个⼈计算机中普及。

半导体封装后道工艺半导体封装后道工艺,这听起来好像很神秘,其实就像是给半导体这个小“精灵”穿上漂亮又实用的外衣,让它能够在各种各样的电子设备里好好发挥作用。

半导体封装后道工艺包含好多环节呢。

咱们先说芯片切割这个事儿。

你可以把一块半导体晶圆想象成一块大蛋糕,芯片切割呢,就是把这个大蛋糕切成一块一块的小蛋糕,每一块小蛋糕就是一个单独的芯片。

这可不像咱们平常切蛋糕那么简单,得用特别精密的设备,就像超级精细的手术刀一样,要是切歪了一点,那这个芯片可能就没法好好工作了,就好比小蛋糕切得歪歪扭扭的,看着就不舒服,吃起来也不方便。

这一步啊,对精度的要求特别高,差之毫厘就可能谬以千里呢。

再来说说芯片贴装。

这个环节就像是把一颗珍贵的宝石镶嵌到戒指上。

芯片就是那颗宝石,而基板就像是戒指。

要把芯片稳稳地、精确地贴装到基板上,得用专门的胶水或者焊接技术。

这胶水啊,可不是咱们平常粘东西的胶水,那可是高科技的胶水,就像魔法胶水一样,能把芯片牢牢地固定住。

焊接呢,更像是一种超级精密的针线活,要把芯片和基板之间的电路连接起来,就像用针线把宝石和戒指连起来,要是有个焊点没焊好,就像针线没缝好,电路就不通畅了,芯片也就没法正常工作了。

接着就是引线键合了。

这就好比是在芯片和基板之间搭建桥梁。

这些细细的金属线就像是桥梁的钢索,把芯片上的焊点和基板上的焊点连接起来。

这个过程得非常小心,金属线要是断了或者没接好,那就像桥梁断了一样,信号就过不去了。

而且每一根金属线的位置和连接都要恰到好处,这可需要操作人员有非常熟练的技巧,就像一个经验丰富的建筑工人建造桥梁一样,容不得半点马虎。

还有封装测试这个环节呢。

这就像是给已经穿上衣服的半导体做一个全面的体检。

要检查它在各种环境下是不是都能正常工作,比如温度高一点、低一点的时候,就像检查一个人在不同天气下是不是都能健康生活一样。

要是发现有问题,就得赶紧找出来是哪个环节出了毛病,是芯片本身呢,还是封装过程中的某个步骤。

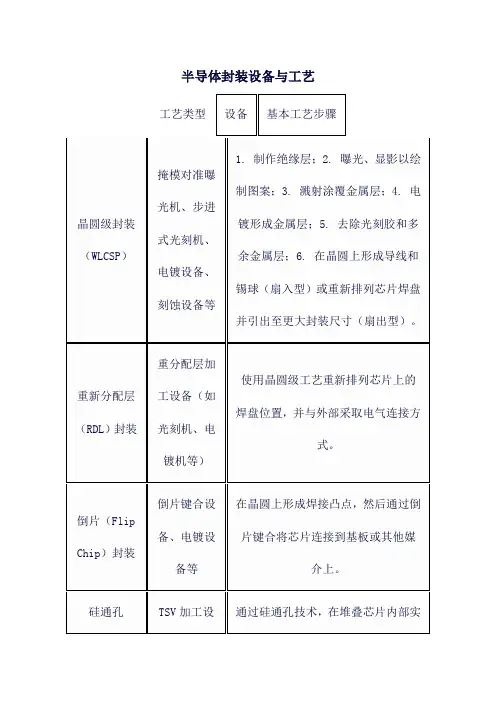

半导体制造主要设备及⼯艺流程半导体产品的加⼯过程主要包括晶圆制造(前道,Front-End)和封装(后道,Back-End)测试,随着先进封装技术的渗透,出现介于晶圆制造和封装之间的加⼯环节,称为中道(Middle-End)。

由于半导体产品的加⼯⼯序多,所以在制造过程中需要⼤量的半导体设备和材料。

⼀、晶圆制造在这⾥,我们以最为复杂的晶圆制造(前道)和传统封装(后道)⼯艺为例,说明制造过程的所需要的设备和材料。

晶圆⽣产线可以分成7个独⽴的⽣产区域:扩散(Thermal Process)、光刻(Photo- lithography)、刻蚀(Etch)、离⼦注⼊(Ion Implant)、薄膜⽣长(Dielectric Deposition)、抛光(CMP)、⾦属化(Metalization)。

这7个主要的⽣产区和相关步骤以及测量等都是晶圆洁净⼚房进⾏的。

在这⼏个⽣产区都放置有若⼲种半导体设备,满⾜不同的需要。

例如在光刻区,除了光刻机之外,还会有配套的涂胶/显影和测量设备。

传统封装(后道)测试⼯艺可以⼤致分为背⾯减薄、晶圆切割、贴⽚、引线键合、模塑、电镀、切筋/成型和终测等8个主要步骤。

与IC晶圆制造(前道)相⽐,后道封装相对简单,技术难度较低,对⼯艺环境、设备和材料的要求远低于晶圆制造。

三、半导体⼯艺解析半导体制造⼯艺是集成电路实现的⼿段,也是集成电路设计的基础。

⾃从1948年晶体管发明以来,半导体器件⼯艺技术的发展经历了三个主要阶段:1950年采⽤合⾦法⼯艺,第⼀次⽣产出了实⽤化的合⾦结三极管;1955年扩散技术的采⽤是半导体器件制造技术的重⼤发展,为制造⾼频器件开辟了新途径;1960年平⾯⼯艺和外延技术的出现是半导体制造技术的重⼤变⾰,不但⼤幅度地提⾼了器件的频率、功率特性,改善了器件的稳定性和可靠性,⽽且也使半导体集成电路的⼯业化批量⽣产得以成为现实。

⽬前平⾯⼯艺仍然是半导体器件和集成电路⽣产的主流⼯艺。