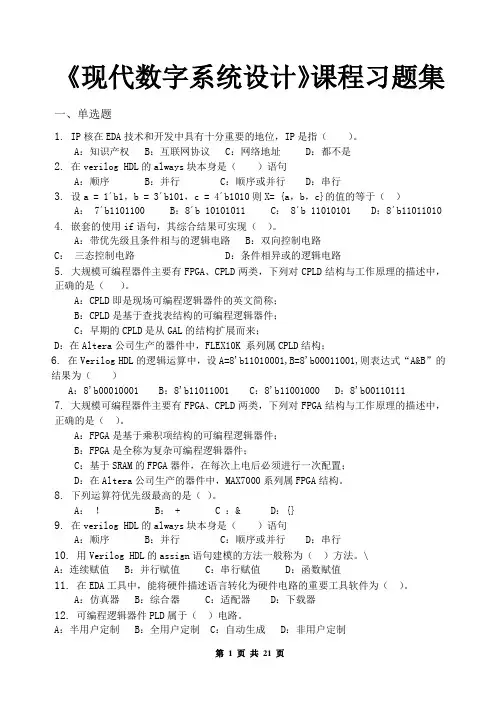

《数字系统设计》试题

- 格式:doc

- 大小:75.00 KB

- 文档页数:3

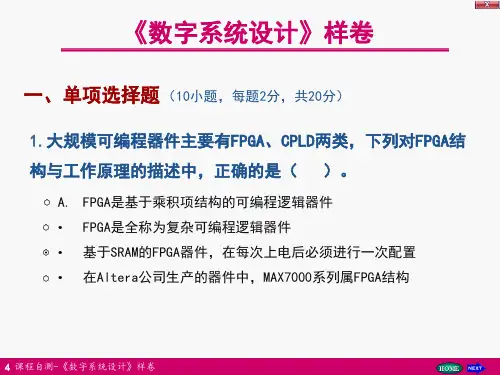

,考试作弊将带来严重后果!华南理工大学期末考试《数字系统设计》试卷1. 考前请将密封线内各项信息填写清楚;所有答案请直接答在试卷上(或答题纸上);.考试形式:开(闭)卷;(每小题2分,共16分)大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理( C )CPLD即是现场可编程逻辑器件的英文简称;CPLD是基于查找表结构的可编程逻辑器件;早期的CPLD是从GAL的结构扩展而来;在Altera公司生产的器件中,FLEX10K 系列属CPLD结构;在VHDL语言中,下列对时钟边沿检测描述中,错误的是( D )then ...;then ...;then ...;在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确( A )PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一.敏感信号参数表中,应列出进程中使用的所有输入信号;进程由说明部分、结构体部分、和敏感信号参数表三部分组成;当前进程中声明的信号也可用于其他进程基于EDA软件的FPGA / CPLD设计流程,以下流程中哪个是正确的:( C )原理图/HDL文本输入→适配→综合→时序仿真→编程下载→功能仿真→硬件测试原理图/HDL文本输入→功能仿真→综合→时序仿真→编程下载→适配→硬件测试;原理图/HDL文本输入→功能仿真→综合→适配→时序仿真→编程下载→硬件测试原理图/HDL文本输入→适配→时序仿真→编程下载→功能仿真→综合→硬件测试。

关于综合,从输入设计文件到产生编程文件的顺序正确的是:(B).逻辑综合→高层次综合→物理综合;B. 高层次综合→逻辑综合→物理综合;C. 物理综合→逻辑综合→高层次综合;D. 高层次综合→逻辑综合→时序综合;6. 进程中的信号赋值语句,其信号更新是( C )A. 按顺序完成;B. 比变量更快完成;C. 在进程的挂起时完成;D. 都不对。

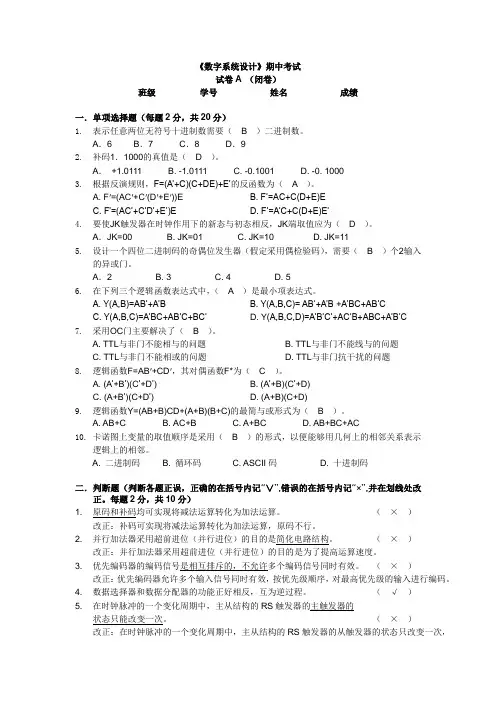

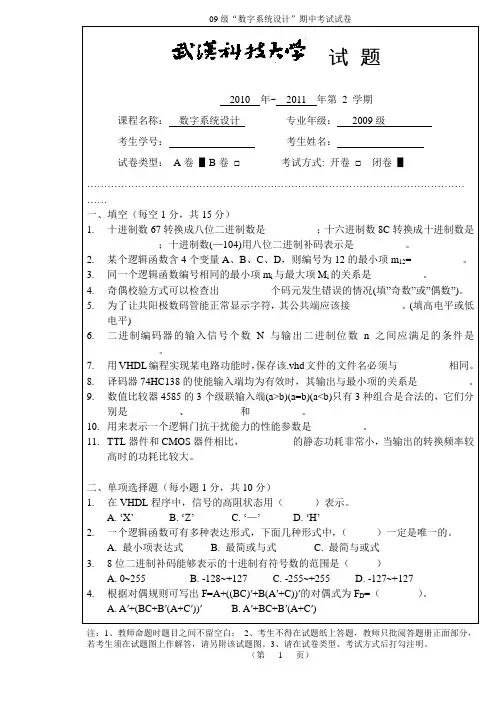

《数字系统设计》期中考试试卷A (闭卷)班级学号姓名成绩一.单项选择题(每题2分,共20分)1.表示任意两位无符号十进制数需要( B )二进制数。

A.6 B.7 C.8 D.92.补码1.1000的真值是( D )。

A.+1.0111 B. -1.0111 C. -0.1001 D. -0. 10003.根据反演规则,F=(A’+C)(C+DE)+E’的反函数为( A )。

A. F'=(AC'+C'(D'+E'))EB. F’=AC+C(D+E)EC. F'=(AC’+C’D’+E’)ED. F’=A’C+C(D+E)E’4.要使JK触发器在时钟作用下的新态与初态相反,JK端取值应为( D )。

A.JK=00 B. JK=01 C. JK=10 D. JK=115.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要( B )个2输入的异或门。

A.2 B. 3 C. 4 D. 56.在下列三个逻辑函数表达式中,( A )是最小项表达式。

A. Y(A,B)=AB’+A’BB. Y(A,B,C)= AB’+A’B +A’BC+AB’CC. Y(A,B,C)=A’BC+AB’C+BC’D. Y(A,B,C,D)=A’B’C’+AC’B+ABC+A’B’C7.采用OC门主要解决了( B )。

A. TTL与非门不能相与的问题B. TTL与非门不能线与的问题C. TTL与非门不能相或的问题D. TTL与非门抗干扰的问题8.逻辑函数F=AB'+CD',其对偶函数F*为( C )。

A. (A’+B’)(C’+D’)B. (A’+B)(C’+D)C. (A+B’)(C+D’)D. (A+B)(C+D)9.逻辑函数Y=(AB+B)CD+(A+B)(B+C)的最简与或形式为( B )。

A. AB+CB. AC+BC. A+BCD. AB+BC+AC10.卡诺图上变量的取值顺序是采用( B )的形式,以便能够用几何上的相邻关系表示逻辑上的相邻。

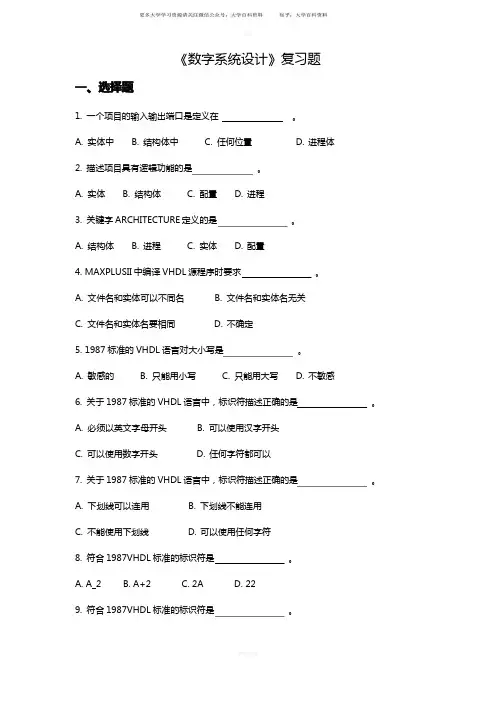

《数字系统设计》复习题一、选择题1.一个项目的输入输出端口是定义在。

A.实体中B.结构体中C.任何位置D.进程体2.描述项目具有逻辑功能的是。

A.实体B.结构体C.配置D.进程3.关键字ARCHITECTURE定义的是。

A.结构体B.进程C.实体D.配置4. MAXPLUSII中编译VHDL源程序时要求。

A.文件名和实体可以不同名B.文件名和实体名无关C.文件名和实体名要相同D.不确定5. 1987标准的VHDL语言对大小写是。

A.敏感的B.只能用小写C.只能用大写D.不敏感6.关于1987标准的VHDL语言中,标识符描述正确的是。

A.必须以英文字母开头B.可以使用汉字开头C.可以使用数字开头D.任何字符都可以7.关于1987标准的VHDL语言中,标识符描述正确的是。

A.下划线可以连用B.下划线不能连用C.不能使用下划线D.可以使用任何字符8.符合1987VHDL标准的标识符是。

A. A_2B. A+2C. 2AD. 229.符合1987VHDL标准的标识符是。

A. a_2_3B. a_2C. 2_2_aD. 2a10.不符合1987VHDL标准的标识符是。

A. a_1_inB. a_in_2C. 2_aD. asd_111.不符合1987VHDL标准的标识符是。

A. a2b2B. a1b1C. ad12D. %5012. VHDL语言中变量定义的位置是。

A.实体中中任何位置B.实体中特定位置C.结构体中任何位置D.结构体中特定位置13. VHDL语言中信号定义的位置是。

A.实体中任何位置B.实体中特定位置C.结构体中任何位置D.结构体中特定位置14.变量是局部量可以写在。

A.实体中B.进程中C.线粒体D.种子体中15.变量和信号的描述正确的是。

A.变量赋值号是:=B.信号赋值号是:=C.变量赋值号是<=D.二者没有区别16.变量和信号的描述正确的是。

A.变量可以带出进程B.信号可以带出进程C.信号不能带出进程别17.关于VHDL数据类型,正确的是。

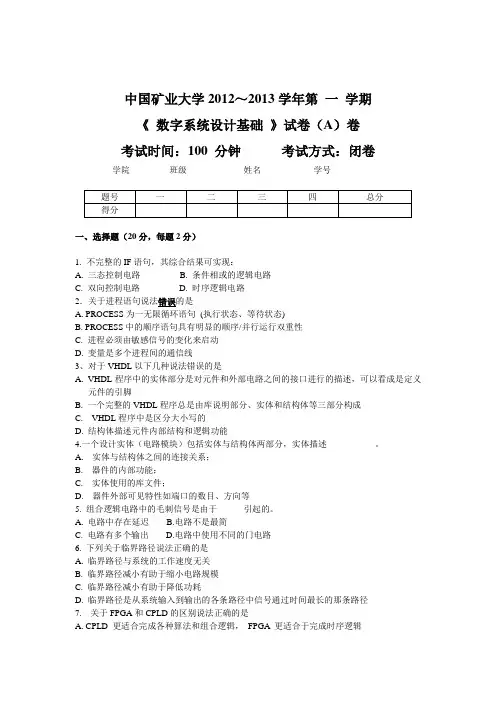

中国矿业大学2012~2013学年第一学期《数字系统设计基础》试卷(A)卷考试时间:100 分钟考试方式:闭卷学院_________班级_____________姓名___________学号____________一、选择题(20分,每题2分)1.不完整的IF语句,其综合结果可实现:_________A. 三态控制电路B. 条件相或的逻辑电路C. 双向控制电路D. 时序逻辑电路2.关于进程语句说法错误的是_________A. PROCESS为一无限循环语句(执行状态、等待状态)B. PROCESS中的顺序语句具有明显的顺序/并行运行双重性C. 进程必须由敏感信号的变化来启动D. 变量是多个进程间的通信线3、对于VHDL以下几种说法错误的是___________A. VHDL程序中的实体部分是对元件和外部电路之间的接口进行的描述,可以看成是定义元件的引脚B. 一个完整的VHDL程序总是由库说明部分、实体和结构体等三部分构成C. VHDL程序中是区分大小写的D.结构体描述元件内部结构和逻辑功能4.一个设计实体(电路模块)包括实体与结构体两部分,实体描述___________。

A. 实体与结构体之间的连接关系;B. 器件的内部功能;C. 实体使用的库文件;D. 器件外部可见特性如端口的数目、方向等5. 组合逻辑电路中的毛刺信号是由于______引起的。

A. 电路中存在延迟B.电路不是最简C. 电路有多个输出D.电路中使用不同的门电路6. 下列关于临界路径说法正确的是___________A. 临界路径与系统的工作速度无关B. 临界路径减小有助于缩小电路规模C. 临界路径减小有助于降低功耗D. 临界路径是从系统输入到输出的各条路径中信号通过时间最长的那条路径7. 关于FPGA和CPLD的区别说法正确的是___________A. CPLD 更适合完成各种算法和组合逻辑,FPGA 更适合于完成时序逻辑B. FPGA 的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而CPLD的分段式布线结构决定了其延迟的不可预测性C. 在编程上CPLD 比FPGA具有更大的灵活性D. CPLD的集成度比FPGA高,具有更复杂的布线结构和逻辑实现。

注:1、教师命题时题目之间不留空白;2、考生不得在试题纸上答题,教师只批阅答题册正面部分,若考

注:1、教师命题时题目之间不留空白;2、考生不得在试题纸上答题,教师只批阅答题册正面部分,若考

(6分)画出下图中触发器电路Q1、Q2在CP作用下的输出波形(设

要求画出时钟边沿的标识线,并写出分析过程。

六、设计题:根据要求设计电路,写出设计步骤(8+10+10=28

1.(8分)用VHDL描述一个4线-2线优先编码器,写出VHDL

注:1、教师命题时题目之间不留空白;2、考生不得在试题纸上答题,教师只批阅答题册正面部分,若考

注:1、教师命题时题目之间不留空白;2、考生不得在试题纸上答题,教师只批阅答题册正面部分,若考。

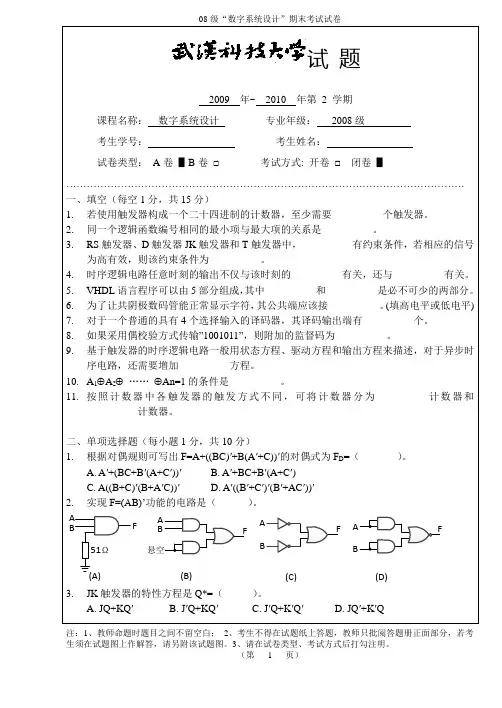

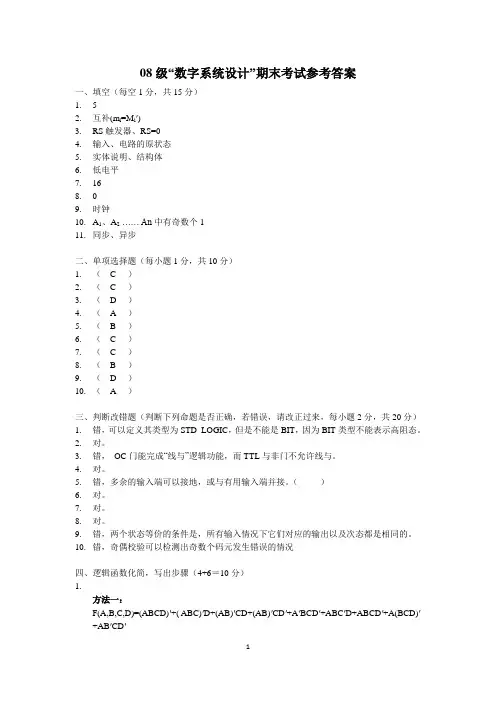

08级“数字系统设计”期末考试参考答案一、填空(每空1分,共15分)1. 52.互补(m i=M i')3.RS触发器、RS=04.输入、电路的原状态5.实体说明、结构体6.低电平7.168.09.时钟10.A1、A2…… An中有奇数个111.同步、异步二、单项选择题(每小题1分,共10分)1.( C )2.( C )3.( D )4.( A )5.( B )6.( C )7.( C )8.( B )9.( D )10.( A )三、判断改错题(判断下列命题是否正确,若错误,请改正过来,每小题2分,共20分)1.错,可以定义其类型为STD_LOGIC,但是不能是BIT,因为BIT类型不能表示高阻态。

2.对。

3.错,OC门能完成“线与”逻辑功能,而TTL与非门不允许线与。

4.对。

5.错,多余的输入端可以接地,或与有用输入端并接。

()6.对。

7.对。

8.对。

9.错,两个状态等价的条件是,所有输入情况下它们对应的输出以及次态都是相同的。

10.错,奇偶校验可以检测出奇数个码元发生错误的情况四、逻辑函数化简,写出步骤(4+6=10分)1.方法一:F(A,B,C,D)=(ABCD)'+( ABC)'D+(AB)'CD+(AB)'CD'+A'BCD'+ABC'D+ABCD'+A(BCD)' +AB'CD'=A'+B'+C'+D'+(A'+B'+C')D+( A'+B')CD+( A'+B')CD'+A'BCD'+ABC'D+ABCD'+A(B'+C '+D')+ AB'CD'= A'+B'+C'+D'方法二:由函数式可画出卡诺图如下:由卡诺图化简得:F= A'+B'+C'+D'2.输入ABCD为8421BCD码,故取值为0000~1001,当取值为0000、0011、0110、1001时,F=1,取其他的8421BCD码时,输出为0;1010~1111为无关项,由此可画出卡诺图如下:F=A'B'C'D'+AD+B'CD+BCD'五、按要求完成下列各题,并写出分析步骤(5+6+6=17分)1.(5分)分析下面的电路是否存在竞争-冒险现象?由逻辑电路图可写出函数表达式:F=AC+A'C'+A'B,当B=C=1时,F=A+A',故该电路存在竞争-冒险现象2.(6分)方法一:74283的输出S= A4A3A2A1+ B4B3B2B1+C0= ABCD+A'A'0A'输入ABCD是余3码,即取值范围为:0011~1100当ABCD=0011~0111时,A=0,74283的输出S=ABCD+1101=0000~0100当ABCD=1000~1100时,A=1,74283的输出S=ABCD+0000=ABCD即:对于十进制数0~4的余3码,该电路输出0000~0100;对于十进制5~9的余3码,该电路输出为1000~1100——5421码输出故该电路的功能是将余3码转换成5421码输出方法二:74283的输出S= A4A3A2A1+ B4B3B2B1+C0= ABCD+A'A'0A'输入ABCD是余3码,即取值范围为:0011~1100,列出真值表如下:由真值表可知,该电路的功能是将余3码转换成5421码。

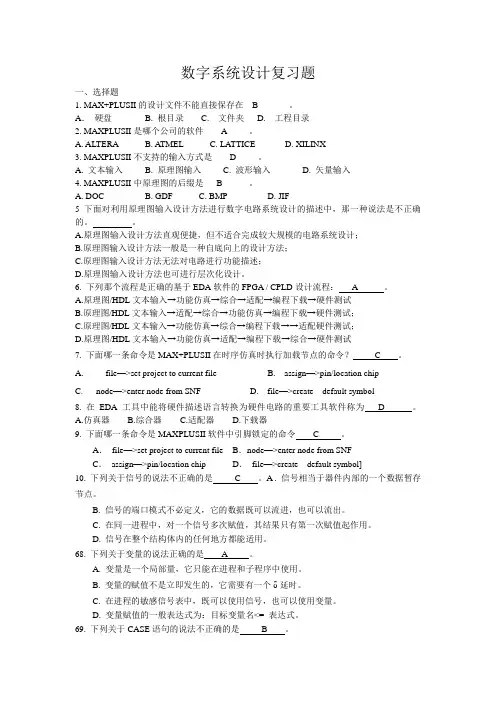

数字系统设计复习题一、选择题1. MAX+PLUSII的设计文件不能直接保存在 B 。

A.硬盘 B. 根目录 C. 文件夹 D. 工程目录2. MAXPLUSII是哪个公司的软件 A 。

A. ALTERAB. A TMELC. LATTICED. XILINX3. MAXPLUSII不支持的输入方式是 D 。

A. 文本输入B. 原理图输入C. 波形输入D. 矢量输入4. MAXPLUSII中原理图的后缀是 B 。

A. DOCB. GDFC. BMPD. JIF5下面对利用原理图输入设计方法进行数字电路系统设计的描述中,那一种说法是不正确的。

A.原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;B.原理图输入设计方法一般是一种自底向上的设计方法;C.原理图输入设计方法无法对电路进行功能描述;D.原理图输入设计方法也可进行层次化设计。

6. 下列那个流程是正确的基于EDA软件的FPGA / CPLD设计流程: A 。

A.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试B.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试;C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;D.原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试7. 下面哪一条命令是MAX+PLUSII在时序仿真时执行加载节点的命令? C 。

A. file—>set project to current fileB. assign—>pin/location chipC. node—>enter node from SNFD. file—>create default symbol8. 在EDA工具中能将硬件描述语言转换为硬件电路的重要工具软件称为 D 。

A.仿真器B.综合器C.适配器D.下载器9. 下面哪一条命令是MAXPLUSII软件中引脚锁定的命令 C 。

数字系统设计复习题一、选择题1. MAX+PLUSII的设计文件不能直接保存在 B 。

A.硬盘 B. 根目录 C. 文件夹 D. 工程目录2. MAXPLUSII是哪个公司的软件 A 。

A. ALTERAB. A TMELC. LATTICED. XILINX3. MAXPLUSII不支持的输入方式是 D 。

A. 文本输入B. 原理图输入C. 波形输入D. 矢量输入4. MAXPLUSII中原理图的后缀是 B 。

A. DOCB. GDFC. BMPD. JIF5下面对利用原理图输入设计方法进行数字电路系统设计的描述中,那一种说法是不正确的。

A.原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;B.原理图输入设计方法一般是一种自底向上的设计方法;C.原理图输入设计方法无法对电路进行功能描述;D.原理图输入设计方法也可进行层次化设计。

6. 下列那个流程是正确的基于EDA软件的FPGA / CPLD设计流程: A 。

A.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试B.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试;C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;D.原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试7. 下面哪一条命令是MAX+PLUSII在时序仿真时执行加载节点的命令? C 。

A. file—>set project to current fileB. assign—>pin/location chipC. node—>enter node from SNFD. file—>create default symbol8. 在EDA工具中能将硬件描述语言转换为硬件电路的重要工具软件称为 D 。

A.仿真器B.综合器C.适配器D.下载器9. 下面哪一条命令是MAXPLUSII软件中引脚锁定的命令 C 。

第 2.1 节:1)为布尔函数 f = a ⋅ b + c 填写一张真值表。

的真值表如下: 答:逻辑表达式 f = a ⋅ b + c 的真值表如下: a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1a ⋅b + c1 0 1 0 1 1 1 02)用真值表证明布尔表达式 a ⋅ b 和 a + b 是等价的。

答:这两个表达式的真值表如下: 这两个表达式的真值表如下: a 0 0 1 1 b 0 1 0 1a ⋅ba+b1 1 1 01 1 1 0的所有组合值都具有相同的值, 因为这两个表达式对 a 和 b 的所有组合值都具有相同的值,所以这两个表达式 相等。

相等。

3)用积之和 积之和形式来表示布尔表达式的含义是什么? 积之和积之和是指与或逻辑的布尔表达。

答:积之和是指与或逻辑的布尔表达。

与或逻辑的含义是先把输入变量或变量 的非连接到与门的输入端 几个这样的与门输出连接到一个或门的输入, 的输入端, 连接到一个或门的输入 的非连接到与门的输入端,几个这样的与门输出连接到一个或门的输入,该或 门的输出就是所谓的积之和 积之和。

门的输出就是所谓的积之和。

4)为如图 2.3 所示的与或非 与或非门填写真值表。

与或非答:该与或非门的真值表如下表所示: 该与或非门的真值表如下表所示:a 0 0 0b 0 0 0c 0 0 1d 0 1 0a ⋅b + c ⋅d1 1 10 0 0 0 0 1 1 1 1 1 1 1 10 1 1 1 1 0 0 0 0 1 1 1 11 0 0 1 1 0 0 1 1 0 0 1 11 0 1 0 1 0 1 0 1 0 1 0 10 1 1 1 0 1 1 1 0 0 0 0 05)在数字电路中,为什么要用缓冲器?缓冲器可以用来降低输出的负载, 答:缓冲器可以用来降低输出的负载,当输出必须驱动下一级逻辑门的很多个输 缓冲器可以用来降低输出的负载 入时,其负载是很重的。