实验5 优先编码器的设计

- 格式:doc

- 大小:26.00 KB

- 文档页数:2

优先编码器课程设计一、课程目标知识目标:1. 学生能理解优先编码器的概念,掌握其工作原理和功能。

2. 学生能掌握优先编码器在不同情况下的应用,如数字电路、信号处理等。

3. 学生能运用所学知识分析优先编码器的电路图,并解释其工作过程。

技能目标:1. 学生能运用所学知识设计简单的优先编码器电路,提高实际问题解决能力。

2. 学生能在团队合作中发挥自己的优势,与他人共同完成优先编码器电路的设计和搭建。

3. 学生能通过实验操作,提高动手能力和观察分析能力。

情感态度价值观目标:1. 学生对电子技术产生兴趣,培养积极探究科学问题的态度。

2. 学生在学习过程中,培养严谨、细致、专注的学习习惯。

3. 学生能认识到电子技术在实际生活中的广泛应用,增强学以致用的意识。

课程性质:本课程为电子技术基础课程,旨在帮助学生掌握优先编码器的基本知识和应用技能。

学生特点:学生处于初中年级,具有一定的电子技术基础,对实验操作感兴趣,但需加强对理论知识的学习。

教学要求:结合学生特点,注重理论与实践相结合,提高学生的实际操作能力。

同时,关注学生的情感态度价值观培养,激发学生的学习兴趣和探究精神。

通过分解课程目标为具体学习成果,为教学设计和评估提供依据。

二、教学内容1. 优先编码器的概念与分类:介绍优先编码器的定义、功能及其分类,结合教材第二章第三节内容,让学生了解优先编码器的基本概念。

2. 优先编码器的工作原理:详细讲解优先编码器的工作原理,结合教材第二章第四节内容,分析优先编码器的内部结构及工作过程。

3. 优先编码器的应用:分析优先编码器在不同场景下的应用,如数字电路、信号处理等,引用教材第二章第五节实例,让学生了解其实际应用。

4. 优先编码器电路设计:教授如何设计简单的优先编码器电路,结合教材第二章第六节内容,引导学生运用所学知识解决实际问题。

5. 实验操作:组织学生进行优先编码器电路的搭建和测试,参考教材第二章实验部分,提高学生的动手能力和观察能力。

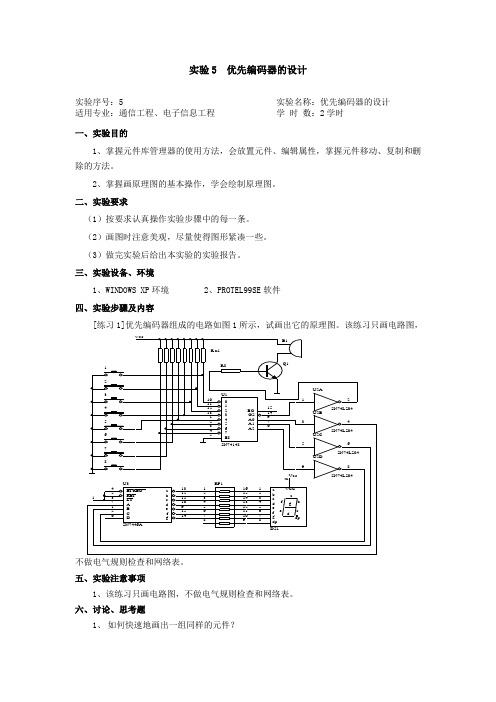

实验5 优先编码器的设计

实验序号:5 实验名称:优先编码器的设计

适用专业:通信工程、电子信息工程学时数:2学时

一、实验目的

1、掌握元件库管理器的使用方法,会放置元件、编辑属性,掌握元件移动、复制和删除的方法。

2、掌握画原理图的基本操作,学会绘制原理图。

二、实验要求

(1)按要求认真操作实验步骤中的每一条。

(2)画图时注意美观,尽量使得图形紧凑一些。

(3)做完实验后给出本实验的实验报告。

2、用到一个集成块里不同引脚的同样元件时该如何处理?如果设置错误会出现什么样的问题?。

第3章 组合逻辑函数电路一、 实验目的1. 掌握常用中规模组合逻辑器件的功能和使用方法;2. 掌握逻辑函数工程设计方法;3. 了解存储器实现复杂逻辑函数的原理和存储器的使用过程。

二、 实验原理思考题:1. 使用图2-1给出的值固定、传递和取反的符号画出基本向量函数)1,1,,,1,0,,(),,,,,,,(01234567A A A A G G G G G G G G G ==的实现图。

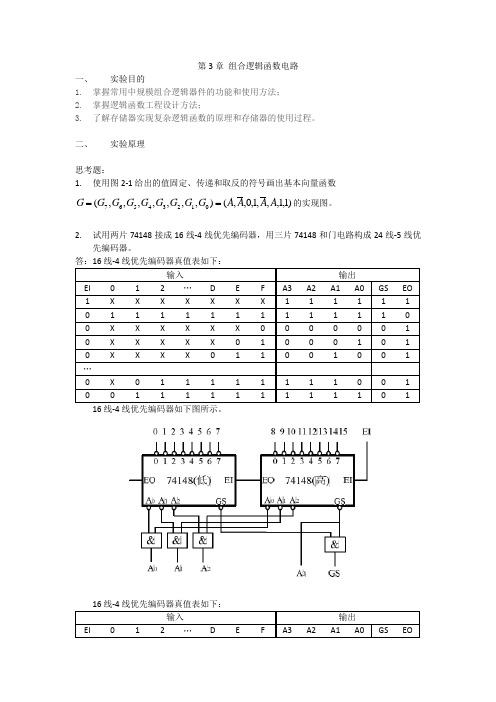

2. 试用两片74148接成16线-4线优先编码器,用三片74148和门电路构成24线-5线优先编码器。

答:16线-4线优先编码器真值表如下:123456789ABCDEFI 0I 1I 2I 3I 0I 1I 2I 31011121314151617000102030405060708090A 0B 0C 0D 0E 0FI 416线-4线优先编码器3. 用一片 74LS138 加若干与非门实现如下三输出函数的电路图:123Y AC BC Y A C Y A B C ⎧=+⎪⎪=+⎨⎪=++⎪⎩答:表达式转换如下⎪⎪⎩⎪⎪⎨⎧==++=⋅=+=+=⋅⋅=++=033127511Y C B A C B A Y Y Y C B A BC A C A Y YY Y C B A C B A ABC Y4. 完成两个3位二进制数相乘,需用几片74283?试画出逻辑电路图。

答:210B 03位的二进制数乘法器三、 实验内容1. 用多种方案设计一位全减器电路。

全减器真值表:方法一:用译码器实现(74138 一片,7420 一片)由真值表可得:7421Y Y Y Y S i ⋅⋅⋅= 7321Y Y Y Y C i ⋅⋅⋅=用译码器实现该电路如图:方法二:用8 选 1 数据选择器实现(74151 两片):方法三:用双 4 选 1 数据选择器实现(74153 一片,非门一个) 画出卡诺图并降维:S iC i由此设计电路如下:方法四:用ROM 实现由真值表编程即可。

实验三:编码器、显示译码器和数码管班级:姓名:学号:实验日期:一、实验目的:(1)了解编码器,译码器及七段数码管的工作原理。

(2)掌握编码器,七段显示译码器及数码管的使用及测试方法。

(3)学会使用编码器74LS148及七段显示译码器74LS47、数码管组成编码—译码显示系统。

二、实验设备与器件(1)集成芯片74LS148、74LS04、74LS47、共阳极数码管(2)数字万用表(3)数电实验箱三、预习要求(1)查阅资料,了解关于编码器,显示译码器及数码管的介绍(2)了解74LS148,74LS47功能及使用方法(3)掌握编码—译码显示系统的组成原理。

四、预习思考题1、什么是优先编码器?它与普通编码器有什么区别?允许同时在几个输入端有输入信号,编码器按输入信号排定的优先顺序,只对同时输入的几个信号中优先权最高的一个进行编码。

1,输入信号不同:普通的一次只能输入一个信号,但是优先编码器可同时输入多个;2、输入信号优先级不同:在普通编码器中,任何时刻只允许输入一个编码信号,优先编码器在设计时已经将各输入信号的优先顺序排好,当几个信号同时输入时,优先权最高的信号优先编码。

3、处理能力不同:优先编码器相比普通编码器电路有更强的处理能力,因为其能处理所有的输入组合情况。

2、显示译码器74LS47输出的有效驱动电平为高电平还是低电平?输出的是低电平有效;3、显示译码器74LS47能译码显示9以后的数字吗?为什么?9以后的数字无法显示,因为9以后的无法有意义的编译;4、如何测试一个数码管的好坏?一、PFC(功率因数)的高低但是不一定PFC高就是好,还要整体的斜波小,纹波小,干扰低(因为有些厂家故意把PFC做的很高但是忽略了电磁兼容这一部分)。

二、转换效率转换效率的高低,偏差值的大小和稳定,打个比方:AC170-250V这个工作电压区间,我可以尝试从170V-250V去调试,由低到高的不断变化电压,可以在功率计上看到“转换效率,PFC”的波动是否大,来证明其稳定性。

数电实验二数据编码器和译码器功能验证数据编码器和译码器是数电实验中常用的电路元件,用于将逻辑电平转换为二进制编码或者从二进制编码转换为逻辑电平。

本实验将验证编码器和译码器的功能。

编码器是一种将多个输入信号转换为对应的二进制编码输出信号的电路。

常见的编码器有优先编码器,BCD编码器和十进制-二进制编码器等。

本实验将以优先编码器为例进行验证。

实验所需器件和元件:1.优先编码器芯片(例如74LS148)2.开关等输入元件3.LED灯等输出元件4.电源和杜邦线等实验用品实验步骤:1.连接电源和电路元件:将电源连接到优先编码器芯片上,并将开关等输入元件和LED灯等输出元件连接到芯片上相应的管脚上。

2.编码器功能验证:通过设置不同的输入信号,观察输出信号的变化。

例如,设置开关为输入信号,并将不同的开关打开或关闭,观察LED灯的亮灭情况。

3.结果分析:根据编码器的功能特点,分析输出信号与输入信号的对应关系。

对于优先编码器而言,输入信号优先级较高的输入将被编码输出,而其他输入则被忽略。

4.译码器功能验证:将输入信号与编码器的输出信号连接,观察译码器的输出信号。

可以通过设计逻辑门电路来实现译码器的功能。

5.结果分析:根据译码器的功能特点,分析输出信号与输入信号的对应关系。

例如,对于BCD编码器而言,4位BCD码将被译码为10位二进制信号。

6.实验总结:通过本实验的验证,可以得出编码器和译码器的功能特点和应用范围。

编码器可以将多个输入信号编码为二进制信号输出,而译码器可以将二进制信号译码为对应的输出信号,用于实现数据的编码和译码。

本实验的目的是验证编码器和译码器的功能,通过观察输入信号和输出信号的对应关系,可以了解编码器和译码器的工作原理,并掌握它们的应用场景。

实验结果应与预期结果一致,即输入信号与编码/译码输出信号之间有明确的对应关系。

同时,实验还可以加深对数字电路和逻辑门电路的理解,提高实验操作能力和分析问题的能力。

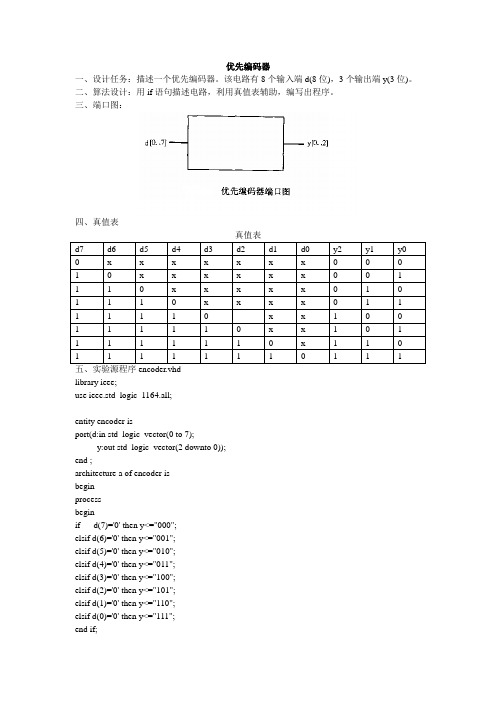

优先编码器一、设计任务:描述一个优先编码器。

该电路有8个输入端d(8位),3个输出端y(3位)。

二、算法设计:用if语句描述电路,利用真值表辅助,编写出程序。

三、端口图:四、真值表真值表d7 d6 d5 d4 d3 d2 d1 d0 y2 y1 y00 x x x x x x x 0 0 01 0 x x x x x x 0 0 11 1 0 x x x x x 0 1 01 1 1 0 x x x x 0 1 11 1 1 1 0 x x 1 0 01 1 1 1 1 0 x x 1 0 11 1 1 1 1 1 0 x 1 1 01 1 1 1 1 1 1 0 1 1 1library ieee;use ieee.std_logic_1164.all;entity encoder isport(d:in std_logic_vector(0 to 7);y:out std_logic_vector(2 downto 0));end ;architecture a of encoder isbeginprocessbeginif d(7)='0' then y<="000";elsif d(6)='0' then y<="001";elsif d(5)='0' then y<="010";elsif d(4)='0' then y<="011";elsif d(3)='0' then y<="100";elsif d(2)='0' then y<="101";elsif d(1)='0' then y<="110";elsif d(0)='0' then y<="111";end if;end process;end;--由优先编码器的真值表可知,输入信号d7的优先权最高,只要d7=0,无论其他为何值,输出都由d7决定。

编码器实验报告编码器实验报告引言编码器是一种重要的数字电路设备,用于将输入的信息转换为特定的编码形式。

在现代科技发展中,编码器广泛应用于通信、计算机、电子设备等领域。

本实验旨在通过设计和实现一个简单的编码器电路,深入了解编码器的原理和应用。

实验目的1. 了解编码器的基本原理和分类;2. 学习编码器的设计方法和实现技巧;3. 掌握编码器的应用场景和使用方法。

实验原理编码器是一种多对一的数字电路设备,通过对输入信号进行编码,将多个输入状态映射为唯一的输出状态。

常见的编码器有优先编码器、旋转编码器、格雷码编码器等。

1. 优先编码器优先编码器是一种将多个输入状态按照优先级进行编码的设备。

当多个输入同时有效时,只有优先级最高的输入被编码输出。

优先编码器常用于优先级译码器和多路选择器中。

2. 旋转编码器旋转编码器是一种通过旋转操作来改变输出状态的设备。

它通常由一个旋转轮和两个感应器组成,感应器用于检测旋转轮的方向和速度。

旋转编码器常用于旋钮、鼠标滚轮等设备中。

3. 格雷码编码器格雷码编码器是一种将二进制输入信号转换为格雷码输出信号的设备。

格雷码是一种特殊的二进制编码形式,相邻的两个码字只有一位不同,避免了二进制编码中的多位错误。

格雷码编码器常用于数字显示器、光电编码器等设备中。

实验过程本实验以优先编码器为例,设计和实现一个4输入优先编码器电路。

1. 确定输入和输出端口根据实验要求,我们需要设计一个4输入优先编码器,因此需要确定4个输入端口和1个输出端口。

2. 绘制逻辑电路图根据优先编码器的原理,我们可以绘制出如下的逻辑电路图:(图略)3. 确定逻辑门类型根据逻辑电路图,我们可以确定每个逻辑门的类型。

在本实验中,我们选择使用与门和或门。

4. 搭建电路实验平台根据逻辑电路图,我们可以搭建实验平台,连接逻辑门和输入输出端口。

5. 进行实验测试将不同输入信号输入到优先编码器中,观察输出信号的变化。

测试不同输入组合下的编码输出结果。

实验3:优先编码器的Verilog HDL描述及仿真一、实验目的及要求:1.掌握优先编码器的Verilog HDL描述方法2.理解逻辑综合的概念3.掌握RTL电路原理图分析的分析方法二、实验工具:Quartus_II 9.0三、实验原理:1. 优先编码器简介在数字系统中,常常需要将某一信息变换为某一特定的代码,把二进制代码按一定的规律编排,时每组代码具有一定的含义称为编码。

具有编码功能的逻辑电路称之为编码器。

常常会有几个部件同时发出服务请求的可能,而在同一时刻只能给其中一个部件发出允许操作信号。

因此,必须根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先级别。

8-3优先编码器有8个输入端,3个输出端。

还有一个输入使能,输出使能和优先编码器工作状态标志。

编码器以低为有效。

输入优先级别的次序为7,6,5,…,0。

当某一输入端有低电平输入,且比它优先级高的输入没有低电平输入时,输出端才输出相应输入端的代码。

优先编码器的真值表如下表1所示。

表1.2.Verilog程序设计与逻辑综合2.1 8-3线编码器示例always @ (din)begincase(din)8’b0000_0001: dout = 3’b000;8’b0000_0010: dout = 3’b001;8’b0000_0100: dout = 3’b010;8’b0000_1000: dout = 3’b011;…8’b1000_0000: dout = 3’b111;default : dout = 3’bx;endcaseend2.2 优先编码器设计优先编码器与上面描述的普通8-3线编码器不同,每次只需判断优先级高的输入端是否有效always @ (din)begincasex(din)8’b1xxx_xxxx: dout = 3’b111;8’b01xx_xxxx: dout = 3’b110;8’b001x_xxxx: dout = 3’b101;8’b0001_xxxx: dout = 3’b100;…8’b0000_0001: dout = 3’b000;default : dout = 3’bx;endcaseend2.3.逻辑综合逻辑综合是在标准单元库和特定的设计约束的基础上,把设计的高层次描述转换成优化的门级网表的过程。

学生实验报告(理工类)课程名称:电子线路CAD专业班级:G11通信工程学生学号: 1122103037学生姓名:石泽忠所属院部:信息技术学院指导教师:徐志国2012 ——2013学年第 2 学期金陵科技学院教务处制实验报告书写要求实验报告原则上要求学生手写,要求书写工整。

若因课程特点需打印的,要遵照以下字体、字号、间距等的具体要求。

纸张一律采用A4的纸张。

实验报告书写说明实验报告中一至四项内容为必填项,包括实验目的和要求;实验仪器和设备;实验内容与过程;实验结果与分析。

各院部可根据学科特点和实验具体要求增加项目。

填写注意事项(1)细致观察,及时、准确、如实记录。

(2)准确说明,层次清晰。

(3)尽量采用专用术语来说明事物。

(4)外文、符号、公式要准确,应使用统一规定的名词和符号。

(5)应独立完成实验报告的书写,严禁抄袭、复印,一经发现,以零分论处。

实验报告批改说明实验报告的批改要及时、认真、仔细,一律用红色笔批改。

实验报告的批改成绩采用百分制,具体评分标准由各院部自行制定。

实验报告装订要求实验批改完毕后,任课老师将每门课程的每个实验项目的实验报告以自然班为单位、按学号升序排列,装订成册,并附上一份该门课程的实验大纲。

实验项目名称:1、Protel99SE的基本操作实验学时: 1实验地点:B513实验日期: 2013年2月26日实验成绩:批改教师:徐志国批改时间:一、实验目的和要求1、实验目的Protel99SE的基本操作主要包括文件的建立,导入导出,为文件进行加密,创建工作组及设置成员权限等操作。

本训练的目的主要是掌握这些基本操作。

2、实验要求(1)按要求认真操作实验步骤中的每一条。

(2)做完实验后给出本实验的实验报告。

二、实验仪器和设备1、WINDOWS XP环境2、PROTEL99SE软件三、实验过程1、启动Protel99SE,在F盘建立名为你的学号的文件夹并在其下建立名为实验1的文件夹,在文件夹中建立名为lx1.ddb设计数据库文件。

专用集成电路实验报告13050Z011305024237X德文实验一开发平台软件安装与认知实验实验内容1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计电路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。

下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。

2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。

源程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Unment the following lines to use the declarations that are-- provided for instantiating Xilinx primitive ponents.--library UNISIM;--use UNISIM.Vponents.all;entity ls74138 isPort ( g1 : in std_logic;g2 : in std_logic;inp : in std_logic_vector(2 downto 0);y : out std_logic_vector(7 downto 0));end ls74138;architecture Behavioral of ls74138 isbeginprocess(g1,g2,inp)beginif((g1 and g2)='1') thencase inp iswhen "000"=>y<="00000001";when "001"=>y<="00000010";when "010"=>y<="00000100";when "011"=>y<="00001000";when "100"=>y<="00010000";when "101"=>y<="00100000";when "110"=>y<="01000000";when "111"=>y<="10000000";when others=>y<="00000000";end case;elsey<="00000000";end if;end process;end Behavioral;波形文件:生成元器件及连接电路思考:有程序可以看出,定义了三个输入端,一个输出端。

实验5 优先编码器的设计

实验序号:5 实验名称:优先编码器的设计

适用专业:通信工程、电子信息工程学时数:2学时

一、实验目的

1、掌握元件库管理器的使用方法,会放置元件、编辑属性,掌握元件移动、复制和删除的方法。

2、掌握画原理图的基本操作,学会绘制原理图。

二、实验要求

(1)按要求认真操作实验步骤中的每一条。

(2)画图时注意美观,尽量使得图形紧凑一些。

(3)做完实验后给出本实验的实验报告。

2、用到一个集成块里不同引脚的同样元件时该如何处理?如果设置错误会出现什么样的问题?。