优先编码器课程设计

- 格式:docx

- 大小:26.93 KB

- 文档页数:11

优先编码器课程设计一、课程目标知识目标:1. 学生能理解优先编码器的概念,掌握其工作原理和功能。

2. 学生能掌握优先编码器在不同情况下的应用,如数字电路、信号处理等。

3. 学生能运用所学知识分析优先编码器的电路图,并解释其工作过程。

技能目标:1. 学生能运用所学知识设计简单的优先编码器电路,提高实际问题解决能力。

2. 学生能在团队合作中发挥自己的优势,与他人共同完成优先编码器电路的设计和搭建。

3. 学生能通过实验操作,提高动手能力和观察分析能力。

情感态度价值观目标:1. 学生对电子技术产生兴趣,培养积极探究科学问题的态度。

2. 学生在学习过程中,培养严谨、细致、专注的学习习惯。

3. 学生能认识到电子技术在实际生活中的广泛应用,增强学以致用的意识。

课程性质:本课程为电子技术基础课程,旨在帮助学生掌握优先编码器的基本知识和应用技能。

学生特点:学生处于初中年级,具有一定的电子技术基础,对实验操作感兴趣,但需加强对理论知识的学习。

教学要求:结合学生特点,注重理论与实践相结合,提高学生的实际操作能力。

同时,关注学生的情感态度价值观培养,激发学生的学习兴趣和探究精神。

通过分解课程目标为具体学习成果,为教学设计和评估提供依据。

二、教学内容1. 优先编码器的概念与分类:介绍优先编码器的定义、功能及其分类,结合教材第二章第三节内容,让学生了解优先编码器的基本概念。

2. 优先编码器的工作原理:详细讲解优先编码器的工作原理,结合教材第二章第四节内容,分析优先编码器的内部结构及工作过程。

3. 优先编码器的应用:分析优先编码器在不同场景下的应用,如数字电路、信号处理等,引用教材第二章第五节实例,让学生了解其实际应用。

4. 优先编码器电路设计:教授如何设计简单的优先编码器电路,结合教材第二章第六节内容,引导学生运用所学知识解决实际问题。

5. 实验操作:组织学生进行优先编码器电路的搭建和测试,参考教材第二章实验部分,提高学生的动手能力和观察能力。

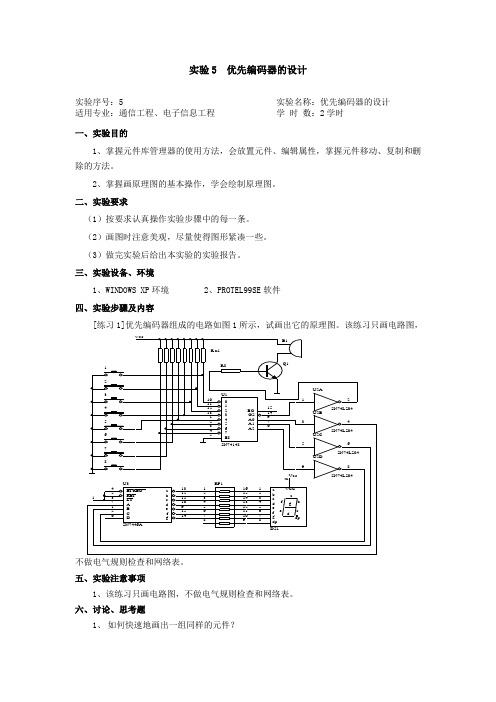

实验5 优先编码器的设计

实验序号:5 实验名称:优先编码器的设计

适用专业:通信工程、电子信息工程学时数:2学时

一、实验目的

1、掌握元件库管理器的使用方法,会放置元件、编辑属性,掌握元件移动、复制和删除的方法。

2、掌握画原理图的基本操作,学会绘制原理图。

二、实验要求

(1)按要求认真操作实验步骤中的每一条。

(2)画图时注意美观,尽量使得图形紧凑一些。

(3)做完实验后给出本实验的实验报告。

2、用到一个集成块里不同引脚的同样元件时该如何处理?如果设置错误会出现什么样的问题?。

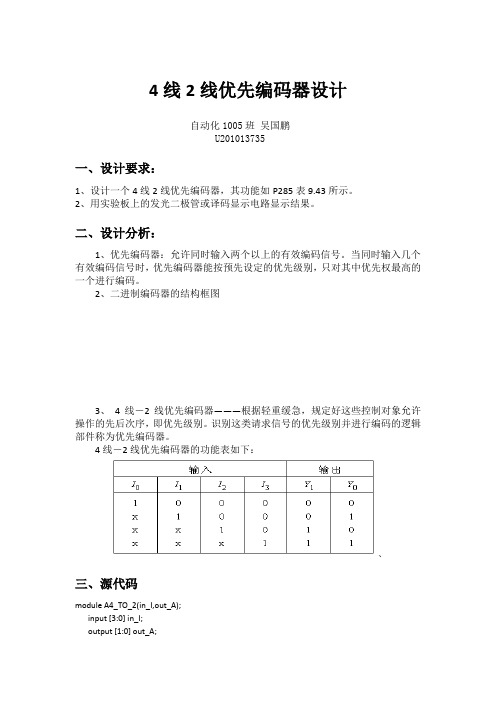

4线2线优先编码器设计自动化1005班吴国鹏U201013735一、设计要求:1、设计一个4线2线优先编码器,其功能如P285表9.43所示。

2、用实验板上的发光二极管或译码显示电路显示结果。

二、设计分析:1、优先编码器:允许同时输入两个以上的有效编码信号。

当同时输入几个有效编码信号时,优先编码器能按预先设定的优先级别,只对其中优先权最高的一个进行编码。

2、二进制编码器的结构框图3、4线-2线优先编码器―――根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先级别。

识别这类请求信号的优先级别并进行编码的逻辑部件称为优先编码器。

4线-2线优先编码器的功能表如下:、三、源代码module A4_TO_2(in_I,out_A);input [3:0] in_I;output [1:0] out_A;reg [1:0] out_A;always @(in_I)begincase(in_I)4'b0001 : out_A=2'b00;4'b0010 : out_A=2'b01;4'b0011 : out_A=2'b01;4'b0100 : out_A=2'b10;4'b0101 : out_A=2'b10;4'b0110 : out_A=2'b10;4'b0111 : out_A=2'b10;4'b1000 : out_A=2'b11;4'b1001 : out_A=2'b11;4'b1010 : out_A=2'b11;4'b1011 : out_A=2'b11;4'b1100 : out_A=2'b11;4'b1101 : out_A=2'b11;4'b1110 : out_A=2'b11;4'b1111 : out_A=2'b11;endcaseendendmodule四、仿真波形。

引言随着科学技术的发展和高新技术的广泛应用,电子技术在国民经济的各个领域所起的作用越来越大,并深深地渗透到人们的生活、工作、学习的各个方面。

新的世纪已经跨入以电子技术为基础的信息化社会,层出不穷的电子新业务、电子新设施几乎无处不在、举目可见。

作为一名微电子学专业的大学生,尽快地学习和掌握电子技术基础知识和技能是一项基本的任务。

为了更好地将理论和实际相结合,也为了增强动手能力,同时加深对理论知识的理解,笔者进行了十线-四线优先编码器的设计。

1设计原理分析1.1 编码器介绍用数字或文字对一组事件进行编号排队的过程称为编码。

如邮政编码、宿舍房间编码、计算机键盘上键的编码等等。

编码器是以数字化信息将角度、长度、速度等物理量的信息以数字量0、1编码的方式输出的传感器,由于其具有高精度,大量程测量,反应快,数字化输出特点;体积小,重量轻,机构紧凑,安装方便,维护简单,工作可靠等优良特点,故成为当今工业控制系统备受青睐及不可或缺的一部分。

编码器是由若干个与非门组合而成的,输入端是各事件代号,如n个事件用Y0~Yn-1表示,输出端是相应的二进制各位值N0~Nk-1,2k-1=Yn-1。

编码器分二进制编码器和十进制编码器,各种译码器的工作原理类似,设计方法也相同。

集成二进制编码器和集成十进制编码器均采用优先编码方案。

下面介绍一些编码器的相关概念:二进制编码器:实现以二进制数进行编码的电子电路称二进制编码器。

n位二进制数可对2n个事件进行编码,如8位计算机中地址寄存器是8位,可对28=256个指令进行编码。

二—十进制编码器:用4位二进制对十进制的10个数字0~9进行编码的电路称二-十进制编码器,常用的是8421加权码,简称BCD码。

输入是10个有效数字0~9,输出是10个4位二进制代码0000~1001。

本次设计所做的10线-4线编码器就是其中一种。

优先编码器:在使用二进制编码器和二-十进制编码器中,当两个以上信号同时输入编码器时将产生错误码输出,而优先编码器则对输入信号依照规定的先后顺序进行编码。

数字逻辑课程实验报告实验名称全加器与8路优先权编码器的设计实验人姓名学号班级同组人姓名实验时间成绩一、实验内容1、全加器的设计2、8路优先权编码器的设计二、实验原理全加器的设计:1.系统输入输出确定3个输入A、B、Cin,2个输出S、Co2.真值表A B Cin Co S0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 11 0 1 1 01 1 0 1 01 1 1 1 13.电路图4.VHDL程序源代码library ieee;use ieee.std_logic_1164.all;entity wang isport(A:in std_logic;B:in std_logic;Cin:in std_logic;Co:out std_logic;S:out std_logic);end wang;architecture dateflow of wang issignal tmp1,tmp2:std_logic;begintmp1<=A xor B;tmp2<=tmp1 and CIN;s<=TMP1 xor Cin;Co<=tmp2 or (A and B);end dateflow;8路优先权编码器的设计:1、系统输入输出确定9个输入i(7 downto 0)、s,5个输出y(2 downto 0)、ys、yex2、真值表i(7 downto 0) s y(2 downto 0) ys yex 00000000 1 111 1 1 11111111 1 111 0 1 01111111 0 000 0 0 00111111 0 000 0 0 00011111 0 000 0 0 00001111 0 000 0 0 00000111 0 000 0 0 00000011 0 000 0 0 00000001 0 000 0 03、电路图5、 VHDL程序源代码library ieee;use ieee.std_logic_1164.all;entity bmq isport(i:in std_logic_vector(7 downto 0); s:in std_logic;y:out std_logic_vector(2 downto 0); ys,yex:out std_logic);end bmq;architecture rtl of bmq isbeginprocess(i,s)beginif(s='1')theny<="111";yex<='1';ys<='1';elsif(i="11111111")theny<="111";yex<='1';ys<='0';elsif(i(7)='0')theny<="000";yex<='0';ys<='0';elsif(i(6)='0')theny<="001";yex<='0';ys<='1';elsif(i(5)='0')theny<="010";yex<='0';ys<='1';elsif(i(4)='0')theny<="011";yex<='0';ys<='1';elsif(i(3)='0')theny<="100";yex<='0';ys<='1';elsif(i(2)='0')theny<="101";yex<='0';ys<='1';elsif(i(1)='0')theny<="110";yex<='0';ys<='1';elsif(i(0)='0')theny<="111";yex<='0';ys<='1';end if;end process;end rtl;三、测试及分析全加器仿真波形8路优先权编码器仿真波形实验分析:全加器和8路优先权编码器的仿真波形图中波形与真值表一致实验结果证明:全加器的设计和8路优先权编码器的设计真实的实验结果与理论结果相同。

⽤EDA技术实现4-2线优先编码器

实验⼀:⽤EDA技术实现编码器(4学时)

课程内容:①HDL举例—译码器设计、仿真、下载

②QuartusII(ISE)软件使⽤与DE0实验板介绍

P1:基本实验:⽤FPGA实现4-2线优先编码器p238

⼀、设计要求:

1、设计⼀个4线2线优先编码器,其功能如P285表9.43所⽰。

2、⽤实验板上的发光⼆极管或译码显⽰电路显⽰结果。

⼆、设计分析:

1、优先编码器:允许同时输⼊两个以上的有效编码信号。

当同时输⼊⼏个有效编码信号时,优先编码器能按预先设定的优先级别,只对其中优先权最⾼的⼀个进⾏编码。

2, 4线-2线优先编码器的功能表如下:

、

3.逻辑关系

Y1 = X0 + X1

Y2 = X0 + X1’X2

仿真波形:。

优先编码器设计辽宁⼯程技术⼤学数电项⽬设计题⽬74LS148编码器设计指导教师院(系、部)电⽓与控制⼯程学院专业班级电⽹13-1学号1305080116姓名苏⼩平⽇期2016/12/231.设计规则在优先编码器电路中,允许同时输⼊两个以上的编码信号。

不过在设计优先编码器时已经将所有的输⼊信号按照优先顺序依次排序,当⼏个输⼊信号同时出现时,只对其中优先级别最⾼的先进⾏编码。

2.设计原理编码器的逻辑功能是将输⼊的每⼀个信号编成⼀个对应的⼆进制代码。

优先编码器的特点是允许编码器同时输⼊两个以上编码信号但只对优先级别最⾼的信号进⾏编码。

8线-3线优先编码器74LS148有8个信号输⼊端输⼊端为低电平时表⽰请求编码为⾼电平时表⽰没有编码请求有3个编码输出端输出3位⼆进制代码编码器还有⼀个使能端EI当其为低电平时编码器才能正常⼯作还有两个输出端GS和E0⽤于扩展编码功能GS为0表⽰编码器处于⼯作状态且⾄少有⼀个信号请求编码E0为0表⽰编码器处于⼯作状态但没有信号请求编码。

74LS148芯⽚管脚:0-7 编码输⼊端(低电平有效) EI 选通输⼊端(低电平有效),A0、A1、A2 三位⼆进制编码输出信号即编码输出端(低电平有效),GS ⽚优先编码输出端即宽展端(低电平有效),EO 选通输出端,即使能输出端。

芯⽚管⾓使⽤⽅法:(1)0-7 EI 选通输⼊端(低电平有效)(2)编码输⼊端(低电平有效);(3)A0、A1、A2 三位⼆进制编码输出信号即编码输出端(低电平有效);(4)GS ⽚优先编码输出端即宽展端(低电平有效);(5)EO 选通输出端,即使能输出端;3.设计思路构建8-3线优先编码器的实验电路。

输⼊信号通过单⼑双掷开关接优先编码器的输⼊端开关通过键盘上的A⾄H键控制接⾼电平(VCC)或低电平(地)。

使能端通过空格键控制接⾼电平或低电平。

输出端接逻辑探测器的监测输出。

在本次优先编码器的设计规定优先级顺序,采⽤A—H之间代表输⼊,其中优先级别从A⾄H依次增⾼,进⽽H的优先级别最⾼。

东北石油大学课程设计任务书课程硬件课程设计题目 8-3优先级编码器设计专业计算机科学与技术姓名学号主要内容、基本要求等一、主要内容:利用EL教学实验箱、微机和QuartusⅡ软件系统,使用VHDL语言输入方法设计8-3优先编码器。

可以利用层次设计方法和VHDL语言,完成硬件设计设计和仿真。

最后在EL教学实验箱中实现。

二、基本要求:设计并实现一个8-3优先级编码器,要求I0优先级最高,I7优先级最低,编码输出为原码。

三、扩展要求:输入端加使能端,在使能端为有效的低电平时,进行编码;在使能端为无效的高电平时,输出高阻状态。

四、参考文献:[1] 杨刚,龙海燕.现代电子技术-VHDL与数据系统设计.北京:电子工业出版社,2004[2] 黄仁欣.EDA技术实用教程.北京:清华大学出版社,2006[3] 潘松.VHDL实用教程[M].成都:电子科技大学出版社,2000[4] 李国丽,朱维勇.电子技术实验指导书.合肥:中国科技大学出版社,2000[5] 宋振辉. EDA技术与VHDL.北京:北京大学出版社,2008完成期限 18-19周指导教师张岩专业负责人富宇2011年 6月 28日目录第1章概述 (1)1.1 EDA的概念 (1)1.2 EDA技术及应用 (2)1.3 EDA技术发展趋势 (2)1.4 Quartus II特点介绍 (3)第2章硬件描述语言——VHDL (4)2.1 VHDL的简介 (4)2.2 VHDL语言的特点 (4)2.3 VHDL的设计流程 (5)第3章 8-3优先编码器的设计 (6)3.1 编码器的工作原理 (6)3.2 8-3优先编码器的设计 (6)3.3 8-3优先编码器仿真及分析 (7)3.4 在实验箱上实现8-3优先编码器 (8)结论 (11)参考文献 (12)第1章概述1.1EDA的概念EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程在计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA 技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

EDA 设计可分为系统级、电路级和物理实现级。

EDA是电子技术设计自动化,也就是能够帮助人们设计电子电路或系统的软件工具。

该工具可以在电子产品的各个设计阶段发挥作用,使设计更复杂的电路和系统成为可能。

在原理图设计阶段,可以使用EDA中的仿真工具论证设计的正确性;在芯片设计阶段,可以使用EDA中的芯片设计工具设计制作芯片的版图;在电路板设计阶段,可以使用EDA中电路板设计工具设计多层电路板。

特别是支持硬件描述语言的EDA工具的出现,使复杂数字系统设计自动化成为可能,只要用硬件描述语言将数字系统的行为描述正确,就可以进行该数字系统的芯片设计与制造。

21世纪将是EDA技术的高速发展期,EDA技术将是对21世纪产生重大影响的十大技术之一。

?硬件描述语言?:?硬件描述语言(HDL)是一种用于进行电子系统硬件设计的计算机高级语言,它采用软件的设计方法来描述电子系统的逻辑功能、电路结构和连接形式。

?常用硬件描述语言有HDL、Verilog和VHDL语言。

[1]1.2 EDA技术及应用EDA在教学、科研、产品设计与制造等各方面都发挥着巨大的作用。

在教学方面,几乎所有理工科(特别是电子信息)类的高校都开设了EDA课程。

主要是让学生了解EDA的基本概念和基本原理、掌握用HDL语言编写规范、掌握逻辑综合的理论和算法、使用EDA工具进行电子电路课程的实验并从事简单系统的设计。

一般学习电路仿真工具(如EWB、PSPICE)和PLD开发工具(如Altera/Xilinx的器件结构及开发系统),为今后工作打下基础。

在产品设计与制造方面,包括前期的计算机仿真,产品开发中的EDA工具应用、系统级模拟及测试环境的仿真,生产流水线的EDA技术应用、产品测试等各个环节。

如PCB的制作、电子设备的研制与生产、电路板的焊接、ASIC的流片过程等。

从应用领域来看,EDA技术已经渗透到各行各业,如上文所说,包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA有应用。

另外,EDA软件的功能日益强大,原来功能比较单一的软件,现在增加了很多新用途。

如AutoCAD软件可用于机械及建筑设计,也扩展到建筑装璜及各类效果图,汽车和飞机的模型、电影特技等领域。

[2]1.3 EDA技术发展趋势印度正在成为电子设计自动化领域发展最快的两个市场,年夏合增长率分别达到了50%和30%。

EDA技术发展迅猛,完全可以用日新月异来描述。

EDA技术的应用广泛,现在已涉及到各行各业。

EDA水平不断提高,设计工具趋于完美的地步。

EDA市场日趋成熟,但我国的研发水平仍很有限,尚需迎头赶上。

EDA技术在进入21世纪后,由于更大规模的FPGA器件的不断推出,在仿真和设计两方面支持标准硬件描述语言的功能强大的EDA软件不断更新、增加,使电子EDA技术得到了更大的发展。

电子技术全方位纳入EDA 领域,EDA使得电子领域各学科的界限更加模糊,更加互为包容,突出表现在以下几个方面:使电子设计成果以自主知识产权的方式得以明确表达和确认成为可能;基于EDA工具的ASIC设计标准单元已涵盖大规模电子系统及IP核模块;软硬件IP核在电子行业的产业领域、技术领域和设计应用领域得到进一步确认;SoC高效低成本设计技术的成熟。

随着半导体技术、集成技术和计算机技术的迅猛发展,电子系统的设计方法和设计手段都发生了很大的变化。

可以说电子EDA技术是电子设计领域的一场革命。

传统的“固定功能集成块十连线”的设计方法正逐步地退出历史舞台,而基于芯片的设计方法正成为现代电子系统设计的主流。

作为高等院校有关专业的学生和广大的电子工程师了解和掌握这一先进技术是势在必行,这不仅是提高设计效率的需要,更是时代发展的需求,只有掌握了EDA技术才有能力参与世界电子工业市场的竞争,才能生存与发展。

随着科技的进步,电子产品的更新日新月异,EDA技术作为电子产品开发研制的源动力,已成为现代电子设计的核心。

所以发展EDA技术将是电子设计领域和电子产业界的一场重大的技术革命,同时也对电类课程的教学和科研提出了更深更高的要求。

特别是EDA 技术在我国尚未普及,掌握和普及这一全新的技术,将对我国电子技术的发展具有深远的意义。

在EDA软件开发方面,目前主要集中在美国。

但各国也正在努力开发相应的工具。

日本、韩国都有ASIC设计工具,但不对外开放。

中国华大集成电路设计中心,也提供IC设计软件,但性能不是很强。

相信在不久的将来会有更多更好的设计工具在各地开花并结果1.4 Quartus II特点介绍Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式[3]。

具有运行速度快,界面统一,功能集中,易学易用等特点。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

对第三方EDA工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统(SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台。

Maxplus II 作为Altera的上一代PLD设计软件,由于其出色的易用性而得到了广泛的应用。

目前Altera已经停止了对Maxplus II 的更新支持,Quartus II 与之相比不仅仅是支持器件类型的丰富和图形界面的改变[7]。

Altera在Quartus II 中包含了许多诸如SignalTap II、Chip Editor和RTL Viewer的设计辅助工具,集成了SOPC和HardCopy设计流程,并且继承了Maxplus II 友好的图形界面及简便的使用方法。

Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

[4]第2章硬件描述语言——VHDL2.1VHDL的简介VHDL语言是一种用于电路设计的高级语言。

它在80年代的后期出现。

最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。

但是,由于它在一定程度上满足了当时的设计需求,于是他在1987年成为A I/IEEE的标准(IEEE STD1076-1987)。

1993年更进一步修订,变得更加完备,成为A I/IEEE的A I/IEEE STD 1076-1993标准。

目前,大多数的CAD厂商出品的EDA软件都兼容了这种标准。

VHDL的英文全写是:VHSIC(Very High eed Integrated Circuit)Hardware Descriptiong Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

[5]2.2 VHDL语言的特点VHDL是一种用普通文本形式设计数字系统的硬件描述语言,主要用于描述数字系统的结构、行为、功能和接口,可以在任何文字处理软件环境中编辑。

除了含有许多具有硬件特征的语句外,其形式、描述风格及语法十分类似于计算机高级语言。

VHDL程序将一项工程设计项目(或称设计实体)分成描述外部端口信号的可视部分和描述端口信号之间逻辑关系的内部不可视部分,这种将设计项目分成内、外两个部分的概念是硬件描述语言(HDL)的基本特征。