VHDL基础入门学习

- 格式:pdf

- 大小:1.01 MB

- 文档页数:64

vhdl基础及经典实例开发pdf VHDL是一种硬件描述语言,它用于描述和设计数字电路。

VHDL的全称是Very High Speed Integrated Circuit Hardware Description Language,它源于20世纪80年代的美国国防部,是一种为了描述硬件而设计的开发语言。

VHDL的基础知识包括语法、数据类型和结构体。

语法方面,VHDL 有自己的语法规则和词法规则,要正确地描述一个硬件电路,我们需要熟悉这些规则。

数据类型方面,VHDL内置了基本的数据类型,如bit、bit vector、integer等,这些数据类型可以用来描述电路的输入输出和中间信号。

结构体方面,VHDL支持设计者自定义类型,比如用record来描述一个复杂的数据结构。

在VHDL开发中,经典实例是不可或缺的。

经典实例可以帮助我们更好地理解VHDL的使用方法和特点,也可以让我们更好地掌握VHDL的编程技巧。

下面是一些经典实例的介绍。

1.二进制加法器(Binary Adder):二进制加法器可以实现两个二进制数的加法运算。

它是数字电路中常用的基本模块,很多其他的电路都需要用到它。

通过构建一个二进制加法器的实例,我们可以学习到VHDL的语法规则、数据类型的使用以及模块化设计的思想。

2.时钟分频器(Clock Divider):时钟分频器可以将输入的时钟信号分频为较低频率的信号。

在数字电路中,时钟分频器是非常常见的一个模块,它可以用于控制其他电路的时序。

通过构建一个时钟分频器的实例,我们可以学习到VHDL的状态机设计、时序逻辑的实现以及对时钟信号的处理。

3.多路选择器(Multiplexer):多路选择器可以根据选择信号选择其中的一个输入信号输出。

在数字电路中,多路选择器可以用于实现多个输入的选择和切换。

通过构建一个多路选择器的实例,我们可以学习到VHDL的条件语句的使用、信号赋值的方法以及对多个输入信号的处理。

VHDL入门教程VHDL(Very High-Speed Integrated Circuit HardwareDescription Language)是一种硬件描述语言,用于设计数字电路和系统。

它是由美国国防部在20世纪80年代早期开发的,并由IEEE 1076标准化。

VHDL可以用于描述电路结构、电路行为和模拟。

一、VHDL概述VHDL是一种硬件描述语言,它允许工程师以更高级的语言编写硬件描述。

它可以描述电路结构、电路行为和模拟。

VHDL可以应用于各种电子系统的设计,从简单的数字逻辑门到复杂的处理器。

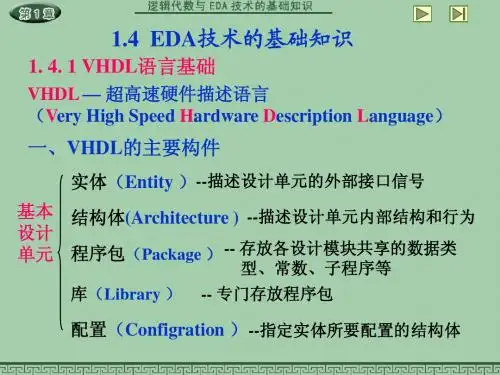

二、VHDL基本结构VHDL的基本结构包括实体声明、体声明和结构化代码。

实体声明描述了电路的接口,包括输入和输出。

主体声明描述了电路的行为。

结构化代码定义了电路的结构。

三、VHDL数据类型VHDL提供了多种数据类型,包括标量类型(比如整数和实数)、数组类型和记录类型。

每种类型都有其特定的操作和范围。

四、VHDL信号VHDL中的信号用于在电路中传递信息。

信号可以在过程中赋值,并且具有各种延迟属性。

信号还可以连接到模块的输入和输出端口,以实现电路之间的通信。

五、VHDL实体和体VHDL设计包含实体和体。

实体描述了电路的接口和连接,而体描述了电路的行为。

实体和体之间使用端口来传递信息。

六、VHDL组件VHDL中的组件用于将电路模块化,以实现更高层次的设计和复用。

组件可以在实体中声明,并在体中实例化。

七、VHDL并发语句VHDL中的并发语句用于描述电路中多个同时运行的过程。

并发语句包括并行语句、过程、并行块和并行时钟。

八、VHDL测试VHDL测试包括自动测试和手动测试。

自动测试使用测试工具和仿真器来验证电路的正确性。

手动测试包括使用仿真器进行手工测试和调试。

九、VHDL实例以下是一个简单的VHDL实例,实现了一个4位二进制加法器:```vhdllibrary IEEE;use IEEE.STD_LOGIC_1164.all;entity binary_adder isporta : in std_logic_vector(3 downto 0);b : in std_logic_vector(3 downto 0);sum : out std_logic_vector(4 downto 0);carry : out std_logicend binary_adder;architecture behavior of binary_adder isbeginprocess(a, b)variable temp_sum : std_logic_vector(4 downto 0);variable temp_carry : std_logic;begintemp_sum := ("0000" & a) + ("0000" & b);temp_carry := '0' when temp_sum(4) = '0' else '1';sum <= temp_sum;carry <= temp_carry;end process;end behavior;```上述VHDL代码定义了一个名为`binary_adder`的实体,它有两个4位输入`a`和`b`,一个5位输出`sum`和一个单一位输出`carry`。

第1章VHDL语言基础1.1 概述硬件描述语言(hardware description language,HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。

目前,利用硬件描述语言可以进行数字电子系统的设计。

随着研究的深入,利用硬件描述语言进行模拟电子系统设计或混合电子系统设计也正在探索中。

国外硬件描述语言种类很多,有的从Pascal发展而来,也有一些从C语言发展而来。

有些HDL成为IEEE标准,但大部分是企业标准。

VHDL来源于美国军方,其他的硬件描述语言则多来源于民间公司。

可谓百家争鸣,百花齐放。

这些不同的语言传播到国内,同样也引起了不同的影响。

在我国比较有影响的有两种硬件描述语言:VHDL语言和Verilog HDL语言。

这两种语言已成为IEEE标准语言。

电子设计自动化(electronic design automation,EDA)技术的理论基础、设计工具、设计器件应是这样的关系:设计师用硬件描述语言HDL描绘出硬件的结构或硬件的行为,再用设计工具将这些描述综合映射成与半导体工艺有关的硬件配置文件,半导体器件FPGA 则是这些硬件配置文件的载体。

当这些FPGA器件加载、配置上不同的文件时,这个器件便具有了相应的功能。

在这一系列的设计、综合、仿真、验证、配置的过程中,现代电子设计理论和现代电子设计方法贯穿于其中。

以HDL语言表达设计意图,以FPGA作为硬件实现载体,以计算机为设计开发工具,以EDA软件为开发环境的现代电子设计方法日趋成熟。

在这里,笔者认为,要振兴我国电子产业,需要各相关专业的人士共同努力。

HDL语言的语法语义学研究与半导体工艺相关联的编译映射关系的研究,深亚微米半导体工艺与EDA设计工具的仿真、验证及方法的研究,这需要半导体专家和操作系统专家共同努力,以便能开发出更加先进的EDA工具软件。

软件、硬件协同开发缩短了电子设计周期,加速了电子产品更新换代的步伐。

毫不夸张地说,EDA工程是电子产业的心脏起搏器,是电子产业飞速发展的原动力。

VHDL语言入门教程VHDL是一种硬件描述语言,主要用于设计数字电路和系统。

它是由美国国防部门于1980年代初开发的,目的是为了改进电子设计自动化(EDA)工具的开发效率和设计文档的可重复性。

VHDL广泛应用于数字信号处理(DSP)、嵌入式系统、通信系统和各种ASIC(专用集成电路)和FPGA(现场可编程门阵列)的设计。

本教程将介绍VHDL的基础知识,包括语法、数据类型和常见的建模技术。

一、VHDL的语法VHDL的语法由标识符、关键字、运算符和分隔符组成。

其中,标识符用于给变量、信号和实体命名,关键字用于定义语言特定的操作,运算符用于数学和逻辑运算,分隔符用于分隔语句。

VHDL中的代码以一个实体(entity)的声明开始,然后是体(architecture)的声明,最后是信号声明和进程(process)的描述。

以下是一个简单的例子:```vhdlentity AND_gate isportA, B: in std_logic;C: out std_logicend entity AND_gate;architecture Behavior of AND_gate isbeginC <= A and B;end architecture Behavior;```在这个例子中,我们声明了一个名为AND_gate的实体,它有两个输入信号A和B,一个输出信号C。

然后我们定义了一个名为Behavior的体,它描述了AND门的行为:C等于A与B的逻辑与运算结果。

二、VHDL的数据类型VHDL支持许多数据类型,包括标量类型、数据类型、自定义类型和引用类型。

标量类型包括bit、bit_vector、integer、real、std_logic和std_ulogic等。

其中,bit_vector是一组连续的位,std_logic和std_ulogic用于表示单个信号。

数据类型是由标量类型和数组类型组成的。

数组类型可以是一维、二维或更高维的,用于存储多个数据。

VHDL语言简介VHDL语言翻译成中文就是超高速集成电路硬件描述语言,主要是应用在数字电路的设计中。

目前,它在中国的应用多数是用在FPGA/CPLD/EPLD的设计中。

当然在一些实力较为雄厚的单位,它也被用来设计ASIC。

VHDL主要用于描述数字系统的结构,行为,功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

VHDL语言简例VHDL设计实体的组成:库和程序包(Library,Package),实体(Entity),结构体(Architecture),配置(Configuration).--- VHDL Examplelibrary ieee;use ieee.std_logic_1164.all; --库声明entity TONE isport(A,B:in std_logic; --实体定义C:out std_logic);end TONE;architecture EX of TONE is --结构体定义beginC<=A OR B;end EX;VHDL不区分大小写VHDL基础知识VHDL设计实体的组成:库和程序包(Library,Package),实体(Entity),结构体(Architecture),配置(Configuration).例:用VHDL语言设计一个2选1的数据选择器entity mux21 isport(a,b:in bit;s:in bit;y:out bit);end entity mux21;architecture one of mux21 issignal d,e:bit;begind<=a and (not s); --左边三行可以用下面的语句代替。

第二章 VHDL基本数据类型与命令语句 第二章 VHDL基本数据类型与命令语句2.1 VHDL基本数据类型 2.2 VHDL数据对象定义 2.3 并行同时语句( When-Else, With-Select ) 2.4 顺序语句一(Process,If-Else,Wait) 2.5 顺序语句二(Case-When,Null)12.1 基本数据类型 (逻辑信号、数值信号) 在VHDL中每一个数据对象都必须具有确 定的数据类型。

只有在相同数据类型的数据对 象之间,才能进行数据交换。

⑴ ⑵ ⑶ ⑷ ⑸ 布尔代数数据类型(BOOLEAN); 位逻辑数据类型(BIT); 位逻辑序列数据类型(BIT_VECTOR); 标准逻辑数据类型(STD_LOGIC); 标准逻辑序列数据类型(STD_LOGIC _VECTOR);2⑹ ⑺ ⑻ ⑼ ⑽整数数据类型(INTEGER); 实数数据类型(REAL); 字符串数据类型(STRING); 字符数据类型(CHARACTER); 无符号整数数据类型(UNSIGNED);今后在逻辑设计中最常用到两种:标准逻辑 数据类型 STD_LOGIC 和标准逻辑序列数据类型 STD_LOGIC _VECTOR。

其语法格式:在实体中是跟在端口模式 (方 向) 后面,在结构体中是跟在数据对象后面。

32.1.1 逻辑信号的数据类型 ⑴ 布尔代数数据类型(BOOLEAN) 布尔代数数据类型(BOOLEAN)属于双值数据 类型,其值只有“TRUE”(真)、“FALSE”(假) 两种 状态,常用来表示关系运算和关系运算的结果。

⑵ 位逻辑数据类型(BIT) 位逻辑数据类型(BIT)也属于双值数据类型, 其值只有 ‘ 1 ’、 ' 0 ' (用单引号表示)两种状态,常 用来表示某一管脚的逻辑值。

4⑶ 标准逻辑数据类型(STD_LOGIC) 标准逻辑数据类型 (STD_LOGIC) 也属于双值 数据类型,但它比“BIT”对于数字逻辑电路的逻辑 特性的描述更完整、更真实。

因此在VHDL中通常 都是采用这种数据类型。

它的取值共有九种形式: ① ' U ' —— 初始值; ② ' X ' —— 不定值; ③ ' 0 ' —— 低电位0; ④ ' 1 ' —— 高电位1; ⑤ ' Z ' —— 高阻抗; ⑥ ' W ' —— 弱信号不定值; ⑦ ' L ' —— 弱信号0; ⑧ ' H' —— 弱信号1; ⑨ ' – ' —— 不可能情况,不必理会。

5⑷ 标准逻辑序列数据类型(STD_LOGIC_VECTOR) 标准逻辑序列数据类型 (STD_LOGIC_ VECTOR) 也属于双值数据类型,但它描述 的是一组序列信号的数据类型。

如:数据总 线、地址总线等(排线)上面的数值。

⑸ 位逻辑序列数据类型(BIT_VECTOR) 位逻辑序列数据类型 (BIT_VECTOR) 也 属于双值数据类型,其值只有"1"、"0" (用双 引号表示) 两种状态,常用来表示某一组管脚 的位逻辑值。

6⑹ 逻辑信号的运算 配合逻辑信号的基本运算符,通常包含有两种: ① 逻辑运算符and与门or或门nand与非门nor或非门xor异或门xnor同或门not非门② 关系运算符=等于/=不等于<小于<=小于等于>大于>=大于等于注意:“<=”符号与赋值符号相同,由上下文来区别。

72.1.2 数值信号的数据类型 ⑴ 整数数据类型(Integer) 整数数据类型的数有正整数、负整数和0,在 VHDL中其取值范围是 -2147483647~2147483646。

即: ( −2 31 ) ~ ( 2 31 − 1) 。

⑵ 无符号整数数据类型(UNSIGNED); 无符号整数数据类型的数与标准逻辑序列相 似,定义时也必须指明这个无符号整数的位数。

[例1] 假若A中的内容是3(11)2,B中的内容是2(10)2,试 分析下程序运行后,C和D中的内容是多少?8LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CH2_1_3 PORT(A : B C D END CH2_1_3; is IN Std_Logic_Vector(1 DOWNTO 0); : IN Unsigned(1 DOWNTO 0); : OUT Unsigned(7 DOWNTO 0); : OUT Std_Logic_Vector(1 DOWNTO 0));ARCHITECTURE a OF CH2_1_3 IS SIGNAL E,F,G : Unsigned(1 DOWNTO 0); SIGNAL H : Unsigned(7 DOWNTO 0);9BEGIN E <= Unsigned (A); F <= B; H(1 DOWNTO 0) <= E+F; H(3 DOWNTO 2) <= E-F; H(7 DOWNTO 4) <= E*F; G(0) <= E(0) AND F(0); G(1) <= E(1) OR F(1); C <= H; D <= Std_Logic_Vector (G); END a;--(1) --(2) --(3) --(4) --(5) --(6) --(7) --(8) --(9)因为A中的内容是3(11)2,B中的内容是2(10)2,故: ① E <=Unsigned (A) 后, E=3 (11)2 ; ② F <= B 后, F=2 (10)2 ;10BEGINE <= Unsigned (A);--(1)F <= B;--(2)H(1 DOWNTO 0) <= E+F; --(3)H(3 DOWNTO 2) <= E-F; --(4)H(7 DOWNTO 4) <= E*F; --(5)G(0) <= E(0) AND F(0); --(6)G(1) <= E(1) OR F(1);--(7)C <= H;--(8)D <= Std_Logic_Vector(G);--(9) END a;BEGINE <= Unsigned (A);--(1)F <= B;--(2)H(1 DOWNTO 0) <= E+F; --(3)H(3 DOWNTO 2) <= E-F; --(4)H(7 DOWNTO 4) <= E*F; --(5)G(0) <= E(0) AND F(0); --(6)G(1) <= E(1) OR F(1);--(7)C <= H;--(8)D <= Std_Logic_Vector(G);--(9) END a;BEGINE <= Unsigned (A);--(1)F <= B;--(2)H(1 DOWNTO 0) <= E+F; --(3)H(3 DOWNTO 2) <= E-F; --(4)H(7 DOWNTO 4) <= E*F; --(5)G(0) <= E(0) AND F(0); --(6)G(1) <= E(1) OR F(1);--(7)C <= H;--(8)D <= Std_Logic_Vector(G);--(9) END a;BEGINE <= Unsigned (A);--(1)F <= B;--(2)H(1 DOWNTO 0) <= E+F; --(3)H(3 DOWNTO 2) <= E-F; --(4)H(7 DOWNTO 4) <= E*F; --(5)G(0) <= E(0) AND F(0); --(6)G(1) <= E(1) OR F(1);--(7)C <= H;--(8)D <= Std_Logic_Vector(G);--(9) END a;A中的内容是3(11)2,B中的内容是2(10)2,仿真的结果是:C中的内容为65,D中的内容为2。

注意1、无符号整数(Unsigned)与标准逻辑序列(Std_Logic_Vector)信号之间是可以作转换的;2、无符号整数(Unsigned)信号的序列编号是由高至低的,所以一定要使用Downto的序列形式来定义。

Constant 常数名称:数据类型:= 设置值;注意:设置值一旦设定,就不能再更改。

Signal 信号名[,信号名…]: 数据类型[:=表达式];LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CH2_2_1 isPORT( A : IN Std_Logic;B : IN Std_Logic;C : IN Std_Logic;F : OUT Std_Logic); END CH2_2_1;ABCDEFARCHITECTURE a OF CH2_2_1 IS SIGNAL D, E : Std_Logic;BEGIND <= A and B;--A 与B 后送入DE <= not C;--将C 取非后送入EF <= D or E;--D 或E 后送到FEND a;AB C D E FVariable 变量名[,变量名…]: 数据类型[:=表达式];补充:信号和变量的区别LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CH2_2_2 isPORT( IP : IN Std_Logic;CP : IN Std_Logic;OP : OUT Std_Logic);END CH2_2_2;ARCHITECTURE a OF CH2_2_3 ISSignal D: Std_Logic;BEGINProcess (CP,IP) --(1) BeginIF CP'EVENT AND CP ='1' THEN --(2)D <= IP ; --(3)OP <= D ; --(4) END IF ;End Process ;END a;ARCHITECTURE a OF CH2_2_3 ISSignal D: Std_Logic;BEGINProcess (CP,IP) --(1) BeginIF CP'EVENT AND CP ='1' THEN --(2)D <= IP ; --(3)OP <= D ; --(4) END IF ;End Process ;END a;将IP的变化暂存延迟了一个周期左右的时间后才传递到了变量D。