实验七报告-双面印制电路板设计

- 格式:docx

- 大小:240.23 KB

- 文档页数:19

《双面印制电路板制作》课程实验教学内容的研究与实践双面印制电路板的设计与制作是电子科技大学应用化学专业开设的核心实验课程之一,也是全校的公选实验课程,受到学校微电子、集成电路、通讯工程等专业学生广泛欢迎。

实验主要有钻孔、孔金属化、图形转移、线路制作和线路保护技术以及印制板检测技术等内容。

该实验让学生对于现代印制电路产业的工艺流程有了较为具体、形象的了解,并能自己制作成品的电路板,同时也能为学生以后可能的就业方向提供一定的支持,因此学生对该实验有浓厚的兴趣。

标签:印制电路;双面板;钻孔1引言我校应用化学专业是我国目前唯一培养电子技术与化学技术相结合的综合性高科技人才的专业,着重培养在信息产业重要组成部分的电子工艺技术领域的高技术人才[1],而印制电路工艺作为其中一门必不可少的课程,将化学知识与电子工艺结合在一起,培养学生的动手能力和创新能力。

印制电路(printed circuit board 即PCB)是一种新的互连工艺技术,它革新了电子产品的结构工艺和产品的组装工艺。

印制电路工艺技术总的发展方向是高密度、高精度、高可靠性、大面积、细线条,而基础又在印制技术、化学工艺、精密机械加工、光学技术、CAD技术及新材料等各种技术的不断提高与发展[2]。

电子科技大学拥有全国高校第一个印制电路制造工艺平台。

利用该平台开设的印制电路课程的实验教学旨在激发学生对印制电路制造的兴趣,提高学习的积极性,初步了解印制电路工艺的制造流程,了解将来工作的方向性。

我们特别注重实验环节对学生专业知识的巩固与创新能力、实际动手能力的培养。

下面将本课程实验内容介绍如下。

2实验课程内容印制电路工艺技术不断发展,制造方法有若干种,基本上分为两大类:减成法和加成法。

本实验主要应用传统的减成法制作双面印制电路板。

双面印制电路板制作主要工艺流程如图1所示。

图1:双面印制电路板制作主要工艺流程图2.1钻孔。

本实验采用的数控机械钻孔是在电脑的控制下利用不同直径的钻头按相应的工艺参数(钻数、进刀速率、退刀速率)在印制电路板上得到所需的导通孔。

实习报告-印制电路板的制作与检测-3000字我来到大连XXX有限电子公司进行为期10周的实习培训。

这里充满了和谐与朝气,充满了团结与智慧。

本公司大连XX电子有限公司(简称:大连XX)主要从事二极管、MOSFET、肖特基等电子元器件的专业生产,以及PCB板的制作。

公司总部设在辽宁大连庄河市,大连XX电子有限公司的诚信、实力和产品质量获得业界的认可。

我的实习岗位是熟练运用protel制图软件并制成PCB板,并检验出制成的板质量是否合格。

也就是进行PCB板的制作与维护。

1. 印制电路板的制作实习过程中,我首先进行印制电路板的制作,具体步骤如下:第一步,使用Protel设计PCB板。

首先,新建原理图库文件并设计:先要点击【Document】选择【schematic library】,在原来的库里找到类似的进行编辑修改,这样比较省时省力一些。

找到相似的元件后我要注意,要把粘贴到【schematic library】里面进行的引脚等其他部分进行编辑和修改。

设计完成后保存,回到【schematic document】中,找到自己做好的元件双击添加。

其次,新建原理图文件并设计:打开Protel 软件点击【New document】选择【schematic Document】,新建一个原理图纸,设置原理图图纸大小为“A4”。

然后回到建好的原理图图纸页面,在任意位置,双击页面对照图纸来选择相应的符号,在原理图页面对照图纸画好原理图,双击的标示改好。

在画原理图的时候特别要注意,导线的节点不能忘记标注,要修改属性,检查电气规则等。

原理图中的集成电路,有些在库中找不到,需要自己画好添加到库中然后调用到原理图上。

然后,新建PCB文件并设计。

在【New document】选择【PCB document】,将工作层面调至Keep Out Layer,并画出电路板电气边界。

生成网络表后,打开网络表点击以NET结尾的文件进行检查,检查错误,直到修改无误把焊盘修改为合适大小。

印制电路板制作实习报告:篇一:电路板设计制作实习报告电路板设计制作实习报告一、实习200x.1.2——200x.1.11二、实习地点:xx工业大学电气楼三、指导老师:四、实习目的:通过二个星期的电子实习,对绘制原理图pcb图打印曝光显影腐蚀钻孔焊接门铃电路工作原理等有了一个基本的了解,对制作元器件收音机的装机与调试有一定的感性和理性认识,打好了日后学习计算机硬件基础。

同时实习使我获得了收音机的实际生产知识和装配技能,培养了我理论联系实际的能力,提高了我分析问题和解决问题的能力,增强了独立工作的能力。

1.熟悉手工焊锡常用工具的使用及其维护与修理。

2.基本掌握手工电烙铁的焊接技术,能够独立的完成简单电子产品的安装与焊接。

熟悉电子产品的安装工艺的生产流程。

3.熟悉印制电路板设计的步骤和方法,熟悉手工制作印制电板的工艺流程,能够根据电路原理图,元器件实物设计并制作印制电路板。

4.熟悉常用电子器件的类别、型号、规格、性能及其使用范围,能查阅有关的电子器件图书。

5.能够正确识别和选用常用的电子器件,并且能够熟练使用普通万用表。

.了解电子产品的焊接、调试与维修方法。

五、实习内容:1.用protel绘制作品的原理图.pcb图打印曝光2.显影腐蚀钻孔焊接门铃电路测试验收3.收音机的焊接组装测试与验收4.实习结束,写实习报告六、焊接顺序与辨认测量辨认测量:①学会了怎样利用色环来读电阻,然后用万用表来验证读数和实际情况是否一致,再将电阻别在纸上,标上数据,以提高下一步的焊接速度;②学会了怎样测量二极管及怎样辨认二极管的“+”,“—”极,③学会了怎样利用万用表测量三极管的放大倍数,怎样辨认三极管的“b”,“e”,“c”的三个管脚;④学会了电容的辨认及读数,“╫”表示元片电容,不分“+”、“—”极;“┥┣+”表示电解电容(注意:电解电容的长脚为“+”,短脚为“—”)。

焊接顺序:①焊接中周,为了使印刷电路板保持平衡,我们需要先焊两个对角的中周,在焊接之前一定要辨认好中周的颜色,以免焊错,千万不要一下子将四个中周全部焊在上面,这样以后的小元件就不好安装→②焊接电阻,前面我们已经将电阻别在纸上,我们要按r1——r13的顺序焊接,以免漏掉电阻,焊接完电阻之后我们需要用万用表检验一下各电阻是否还和以前的值是一样(检验是否有虚焊)→③焊接电容,先焊接元片电容,要注意上面的读数(要知道223型元片电阻&103型元片电阻的区别,元片电容的读数方法——前两数字表示电容的值,后面的数字表示零的个数),紧接着就是焊电解电容了,特别要注意长脚是“+”极,短脚是“—”极→④焊接二极管,红端为“+”,黑端为“—”→⑤焊接三极管,一定要认清“e”,“b”,“c”三管脚按放大倍数从大到小的顺序焊接)→⑥剩下的中周和变压器及开关都可以焊了→⑦最需要细心的就是焊接天线线圈了,用四根线一定要按照电路图准确无误的焊接好→⑧焊接印刷电路板上“”状的间断部分,我们需要用焊锡把它们连接起来→⑨焊接喇叭和电池座。

实习报告一、前言随着电子科技的飞速发展,印制电路板(PCB)作为电子设备的基础板卡,其设计质量和效率对整个电子产品的性能和可靠性具有重要影响。

本次实习,我有幸加入一家专业的PCB设计公司,通过为期三个月的实习,深入了解了PCB设计的全过程,掌握了相关软件的使用技巧,并提高了自己的工程实践能力。

二、实习内容1. 学习PCB设计基础知识:在实习初期,我通过阅读相关书籍和资料,学习了PCB设计的基本概念、原理和流程。

了解了不同类型的PCB设计,如单层PCB、双层PCB和多层PCB,以及它们的优缺点。

2. 熟悉设计软件:在实习过程中,我熟练掌握了Altium Designer、Cadence等PCB设计软件的使用。

通过实际操作,学会了如何绘制原理图、布线、创建元件封装、生成Gerber文件等。

3. 参与实际项目:在导师的指导下,我参与了公司的一个实际项目,负责部分PCB的设计和制作。

在项目过程中,我学会了如何与团队成员沟通协作,如何根据项目需求制定合理的设计方案,以及如何解决设计过程中遇到的问题。

4. 学习PCB制作工艺:为了更好地理解PCB设计,我参观了公司的生产线,了解了PCB制作的整个工艺流程,包括印刷、腐蚀、覆铜、钻孔、贴片等环节。

这使我更加明确了设计过程中的注意事项,提高了设计的可靠性。

5. 参加培训和交流:在实习期间,公司组织了多次培训和交流活动,邀请了行业专家分享PCB设计经验和最新技术。

我积极参与这些活动,拓宽了自己的视野,学到了许多宝贵的经验。

三、实习收获1. 技能提升:通过实习,我掌握了PCB设计的基本知识和技能,能够独立完成简单的PCB设计任务。

2. 工程实践能力:在实际项目中,我学会了如何将理论知识应用到实际设计中,提高了自己的工程实践能力。

3. 团队协作:在项目过程中,我学会了与团队成员有效沟通,共同解决问题,提高了自己的团队协作能力。

4. 行业认知:通过实习,我对PCB行业有了更深入的了解,为将来就业和发展奠定了基础。

印制电路板实训(实验)报告系别:物理与电子工程系专业:印制电路技术与工艺班级:2011级???班姓名:???(2011070???)实训(实验)报告系别物理与电子工程系专业印制电路技术与工艺方向班级2011级??班实验地点印制电路实验室2207姓名???学号201107??时间201?年??月??日指导教师李、吴王、张一、实训目的1、了解制作二、四层电路板原理。

2、掌握基本的数据处理;3、掌握电化学孔金属化法的原理;4、熟悉二层、四层或更多层印制电路板工艺流程。

5、学会并掌握印制电路各设备的使用方法。

二、实训设备电脑1台LPKF Protomat S63电路板刻制机1台覆膜机1台LPKF MultiPress S层压机1台刷版机1台紫外曝光机1台激光绘图机1台孔金属化机1台蚀刻机1台去膜机1台显影机1台气泵枪1台三、制版步骤Ⅰ、准备工作(数据处理):连接各硬件及配套设施、设置好电脑COM通讯端口,安装软件并配置好软件及机器参数;从EDA或CAD软件中导出Gerber数据:需要注意各种数据类型对应含义:Ⅱ、制作二层电路板流程:主要流程:cbf文件的导入→打靶标、打孔→刷板→孔金属化(除油、预处理、沉碳、电镀)→刷板→覆干膜→曝光→显影→蚀刻→去膜→裁板具体如下:1、将需要用到的机器提前开机预热。

2、从EDA或CAD软件中导出Gerber数据;3、打孔①、打开LPKF CircuitPro软件,之后操作如下:File-Open-二层板cbf文件,Edit-Material Settings,在Materialtkickness对应的栏目中修改板子厚度(设二层板厚度为1.8mm),在工具栏中单击Technology Dialog,单击Show Details,在Tool栏目中修改裁刀,裁刀修改为Contour Routing 1mm,单击Start,然后单击Close,单击工具栏Opens the dialog to edit of the tool magazine,查看配刀的情况(‘√’表示刀已配好,否则表示缺少此刀,此时就得在打孔机上配好此大小的刀)。

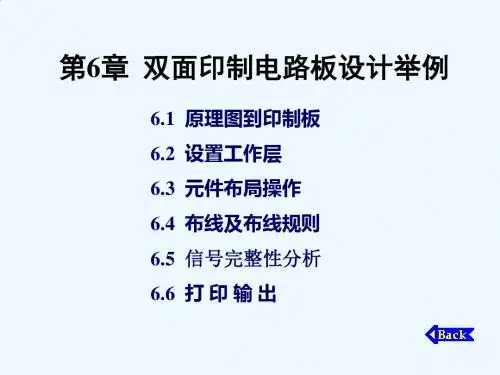

实验报告实验七、双面印制电路板设计一、实验目的1、掌握双面印制电路板的设计过程与步骤。

2、熟悉印制电路板设计程序的工作环境与工作参数设置。

3、掌握印制电路板的设计规则设置的方法。

4、比较单面板与双面设计的异同。

5、要求做到能设计出较高质量的印制电路板。

二、实验原理简述根据给出的电路图,设计双面板一块。

设计的注意事项与关键环节同上一实验类似。

主要区别在于:跟单面板比较,对于稍复杂的电路,因单面板布线受限于一面之内,有些线可能布不通,或布线效果不理想,此时可考虑采用双面板设计;双面板使用两面布线(Top Layer和Bottom Layer),而单面板只使用一面布线(Bottom Layer);双面板中可能有过孔存在,而单面板中没有过孔存在;双面板的布通率通常要比单面板的布通率要高,走线更方便;但就机械加工成本来看,双面板的制作费用高于单面板。

在实际工程中,到底是使用几层板,要看具体情况。

本实验给出的电路比较简单(限于指导书的纸张小,无法给出较复杂的图纸),但也要求根据该简单电路设计出双面板,因为主要的目的是要求读者掌握双面板的设计过程,理解双面板与单面板设计的主要区别。

三、实验内容与主要步骤1、绘制电路图,输入每个电路封装形式,进行ERC电气规则检查。

2、生成该电路的网络表。

3、新建一个PCB文件(*.pcb)。

4、设置工作环境参数(工作环境参数也可不设置,采用默认参数即可)。

5、设置相对坐标原点(用命令Edit/Origin/Set)。

并在Keepout Layer层画线确定板子边框的尺寸与外形(若要精确按坐标定义板子的尺寸与形状,在画线时,配合使用J+L键进行)。

6、通过Design/Netlist命令,用网络表的形式调入PCB元件置工作界面(当然也可以在电路图SCH环境中,用同步器Design/Update PCB调入PCB元件,但建议使用网络表的形式)。

这一步要注意的是网络表不能有错误,否则要回到电路图中去修改,再次生成网络表并保存覆盖原有网络表,直到网络表正确为止。

7、PCB设计规则设置,用命令Design/Rules,对各种规则进行设置(如元件安全距离、走线角度、板层设置、布线优先级、布线技术算法、过孔、线宽等)。

规则较多,要求一定要理解各规则的含义和设置方法与技巧。

8、自动布局(用命令T ools/Auto Place)和手工布局。

一般自动布局很难达到理想的布局效果,一般要采用自动布局和手工调整布局相结合的形式,或干脆就不使用自动布局,而直接使用手工布局。

在布局时可使用排齐工具(或命令Tools/Align Components)来帮助进行调整。

因布局阶段对印制电路板设计是最为关键的环节,所以要求布局一定要符合规则(考虑的布局规则主要有:安全距离、信号流方向、总连线最短、插座的布置、核心元件的布置、数模混合电路的布置、高频元件的布置、抗干扰措施的安排、有利于工程安装、布局美观工整等)9、密度分析与DRC规则检查。

用命令Tools/Density Map进行密度图分析,看布局是否合理,否则回到上一步,继续进行调整。

并进行DRC规则检查。

10、自动布线规则设置(用命令Auto Route/Setup )与自动布线(用命令Auto Route/All,局部布线用Auto Route/Net(或Connection、Component、Area ))。

11、修改与调整。

(1)对布得不好的连线进行手工修改或调整。

(2)处理好电源线与地线(允许范围内,线尽可能粗些、短些)。

(3)元件标号与参数的位置与方向调整。

(4)若有些部分要求进行特殊处理的要进行特殊处理(如补泪滴、铺铜等)。

(5)放置工程安装螺钉孔。

(6)标注尺寸与坐标。

12、生成板子信息报表13、生成材料清单并与电路图的材料清单比较。

14、保存15、打印(在File/Setup Printer项设置参数)。

要求用分层(Final)打印方式,打印电路图、顶层(Top Layer)、底层(Bottom Layer)、丝印层(Silkscream)、焊盘层(Pad Master)、阻焊层与助焊层(Mask)。

D7图A 根据该图设计双面印制电路板四、实验报告要求1、截取实验图:图1 sch电路图图2 PCB电路板图3 顶层(Top Layer)打印截图图4 底层(Bottom Layer)打印截图图5 丝印层(Silkscream)打印截图图6 焊盘层(Pad Master)打印截图图7 阻焊层与助焊层(Mask)打印截图2、在实验原始数据记录栏中,填写本次实验所用到的PCB元件库名称、保存的文件的名称、网络表、板子信息报告表。

●PCB元件库名称:PCB Footprints.lib●保存的文件的名称:●网络表:[C1RAD0.20.5u][C2RAD0.21u][D1DIODE0.4 1N2156 ][D2 DIODE0.4 1N2156 ][D3 DIODE0.4 1N2156 ][D4 DIODE0.4 1N1695 ][D5 DIODE0.4 1N1695 ][D6 DIODE0.4 1N1695][D7 DIODE0.4 1N2156][JP2SIP44 HEADER ][JP3SIP44 HEADER ][Q1TO-92B SCR][Q2TO-92B SCR][Q3TO-92B SCR][Q4TO-39 UJT N][Q5TO-92A 2N2923 ][Q6TO-39 UJT N][R1 AXIAL0.3 25][R2 AXIAL0.3 25][R3 AXIAL0.3 25][R4 AXIAL0.3 100][R5 AXIAL0.3 3k3/2w][R6 AXIAL0.3 390][R7 AXIAL0.3 470][R8AXIAL0.3 100][R9 AXIAL0.3 390][VR1 AXIAL1.0 500VR][VR2 AXIAL1.0 10KVR ][VR3 AXIAL1.0 20KVR ][ZD1 DIODE0.7 ZENER2](GNDC1-2D7-2JP2-4JP3-3JP3-4Q1-2Q2-2Q3-2Q5-1Q6-2R4-1R8-1ZD1-1 )(NetD4_2 D4-2D5-2D6-2R5-1R9-2)(NetJP2_1 D1-2D4-1JP2-1Q1-1)(NetJP2_2 D2-2D5-1JP2-2Q2-1)(NetJP2_3 D3-2D6-1JP2-3Q3-1)(NetJP3_1 D1-1D2-1D3-1D7-1JP3-1JP3-2)(NetQ1_3 Q1-3R1-2)(NetQ2_3 Q2-3R2-2)(NetQ3_3 Q3-3R3-2)(NetQ4_1 C1-1Q4-1Q5-2R7-1)(NetQ5_3 C2-2Q5-3R8-2)(NetQ6_3 Q6-3R9-1)(NetR1_1Q4-2R1-1R2-1R3-1R4-2)(NetR5_2R5-2VR1-2)(NetR6_1Q4-3R6-1)(NetVR1_1R6-2VR1-1VR2-2VR3-2ZD1-2)(NetVR2_1C2-1Q6-1VR2-1)(NetVR3_1R7-2VR3-1)板子信息报告表:Specifications For 实验七.PcbOn 5-Jun-2020 at 16:37:26Size Of board 5.01 x 2.03 sq inEquivalent 14 pin components 2.03 sq in/14 pin componentComponents on board 30Layer Route Pads Tracks Fills Arcs Text------------------------------------------------------------------------TopLayer 0 163 0 0 0BottomLayer 2 107 0 0 0TopOverlay 0 185 0 2 60KeepOutLayer 0 5 0 0 0MultiLayer 70 0 0 0 0------------------------------------------------------------------------Total 72 460 0 2 60Layer Pair Vias----------------------------------------Top Layer - Bottom Layer 2----------------------------------------Total 2Non-Plated Hole Size Pads Vias--------------------------------------------------------------------------------Total 0 0Plated Hole Size Pads Vias----------------------------------------0mil (0mm) 2 028mil (0.7112mm) 4 230mil (0.762mm) 18 032mil (0.8128mm) 40 040mil (1.016mm) 8 0----------------------------------------Total 72 2Top Layer Annular Ring Size Count----------------------------------10mil (0.254mm) 918mil (0.4572mm) 820mil (0.508mm) 322mil (0.5588mm) 230mil (0.762mm) 3834mil (0.8636mm) 460mil (1.524mm) 8----------------------------------Total 72 Mid Layer Annular Ring Size Count----------------------------------10mil (0.254mm) 918mil (0.4572mm) 820mil (0.508mm) 322mil (0.5588mm) 230mil (0.762mm) 3834mil (0.8636mm) 460mil (1.524mm) 8----------------------------------Total 72 Bottom Layer Annular Ring Size Count ----------------------------------10mil (0.254mm) 918mil (0.4572mm) 820mil (0.508mm) 322mil (0.5588mm) 230mil (0.762mm) 3834mil (0.8636mm) 460mil (1.524mm) 8----------------------------------Total 72 Pad Solder Mask Count----------------------------------4mil (0.1016mm) 72----------------------------------Total 72 Pad Paste Mask Count ----------------------------------0mil (0mm) 72 ----------------------------------Total 72 Pad Pwr/Gnd Expansion Count ----------------------------------20mil (0.508mm) 72 ----------------------------------Total 72 Pad Relief Conductor Width Count ----------------------------------10mil (0.254mm) 72 ----------------------------------Total 72 Pad Relief Air Gap Count----------------------------------10mil (0.254mm) 72 ----------------------------------Total 72 Pad Relief Entries Count----------------------------------4 72 ----------------------------------Total 72 Via Solder Mask Count ----------------------------------4mil (0.1016mm) 2 ----------------------------------Total 2Via Pwr/Gnd Expansion Count ----------------------------------20mil (0.508mm) 2 ----------------------------------Total 2 Track Width Count ----------------------------------8mil (0.2032mm) 30 10mil (0.254mm) 275 12mil (0.3048mm) 145 20mil (0.508mm) 10 ----------------------------------Total 460 Arc Line Width Count ----------------------------------10mil (0.254mm) 2 ----------------------------------Total 2 Arc Radius Count ----------------------------------160mil (4.064mm) 2 ----------------------------------Total 2 Arc Degrees Count ----------------------------------360 2 ----------------------------------Total 2 Text Height Count ----------------------------------60mil (1.524mm) 60 ----------------------------------Total 60Text Width Count----------------------------------10mil (0.254mm) 60----------------------------------Total 60Net Track Width Count----------------------------------10mil (0.254mm) 18----------------------------------Total 18Net Via Size Count----------------------------------50mil (1.27mm) 18----------------------------------Total 18Routing Information----------------------------------Routing completion : 100.00%Connections : 54Connections routed : 54Connections remaining : 0----------------------------------3、将打印的图纸粘贴在实验报告本中。