低电压环形振荡器设计

- 格式:pdf

- 大小:743.40 KB

- 文档页数:5

环形振荡器设计范文首先,我们来看一下环形振荡器的原理。

环形振荡器由一个环形反馈回路和一个放大器组成。

环形反馈回路通过正反馈路径将输出信号重新引入放大器的输入,形成一个闭环反馈结构。

当放大器的增益满足一定条件时,环形振荡器就能产生持续的正弦波振荡输出。

1.选择合适的放大器:放大器是环形振荡器的核心部件,负责放大信号并维持振荡。

选择合适的放大器应考虑其增益、带宽、非线性特性等因素。

2.确定振荡频率:根据应用需求,确定振荡器的工作频率。

振荡频率通常取决于放大器的参数和反馈网络的元件值。

3.设计反馈网络:反馈网络是环形振荡器的另一个关键部分,它决定了振荡器的稳定性和频率特性。

常见的反馈网络包括LC电路、RC电路和晶体振荡器等,根据应用需求选择合适的反馈网络。

4.确定放大器的工作点:根据放大器的静态特性和电源电压,确定放大器的工作点。

工作点的选择应使得放大器在非线性区域内工作,以产生满足振荡条件的正弦波输出。

5.模拟和优化:通过模拟软件进行仿真模拟,优化电路参数以满足设计需求。

模拟软件可以帮助设计者分析和预测振荡器的性能,并进行参数调整和优化。

实际应用方面,环形振荡器有广泛的应用领域,包括通信、射频、音频、雷达等。

在通信领域,环形振荡器常用于生成本地振荡信号,用于调制和解调、频率合成等。

在射频领域,环形振荡器可以产生稳定的射频信号,用于无线通信系统和雷达系统。

在音频领域,环形振荡器可以用于声音合成、音效处理等应用。

总之,环形振荡器是一种具有稳定输出的振荡器,其设计需要考虑放大器的选择、振荡频率、反馈网络以及放大器的工作点等因素。

在实际应用中,环形振荡器有广泛的应用领域,为通信、射频、音频等领域的电路设计提供了重要的解决方案。

设计人员可以通过仿真模拟和优化来完善环形振荡器的设计,以满足实际需求。

环形振荡器设计报告1.引言1.1 概述概述:环形振荡器作为一种重要的电路元件,在无线通信和射频领域具有广泛的应用。

它能够产生稳定的高频信号,被广泛用于无线电发射机、接收机、雷达等系统中。

本报告旨在通过详细的介绍环形振荡器的原理和设计要点,帮助读者了解和掌握环形振荡器的设计方法和关键技术,为相关领域的工程师和研究人员提供参考和借鉴。

同时本报告将介绍环形振荡器的基本原理,阐述设计环形振荡器的关键要点,并通过实例分析展示设计过程和结果。

最后,对环形振荡器的未来发展趋势进行展望,为相关领域的研究和应用提供一定的指导和借鉴。

1.2 文章结构文章结构部分的内容:本报告共分为三个部分。

第一部分是引言部分,主要介绍了本报告的概述、文章的结构和撰写本报告的目的。

第二部分是正文部分,主要包括环形振荡器原理的介绍以及设计要点的讨论,帮助读者更深入地了解环形振荡器的设计和实现。

第三部分是结论部分,主要总结了本报告的主要内容,分析了设计结果,并展望了环形振荡器在未来的发展方向。

通过这三个部分的内容,读者可以全面了解环形振荡器的设计和实现过程,以及对未来的展望。

1.3 目的目的部分的内容:本报告旨在针对环形振荡器的设计过程进行详细分析和论述。

具体目的包括:1. 探讨环形振荡器原理,深入了解其工作机制和特性,为设计提供理论基础和指导。

2. 分析环形振荡器设计中的关键要点,包括电路参数选择、频率稳定性和功耗等方面,以确定设计方案和优化电路性能。

3. 总结设计过程中的经验和教训,为今后的环形振荡器设计提供参考和借鉴。

4. 展望环形振荡器在未来的应用前景和发展方向,以及可能的改进和创新方向。

2.正文2.1 环形振荡器原理环形振荡器是一种基于反馈电路的振荡器,其工作原理是通过正反馈电路产生自持振荡的信号。

环形振荡器一般由放大器、反馈网络和振荡电路组成。

其中,放大器用于放大输入信号,反馈网络将一部分输出信号送回输入端,形成正反馈,而振荡电路则产生频率稳定的振荡信号。

环形振荡器的优化设计摘要:芯片在人们的生产生活中扮演者越来越重要的角色,尤其是数字芯片,随着工艺尺寸的不断缩小,数字芯片的优化设计变得尤为重要。

而环形振荡器是数字时钟芯片中的一种重要的结构,对环形振荡器的参数研究成为当下热门的一个方向。

本文建立了环形振荡器系统优化模型,给出了在不同参数变换下的MOSFET单晶管频率和尺寸建议。

在芯片面积的约束下进行全局寻优。

本文最终得到了NMOS和PMOS最优尺寸:1.424u,0.731u,1.660u,0.719u。

关键词:频率函数单目标非线性规划蒙特卡洛算法免疫粒子群环形振荡器一、前言振荡器是电子产品中最重要和最通用的结构之一。

从音频合成器到锁相放大器,它们在信号生成、波形合成和定时器中起着至关重要的作用。

在数字系统中,振荡器负责产生时序电路的核心:时钟。

时钟信号允许电路执行顺序操作,并使其能够精确设置重要事件的时间。

因此,没有振荡器就不可能设计出数字处理电路。

环形振荡器则易于理解和设计,它是由三个非门或更多奇数个非门输出端和输入端首尾相接,构成环状的机器。

频率很容易随逆变器级数进行调整,其频率成分明显比基于松弛的电路更纯净,功率集中在基波谐波上,广泛应用于工业、测试、温度传感器等。

其受速度、面积、功耗等方面的影响,故如何设计环形振荡器使其更有效发挥作用是关键。

(1)假设忽略环形振荡器中芯片间的微小距离;(2)假设题目给出的环形振荡器所有参数测量数据准确,无异常值;(3)假设忽略环形振荡器功耗散发的热量带来的影响;二、模型的建立与求解2.1 模型一的建立与求解2.1.1 环形振荡器的频率函数为了实现自持续振荡,环必须提供2π的相移,RO的振荡频率取决于每级的传播延迟和环结构中使用的级数。

为了实现自持续振荡,环必须提供2π的相移,并在振荡频率上具有统一的电压增益。

在m级环振荡器中,每个级提供了π/m的相移,直流反演提供了π的剩余相移。

因此,振荡信号必须通过每个m延迟阶段一次来提供第一个π相位,在m的时间内移位,每个阶段必须进行第二次,才能在2m的时间内获得剩余的π的移位。

25卷 第5期2008年5月微电子学与计算机M ICROELECTRONICS &COM PUTERVol.25 No.5M ay 2008收稿日期:2007-07-24一种低电压低功耗的环形压控振荡器设计伍翠萍,何 波,于 奇,陈 达(电子科技大学微电子与固体电子学院,四川成都610054)摘 要:提出了锁相环的核心部件压控振荡器(VCO)的一种设计方案.该压控振荡器采用全差分环形压控振荡器结构,其延迟单元使用交叉耦合晶体管对来进行频率调节.基于SM IC 0.18L m CM OS 工艺,用Hspice 对电路进行了仿真.仿真结果表明,该压控振荡器具有良好的线性度,较宽的线性范围以及高的工作频率,在1.8V 的低电源电压下,振荡频率的变化范围为402~873M Hz,中心频率在635MHz,功耗仅为6mW,振荡在中心频率635MHz 时的均方根抖动为3.91ps.关键词:环形压控振荡器;锁相环;交叉耦合晶体管对;均方根抖动中图分类号:T N 4 文献标识码:A 文章编号:1000-7180(2008)05-0069-04A Design of Ring Voltage -Controlled Oscillatorfor Low Voltage ApplicationWU Cu-i ping,HE Bo,YU Qi,CHEN Da(Colleg e of M icroelectronics and Solid -State Electr onics,U EST C,Cheng du 610054,China)Abstract:A design project of v oltage -controlled oscillator (V CO)which is the central component of the low voltage phase -locked loop(PL L)is proposed in this paper.T he VCO adopted the configuration of the full differential voltage -controlled -oscillator and the cross -coupled tr ansistors are used in the delay cells to adjust t he frequency.U nder the SM I C 0.18L m CM OS model,simulation results in Cadence Hspice indicate that the V CO proposed behaves in good linearity,wide linear r ange and high operating frequency.U nder a voltage supply of 1.8V,the var iety of the frequency is from 402M Hz to 873MHz,w ith the pow er dissipation of 6mW and rms jitter of 3.91ps at the central frequency of 635MHz.Key words:r ing voltage -controlled oscillator;PLL ;cross -coupled transistor pairs;rms jitt er1 引言近年来,由锁相环构成的时钟稳定电路、频率合成器以及时钟数据恢复电路得到了广泛应用.压控振荡器(Voltage -Controlled Oscillator,VCO)作为锁相环中的核心部分,对它的研究近些年得到了特别的关注.功耗的降低一直是集成电路设计的一个努力方向,因此,低电压低功耗的压控振荡器的设计成为研究热点.常见的VCO 有LC 压控振荡器、环形振荡器和晶体压控振荡器(VCXO).LC 压控振荡器可获得很好的相位噪声特性[1],良好的稳定性,并且振荡频率极高(达几吉赫兹),然而由于可调电容部分占电路总电容的比例很小,造成此种振荡器的频率调节范围不大.目前主流的CMOS 工艺在片上集成高Q 值的电感也比较困难,而且往往不能提供精确的电感模型.环形振荡器线性度好,功耗小,成本低,易于集成,调节范围宽,结构简单易于实现,基本组成单元可以是反相器或差分对.由于环形振荡器不使用电感,所以和CM OS 工艺兼容性非常好.但是环形振荡器稳定性不如LC 压控振荡器,而且随电压的波动,输出变化太快,不容易控制.晶体压控振荡器(VCXO)工作频率很准、稳定,仅与所选定晶体器件有关.但成本较高(相对民用消费类产品),一般用于特殊要求或与时钟、仪表、军工及通讯类产品合用.基于环形振荡器结构简单易于集成而且功耗低的优点,文中提出了一个全差分环形压控振荡器的设计方案,通过调节交叉耦合晶体管对的电阻值来对压控振荡器进行频率调节,该电路工作于1.8V 的低电源电压下,具有良好的线性度、较宽的线性范围以及较高的工作频率.2 压控振荡器定义及性能参数大多数应用要求振荡器频率为可调的,即其输出频率是一个控制输入的函数,这个控制输入通常是电压,这样的振荡器就是压控振荡器(VCO).图1为一个理想VCO 的振荡频率与输入控制电压关系的特性曲线[2].图1 理想VCO 的振荡频率与输入控制电压关系曲线理想VCO 的输出频率应是其输入控制电压的线性函数[3],可以由式(1)表示:X out =X 0+K VCO #V ct rl(1)式中,X 0表示V ctrl =0时的截距,K VCO 表示压控振荡器的压频增益或称灵敏度.VCO 主要的性能参数有中心频率、调节范围、调节线性度、输出摆幅、电源与共模抑制、功耗以及输出抖动.和其他任何模拟电路一样,压控振荡器受到速度、功耗和噪声之间折衷的限制.3 电路设计由于SMIC 0.18L m CM OS 工艺不支持制作集成电感和变容二极管的工艺,也不提供相应器件的模型,因此,设计的VCO 电路采用常用的环形VCO 结构.再考虑到全差分结构比单端结构对共模噪声抑制能力更强,本设计最终选用全差分环形VCO.3.1 环形VCO 级数的选取N 级振荡器的振荡频率f osc =12NT d,其中T d 表示每一级电路的大信号延时,有T d =RC L ,从振荡频率的计算式可看出,环形振荡器的级数越少,振荡频率越高,而级数越多,抖动会被一级级放大,相位误差积累效应会越发严重.所以,从性能的因素考虑,环形振荡器的级数较少为好,最少为三级,而采用全差分结构使得环形振荡器可以有偶数级,故选为四级.3.2 延迟单元的结构图2(a )是文中采用的延迟单元结构.差动对的负载由电阻R 1、R 2及交叉耦合晶体管对M 5、M 6组成.交叉耦合晶体管对表现为负电阻-2/g m5,6,负电阻值可由偏置电流控制.当I 1增加时,小信号差动电阻-2/g m5,6绝对值变小,由半边电路可得,等效电阻R 1//(-2/g m5,6)=R 1/(1-g m 5,6R 1)增大,从而使振荡频率降低,达到调节振荡频率的作用[4].图2 延迟单元结构这里使用差动对来控制M 1、M 2和M 5、M 6之间切换的电流并把电流折叠应用于电流切换控制.差动对M 7、M 8驱动两个电流镜,产生I ss1和I ss2,因为I 1+I 2=I ss ,I ss1=k #I 1,且I ss2=k #I 2,所以I ss1+I ss2=k #I ss .当V c t rl +-V ctrl -由非常正的值变到非常负的值时,I ss1由k #I ss 变到零而I ss2由零变到k #I ss ,而它们的和保持恒定,仍为k #I ss ,这即是差动对特性.比起将控制电压V ctrl +和V c t rl -分别直接加在M 11和M 12的栅端,并在M 11,M 12的下面层叠一电流源来实现差动控制的方法相比,本设计应用电流折叠的原理进行差动控制,不会消耗额外电压余度,使得电路可工作于低电源电压下.70微电子学与计算机2008年环形VCO 的振荡频率f osc W1R tot C L,R tot 为延迟单元的负载电阻,这里为负电阻与正电阻的并联电阻值,设V SW 为输出摆幅,那么R tot =V SW /I ss ,则f osc WI ssV SW #C L.若V SW 恒定,频率特性就能保持相对线性[5].许多CM OS 工艺条件下,制作能精确控制阻值或者具有合理物理尺寸的电阻很困难,因此,最好采用M OS 管代替图2(a)中电阻R 1和R 2.按此思路设计的延迟单元见图2(b ).当PMOS 晶体管处在深线性区时,它的电阻可近似为R o n U1L p C ox W L(V SG -|V tp |)(2)只要给定合适的栅极电压,让M 3的源漏电压V SD <<2(V SG -|V tp |),则M 3工作于深线性区,电阻R on 就几乎为常数了.环形VCO 是一个有反馈回路的振荡器,必须要满足/巴克豪森准则0(Barkhausen Criteria)起振条件以及稳定振荡的振荡条件.对于本设计中四级的环形振荡器,由/巴克豪森准则0决定的单级增益至少应大于1.4.当然增益也不是越大越好,否则抖动会通过级间放大而大大增加,综合考虑之,本设计选取单级增益为1.7,然后根据此条件来指导输入管尺寸的设计[6].3.3 全差分环形VCO 的整体电路图3是设计的全差分环形VCO 的整体电路.图3 V CO 总体电路图图3中左半部分为偏置电路,I ref1与I ref2是提供的基准电流.为减小沟道长度调制效应的影响,偏置电路采用低压共源共栅电流镜,在较为精确地镜像电流的同时又能满足低压应用.该偏置电路为延迟单元中的PMOS 负载管M 3和M 4的栅极提供V bi as =0155V 的偏置电压,并为差分控制支路的电流源提供I ss =320L A 的电流.右半部分为振荡环路的主体部分,每一个单元模块即为一个延迟单元,Clk1?~Clk4?为输出的差分时钟信号,它们相位不同,振荡频率相同.4 整体电路仿真结果在Cadence 环境下,利用Hspice 仿真工具,基于SMIC 0.18L m CMOS 工艺对设计的全差分环形压控振荡器进行了仿真.仿真结果:VCO 单边输出摆幅为500mV,中心频率为635MHz.振荡器输出波形见图4,该VCO 的主要性能参数见表1.图4 振荡器单边输出电压与时间的关系表1 VCO 的主要性能参数性能参数仿真结果电源电压 1.8V 输出摆幅500mV 控制电压0.55~0.75V 中心频率635M Hz 振荡频率变化范围402~873M Hz功耗6mW 均方根抖动3.91ps图5是仿真得到的VCO 振荡频率与输入控制电压的关系,可以看到,该VCO 在电压调节范围内,振荡频率与控制电压呈现较好的线性关系.图5 V CO 振荡频率与控制电压的关系仿真测试得到,输出电压摆幅在电压调节范围内的变化不大(参见表2),也进一步验证了该VCO压频增益的线性度较好.71第5期伍翠萍,等:一种低电压低功耗的环形压控振荡器设计表2 控制电压与输出电压摆幅对应关系V ctrl /mV V out /mV 550489650502750493.45 结束语压控振荡器(VCO)是锁相环的核心部件,文中设计了一种可于低电压下应用的四级全差分环形压控振荡器,基于SMIC 0.18L m CM OS 工艺仿真得到VCO 输出摆幅为500mV,中心频率为635MH z,输出频率范围较宽,在整个电压调节范围内,输出摆幅变化不超过20mV,压频增益的线性度非常好,此电路功耗较低,仅为6mW,振荡在中心频率时的均方根抖动为3.91ps.该VCO 可应用于锁相环构成的时钟稳定电路,锁相环型频率合成器以及时钟数据恢复电路中.参考文献:[1]杨丰林,闵昊,沈绪榜.CM OS 电感电容压控振荡器中对称噪声滤波技术的研究[J].微电子学与计算机,2007,24(5):41-44.[2]毕查德#拉扎维.模拟CM OS 集成电路设计[M ].陈贵灿,译.西安:西安交通大学出版社,2003:413-429.[3]肖杜,李小峰,朱小飞,等.基于数模混合仿真的PLL 系统设计[J].微电子学与计算机,2006,23(8):73-75.[4]房华.低电压低功耗高稳定性CM OS 锁相环的研究与设计[D].长沙:湖南大学,2006:40-46.[5]T odd Char les W eig andt.L ow-phase-noise,low-timing-jitter design techniques for delay cell based V COs and frequency synthesizers[C]//PH D thesi s.Berkeley ,U SA:U niversity of California,1998:145-150.[6]Geor ge Lee,Karina N g,Edmond K wang.Design of r ingoscillator based voltage contro lled oscillator ,P roject F inal R epo rt [R ].Canada,O ntario :U niv ersity of Waterloo,2005:3-19.作者简介:伍翠萍 女,(1983-),硕士研究生.研究方向为数模混合信号集成电路.何 波 硕士研究生.研究方向为数模混合信号集成电路.于 奇 副教授.研究方向为集成电路设计.陈 达 硕士研究生.研究方向为数模混合信号集成电路.(上接第68页)进行在线统计、分析、汇总,最终生成Ex cel 格式的汇总报表,为饮水安全决策提供了可靠的依据.图4 系统执行界面参考文献:[1]刘春霞,陈殿波.利用ODBC 技术实现异构数据源数据的共享[J].计算机与数字工程,2007,35(2):73-75.[2]王志坚,许峰,李静燕,等.基于XM L 的领域异构数据库间的数据转换[J].计算机与现代化,2004(5):71-74.[3]蔡延峰.蔡启明.异构数据库间的数据转换[J].计算机与现代化,2002(1):42-43.[4]杨勇,曹卉星,周建国,等.异构数据源数据转换[J].计算机工程与应用,1997(11):5-6.[5]Paul Benjamin L owr y.XM L data mediation and collabora -tion:a proposed comprehensive ar chitecture and query re -quirements for using XM L to mediate heterogeneous data source and targets[C ]//Pro ceedings of the 34th Hawaii I nternatio nal Conference on System Science.U SA:Ar izona U niversity ,2001:1-9.[6]邹建.SQ L Server 2000开发与管理应用实例[M ].北京:人民邮电出版社,2003.作者简介:周海鹏 男,(1982-),硕士研究生.研究方向为计算机网络与信息安全、SOA.张男,(1952-),教授,博士生导师.研究方向为分布式系统与W EB 技术及应用.李军怀 男,(1969-),副教授.研究方向为分布式计算、CSCW.72微电子学与计算机2008年。

摘要21世纪被称为信息时代,信息和通信技术革命从上世纪开始方兴未艾,以电子技术为基础的无线电通信技术和信息技术已经逐步走向成熟,电子工业的进步给人类生活方式带来了天翻地覆的变化。

新一代的通信技术需要更大带宽的基带芯片,大数据时代处理更多的数据需要更强运算能力的处理芯片,这对集成电路的发展提出了新的要求。

作为电子设备中时钟源信号产生的重要模块,低压低功耗的高精度振荡器一直是国内外学者研究的重点之一。

本论文对工艺、电源电压和温度波动如何影响振荡器输出频率展开研究并提出提高时钟精度的方法,提出了两种不同结构的低功耗的张弛振荡器,在-40-80℃的温度范围内产生32.768kHz目标频率,两种振荡器输出时钟具有较小的温漂和较高的电源线性。

振荡器的性能如下:(1)基于反相器方案的张弛振荡器提出了一种全MOS(Metal Oxide Semiconductor)管PTAT(Proportional to Absolute Temperature)电流源,利用多级反相器和RC延迟单元构成反馈回路作为振荡器核心电路,通过局部电压调整电路为振荡器核心电路供电,实现电源与振荡器核心电路隔离,降低了电源电压波动对振荡器输出频率的影响,此外偏置电路中使用MOS管阈值电压的温度特性对反相器延迟时间的温度波动进行补偿,降低了温度对振荡器温漂特性的影响。

室温下,振荡器输出频率33.769kHz,相对频率变化在-0.049%-0.353%之间,在-40-40℃温度范围内,相对频率变化不超过±0.62‰;(2)基于比较器方案的张弛振荡器使用14nA低功耗PTAT电流源提供偏置,为提高时钟信号精度,对核心电路中电阻进行微调,并进行正负温度系数电阻匹配以降低电阻温漂,同时采用温度系数较小的MOM电容。

为了改善振荡器输出波形,比较器输出级后加入数字逻辑单元,对振荡器波形进行整形和分频,产生我们需要的目标频率。

室温下,PTAT偏置电流源输出14nA,振荡器在1V电源电压下功耗约130nW,产生32.768kHz稳定的时钟信号输出,在-40-80℃范围内温漂为0.14%/℃;电源电压在0.9-1.5V电压范围内稳定输出。

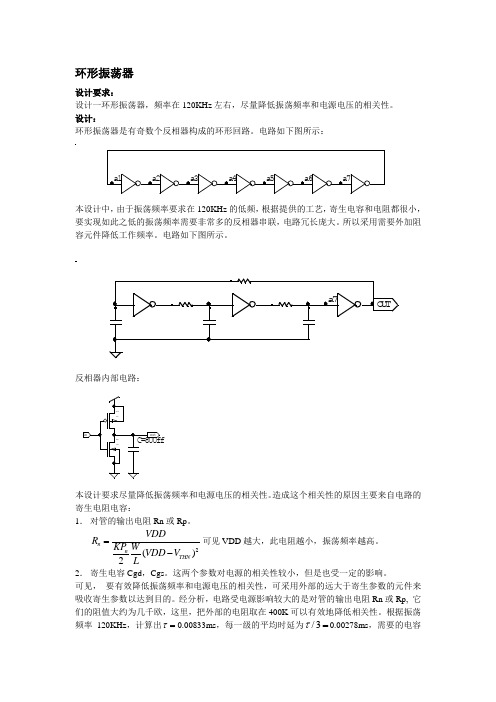

环形振荡器设计要求:设计一环形振荡器,频率在120KHz 左右,尽量降低振荡频率和电源电压的相关性。

设计:环形振荡器是有奇数个反相器构成的环形回路。

电路如下图所示:本设计中,由于振荡频率要求在120KHz 的低频,根据提供的工艺,寄生电容和电阻都很小,要实现如此之低的振荡频率需要非常多的反相器串联,电路冗长庞大。

所以采用需要外加阻容元件降低工作频率。

电路如下图所示。

反相器内部电路:本设计要求尽量降低振荡频率和电源电压的相关性。

造成这个相关性的原因主要来自电路的寄生电阻电容:1. 对管的输出电阻Rn 或Rp 。

2()2n n THN VDDR KP W VDD V L =-可见VDD 越大,此电阻越小,振荡频率越高。

2. 寄生电容Cgd ,Cgs 。

这两个参数对电源的相关性较小,但是也受一定的影响。

可见, 要有效降低振荡频率和电源电压的相关性,可采用外部的远大于寄生参数的元件来吸收寄生参数以达到目的。

经分析,电路受电源影响较大的是对管的输出电阻Rn 或Rp, 它们的阻值大约为几千欧,这里,把外部的电阻取在400K 可以有效地降低相关性。

根据振荡频率120KHz ,计算出τ=0.00833ms ,每一级的平均时延为/3τ=0.00278ms ,需要的电容大小为3C R τ==6.94pF 。

这里设计的反相器输出端本身就有800fF 的电容,再考虑到寄生电阻,电容,这里将外接电容的值取为5.5pF 。

Spice 网表文件:* Waveform probing commands.probe.options probefilename="ring_my1.dat"+ probesdbfile="E:\Program Files\Tanner EDA\S-Edit\tutorial\schematic\ring_my1.sdb" + probetopmodule="ring_my1".lib "E:\Gspice\HSPICE2002\H06MIXDDCT10V02.LIB" tt.lib "E:\Gspice\HSPICE2002\H06MIXDDCT10V02.LIB" resistor.lib "E:\Gspice\HSPICE2002\H06MIXDDCT10V02.LIB" bjt.SUBCKT inv in out Gnd Vddc2 out Gnd 800ffm1p out in Vdd Vdd pmos L=5u W=12umn1 out in Gnd Gnd nmos L=5u W=8u.ENDS* Main circuit: ring_my1C1 N3 Gnd 5.5pFC2 N2 Gnd 5.5pFC3 a7 Gnd 5.5pFXinv7 a7 OUT Gnd Vdd invXinv_1 N3 N5 Gnd Vdd invXinv_2 N2 N1 Gnd Vdd inv.print tran OUTR4 N2 OUT 400K TC=0.0, 0.0R5 N1 N3 400K TC=0.0, 0.0R6 N5 a7 400K TC=0.0, 0.0.tran 50n 14000000n start=800000nVCC Vdd GND PWL (0 5 8000000n 4.5 9000000n 4 10000000n 3.5 11000000n 3 12000000n 2.5 13000000n 2)* End of main circuit: ring_my1这里用的仿真软件是Tanner 系列的T-Spice 。

环形振荡器的设计报告1. 引言环形振荡器是一种基于正反馈原理的电路,可以产生连续振荡输出信号。

在许多电子系统中,环形振荡器被广泛应用于频率合成、时钟信号生成以及通信等领域。

本报告旨在介绍环形振荡器的设计原理、电路结构以及性能参数的选择和优化。

2. 设计原理环形振荡器的主要设计原理是正反馈。

正反馈将一部分输出信号重新引入输入端,通过放大和滤波等操作,使得输入信号不断被放大和延迟,从而产生振荡输出信号。

环形振荡器的关键是设计一个恰当的正反馈路径,以确保稳定的振荡输出。

3. 电路结构环形振荡器的核心是由放大器和滤波器组成的正反馈回路。

在设计中,可以选择不同类型的放大器和滤波器,以实现所需的振荡频率和幅值。

常见的环形振荡器电路结构有MOS环形振荡器和LC环形振荡器两种。

MOS环形振荡器基于MOS管的工作原理,适用于较低频率的振荡。

LC环形振荡器则利用电感和电容组成的LC振荡回路,适用于较高频率的振荡。

在设计电路结构时,需要确定放大器类型、滤波器类型、增益和带宽等参数。

选择合适的参数可以实现稳定的振荡输出。

4. 参数选择与优化在设计环形振荡器时,需要选择和优化一些关键参数,以确保电路的性能。

以下是一些常见的参数:- 频率:选择合适的放大器和滤波器元件,并调整它们的数值,以实现所需的振荡频率。

- 增益:增益影响环形振荡器的输出幅值,需要根据实际需求确定增益大小。

- 相位噪声:相位噪声是指振荡器输出信号的相位偏差,可以通过增加滤波器元件来减少相位噪声。

- 抑制功率噪声:通过合适的反馈电路和滤波器元件,可以降低振荡器输出的功率噪声水平。

参数选择和优化是一个复杂的过程,需要结合实际要求和电路特性进行综合考虑。

5. 实验结果与讨论为了验证设计的环形振荡器电路的性能,我们进行了实验并得到了以下结果。

通过实验,我们成功实现了一个工作在100MHz频率的环形振荡器。

测量结果显示,振荡器的输出幅值为2V,相位噪声为-90dBc/Hz。

实验三:环形振荡器版图设计一、实验目的1、使用现有的布局实例创建新的布局;2、仿真提取版图;二、实验要求1、打印出DRC报告;2、输出CMOS环形振荡器的后置仿真结果,包括瞬态响应、振荡频率和平均功率。

三、实验工具Virtuoso四、实验内容1、创建CMOS环形振荡器电路原理图;2、创建CMOS环形振荡器的版图;3、后仿真(Post-layoutsimulation,PLS)。

1、创建CMOS 环形振荡器的电路原理图在librarymanager 界面选中lab1(自己创建的库),并点击菜单栏上的file->new->cellview,创建CMOS 环形振荡器的电路原理图。

ViewName ToolLibrarypathfileZhowte/iccad/iclab/tds.LiH图1CMOS 环形振荡器电路原理图的创建因为CMOS 环形振荡器是由几个CMOS 反相器组成的,在前面两个实验中已经创建好了CMOS 反相器的电路原理图,所以可以直接调用CMOS 反相器,在schematicediting 窗口利用快捷键中打开添加实例窗口,选择之前所创建的CMOS 反相器,如图2所示,连续放置5个。

图2添加CMOS 反相器将5个CMOS 反相器一次首尾相连,接着创建一个输出引脚,放置在最后一个CMOS 反相器后,并通过wire 将它们连接起来,具体如图3所示:Create File]XOKCancel DefaultsHel plablLibraryName CellNameschemaitidComposer-Schematic <View Column sUpsideDownNames图3CMOS环形振荡器电路原理图CreateNewFile_l:]Xr OK Default s Hel p、创建环形振荡器的版图与创建CMOS反相器的版图类似,也是在librarymanager窗口先选中labl, 在选择file->new->cellview,在弹出的窗口中输入环形振荡器的信息如图4所示:ToolLibrarypathfile/home/iccad/icLab/ctis.Li及LibraryNameCellNameViewName图4CMOS环形振荡器版图的创建在layoutediting中添加5个CMOS反相器,并将它们摆放在一起,中间的金属正好相接,如图5所示:图5CMOS环形振荡器版图接着用金属将CMOS反相器的输入引脚与输出引脚连接起来,为了避免短路,在穿过CMOS环形振荡器时需要换另一种金属,首先在LSW窗口选中metall金属,再回到layoutediting窗口,使用快捷键来1在点击F3,弹出createpath窗口,首先画一条metal1金属通路,然后在合适的位置点击F3,在createpath窗口中选择changetolayer,将metal1金属换为metal2金属,画好之后如图6所示:ViirW&s*®LayoutEditing^Nabiring[aycut比-HD.21DO此SL40U(F)Sdii:i::L口DRQ:OFF隔d世Del:£mri:TootsIDe-shina FIEW™Mat®Efflt1115MTy①川面建的小卬值11蜘FtouM呵佃即忸Migrate图6CMOS环形振荡器版图将金属通路画好之后添加vdd、gnd和out,其中vdd与gnd在放置好后要与实验二一样进行同样的操作,这里不再赘述,添加好引脚后的CMOS环形振荡器的版图如图7所示:Virtuosa^LayoutEditing;llablringlayautXi-3.11®V:-1.IBS(FJi Stilbsct:0DAb:OFT dX:Disk Omd:TaalgISe^igHWiilnwCrai也EtH.VarllTyCom惬irtiM均OpOuiiisOwU旭网向随图7CMOS环形振荡器版图3、CMOS环形振荡器的后仿真和实验一实验二类似,首先进行DRC验证,DRC验证成功后再使用提取工具,生成提取视图后再做LVS,在这些步骤都完成后,就可以对这个环形振荡器进行布局后仿真,提取其工作频率并测量其平均功率。

环形振荡器的电路

如图1,为了进一步加大RC和G2的传输延迟时间,在有用电路中将电容C 的接地端改接G1的输出端。

如图2所示。

例如当v12处发生负跳变时,经过电容C使v13首先跳变到一个负电平,然后再从这个负电平开头对电容C充电,这就加长了v13从开头充电到上升为VTH 的时间,等于加大了v12到v13的传输延迟时间。

图4 环形振荡器的有用改进电路图

通常RC电路产生的延迟时间远远大于门电路本身的传输延迟时间,所以在计算振荡周期时可以只考虑RC电路的作用而将门电路固有的传输延迟时间忽视不计。

另外,为防止v13发生负跳变时流过反相器G3输入端钳位二极管的电流过大,还在G3输入端串接了爱护电阻RS。

电路中各点的电压波形如图2所示。

图2 电路的工作波形

图2中画出了电容C充、放电的等效电路。

利用式:

和式求得电容C的充电时间T1和放电时间T2各为

其中

若R1+RS》R ,VOL≈0,则VE≈VOH,RE≈R,这时T1和T2可简化为

故图10.3.5电路的振荡周期近似等于假定VOH=3V、Vth=1.4V,代入上式后得到

T≈2.2RC式T≈2.2RC可用于近似估算振荡周期。

但使用时应留意它的假定条件是否满意,否则计算结果会有较大的误差。