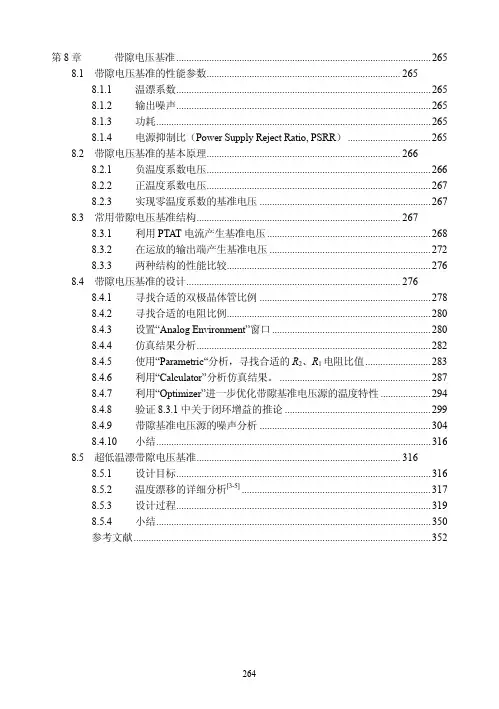

带隙基准学习笔记

- 格式:doc

- 大小:2.28 MB

- 文档页数:45

开关电容带隙基准1. 引言开关电容带隙基准是指在开关电容器中,用于控制开关的电荷存储和释放的能量差。

该能量差由带隙决定,带隙越大,存储和释放的能量差越大,开关性能越好。

本文将介绍开关电容带隙基准的定义、影响因素以及相关技术。

2. 开关电容带隙基准的定义开关电容器是一种用于存储和释放电荷的装置,它由两个可互相接通或断开的电极构成。

当两个电极相连时,可以通过充放电过程将电荷存储在其中,当两个电极断开时,则可以将存储的电荷释放出来。

而带隙则是指两个相连或相断的状态之间所需施加的最小能量。

3. 影响开关电容带隙基准的因素3.1 材料选择材料选择是影响带隙大小的重要因素之一。

常见的材料有金属氧化物、聚合物等。

不同材料具有不同的导体特性和介质特性,从而影响带隙大小。

例如,金属氧化物通常具有较大的带隙,可以实现更大的能量差。

3.2 结构设计结构设计也是影响带隙大小的因素之一。

开关电容器的结构设计包括电极形状、间距等。

间距越小,带隙越小,存储和释放的能量差也相应减小。

因此,在设计过程中需要综合考虑结构参数对带隙的影响。

3.3 制造工艺制造工艺对开关电容带隙基准同样有重要影响。

不同的制造工艺可能导致材料性质、结构参数等方面的差异,进而影响带隙大小。

因此,在制造过程中需要选择合适的工艺参数,并进行严格控制。

4. 开关电容带隙基准相关技术4.1 薄膜沉积技术薄膜沉积技术是一种常用于制备开关电容器的技术。

该技术通过在底座上沉积一层薄膜来形成电容器结构。

通过控制沉积过程中的温度、压力等参数,可以实现带隙的精确控制。

4.2 纳米材料应用纳米材料具有较小的尺寸效应和表面效应,可以实现更小的带隙。

因此,在开关电容器中引入纳米材料可以有效提高带隙基准。

4.3 光刻技术光刻技术是一种常用于微电子制造中的技术。

通过光刻技术,可以在电容器结构上形成亚微米级别的图案,从而实现更小的带隙。

5. 结论开关电容带隙基准是影响开关电容器性能的重要因素之一。

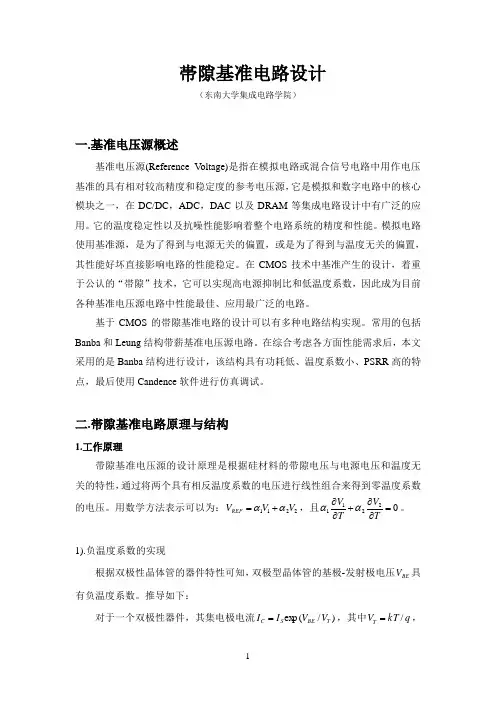

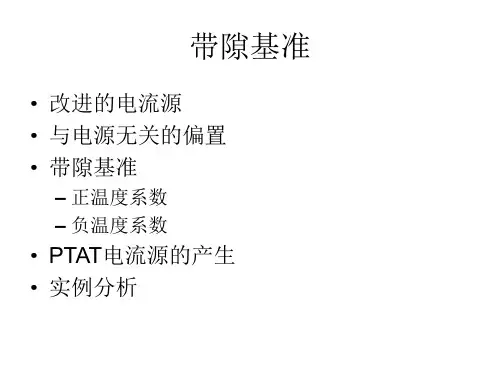

帯隙基准电路设计(东南大学集成电路学院)一.基准电压源概述基准电压源(Reference V oltage)是指在模拟电路或混合信号电路中用作电压基准的具有相对较高精度和稳定度的参考电压源,它是模拟和数字电路中的核心模块之一,在DC/DC ,ADC ,DAC 以及DRAM 等集成电路设计中有广泛的应用。

它的温度稳定性以及抗噪性能影响着整个电路系统的精度和性能。

模拟电路使用基准源,是为了得到与电源无关的偏置,或是为了得到与温度无关的偏置,其性能好坏直接影响电路的性能稳定。

在CMOS 技术中基准产生的设计,着重于公认的“帯隙”技术,它可以实现高电源抑制比和低温度系数,因此成为目前各种基准电压源电路中性能最佳、应用最广泛的电路。

基于CMOS 的帯隙基准电路的设计可以有多种电路结构实现。

常用的包括Banba 和Leung 结构带薪基准电压源电路。

在综合考虑各方面性能需求后,本文采用的是Banba 结构进行设计,该结构具有功耗低、温度系数小、PSRR 高的特点,最后使用Candence 软件进行仿真调试。

二.帯隙基准电路原理与结构1.工作原理带隙基准电压源的设计原理是根据硅材料的带隙电压与电源电压和温度无关的特性,通过将两个具有相反温度系数的电压进行线性组合来得到零温度系数的电压。

用数学方法表示可以为:2211V V V REF αα+=,且02211=∂∂+∂∂T V T V αα。

1).负温度系数的实现根据双极性晶体管的器件特性可知,双极型晶体管的基极-发射极电压BE V 具有负温度系数。

推导如下:对于一个双极性器件,其集电极电流)/(ex p T BE S C V V I I =,其中q kT V T /=,约为0.026V ,S I 为饱和电流。

根据集电极电流公式,得到:SC T BE I I V V ln= (2.1) 为了简化分析,假设C I 保持不变,这样: TI I V I I T V T V S S T S C T BE ∂∂-∂∂=∂∂ln (2.2) 根据半导体物理知识可知:kT E bT I gm S -=+ex p 4 (2.3)其中b 为比例系数,m ≈−3/2,Eg 为硅的带隙能量,约为1.12eV 。

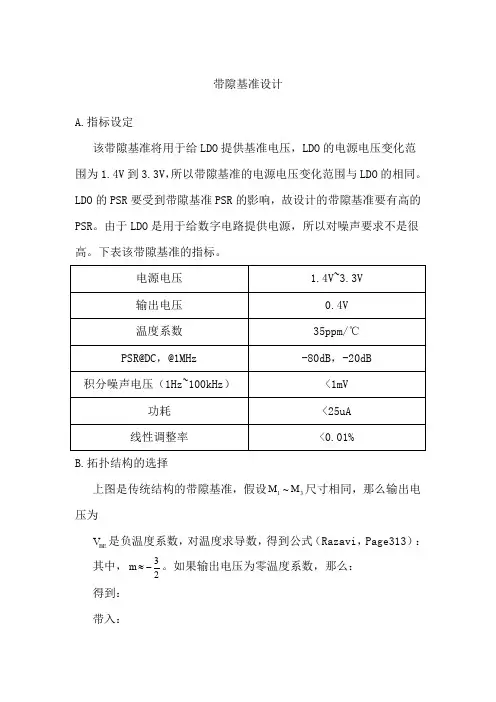

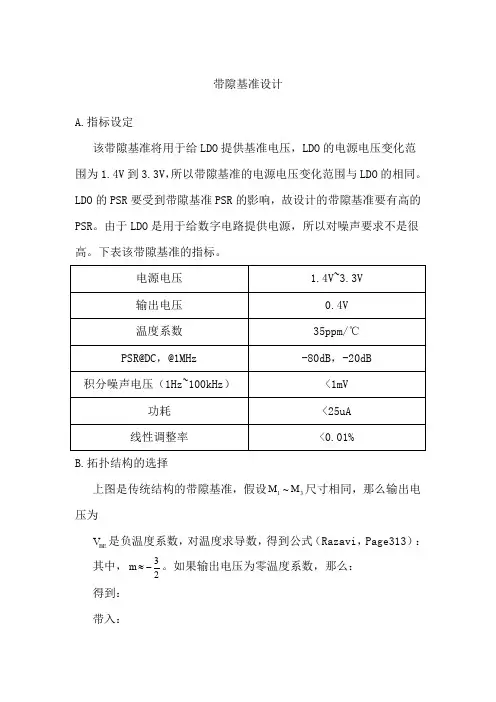

带隙基准设计A.指标设定该带隙基准将用于给LDO 提供基准电压,LDO 的电源电压变化范围为1.4V 到3.3V ,所以带隙基准的电源电压变化范围与LDO 的相同。

LDO 的PSR 要受到带隙基准PSR 的影响,故设计的带隙基准要有高的PSR 。

由于LDO 是用于给数字电路提供电源,所以对噪声要求不是很高。

下表该带隙基准的指标。

电源电压 1.4V~3.3V 输出电压 0.4V 温度系数 35ppm/℃ PSR@DC ,@1MHz-80dB ,-20dB积分噪声电压(1Hz~100kHz )<1mV 功耗 <25uA 线性调整率<0.01%B.拓扑结构的选择上图是传统结构的带隙基准,假设31M ~M 尺寸相同,那么输出电压为BE V 是负温度系数,对温度求导数,得到公式(Razavi ,Page313): 其中,23-≈m 。

如果输出电压为零温度系数,那么: 得到: 带入:得到:在27°温度下,输出电压等于1.185V ,小于电源电压1.4V ,可这个电路并不能工作在1.4V 电源电压下,因为对于带隙基准里的运放来说,共模输入范围会受到电源电压限制,电源电压的最小值为: 其中,2BE V 是三极管2Q 的导通电压,pair al differenti input GS V ___是运放差分输入管对的栅源电压,source current of drive over V ____是运放差分输入管对尾电流源的过驱动电压。

对于微安级别的电流,可以认为:这里将差分输入对的体和源级短接以减小失配,同时阈值电压不会受到体效应的影响。

假设差分对尾电流源的过驱动电压为100mV ,那么,电源电压的最小值为:下表列出了smic.13工艺P33晶体管阈值电压和三极管的导通电压随Corner 角和温度变化的情况:-40° 27° 80° slow -826mV -755mV -699mV typical -730mV -660mV -604mV fast -637mV -567mV -510mV BJT 的BE V -40° 27° 80° slow 830mV 720mV 630mV typical 840mV 730mV 640mV fast860mV750mV660mV可以计算出在不同温度的Corner 角下电源电压的最小值:-40° 27° 80° slow 1.756V 1.575V 1.429V typical 1.67V 1.49V 1.344V fast1.597V1.417V1.27V可以看出,对于大部分情况,1.4V 电源电压无法保证带隙基准中运放的正常工作,所以必须改进电路结构,使其可以工作在1.4V 电源电压下。

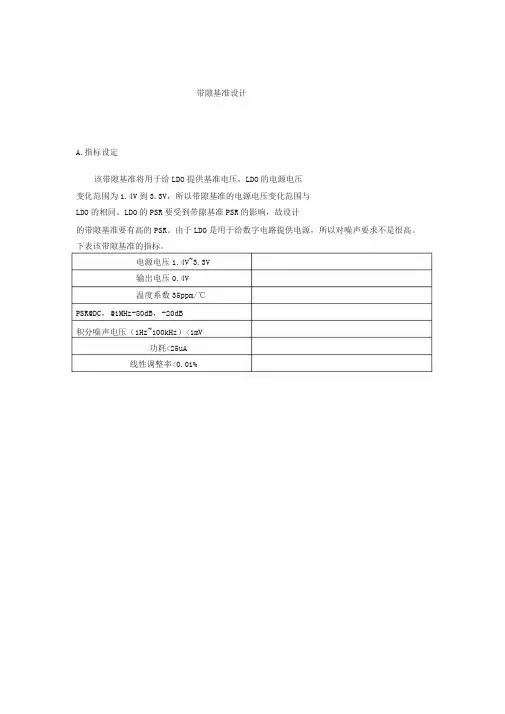

带隙基准设计A.指标设定该带隙基准将用于给LDO提供基准电压,LDO的电源电压变化范围为1.4V到3.3V,所以带隙基准的电源电压变化范围与LDO的相同。

LDO的PSR要受到带隙基准PSR的影响,故设计的带隙基准要有高的PSR。

由于LDO是用于给数字电路提供电源,所以对噪声要求不是很高。

下表该带隙基准的指标。

电源电压1.4V~3.3V输出电压0.4V温度系数35ppm/℃PSR@DC,@1MHz-80dB,-20dB积分噪声电压(1Hz~100kHz)<1mV功耗<25uA线性调整率<0.01%B.拓扑结构的选择上图是传统结构的带隙基准,假设M1~M尺寸相同,那么输3出电压为R2V REF VlnNV BET3R1V是负温度系数,对温度求导数,得到公式(Razavi,BEPage313):V BE3BE3(4)Tg/VmVETTq其中,3m。

如果输出电压为零温度系数,那么:2V REF V BE3TTkqlnNR2R1得到:kV BE(4m)V T E g/R32lnNqRT1q带入:R2V REF VlnNV BET3R1 得到:EgV REF(4m)VTq在27°温度下,输出电压等于1.185V,小于电源电压1.4V,可这个电路并不能工作在1.4V电源电压下,因为对于带隙基准里的运放来说,共模输入范围会受到电源电压限制,电源电压的最小值为:VDDmin V BE VV2GS_input_differential_pairover_drive_of_current_source其中,V是三极管Q2的导通电压,V GS_input_differential_pair是运放差BE2分输入管对的栅源电压,V____是运放差分输入管对尾overdriveofcurrentsource 电流源的过驱动电压。

对于微安级别的电流,可以认为:V GS VTH 这里将差分输入对的体和源级短接以减小失配,同时阈值电压不会受到体效应的影响。

带隙基准的原理

嘿,朋友们!今天咱们来聊聊带隙基准的原理,这可真是个超级厉害的东西啊!

想象一下,带隙基准就像是一个精准无比的导航仪,能为电子设备指引出最正确的方向。

比如说,你的手机能稳定地显示时间、你的电脑能准确处理各种数据,这里面可都有带隙基准的大功劳呢!

带隙基准的原理其实不难理解啦。

它就像是一个聪明的裁判,能够提供一个非常稳定的参考电压。

你知道吗,就好像在一场比赛中,如果裁判不靠谱,那整个比赛不就乱套啦?带隙基准就是要保证这个参考电压稳如泰山,不管周围环境怎么变化,它都能坚守阵地!

再打个比方吧,带隙基准就像你在黑暗中前行时手里的那盏明灯,始终为你照亮前方的路。

它依靠巧妙的电路设计和特殊的半导体材料,实现了这种令人惊叹的稳定性。

这可不是随便就能做到的哟,得靠无数科学家和工程师们的智慧和努力呢!

比如说,在芯片制造中,带隙基准就发挥着至关重要的作用。

如果没有它,芯片可能就会变得神经兮兮的,一会儿正常一会儿出问题。

“哎呀,那可不行啊!”你肯定会这么说。

总之,带隙基准的原理虽然有点复杂,但它真的是电子世界里的无名英雄啊!它默默地工作,保证着各种电子设备的正常运行。

所以啊,我们真应该好好感谢这些看似不起眼,实则无比重要的带隙基准们!它们真的是太了不起啦!

我的观点很明确,带隙基准是电子领域中不可或缺的关键要素,它的作用和价值不可估量。

带隙基准原理带隙基准原理是一个重要的概念,在材料科学中有广泛的应用。

在物理学中,带隙是指能带中最高的已占据电子带和最低的未占据电子带之间的能隙。

它是一种材料特性,能够影响该材料的电子能级结构和光学性质。

许多领域,如电子行业、信息行业、太阳能行业、照明行业、半导体行业和光电行业等,对带隙的研究和应用具有重要意义。

在半导体行业中,半导体材料的带隙是一个关键参数。

带隙提供了材料的能带结构,影响电子的运动和穿透,因此也影响了半导体材料的电学性能和光学性质。

带隙大小的差异可以使得电子在不同材料中的行为方式发生变化。

例如,较小的带隙可以超越材料的电子激发能,从而产生热激跃和电离,这种特性可以用于光电探测器和光度计以及太阳电池。

同时,大的带隙可以阻碍场效应晶体管的电子流动,从而限制其用于高速数字和模拟电路应用。

半导体材料的带隙取决于材料的组成、晶体结构和纯度。

材料的组成指的是半导体材料的原子组成,例如硅、锗、镓砷等。

不同的半导体组成会产生不同大小的带隙。

晶体结构指的是半导体材料的排列方式,如三方晶体结构、脉冲晶体结构等。

纯度指的是材料中杂质的含量,杂质含量越少,材料的带隙就越大。

半导体材料的带隙可以通过不同的方法实现测量。

其中一个重要的测量方法是光学方法,是通过使用不同的光源和测量设备来测量材料中电子的行为。

这种方法通常被用于半导体制造过程中,以确保不同批次的材料具有相同的带隙。

总之,带隙基准原理是材料科学和物理学的一个重要概念,可以用于描述材料的电子能级结构和光学性质。

在半导体行业中,带隙大小是一个关键参数,影响半导体材料的电学性能和光学性质。

因此,准确测量带隙大小对于半导体制造过程非常重要。

带隙基准设计A.指标设定该带隙基准将用于给LDO 提供基准电压,LDO 的电源电压变化范围为1.4V 到3.3V ,所以带隙基准的电源电压变化范围与LDO 的相同。

LDO 的PSR 要受到带隙基准PSR 的影响,故设计的带隙基准要有高的PSR 。

由于LDO 是用于给数字电路提供电源,所以对噪声要求不是很高。

下表该带隙基准的指标。

电源电压 1.4V~3.3V 输出电压 0.4V 温度系数 35ppm/℃ PSR@DC ,@1MHz-80dB ,-20dB积分噪声电压(1Hz~100kHz )<1mV 功耗 <25uA 线性调整率<0.01%B.拓扑结构的选择上图是传统结构的带隙基准,假设31M ~M 尺寸相同,那么输出电压为BE V 是负温度系数,对温度求导数,得到公式(Razavi ,Page313): 其中,23-≈m 。

如果输出电压为零温度系数,那么: 得到: 带入:得到:在27°温度下,输出电压等于1.185V ,小于电源电压1.4V ,可这个电路并不能工作在1.4V 电源电压下,因为对于带隙基准里的运放来说,共模输入范围会受到电源电压限制,电源电压的最小值为: 其中,2BE V 是三极管2Q 的导通电压,pair al differenti input GS V ___是运放差分输入管对的栅源电压,source current of drive over V ____是运放差分输入管对尾电流源的过驱动电压。

对于微安级别的电流,可以认为:这里将差分输入对的体和源级短接以减小失配,同时阈值电压不会受到体效应的影响。

假设差分对尾电流源的过驱动电压为100mV ,那么,电源电压的最小值为:下表列出了smic.13工艺P33晶体管阈值电压和三极管的导通电压随Corner 角和温度变化的情况:-40° 27° 80° slow -826mV -755mV -699mV typical -730mV -660mV -604mV fast -637mV -567mV -510mV BJT 的BE V -40° 27° 80° slow 830mV 720mV 630mV typical 840mV 730mV 640mV fast860mV750mV660mV可以计算出在不同温度的Corner 角下电源电压的最小值:-40° 27° 80° slow 1.756V 1.575V 1.429V typical 1.67V 1.49V 1.344V fast1.597V1.417V1.27V可以看出,对于大部分情况,1.4V 电源电压无法保证带隙基准中运放的正常工作,所以必须改进电路结构,使其可以工作在1.4V 电源电压下。

![cmos模拟集成电路设计ch11带隙基准up[精华]讲解学习](https://uimg.taocdn.com/47bb408f2cc58bd63086bd18.webp)

带隙基准的原理和应用1. 带隙基准的概念带隙基准是指能源禁带(带隙)的能量差作为基准来描述其他能级的能量。

在固体物理学和半导体器件工程中,带隙基准是一个重要的概念。

在材料科学和电子学领域,带隙基准的理解和应用对于开发新材料和设计新型器件具有重要意义。

2. 带隙基准的原理带隙是固体材料中电子能级的能带结构中出现的能量差。

在绝缘体和半导体中,带隙是由原子之间的相互作用和晶格结构所决定的。

带隙基准的原理可以通过能带理论来解释,即根据固体结构和电子行为来描述材料的能量级。

根据能带理论,材料中的电子分为价带和导带。

在绝缘体中,带隙较大,导带与价带之间没有电子,因此电子无法在绝缘体中自由移动。

而在导电材料中,带隙较小,导带和价带之间有部分电子,因此电子可以在导电材料中自由移动。

带隙基准的原理是通过确定材料中带隙的大小来描述其他能级的能量。

带隙越大,材料的导电性越差,绝缘性越好。

带隙越小,材料的导电性越好,半导体性质越明显。

3. 带隙基准的应用带隙基准在材料科学和半导体器件工程中具有广泛的应用。

以下列举几个应用案例:•化学材料设计:通过带隙基准可以预测一种化学材料的导电性和光学性质,进而引导新材料的设计和合成。

例如,在太阳能电池的设计中,通过调整材料的带隙大小可以提高光电转换效率。

•半导体器件制造:在半导体器件的设计和制造过程中,带隙基准起到了关键的作用。

带隙基准可以帮助工程师确定材料的导电性和电子特性,从而指导半导体器件的设计和性能优化。

例如,在集成电路中,带隙基准可以帮助确定材料的选择和布局。

•能源存储与转换:带隙基准在能源存储和转换领域也有重要的应用。

通过带隙基准,可以预测材料在光伏、光催化和电池等能源转换过程中的效率和稳定性。

例如,在锂离子电池的设计中,带隙基准可以帮助选择合适的正负极材料,以提高电池的容量和循环寿命。

•电子行为研究:带隙基准也可以用于研究材料中的电子行为。

通过带隙基准,可以了解材料中的电子结构和激发态,进而研究材料的输运性质和光学性质。

带隙基准和简并点带隙基准是指在固体材料中,最低的电子能级和最高的价带之间的能量差。

它是评估材料导电性质的重要因素,也是研究材料光学性质和电子结构的基础。

在这篇文章中,我们将讨论带隙基准以及与之相关的简并点。

带隙基准的概念最早出现在固体物理学中,用于描述电子在晶体中的行为。

在晶体中,价带是指原子价电子能量最高的一层能级,而导带则是指电子能量较低的一组能级。

介于这两者之间的能量差被定义为带隙。

带隙的大小直接影响了材料的导电性质,通常被分为导体、绝缘体和半导体三种类型。

对于导体来说,它们的带隙非常小或者完全没有带隙。

这意味着导体中电子可以自由地从价带跃迁到导带,导致材料呈现出良好的导电性质。

金属就是典型的导体例子,其带隙大小接近于零。

绝缘体与导体相反,具有较大的带隙。

这意味着绝缘体中价带的电子无法轻易地跃迁到导带。

因此,在绝缘体中几乎没有自由电子的存在,导致材料呈现出良好的绝缘性质。

典型的绝缘体包括陶瓷和某些半导体材料。

半导体是介于导体和绝缘体之间的一类材料。

它们的带隙大小介于导体和绝缘体之间,允许部分电子从价带跃迁到导带。

这使得半导体能够表现出导电性,但相对于金属来说,其电导率要低得多。

半导体的典型例子包括硅和锗。

而简并点是指在材料的能带中出现能量等于或接近于零的点。

简并点通常与材料的对称性和晶体结构密切相关。

正如其名称所示,简并点会导致能带在特定的能量处交叉,使得电子在能带之间跃迁的概率增加。

这样的交叉点对于材料的电子传输、热传导和光学性质起着重要的影响。

简并点可以出现在材料的导带和价带之间,也可以在价带或导带内部的不同能级之间。

简并点的存在可以帮助我们理解材料的电子行为和性质。

例如,一些具有简并点的材料表现出非常高的电导率,使其成为导电性能优异的材料。

总结起来,带隙基准是描述固体材料电子行为的重要因素之一,能够评估材料的导电性质和光学性质。

带隙大小直接影响着材料的导电性质,使得材料呈现出导体、绝缘体或半导体的特性。

带隙基准电压源的基本原理带隙基准电压源是一种用于产生精确稳定的参考电压的电路。

在许多电子器件中,需要一个稳定的电压来作为参考,例如ADC(模数转换器)、DAC(数模转换器)、放大器、航天器等。

而带隙基准电压源能提供一个非常稳定且几乎不受温度和供电电压变化的电压。

1.硅基隙参考电压:带隙基准电压源的原理基于半导体物质中的能带隙。

在半导体材料中,能带是指电子在晶格中移动的能力。

在导带(conduction band)和价带(valence band)之间有一个能带隙,它是电子无法自由传导的区域。

该能带隙的大小决定了半导体材料的导电性和光电特性。

硅是一个常用的半导体材料,其能带隙约为1.1电子伏特(eV)。

2.基于二极管的温度补偿:带隙基准电压源使用基于二极管的温度补偿技术来实现电压稳定性。

基于二极管的温度补偿电路利用半导体材料随温度变化而改变的特性。

在这种电路中,两个二极管的温度特性相互抵消,从而通过将它们串联,可以得到一个与温度变化关系较小的电压输出。

3.反馈环路设计:4.温度补偿和功耗:将温度补偿器件放置在设备中,可以在温度变化时自动适应电源电压的变化,从而保持输出电压的稳定性。

在实际应用中,为了减少功耗,可以通过动态功率调整技术来控制带隙基准电压源的功耗。

5.噪声抑制:综上所述,带隙基准电压源是通过利用半导体材料中的能带隙原理,结合基于二极管的温度补偿技术和反馈环路设计,实现稳定、精确和低噪声的参考电压源。

它在很多电子器件中被广泛应用,能够提供稳定的电压参考,从而提高了其他电路的性能和精确度。

带隙基准电路1 带隙基准电路的概述带隙基准电路是一种先进的模拟电路解决方案,它不仅能够实现参考电压的产生,而且可以实现多通道的参考电压的精确控制。

它相对于传统的参考电路有以下几个优点:· 能提供宽带隙电压范围:这种情况下,能够以一种精确而稳定的方式实现跨越最大可能输入范围的处理。

· 电路可以实现多通道、高精度的参考电压:它提供了一种高精度、稳定性优良的多分量参考输出电压。

· 产生低噪声和高稳定性:因为带隙基准电路采用了集成技术,所以能够有效减少噪声并具备较好的稳定性。

· 简单的操作和便携性:它的操作非常简单,而且带隙基准电路也非常便携,可以轻松实现重新定位。

2 带隙基准电路的工作原理带隙基准电路是实现多种电能质量测量应用的有效解决方案,它采用了两种不同的工作方式:精确模式和保护模式。

在精确模式下,带隙基准电路的工作原理很简单,只需要调节电路的内部参数即可产生高精度的输出电压。

它是由三部分组成:输出稳压器,用于提供稳定的输出电压;一个参考电源,主要用于调节带隙电压范围;以及一组校准电阻,用于控制输出精度。

在保护模式下,带隙基准电路会根据外部环境和输入电压变化情况,自动调节其输出电压,以确保它的正确工作。

它的主要组成部分也包括一个稳压器,一个参考电源和一组校准电阻。

但是,它需要一个可变增益放大器,以更精准地检测并调节电路的输出电压。

3 带隙基准电路的应用带隙基准电路是由一套事先经过优化设计的电路元件组成,因此它可以用于很多不同的应用领域。

比如:可以用于实现数字电路中的电源供应器被板实现;可以应用在移动电话和便携式电子装置电源管理中实现电压控制;可以应用在太阳能发电系统上实现电源监控;可以用于实现电能表的正确参考精度;可以用于智能电表实现电压、电流和温度的监测;可以应用于数据采集卡和传感器从机上实现精确的参考电压等。

总之,带隙基准电路是一种非常有效的、精确的参考电路解决方案,能够满足不同的应用需求,为多种电能应用的精准测量提供有用的辅助。

带隙基准电路的基本原理是基于半导体材料的能带结构。

在半导体中,存在一个禁带(能隙),用于区分导带和价带。

导带中的电子能够在半导体中自由移动,而价带中的电子处于固定位置。

当在半导体中施加电压时,电子能够从价带跃迁到导带中,从而形成电流。

带隙基准利用半导体材料特有的能带结构来生成稳定的电压参考。

具体原理如下:首先,在半导体材料中形成两个P-N结,其中一个为温度感应器,另一个是反向偏置的二极管。

当在这两个结之间施加偏置电压时,会形成一条叫做带隙电压(Bandgap Voltage)的电压参考。

该电压与半导体材料的能带隙相关,而与工作温度无关。

带隙基准设计A.指标设定该带隙基准将用于给LDO提供基准电压,LDO的电源电压变化范围为1.4V到3.3V,所以带隙基准的电源电压变化范围与LDO的相同。

LDO的PSR要受到带隙基准PSR的影响,故设计的带隙基准要有高的PSR。

由于LDO是用于给数字电路提供电B.拓扑结构的选择上图是传统结构的带隙基准,假设31M ~M 尺寸相同,那么输出电压为312ln BE T REF V R R N V V += BE V 是负温度系数,对温度求导数,得到公式(Razavi ,Page313):Tq E V m V T V g T BE BE /)4(33-+-=∂∂ 其中,23-≈m 。

如果输出电压为零温度系数,那么:0ln 123=+∂∂=∂∂R R N q k T V T V BE REF 得到:T q E V m V R R N q k g T BE /)4(ln 312-+--=带入:312ln BE T REF V R R N V V += 得到:T gREF V m q E V )4(++=在27°温度下,输出电压等于1.185V ,小于电源电压1.4V ,可这个电路并不能工作在1.4V 电源电压下,因为对于带隙基准里的运放来说,共模输入范围会受到电源电压限制,电源电压的最小值为:source current of drive over pair al differenti input GS BE V V V VDD _______2min ++=其中,2BE V 是三极管2Q 的导通电压,pair al differenti input GS V ___是运放差分输入管对的栅源电压,source current of drive over V ____是运放差分输入管对尾电流源的过驱动电压。

对于微安级别的电流,可以认为:TH GS V V ≈这里将差分输入对的体和源级短接以减小失配,同时阈值电压不会受到体效应的影响。

假设差分对尾电流源的过驱动电压为100mV ,那么,电源电压的最小值为:mV V V VDD pair al differenti input TH BE 100___2min ++=下表列出了smic.13工艺P33晶体管阈值电压和三极管的导通准中运放的正常工作,所以必须改进电路结构,使其可以工作在1.4V 电源电压下。

上图是一种实用的低压带隙基准的结构,假设31M ~M 尺寸相同,同样假设:222122212R R R R R B B A A =+=+那么,输出电压为:3221)ln (R R V R N V V BE T REF += 如果输出电压为零温度系数,那么:0ln 13232=+∂∂=∂∂R R N q k R R T V T V BE REF 得到:23213/)4(ln R R T q E V m V R R N q k g T BE -+--=带入:3221)ln (R R V R N V V BE T REF += 得到:23])4([R R V m q E V T gREF ++=可以通过设置3R 与2R 的比值,将输出电压设定在任意值。

误差放大器输入端在1N 和2N 处,通过将2212/A A R R 设置为1,将这两点电压设定为BJT 导通电压的二分之一,计算出在不同温度min VDD -40° 27° 80°slow 1.341V 1.215V 1.114V typical 1.25V 1.125V 1.024V fast 1.167V 1.042V 0.94V 可以看到,最坏情况出现在Slow Corner 角低温下,电源电压最小值仍然小于1.4V ,意味着这种结构可以满足本次低压设计的要求。

2212/A A R R 越大,电源电压的最小值越低,不过带隙基准环路增益也变低了。

将23/R R 设置为1,输出电压可以为1.2V ,但是这时候带隙基准的低频PSR 会变差,为了提高低频PSR ,运放的增益要很高,但是在这种电路中,PSR 不仅与运放增益有关,还与输出级PMOS 晶体管的输出电阻有关,如下图所示:当PMOS 晶体管3M 输出电阻足够小的时候,3M 的栅源电压微小变化引起的电流变化与流过3M 小信号输出阻抗的电流相比可以忽略不计,那么此时可以近似认为3M 的栅源电压交流短路,那么,有:ro R V V PSR DD REF 3=∆∆=其中ro 为PMOS 晶体管3M 的小信号输出阻抗,这个输出阻抗与漏源电压有关系,将PMOS 晶体管偏置电流设为5uA ,宽长比分三组,各为10um/1um ,20um/2um ,40um/4um ,电源电压设为1.4V ,漏端加一可变电压V1,V1从0V 扫描到1.4V ,如下图所示:测量PMOS晶体管M、1M、4M的小信号输出阻抗随V1的变化关系,得到如下数据:可以看到,晶体管的输出阻抗随漏源电压的增加而增加,随沟道长度的增加也变大,当V1升高到1.2V时,三种沟道长度的晶体管的输出阻抗减小到大约660k的数值,一般来说,R的3数量级在100k左右,如果在电源电压为1.4V时,带隙基准输出1.2V,那么,此时的PSR是:dB k k ro R V V PSR DD REF 166601003-===∆∆= 为了提高低频PSR ,就必须在尽可能提高运放增益的情况下,增加PMOS 晶体管的小信号输出阻抗ro ,这一措施首先是通过减小带隙基准输出电压来实现,带隙基准输出电压要接在LDO 的误差放大器输入端,如果误差放大器使用NMOS 管作为输入差分对,那么其共模输入电压至少为NMOS 管的栅源电压加上尾电流源的过驱动电压:DSSAT GS cm V V V +=用下图可以仿真出误差放大器最低共模输入电压的数值:用5uA 的电流偏置二极管连接的宽长比为20um/1um 的NMOS 管,将其源级用100mV 的电压偏置,模拟尾电流源的过驱动电压,将体接到地上,测量晶体管栅极电压,这个电压大致cm V -40° 27° 80°slow 945mV 876mV 830mVtypical 822mV 753mV 704mV fast 700mV 630mV 580mV模输入电压为0.945V ,这就意味着如果用NMOS 管作为误差放大器输入管,那么带隙基准输出电压不能低于0.945V 。

但是这时候输出级PMOS 晶体管的小信号输出阻抗已经变的很小,比如当L=2um 时,由上面的图可以看到,输出阻抗为大约为7M 欧姆,此时PSR 不是很高。

所以误差放大器的输入管采用PMOS 比较合适,为了提高匹配,降低噪声,PMOS 管的体和源级可以短接,进一步提高了最高共模输入电压。

共模输入电压最多为电源电压减去PMOS 管的栅源电压再减去尾电流源的过驱动电压:DSSAT GS DD cm V V V V --=假设过驱动电压为100mV ,用同样的手段(宽长比20um/1um ,输出电压必须低于383mV 才能使所有Corner 角都能满足误差放大器共模输入范围的要求。

但是带隙基准输出电压越低,LDO 的噪声性能越差,故将带隙基准输出电压设置在400mV ,实际上,可以增加PMOS 晶体管的宽长比,使在Slow Corner 角低温下,最高共模输入电压大于400mV 即可。

把带隙基准输出电压降低到0.4V 左右,使PMOS 晶体管漏源电压有较大的提高,提高了输出阻抗,,如当L=2um 时,由上面的图可以看到,输出阻抗为大约为23M 欧姆,从而提高了PSR :dB Mk ro R V V PSR DD REF 47231003-===∆∆= 这个数值还是不够高,必须寻找其它结构来提高PSR 。

实际上,低频时,PMOS 晶体管栅极电压并不是与电源电压同步变化的,如果运放低频增益很高,那么,在低频时,可以认为晶体管1M 、2M 的漏端电压不随电源电压变化,等效为接地,如下图所示:ΔVro1假设1M 、2M 、3M 尺寸一样,当电源电压变化V ∆时,PMOS晶体管1M 、2M 、3M 栅极电压变化了1V ∆,对于2M ,由基尔霍夫电流定律,可以得到:0/)1(=∆+∆-∆ro V V V gm那么,如果输出级PMOS晶体管的1ro等于1M和2M的输出阻抗ro,那么流过R的电流将约等于零,PSR会有很大的提高,但L是对于M、2M,它们的漏极电压为BJT导通电压,大约为0.7V,1对于M,由于输出电压为0.4V,它的漏极电压与1M、2M显然不3同,所以:1roro为了使它们相等,在晶体管M、2M、3M漏极加入一层cascode1管,如下图所示:ΔVro1这层cascode管强制使晶体管M、2M、3M的漏极电压相等,1从而保证1ro与ro相等,提高了PSR,由于输出电压为0.4V,Cascode管的栅极电压直接接地即可,省去了偏置电路,降低了额外的功耗。

当然,这个结论是在运放增益足够大保证运放输入端电压的变化足够小,可以近似认为接地的条件下得出的,那么运放的设计要保证这个条件的成立。

为了使运放输入端对地电压基本不变,必须提高环路增益,由于电源电压变化范围在1.4V到3.3V内,当电源电压降至1.4V 时,折叠式共源共栅放大器将不适用,可以采用两级运放,加Miller电容补偿,也可以采用如下形式的误差放大器结构:这种结构中,在Vbias 处有一个二极管连接形式的晶体管,它为带隙基准主电路和运放尾电流源提供偏置电压,当电源电压变化时,这个二极管栅极电压和电源电压同时变化,这样一来低频PSR 会减小很多,该运放为单级运放,主级点在第一级输出端,非主级点在Vbias 处而且在高频,只需在主级点处加电容即可保证稳定性。

带隙基准结构(不包括启动电路)如下图所示:C.零温度系数设计假设9M 、10M 、11M 尺寸相同,且:222122212R R R R R B B A A =+=+那么,输出电压的表达式为:3221)ln (R R V R N V V BE T REF += 若要得到零温度系数,那么根据前面推导过公式,有:23213/)4(ln R R T q E V m V R R N q kg T BE -+--=带入输出电压的表达式,得到:23232.1])4([R RV R R V m qE V T g REF ⨯≈++=要得到400mV 的输出电压,那么,得到:3123≈R R 考虑版图布局的对称性,将N 设为8。

现在仿真正温度系数电压特性,理论值为:41923107935.18ln 106.11038.1ln ---⨯=⨯⨯=N q k 用smic.13um 的PNP33管,发射结面积用5×5的,Q2和Q4的N=8,Q1和Q2的N=1,Q1和Q2的偏置电流设在1uA ,Q3和Q4的偏置电流设在10uA ,如下图所示:温度从-40°扫描到80°,测量VQ1-VQ2与VQ3-VQ4随温度变化的曲线,得到下图:实测值为:4107783.112034.21-⨯==CmVslpoe 附上两个Corner slpoefast4107942.1-⨯ slow4107633.1-⨯ Corner 角也无关,实测值与理论值基本吻合。