Allegro基本操作-机构图及网表的导入

- 格式:ppt

- 大小:503.00 KB

- 文档页数:23

26、非电气引脚零件的制作1、建圆形钻孔:(1)、parameter:没有电器属性(non-plated)(2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要比drill hole大一点27、Allegro建立电路板板框步骤:1、设置绘图区参数,包括单位,大小。

2、定义outline区域3、定义route keepin区域(可使用Z-copy操作)4、定义package keepin区域5、添加定位孔28、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电气层之间加入电介质,一般为FR-43、指定电源层和地层都为负片(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find面板选shape(因为铺铜是shape)–> option面板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND层覆铜7、相同的方法完成POWER层覆铜Allegro生成网表1、重新生成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、生成网表:tools –> create netlist,产生的网表会保存到allegro文件夹,可以看一下session log内容。

29、Allegro导入网表1、file –> import –> logic –> design entry CIS(这里有一些选项可以设置导入网表对当前设计的影响)2、选择网表路径,在allegro文件夹。

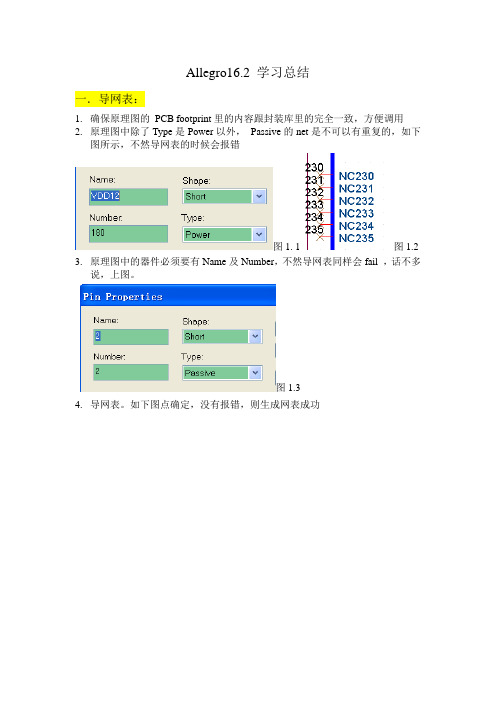

Allegro16.2 学习总结一.导网表:1.确保原理图的PCB footprint里的内容跟封装库里的完全一致,方便调用2.原理图中除了Type是Power以外,Passive的net是不可以有重复的,如下图所示,不然导网表的时候会报错图1. 1图1.2 3.原理图中的器件必须要有Name及Number,不然导网表同样会fail ,话不多说,上图。

图1.34.导网表。

如下图点确定,没有报错,则生成网表成功二.建立焊盘:Allegro的封装必须先建立相对应的PAD.2.1插播一下PAD的基本知识:一个物理焊盘包含三个pad,即:Regular Pad:正规焊盘,在正片中看到的焊盘,也是通孔焊盘的基本焊盘。

Thermal Relief:热风焊盘,也叫花焊盘,在负片中有效。

用于在负片中焊盘与敷铜的接连方式。

Anti Pad:隔离焊盘,也是在负片中有效,用于在负片中焊盘与敷铜的隔离。

SOLDEMASK:阻焊层,使铜皮裸露出来,需要焊接的地方。

PASTEMASK:钢网开窗大小。

表贴元件封装的焊盘名层面尺寸的选取:1.BEGINLAYERRegular Pad:根据器件的数据手册提供的焊盘大小或者自测得的器件引脚尺寸来定。

Thermal Relief:通常比Regular Pad 大20mil,如果Regular Pad 的尺寸小于40mil,根据需要适当减小。

Anti Pad:通常比Regular Pad 大20mil,如果Regular Pad 的尺寸小于40mil,根据需要适当减小2. SOLDEMASK:通常比Regular Pad 大4mil(0.1mm)。

3. PASTEMASK:与SOLDEMASK 一样。

直插元件封装焊盘各层面尺寸的选取:1. BEGINLAYERRegular Pad:根据器件的数据手册提供的焊盘大小或者自测得的器件引脚尺寸来定。

Thermal Relief:通常比Regular Pad 大20mil。

Allegro 16.x 导入网表介绍

今天我们看下Allegro是怎么样导入原理图网表的,有的小白总认为导入网表很难,其实不然只要我们借助下一个Skill工具就可以很简单把原理图网表导入我们的板子里。

先来说下我们要用的Skill工具,这款工具的名字叫CITNO Skill这个工具里包含了很多平时我们设计当中用到的各种功能,比如快速拉取元件到当前光标(不需要拖动屏幕)这在元件布局很有用吧;还有就比较档案间的差异,还有最重要的就自动光绘功能太强了,按菜单顺序执行无需手动设置任何参数就可以把很多文件输出。

不多说了,工具自己搜索下就找到了。

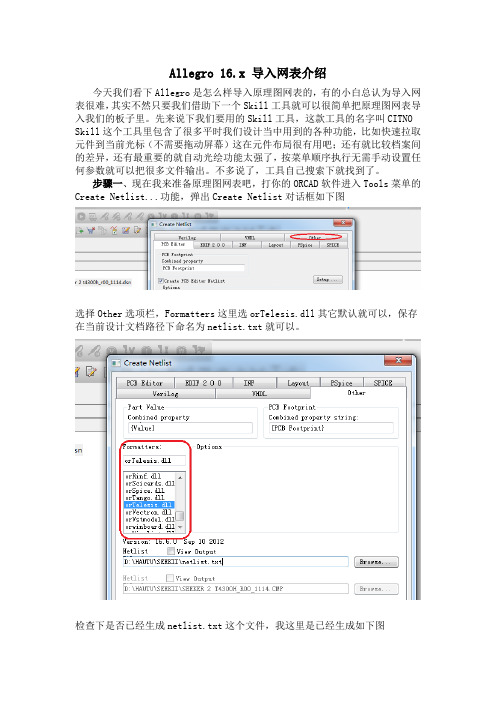

步骤一、现在我来准备原理图网表吧,打你的ORCAD软件进入Tools菜单的Create Netlist...功能,弹出Create Netlist对话框如下图

选择Other选项栏,Formatters这里选orTelesis.dll其它默认就可以,保存在当前设计文档路径下命名为netlist.txt就可以。

检查下是否已经生成netlist.txt这个文件,我这里是已经生成如下图

步骤二,准备已经导入Outline 的PCB档案,下面是我的板子已经有Outline

现在我们的板子是有零件库的,所以必须设置库路径。

现在把CITNO Skill菜单调出来,运行命令:CTRL+z

CITNO Skilll菜单界面图如下

其中Netin,3rd Party这是导入网表功能,即第三方网表导入现在我们开始执行此命令

过几秒钟之后,导入成功

现在我们把器件放置进来,下图我已经成功放置器件。

到这里我们的导入原理图网表教程已经结束,谢谢!。

Allegro导⽹表的⼏种⽅法第⼀种导⽹表⽅法:1:导原理图⽹表点确定,会在设计⽂件所在的⽂件夹下,⽣成⼀个名为allegro的⽂件夹,此时⽹表已经成功⽣成。

2:打开BRD⽂件,导⽹表点File-Import-Logic,弹出Import Logic的对话框,见下图点Import Cadence,成功导⼊器件。

第⼆种导⽹表⽅法:1:如果不是从CIS中导⼊⽹表,采⽤第3⽹表进⾏的话,可以采⽤下⾯的步骤此时要注意的是,要将TXT⽂件中的,NETS中有空格的地⽅都要去掉,⽐如SCR_LOCK GREEN修改成SCR_LOCKGREEN或着SCR_LOCK_GREEN,⽹络名中不可以有空格等特殊符号。

修改好就可以进⾏⽹表的导⼊了。

2:打开BRD⽂件,导⽹表点File-Import-Logic,弹出Import Logic的对话框,见下图选择other选项,找到2222.txt⽂件,点Import Other,器件就成功导⼊BRD⽂件中。

不画原理图进⾏设计1:如果器件PIN数很少的话,就完全没有必要进⾏原理图的绘制。

可以直接添加器件,依照下边的步骤进⾏点击Logic-Part Logic,弹出对话框,见下图在Parts List对话框中,找到Refdes选项,填⼊你所需要的器件名称,点Allegro Components选项,弹出以下对话框点所需要的TXT⽂件,后点OK确定。

在Parts List对话框中,点OK。

就成功添加了⼀个器件。

在以下对话框中查看添加的器件,并把器件放到板⼦中来。

点Place-Manually…直接放置元件的时候(不画原理图),在logic-net logic⽆法进⾏,同样也拿不出元件SET UP –USER PREFERENCES-MICS-logic-edit-enabled,将此选项勾上即可。

后弹出下⾯对话框,点Create,输⼊X1(28),就可以添加⼀个新的⽹络X1(28)选择NET:X1(28),点所要添加的PIN,就可以把⽹络加到指定的PIN中。

Allegro操作说明(中⽂)Word⽂档26、⾮电⽓引脚零件的制作1、建圆形钻孔:(1)、parameter:没有电器属性(non-plated)(2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要⽐drill hole⼤⼀点27、Allegro建⽴电路板板框步骤:1、设置绘图区参数,包括单位,⼤⼩。

2、定义outline区域3、定义route keepin区域(可使⽤Z-copy操作)4、定义package keepin区域5、添加定位孔28、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电⽓层之间加⼊电介质,⼀般为FR-43、指定电源层和地层都为负⽚(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find⾯板选shape(因为铺铜是shape)–> option⾯板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND层覆铜7、相同的⽅法完成POWER层覆铜Allegro⽣成⽹表1、重新⽣成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、⽣成⽹表:tools –> create netlist,产⽣的⽹表会保存到allegro⽂件夹,可以看⼀下session log内容。

29、Allegro导⼊⽹表1、file –> import –> logic –> design entry CIS(这⾥有⼀些选项可以设置导⼊⽹表对当前设计的影响)2、选择⽹表路径,在allegro⽂件夹。

Allegro 如何导入网表一.首先要保证原理图Design rule check 没有问题。

二.从原理图中导出Netlist 。

原理图中Tools->Create Netlist 或者直接点击快捷键;出来如下图所示选择框,选择网表放置的文件夹,点击确定。

导出完成后会生成Netlist 文件(共三个文件)。

注意:导出网表时有时候会提示有error ,如果有error 则无法生成网表,需要按提示将error 解决,然后重新导出。

三.从PCB 中导入Netlist 。

1.打开allegro 新建一个.brd 文件。

2.绘制PCB 边框。

选择菜单项Add->Line 。

Options 窗口设置如下图所示,Line width(线宽)选择0.15mm 。

然后在工作区域内画出一个PCB边框的区域。

3.设置library路径。

选择Setup->User Preferences,弹出User Preferences Editor 对话框,点击 Paths 前面的‘+’号展开来,再点击Library,需要设置其中三个参数,将封装库添加到目录下,如下图所示。

4.导入网络表。

选择菜单File->Import->Logic,如下图所示。

Import dirctionary选择网表放置的文件夹。

点击Import Candence,开始导入。

5.放置元器件。

点击Place->Quickplace菜单,弹出Quickplace对话框,如下图所示。

点击Place 按钮后,元件自动的摆放出来,单击OK 按钮就可以关闭对话框。

完成后如下图所示。

至此,网表导入结束。

在使用DXP的时候,不存在网表导入等问题,大多数的行为已经是软件自动完成了,但是在Allegro中却不行,需要自己手动来完成。

注意在绘制电路板的时候,要先确定绘制区域,以及各个层的状况,边界,安装孔等,都不是随意的来修改。

网表的生成,首先要重新编辑元件编号,先选择dsn文件,然后选择Tools -> Annotate。

scope要选择整个工程,entire。

action中要先选择reset part references to "?"来取消所有的编号,然后再选择无条件的索引更行,Unconditional reference update 来进行全部重新跟新。

然后进行DRC检查,先选择dsn文件,然后再选择Tools -> Design Rules Check。

DRC只能检查出原理图的连接问题,和元器件的属性等。

接着再来查阅器件的封装,在确定器件封装的时候,我有一点点建议,虽然稍微麻烦一点,但是却能够减小出问题的概率。

原理图检查之后,不仅仅要保证没有DRC错误,还要保证没有原理上的错误,这样就生成一张器件清单列表,方法为:在dsn文件被选中的情况下,Tools -> Bill of Materials。

可以不做任何修改的生成bom清单,路径在最下面的Browse可以看到,不做修改会放在同一工程目录下的。

查阅工程目录表,可以看见Outputs下面就有一个.bom后缀名的文件,双击这个文件就可以看见使用了哪一些器件,以及个数。

生成元件清单除了是.bom的方式外,也可以是excel表格,但是由于生成的速度比较慢,所以我就直接选择复制粘贴到excel表格中了。

生成的这个表格有两个作用:一是采购元件的时候有一个详细列表,能够方便的采购人员来查阅;二是将各种器件的封装记录下来,保证每一个封装都存在。

器件封装的绘制见之前的博文。

封装的添加,在原理图中,在dsn文件出右键,选择Editor Object Property, 查阅PCB Footprint这一栏中是不是每一个器件的封装都已经填写上了,并且是不是和相应的原理图对应。

一:导板框

1:导入dxf

-----

---

然后OK ,返回至

此界面,点import,导入,如下图

\

此时DXF已经导入成功,接下来设置板框1:将导入的板框图放一个不用的层,现在我放入新建的DXF层里面

2:copy此板框图,ix横向移动一个数值,以方便后期移回定位

然后将2D线更改为shape,设置在板框层,如图

板框设置完毕

2:设置keepin

选择Edit---z-copy对应右边的选择栏选择好如图

然后选择外框,生成keep in,如图

1: 选择Edit—z-copy,对应右边的选择栏选择好如图

,再选择板框内的定位孔等,如图

,然后将设置好的板框移回导入的结构处,与此重叠如图

此时板框导入设置全部OK

二导网表

1: 设置好库路径setup-------User Preferences

2导网表File—Import--Logic

然后点此选择网表路径,注意allegro下所以路径,及文件名不能有空格,杂乱字符等

然后点import网表导入成功

2:放置元件

点击Place—quick place

后,一次性将所有元件全部调出,如图。