2012DSP复习纲要

- 格式:pdf

- 大小:89.90 KB

- 文档页数:9

指令解释:STM #8765,*AR7+把立即数8765存放到AR7所指定的数据存储单元中去MPY #-2,A立即数-2与T寄存器中的值相乘,并将乘积装入累加器A中 MVPDTABLE,*AR1+把中TABLE标注的程序存储器单元地址中的一个字复制到由AR4所指定的数据存储单元中去。

BC new,AOV若累加器A溢出,则跳转至newBC new,AGT若累加器A中的值大于0,则跳转至newSTL A,*AR1+把累加器A低端存放到AR1所指定的数据存储单元中PRTZ A,#4对A清零并设置重复执行下条指令5次ADD *AR4,16,B,A将AR4所指定的数据存储单元中的值左移16后的值与累加器B中的值相加,并把结果装入累加器A中SUB *AR3+,14,A累加器A中的值减去AR3所指定的数据存储单元中的数左移14位后的值,并将结果装入累加器A中。

即:从累加器A中减去AR3所指定的数据存储单元中的数左移14位后的值的值。

MAC #345H,A,B将T寄存器中的值与立即数345的乘积加上累加器A中的值所得到的和装入累加器B中。

STA, *AR4-(ASM=0)即:将累加器A中的值存储到AR4所指向的数据存储单元中。

MAC *AR3+,*AR4+,A,BAR3所指定数据存储单元中的值与AR4所指定数据存储单元中的值相乘,将乘积与累加器A中的值相加所得到的和装入累加器B中 SUB #12345,8,A,B把累加器A中的值与立即数12345左移8位后的值相减所得到的差装入累加器B 中RPT #99NOP重复执行NOP指令100次MVDD *AR3+,*AR5+将AR3所指定的数据存储单元中的值传送到AR5指定的数据存储单元中。

CALA A用累加器A的滴16位加载PCST T,*AR7-T寄存器高端移位后存储到AR7所指定的数据存储单元中。

DST B,*AR1+将累加器B中STA, *AR4+||LD *AR4-,ALD #0032H,4,A将立即数0032H左移4位后装入累加器A中STM #1000H,*AR2将立即数1000H存放到AR2所指定的数据存储单元中。

1.dsp芯片普遍采用数据总线和程序总线分离的哈佛结构和改进的哈佛结构,有1条程序总线(PB)和3条数据总线(CB、DB、EB)4组地址总线(PAB、CAB、DAB、EAB)。

2.dsp系统的处理过程:①将输入信号x(t)进行抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠②经采样和A/D转换器,将滤波后的信号转换为数字信号x(n)③数字信号处理器对x(n)进行处理,得数字信号y(n)④经D/A转换器,将y(n)转换成模拟信号⑤经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

3.dsp系统的设计过程:①明确设计任务确定设计目标②算法模拟确定性能指标③选择dsp芯片和外围芯片④设计实时的dsp应用系统⑤硬件和软件测试⑥系统集成和测试。

4.双寻址RAM(DARAM):在一个指令周期内,可对其进行两次存取操作,一次读出和一次写入。

单寻址RAM(SARAM): 在一个指令周期内,只能进行一次存取操作。

5.CPU的基本组成:40位算术逻辑运算单元(ALU);2个40累加器(ACCA、ACCB);一个支持-16~31位移位的桶形移位寄存器;乘法器-加法器单元(MAC);比较、选择和存储单元(CSSU);指数编码器;CPU状态和控制寄存器。

6. 乘法器-加法器单元(MAC):具有强大的乘法累加运算功能可在一个流水线周期内完成一次乘法运算和一次加法运算。

7.CPU状态和控制寄存器:状态寄存器0(ST0)、状态寄存器1(ST1)、和处理器工作方式状态寄存器(PMST)。

8.’C54有8个辅助寄存器。

9.流水线操作的原理:将指令分为几个子操作,每个子操作有不同的操作阶段完成,每隔一个机器周期,每个操作阶段就可以进入一条新指令,在同一个机器周期内,在不同的操作阶段可以处理多条指令,相当于并行执行了很多条指令。

T1 T2 T3 T4 T5 T611.中断操作:分为可屏蔽中断和不可屏蔽中断。

12.基本的数据寻址方式:立即寻址、绝对寻址、累加器寻址、直接寻址、间接寻址、存储器映像寄存器寻址、堆栈寻址。

1、请列出几种常用的嵌入式操作系统,并简单说明其特点?2、常用的嵌入式处理器包括?3、DSP按照数据格式可以分为定点和浮点处理器两种4、DSP同单片机不同在于其哈弗结构,请说明其特点?5、DSP与MCU硬件结构比较,有何异同?6、请列出几个常用的DSP制造商?7、CPU组成包括什么?8、DSP的程序执行机构是什么?9、DSP的每次取指操作都是取8条32位指令,称为一个取指包10、指令执行时,每条指令占用一个功能单元11、什么是DSP的数据通路,C6000的数据通路包括什么?12、下列寄存器哪个不能用作条件寄存器A1、A2、A3、B0、B1、B213、C6000DSP中有8个功能单元,分别是什么?14、什么是流水线,其操作原理是什么?15、DSP的流水线都按照所有指令均按取指(fetch)、译码(decode)和执行三级进行。

16、取指级有4个节拍,译码级有2个节拍,执行级对不同类型的指令有不同数目的节拍17、流水线操作以CPU周期为单位,1个执行包在流水线1个节拍的时间就是1个CPU周期。

18、①在DP节拍,1个取指包的8条指令根据并行性被分成几个执行包,执行包由1~8条并行指令组成。

②在DP节拍期间,1个执行包的指令被分别分配到相应的功能单元③同时,源寄存器、目的寄存器和有关数据通路被译码以便在功能单元完成指令执行19、C6000片内为哈佛结构,即存储器分为程序存储空间和数据存储空间。

20、延迟间隙21、取指包:CPU运行时总是一次取8条32位指令,组成一个取指包执行包:所有并行执行的指令组成一个执行包。

22、C6000全部采用间接寻址23、所有寄存器都可以作为线性寻址的地址指针。

而A4~A7,B4~B7这8个寄存器还可以作为循环寻址的地址指针24、DSP试验箱通过仿真器连接电脑,其接口是JTAG口。

25、CCS有两种工作模式,软件仿真模式;硬件在线编程模式26、为什么要使用RTOS27、DSP/BIOS提供了4种不同的线程:硬件中断(HWI)、软件中断(SWI) 、任务(TSK) 、IDLE线程。

一、(1)DSP芯片设置溢出保护位(2)十进制数的截尾与舍入(3)通用DSP芯片是否提供除法指令(4)定标值与计算精度地关系(5)TMS320C54X为浮点或浮点芯片(6)TMS320C54X芯片采用的结构(7)DSP芯片的片内外设包括那些(8)移位寄存器的用途(9)TMS320C54X芯片的CPU寄存器、外设寄存器映射到那个存储空间(10)DSP芯片是否可以通过软件等待状态产生机制使得CPU可以访问慢速I/O设备(11)链接器用于定义存储器并为块分配存储位置的指令(12)当在text段中出现bss指令时,bss是否结束text段(13) 那些指令为非屏蔽中断(14)奈氏抽样定理,为保持信息不丢失,抽样频率。

(15) 16位DSP系统可以达到的精度。

(16) DSP芯片都有MAC硬件的功能(17)哈佛结构的特点(18) 对于DSP芯片的硬件地址产生器的作用(19) 下面对于JTAG标准的作用(20) 定点DSP芯片在进行算术运算中,采用何种数据类型(21) X与Y相乘的结果其定标值Q的计算(22)对于指令缓存CACHE的作用(23)TMS320C54X处理器实现定标的指令(24)影响TMS320C54X存储器结构的状态/控制位(25)DSP的并行结构及片内RAM的双重存取能力,使得CPU可以在一个机器周期内进行多少个存储器操作(26) TMS320C54X的数据总线、程序总线、地址总线有那几组(27)TMS320C54X芯片的可编程开关模块能够在访问程序或数据存储器越过存储块边界时自动插入一个周期(28)TMS320C54X芯片进行外部总线操作时,“程序写”与“数据写”都要用到的总线(29)指令RETE与RET的区别(30)浮点格式分为哪几部分(31)TMS320C54X的串行口有那些(32)一条k段流水能处理n条指令需要多少个时钟周期内。

(33)TMS320C54x的CPU包括那些单元(34)正向溢出处理和负向溢出处理后的最大值,溢出标志位。

DSP原理及应用

复习课

第一章

•:・DSP处理器的特点

•:•与一般处理器的不同

第二章

❖TMS320C54X的总线结构

•:•总线特点

•:•总线的种类

•:•总线的操作方式

•:•片内存储器的配置,控制位的作用

❖CPU状态和控制寄存器的位结构

第三章

❖7种寻址方式

•:•循环寻址的特点(零开销循环),处理器在执行循环时,不用花时间去检查循环计数器的值、

条件转移,可以加速处理能力。

第四章

•:・指令系统

•:・符号和缩写

❖熟悉一些常用指令

•:・ADD、MPY、MAC、DADD、FIRS、

❖BANZ[D] BC[D]

❖RPT RPTB

❖LD ST STH STL STM

•并行加载和存储

❖READA WRITEA

第五章

•:•断的概念

❖常见段

•:•链接器对段的处理

❖常用汇编伪指令

•:•熟悉memory、sections伪指令实例•:•理解链接文件中关于区间的划分、区间的起始地址和长度

第六章

❖CCS的组成特点

•:•编译器、汇编器、链接器•:•探点和断点以及它们的意义

第七章

•条件操作的各种条件表征

❖重复操作

❖中断的类型

❖中断响应过程

❖中断向量的重新映射•:•堆栈的使用

•:•程序实例的理解

第八章

•:•片内外设

•:•多通道缓冲串口的特点

•:•各引脚的功能定义

•:•子地址映射方式

❖时钟和帧同步

❖各引脚收发数据的时序关系

•:•如何通过外部总线与外部存储器、数据存储器以及IO设备链接。

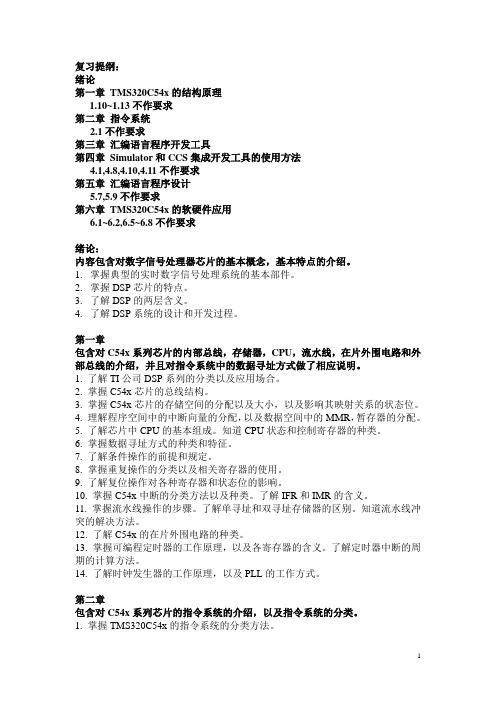

复习提纲:绪论第一章TMS320C54x的结构原理1.10~1.13不作要求第二章指令系统2.1不作要求第三章汇编语言程序开发工具第四章Simulator和CCS集成开发工具的使用方法4.1,4.8,4.10,4.11不作要求第五章汇编语言程序设计5.7,5.9不作要求第六章TMS320C54x的软硬件应用6.1~6.2,6.5~6.8不作要求绪论:内容包含对数字信号处理器芯片的基本概念,基本特点的介绍。

1.掌握典型的实时数字信号处理系统的基本部件。

2.掌握DSP芯片的特点。

3.了解DSP的两层含义。

4.了解DSP系统的设计和开发过程。

第一章包含对C54x系列芯片的内部总线,存储器,CPU,流水线,在片外围电路和外部总线的介绍,并且对指令系统中的数据寻址方式做了相应说明。

1. 了解TI公司DSP系列的分类以及应用场合。

2. 掌握C54x芯片的总线结构。

3. 掌握C54x芯片的存储空间的分配以及大小,以及影响其映射关系的状态位。

4. 理解程序空间中的中断向量的分配,以及数据空间中的MMR,暂存器的分配。

5. 了解芯片中CPU的基本组成。

知道CPU状态和控制寄存器的种类。

6. 掌握数据寻址方式的种类和特征。

7. 了解条件操作的前提和规定。

8. 掌握重复操作的分类以及相关寄存器的使用。

9. 了解复位操作对各种寄存器和状态位的影响。

10. 掌握C54x中断的分类方法以及种类。

了解IFR和IMR的含义。

11. 掌握流水线操作的步骤。

了解单寻址和双寻址存储器的区别。

知道流水线冲突的解决方法。

12. 了解C54x的在片外围电路的种类。

13. 掌握可编程定时器的工作原理,以及各寄存器的含义。

了解定时器中断的周期的计算方法。

14. 了解时钟发生器的工作原理,以及PLL的工作方式。

第二章包含对C54x系列芯片的指令系统的介绍,以及指令系统的分类。

1. 掌握TMS320C54x的指令系统的分类方法。

第三章汇编语言程序设计的一般步骤,COFF文件的基本概念,段的基本概念。

DSP原理与应用复习纲要一、书后习题1、简述数字信号处理器的主要特点。

1-32、TI公司DSP芯片的主要产品系列。

经典产品有:TMS320C1X、TMS320C25、TMS320C3/4X、TMS320C5X、TMS320C8X。

目前主流系列:TMS320C2000、TMS320C5000、TMS320C6000。

3、给出存储器的两种主要结构,并分析其区别。

1-44、给出数字信号处理器的运算速度指标,并给出具体含义。

1-65、TMS320C55x DSP CPU有哪些特征和优点?2-16、TMS320C55x DSP的内部结构由哪几部分组成?2-27、简述指令缓冲单元(I)、程序流程单元(P)、地址流程单元(A)和数据计算单元(D)的组成和功能。

2-38、TMS320C55x DSP有哪些片上外设?2-59、TMS320C55x的寻址空间是多少?当CPU访问程序空间和数据空间时,使用地址是多少位的?理解程序空间和数据空间的寻址方式。

2-610、符合IEEE 1149.1标准的测试/仿真接口(JTAG)的引脚有哪几个?查阅资料了解JTAG接口的功能。

2-7JTAG最初是用来对芯片进行测试的。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

11、TMS320C5509A的复位(/RESET)引脚上出现何种电平会产生复位?复位后,程序入口地址是什么?12、TMS320C55x DSP支持哪三种寻址模式?3-113、查阅资料,了解.text,.bss,.data,.sect,.usect等汇编伪指令的使用方法。

附录14、查阅资料,了解链接伪指令MEMORY和SECTIONS的使用方法。

附录15、理解指令:MOV *AR3+<<#16, AC1 。

3-4指令功能是把AR3指向的地址里面的内容左移16位(二进制左移16位相当于十六进制左移四位,所以在右边补四个0),把AR3指向的地址里面的内容左移后的内容送进AC1,之后指针AC3自加一次。

DSP技术及应用复习概要一、1、DSP按数据格式来分类,可分定点DSP芯片和浮点DSP芯片。

P22、TI DSP主要分为哪三个系列,分别有什么特点,和应用场合?P53、TI公司为DSP C6000推出的集成开发环境CCS提供了配置、建立、调试、跟踪和分析程序的工具。

4、DSP开发中,一个最小的C应用程序,一般包含以下几个文件:(1)主程序main.c。

这个文件必须包含一个main()函数作为C程序的入口点。

(2)链接命令文件.cmd。

这个文件包含了DSP和目标板的存储器空间的定义以及代码段、数据段是如何分配到这些存储器空间的。

这个文件可有用户自己编写。

(3)C运行库文件rts6400.lib(或者DSP兼容的rstxxxx.lib)。

C运行库提供了如printf 等标准C函数,还提供了C环境下的初始化函数c_int00()。

这个文件位于CCS安装目录下的\c6000\cgtools\lib子目录中。

(4)Vectors.asm。

这个文件中的代码将作为IST(中断服务表),并且必须被链接命令文件(.cmd)分配到0地址。

5、MFLOPS、MIOS、MIBS、MIPS含义。

P4MFLOPS——每秒执行百万个浮点操作MIOS——每秒执行百万次操作MIBS——每秒百万位MIPS——每秒百万条指令6、GPIO寄存器GPXEN、GPXDIR和GPXV AL,写0写1的作用?GPIO的功能?P274 GPIO使能寄存器(GPEN)GPIO方向寄存器(GPDIR):决定某一给定GPIO引脚输入还是输出。

相应GPIO信号通过GPxEN位字段使能时,GPDIR才有效。

GPIO数值寄存器(GPV AL):表示给定GPIO引脚驱动的数值,或给定GPIO引脚上检测到的数值。

7、TMS320DM642定点还是浮点?处理器位数TMS320DM642是32位定点型DSP2003年推出,主要面向数字媒体,增加了3个双通道数字视频口,8个功能单元,4GB可寻址地址空间,片外存储器通过EMIF(外部存储器接口)8、EMIF作用P39支持各种外部器件的无缝接口,包括流水线的同步突发SRAM(SBSRAM)、同步DRAM (SDRAM)、异步器件(SRAM、ROM和FIFO等)、以及外部共享存储器件C64x的EMIF支持类型:ZBTSRAM、同步FIFO、流水线式SBSRAM、直通式SBSRAM 9、EDMA P74EDMA控制所有二级高速缓存/内存控制器和C64x DSP外设之间的数据传输,无需占用CPU时间。

DSP(数字信号处理)技术复习资料1.简述数字信号处理器的主要特点(P4)。

数字信号处理(Digital Signal Processing)简称DSP。

主要特点:(1)采用哈佛结构;(2)采用多总线结构;(3)采用流水线结构;(4)配有专用的硬件乘法器-累加器;(5)具有特殊的寻址方式和指令;(6)支持并行指令操作;(7)硬件配置强,具有较强的接口功能;(8)支持多处理器结构。

2. 请给出数字信号处理器的运算速度指标(P6)。

(1)MAC时间:一次乘法和一次加法的时间;(2)FFT执行时间:运行一个N点FFT程序所需的时间;(3)MIPS:每秒执行百万条指令;(4)MOPS:每秒执行百万次操作;(5)MFLOPS:每秒执行百万次浮点操作;(6)BOPS:每秒执行十亿次操作。

(7)指令周期:执行一条指令所需的最短时间,数值等于主频的倒数;常用ns(纳秒)。

3.简述C55x的存储器配置情况(P11~12)。

(1)C55x采用统一的存储空间和I/O空间;(2)C55x的片内存储空间共有352KB(146K字),外部存储空间共有16MB(8M字);(3)存储区支持的存储器类型有异步SRAM,异步EPROM、同步DRAM和同步突发SRAM;(4)C55x的I/O空间与程序/地址空间分开;(5)I/O空间的字地址为16位,能访问64K字地址;(6)当CPU读/写I/O空间时,在16位地址前补0来扩展成24位地址。

4.TMS320C55x的寻址空间是多少当CPU访问程序空间和数据空间时,使用的地址是多少位(P51、P53~54)。

(1)C55x的寻址空间为16MB(24位地址,2^24 = B = 16MB)(2)CPU访问程序空间时,使用24位的地址;(3)访问数据空间时,使用23位地址,使用时23位地址左移一位将地址总线上的最低有效位(LSB)置0。

5.VC5509A的PGE LQFP封装芯片共有多少个引脚其中GPIO引脚有多少个并行地址总线引脚有多少个并行双向数据总线引脚有多少个(P13~15)(1)引脚:144个;(2)GPIO引脚:7个;(注:GPIO[7:6,4:0])(3)并行总线引脚:14个;(注:A[13:0])(4)并行双向数据引脚:16个;(注:D[15:0])6.C55x的指令分为两个阶段,第一阶段为取指阶段,第二阶段为执行阶段;7.C55x的CPU包含4个40位的累加器,辅助寄存器ARn有16位,XARn有 23 位;(P29、P31)8.XF位是寄存器ST1_55中的第13位,它是一通用的输出位,能用软件处理且可输出至DSP引脚。