第8章电磁兼容测量技术

- 格式:ppt

- 大小:1.20 MB

- 文档页数:64

电磁兼容试验和测量技术振铃波抗扰度试验1. 引言1.1 背景介绍电磁兼容是指电子设备在电磁环境中能够正常工作而不产生有害的干扰,同时也不受外部电磁场的干扰。

随着电子设备的广泛应用,电磁干扰问题变得愈加突出。

振铃波抗扰度试验作为电磁兼容测试的重要环节之一,对电子设备的抗扰度能力进行评估和验证,对提高设备的稳定性和可靠性具有重要意义。

在实际应用中,由于电子设备需要在各种不同的电磁环境下工作,如电信网络、雷电场等,其抗扰度能力就显得尤为重要。

通过进行振铃波抗扰度试验可以有效评估设备在强电磁环境下的工作性能,为设备的设计和生产提供参考依据。

本文旨在探讨振铃波抗扰度试验的原理、试验方法、测量技术以及试验结果的分析,同时分析影响试验结果的因素,为提高设备的抗扰度能力提供技术支持和指导。

通过深入研究振铃波抗扰度试验,可以为电子设备在电磁环境下稳定运行提供重要的技术支持。

1.2 研究意义电磁兼容试验和测量技术是当今电子设备领域中非常重要的研究方向。

在现代社会中,各种电子设备的数量和种类不断增加,而这些设备之间往往会相互干扰,甚至会产生严重的电磁兼容问题。

振铃波抗扰度试验作为电磁兼容试验的一种重要形式,具有非常重要的研究意义。

振铃波抗扰度试验主要是用来模拟电磁环境下设备的抗扰度能力。

通过对设备在电磁环境中的抗扰度进行测试,可以评估设备在实际应用中的稳定性和可靠性,为设备的设计和生产提供重要参考。

振铃波抗扰度试验也可以帮助研究人员了解电磁环境中可能出现的干扰形式和程度,从而为电磁兼容问题的解决提供借鉴和参考。

振铃波抗扰度试验在电磁兼容领域中具有重要的研究意义。

通过深入研究和探讨振铃波抗扰度试验的原理和方法,可以为提高电子设备的抗干扰能力,促进电磁兼容技术的发展和应用,提供宝贵的理论支持和实践指导。

1.3 研究目的【研究目的】是为了验证振铃波抗扰度试验的有效性和准确性,进一步提高电磁兼容性试验技术水平,为电子设备的设计和生产提供科学依据。

电磁兼容试验和测量技术电磁兼容试验和测量技术是电磁兼容性领域中不可或缺的重要方面,它对于保障电子设备的正常运行以及维护通信系统的稳定性发挥着关键作用。

电磁兼容试验和测量技术可具备以下几个方面:1. 电磁兼容试验技术电磁兼容试验技术是指对电子设备进行电磁兼容性试验,以评估其在电磁环境下的工作能力。

其中包括:(1) 辐射发射试验:通过外部电磁波源在电磁环境下对待测设备的辐射发射进行测试。

(2) 抗干扰试验:是针对设备在电磁环境中承受外界电磁影响而采取的试验措施。

(3) 静电放电试验:在模拟静电放电干扰环境下,对设备进行静电放电测试,以模拟实际工作环境。

2. 电磁兼容测量技术电磁兼容测量技术是指测量电磁环境下设备的电磁参数,以验证其符合电磁兼容性要求,包括:(1) 辐射场测量:是对电子设备周围辐射场进行的测量,并对其辐射程度进行分析。

(2) 反射场测量:是对电子设备所反射出来的信号进行的测量,可通过调整反射屏幕的结构改变设备的反射特性。

(3) 传导场测量:是对电子设备周围传导场强度的测量,以确定其对设备的影响。

3. 电磁兼容性评估电磁兼容性评估是根据电磁兼容性试验和测量的结果来对设备进行评估,以确定其是否符合要求,包括:(1) 辐射发射评估:通过对设备的辐射发射测试,评估设备对周围环境的辐射干扰程度,以确定是否满足相关标准和要求。

(2) 抗干扰评估:通过对设备的抗干扰试验和测量,评估设备的抗干扰能力,以确保其能够在恶劣环境下正常工作。

(3) 辐射耐受性评估:根据设备在电磁环境中的工作特性,对其所能接受的辐射程度进行评估,以确保设备能够在不同强度的辐射环境下均能正常工作。

综上所述,电磁兼容试验和测量技术是保障电子设备正常工作和维护通信系统稳定性的关键技术之一。

在实际应用中,需要综合运用多种方法和技术手段,确保设备的电磁兼容性能得到充分保证。

芯片集成电路电磁兼容测试技术摘要:当今,集成电路的电磁兼容性越来越受到重视,芯片电磁兼容(EMC)技术关乎整机电子系统及其周围电子器件的运行的安全可靠性,电磁兼容性。

电子设备和系统的生产商努力改进他们的产品以满足电磁兼容规范,降低电磁发射和增强抗干扰能力, 集成电路(IC)的电磁兼容性(EMC)的测试方法正受到越来越多的关注,文章基于国内外资料调研和课题组的研究成果, 介绍了器件级(IC)EMC测试方面的发展现状,测试标准,详细介绍了器件级(IC)主要的电磁兼容测试方法。

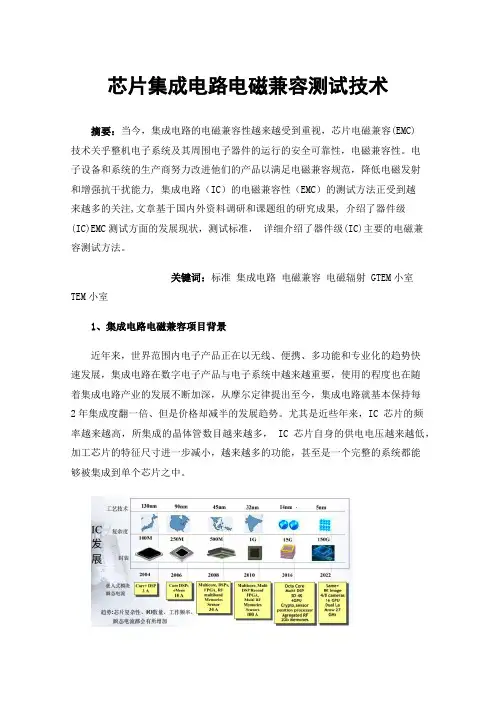

关键词:标准集成电路电磁兼容电磁辐射 GTEM小室TEM小室1、集成电路电磁兼容项目背景近年来,世界范围内电子产品正在以无线、便携、多功能和专业化的趋势快速发展,集成电路在数字电子产品与电子系统中越来越重要,使用的程度也在随着集成电路产业的发展不断加深,从摩尔定律提出至今,集成电路就基本保持每2年集成度翻一倍、但是价格却减半的发展趋势。

尤其是近些年来,IC 芯片的频率越来越高,所集成的晶体管数目越来越多, IC芯片自身的供电电压越来越低,加工芯片的特征尺寸进一步减小,越来越多的功能,甚至是一个完整的系统都能够被集成到单个芯片之中。

图1 IC发展总体趋势图2 IC性能发展趋势根据SEMI的分析报告,全球半导体市场从2015到2025年的预期份额,包括了各类型芯⽚所占的份额。

相⽚2015年的3427亿美元,预计在2025的市场份额将会达到6556亿美元,复合增长率为6.7%。

集成电路的快速发展,这为集成电路的大范围、多层次应用奠定了基础。

尤其在消费类产品领域,这种发展趋势尤为明显,各种数码类产品的普及就是很好的说明。

图3各类型芯⽚所占的份额图4 各尺寸芯⽚所占的份额这种快速发展也造成了电子系统电磁兼容性问题的日益突出,芯⽚复杂性、IO口的数量、⽚作频率、瞬态电流都会有所增加,这些发展均使得芯片级电磁兼容显得尤为突出,更高的集成度和使用密度,是片内和片外耦合的发生几率大大提高。

静电放电抗扰度试验是电磁兼容性(EMC)领域中的一种重要测试方法,用于评估电子设备在静电放电干扰下的抗扰度。

以下是关于静电放电抗扰度试验的一般流程和技术:

1. 试验介绍:

-静电放电试验是模拟人体静电放电现象,通过给予设备定量的静电放电来评估设备对此种电磁干扰的抗扰度。

2. 试验设备:

-静电放电试验通常使用专门的试验设备,包括静电电源、人体模型(HBM)或机器模型(MM)、试验台等。

3. 试验参数:

-试验参数包括静电放电电压、放电极间距、放电次数等,这些参数通常根据相关标准或规范进行设置。

4. 试验环境:

-静电放电试验需要在恒温、恒湿的环境条件下进行,以确保试验结果的可靠性。

5. 试验过程:

-试验前,需要对设备进行预试验,以确定设备的敏感性和适应

性。

-在试验过程中,按照预设的参数和序列进行静电放电,并记录设备在放电过程中的反应和性能变化。

6. 试验评估:

-根据试验结果,对设备的抗扰度进行评估和分析。

-静电放电试验通常根据相关标准或规范,将试验结果与预设的抗扰度要求进行比较,判断设备是否符合要求。

7. 报告和验证:

-完成试验后,生成详细的试验报告,包括试验条件、试验结果、设备反应等信息。

-可以通过再次测试或其他验证手段,确认设备的抗扰度改进措施的有效性。

需要注意的是,静电放电试验应该由专业的测试机构或资质认证实验室进行,以确保试验的准确性和可靠性。

对于电子产品的设计和开发过程中,合理的电磁兼容性设计和抗扰度验证是非常重要的,可以帮助提高产品的可靠性和稳定性。

电磁兼容测试方案第1篇电磁兼容测试方案一、前言随着电子技术的飞速发展,各类电子设备广泛应用于国民经济的各个领域。

电子设备在实现其功能的同时,也产生了电磁干扰(EMI),可能影响其他设备的正常工作。

因此,对电子设备进行电磁兼容(EMC)测试显得尤为重要。

本方案旨在为某项目制定一套合法合规的电磁兼容测试方案,确保项目顺利进行。

二、测试目的1. 验证被测设备在规定的工作环境中,电磁干扰特性是否符合相关标准要求。

2. 验证被测设备在规定的工作环境中,电磁抗干扰特性是否符合相关标准要求。

3. 确保被测设备在复杂电磁环境中稳定、可靠地工作。

三、测试依据1. GB/T 3365-2018《电磁兼容通用测试方法》2. GB 9254-2018《信息技术设备的无线电骚扰限值和测量方法》3. GB/T 17626.2-2018《电磁兼容试验和测量技术 静电放电抗扰度试验》4. GB/T 17626.3-2016《电磁兼容试验和测量技术 射频电磁场辐射抗扰度试验》5. GB/T 17626.6-2017《电磁兼容试验和测量技术 射频场传导抗扰度试验》6. 项目技术要求及设备说明书四、测试项目及要求1. 无线电骚扰测试- 测试频率范围:30MHz~1GHz- 测试限值:参照GB 9254-2018标准- 测试方法:采用开阔场测试法、 TEM小室测试法等方法进行测试。

2. 静电放电抗扰度测试- 测试等级:参照GB/T 17626.2-2018标准- 测试方法:采用接触放电和空气放电两种方式对被测设备进行测试。

3. 射频电磁场辐射抗扰度测试- 测试频率范围:80MHz~1GHz- 测试等级:参照GB/T 17626.3-2016标准- 测试方法:采用电场和磁场两种方式进行测试。

4. 射频场传导抗扰度测试- 测试频率范围:150kHz~80MHz- 测试等级:参照GB/T 17626.6-2017标准- 测试方法:采用AM调制信号进行测试。

集成电路电磁兼容测试技术概述作者:王媛媛许琼童军来源:《硅谷》2008年第19期[摘要]随着电子工业的发展,集成电路的功能要求日趋多样化,内部结构日趋复杂化,越来越多的功能,甚至是一个完整的片上系统都能够被集成到单个芯片之中,包含模拟、数字等多种形式的工作电路于一体。

这种发展趋势使得芯片级的电磁兼容问题显得尤为突出。

主要介绍集成电路电磁发射测量技术的发展状况。

[关键词]集成电路电磁兼容测试中图分类号:TN407 文献标识码:A 文章编号:1671-7597(2008)1010034-01一、引言随着电子技术的快速发展,各类电子电器设备已经广泛应用于人们的日常生活之中。

这些电子设备在提高人们生活品质的同时,也带来了大量的电磁污染。

过去,集成电路生产商关心的重点是研究集成电路的设计技术、研制和生产成本、应用领域和使用性能,几乎很少需要考虑电磁兼容的问题。

但是现在,集成电路设计技术的发展使得电磁兼容性问题越来越突出,直接影响芯片功能的实现,因此也越来越受到重视。

集成电路的电磁兼容性能有两方面考虑:一、集成电路器件在预定工作场所的电磁环境下工作时,不会影响临近其他器件的工作;二、自身工作性能也不会被其他器件所影响。

这样,才能认为该器件满足此电磁环境下的电磁兼容性要求。

目前,世界上众多国家和国际王媛媛许琼童军(西安科技大学电气与控制工程学院陕西西安710054)组织已经针对电子电气产品制定出相应的EMC(Electromagnetic Compatibility)标准。

电磁兼容性要求已成为系统工作可靠性的重要考察内容。

二、集成电路的电磁兼容标准制定机构由于集成电路的电磁兼容是一个相对较新的学科,尽管对于电子设备及子系统已经有了较详细的电磁兼容标准,但对于集成电路来说其测试标准却相对滞后。

国际电工委员会第47A 技术分委会(IEC SC47A)早在1990年就开始专注于集成电路的电磁兼容标准研究。

此外,北美的汽车工程协会也开始制定自己的集成电路电磁兼容测试标准SAE J 1752,主要是发射测试的部分。

电磁兼容(Electromagnetic Compatibility,EMC)是指电子设备在其工作环境中,既不会对外部环境产生有害的电磁干扰,也能抵抗来自外部环境的电磁干扰的能力。

静电放电抗扰度试验是评估电子设备抗静电放电干扰能力的一种重要测试。

静电放电是指人体或其他物体在与电子设备接触或靠近时,由于静电荷积累而发生放电现象,可能导致设备故障或数据损坏。

因此,进行静电放电抗扰度试验可以评估设备在面对静电放电时的表现和稳定性。

静电放电抗扰度试验通常包括以下步骤:

1. 试验设备准备:确保测试设备和环境符合相关标准要求,包括静电发生器、接地装置等。

2. 设备连接:将待测试设备与静电发生器和接地装置连接好,确保连接正确可靠。

3. 放电过程:在规定的条件下,通过控制静电发生器向设备施加静电放电,模拟真实环境中可能出现的静电放电情况。

4. 测量和评估:测试过程中记录设备的反应、性能以及任何异常情

况,评估设备的抗静电放电能力是否符合标准要求。

5. 结果分析:根据测试结果分析设备的抗静电放电性能,确定是否需要改进设计或采取其他措施提高设备的抗扰度。

通过静电放电抗扰度试验,可以帮助电子设备制造商评估设备在静电环境下的稳定性和可靠性,确保设备在实际使用中不受静电放电干扰的影响,提高设备的电磁兼容性。

电磁兼容测试常见故障及排除技术以下为正文:什么是电磁兼容之测试故障?有什么解决办法?对于从事EMC的工程师,在日常工作中经常会遇到瓶颈,而解决这样的问题需要很多时间和精力。

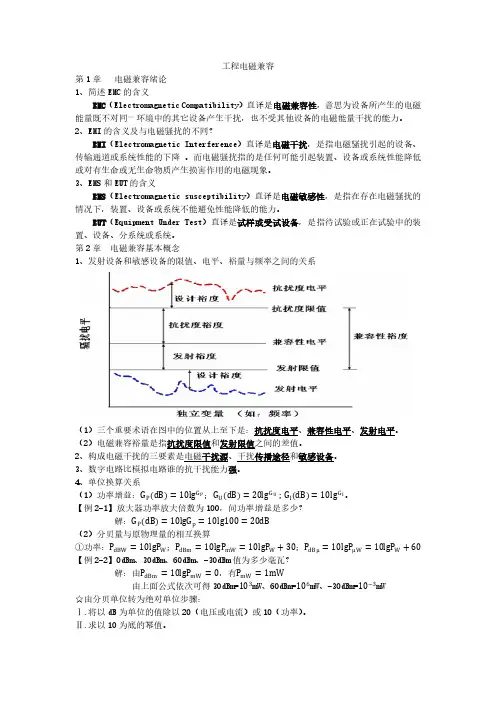

比如说,EMC测试包括两大方面内容:对其向外界发送的电磁骚扰强度进行测试,以便确认是否符合有关标准规定的限制值要求;对其在规定电磁骚扰强度的电磁环境条件下进行敏感度测试,以便确认是否符合有关标准规定的抗扰度要求。

对于从事单片机应用系统设计的工程技术人员来说,掌握一定的EMC测试技术是十分必要的。

1、EMC测试(1)测试环境为了保证测试结果的准确和可靠性,电磁兼容性测量对测试环境有较高的要求,测量场地有室外开阔场地、屏蔽室或电波暗室等。

(2)测试设备电磁兼容测量设备分为两类:一类是电磁干扰测量设备,设备接上适当的传感器,就可以进行电磁干扰的测量;另一类是在电磁敏感度测量,设备模拟不同干扰源,通过适当的耦合/去耦网络、传感器或天线,施加于各类被测设备,用作敏感度或干扰度测量。

(3)测量方法电磁兼容性测试依据标准的不同,有许多种测量方法,但归纳起来可分为4类;传导发射测试、辐射发射测试、传导敏感度(抗扰度)测试和辐射敏感度(抗扰度)测试。

(4)测试准备①试验场地条件:EMC测试实验室为电波半暗室和屏蔽室。

前者用于辐射发射和辐射敏感测试,后者用于传导发射和传导敏感度测试。

②环境电平要求:传导和辐射的电磁环境电平最好远低于标准规定的极限值,一般使环境电平至少低于极限值6dB。

③试验桌。

④测量设备和被测设备的隔离。

⑤敏感性判别准则:一般由被测方提供,并实话监视和判别,以测量和观察的方式确定性能降低的程度。

⑥被测设备的放置:为保证实验的重复性,对被测设备的放置方式通常有具体的规定。

(5)测试种类传导发射测试、辐射发送测试、传导抗扰度测试、辐射抗扰度测试。

(6)常用测量仪电磁干扰(EMI)和电磁敏感度(EMS)测试,需要用到许多电子仪器,如频谱分析仪、电磁场干扰测量仪、信号源、功能放大器、示波器等。

电磁兼容试验和测量技术电磁兼容试验和测量技术是现代电子设备开发和应用中不可或缺的重要环节。

随着电子设备的广泛应用,电磁兼容性问题也日益突出,因此对电磁兼容性进行试验和测量显得尤为重要。

本文将对电磁兼容试验和测量技术进行详细介绍。

一、电磁兼容性概述电磁兼容性是指在特定的电磁环境下,各种电子设备能够在相互之间以及与环境中的其他电子设备之间正常工作,而不产生不可接受的电磁干扰。

在现代社会中,电子设备越来越多,各种设备之间相互干扰的问题也日益突出。

电磁兼容试验和测量技术的目的就是为了确保各种电子设备在不同的电磁环境下能够正常工作,而不会相互干扰。

二、电磁兼容试验技术1. 辐射发射试验:辐射发射试验是指对电子设备所产生的电磁辐射进行测试。

通过在特定的频率范围内对设备进行发射试验,可以评估设备对周围环境的电磁辐射程度。

常用的试验方法包括开路辐射试验和传导辐射试验。

2. 抗干扰能力试验:抗干扰能力试验是指对电子设备在外界电磁干扰下的抗干扰能力进行测试。

通过模拟外界电磁干扰,如电磁波、电磁脉冲等,对设备进行试验,评估设备的抗干扰能力。

常用的试验方法包括抗辐射干扰试验和抗传导干扰试验。

3. 静电放电试验:静电放电试验是指对设备在静电放电干扰下的抗干扰能力进行测试。

通过模拟人体静电放电,对设备进行试验,评估设备的抗静电放电能力。

常用的试验方法包括人体模拟静电放电试验和机器模拟静电放电试验。

三、电磁兼容测量技术1. 辐射发射测量:辐射发射测量是指对电子设备产生的电磁辐射进行测量。

通过使用频谱分析仪、天线等测量设备,对设备在特定频率范围内的辐射进行测量,并评估辐射的强度和频率分布。

2. 抗干扰能力测量:抗干扰能力测量是指对电子设备在外界电磁干扰下的抗干扰能力进行测量。

通过使用信号发生器、功率放大器等测量设备,模拟外界电磁干扰,对设备的工作状态和性能进行测量,并评估设备的抗干扰能力。

3. 静电放电测量:静电放电测量是指对设备在静电放电干扰下的抗干扰能力进行测量。

国际标准CEI IEC 61000-4-7第二版 2002-08电磁兼容性 第4-7章测试与测量技术——电源系统及其相连设备的谐波、间谐波测量方法和测量仪器技术标准Copyright – 版权所有未经出版人书面同意,不得擅自以任何形式或任何方式复制或使用,其中包括电子、机械、影印、缩微等方式。

International Electrotechnical Commission, 3. rue de Varembe, PO Box 131, CH-1211 Geneva 20. Switzerland Telephone: +41 22 919 02 11Telefax: +41 22 919 03 00 E-mail: inmaii@iec.ch Web. 国际电工委员会 CODE PRIXPRICE CODEWPour prix voir catalogue en vigueur For price see current catalogue目录前沿介绍1 范围2 参考标准3 定义、符号和名称3.1 与频率分析有关的定义3.2 与谐波有关的定义3.3 与失真系数有关的定义3.4 与间谐波有关的定义3.5 符号3.5.1 符号与缩写3.5.2 名称4 对各种测量仪器的共同要求和基本概念4.1 测量信号的特点4.2 测量仪器的准确度等级4.3 测量的类型4.4 测量仪器的基本结构4.4.1 主要组成部分4.4.2 后处理部分5 谐波测量5.1 电流输入电路5.2 电压输入电路5.3 准确度要求5.4 发射测量的装置5.5.1 分组和平滑处理5.5.2 谐波发射的限制性规定5.6 电压子谐波群的测量6 其他分析方法7 过渡阶段8 基本介绍附件A(仅供参考)间谐波的测量附件B(仅供参考)高于谐波频率但不超过9kHz的频率分量的测量附件C(仅供参考)分组法涉及的技术问题参考文献图1——测量仪器的基本结构图2——单项发射测量的测量装置图3——三项发射测量的测量装置国际电工委员会电磁兼容性(EMC)——第4-7章测试和测量技术——电源系统及其相连设备的谐波、间谐波测量方法和测量仪器的技术标准前言1)国际电工委员会(IEC)是一家世界性的标准化组织,它由各成员国的电工委员会(国际电工委员会的成员国委员会)组成。

产品办理EMC电磁兼容测试的标准EMC电磁兼容测试指的是对电子产品在电磁场方面干扰大小(EMI)和抗干扰能力(EMS)的综合评定,是产品质量重要的指标之一,电磁兼容的测量由测试场地和测试仪器组成。

EMC电磁兼容测试产品的标准:CISPR 14-1:2000 电磁兼容家用电器、电动工具和类似器具的要求第1部分:发射CISPR 14-2:2006 电磁兼容家用电器、电动工具和类似器具的要求第2部分:抗扰度产品类标准EN 61000-1-1:1992 电磁兼容(EMC)第1部分:总则第1节:基本定义和术语的应用与解释EN 61000-2-2:2002 电磁兼容(EMC)第2部分:环境公用低压供电系统低频传导骚扰及信号传输的兼容水平EN 61000-2-4:2002 电磁兼容(EMC)第2-4部分:环境低频传导骚扰的兼容水平EN 61000-2-9:1996 电磁兼容(EMC)第2部分:环境第9节:HEMP环境叙述干扰辐射EMC基本标准EN 61000-2-10:1999 电磁兼容性(EMC)第2部分:环境第10节:HEMP环境描述传导骚扰EN 61000-2-12:2003电磁兼容性(EMC)第2部分:环境第12节:公共中压电源供给系统中低频传导骚扰和信号传输的兼容性水平EN61000-3-2:2000电磁兼容(EMC)第3-2部分:额定值辐射谐波电流的额定值(设备输入电流为16A/相位)EN61000-3-3:1995电磁兼容(EMC)第3-3部分:限值每相额定电流≤6A并不需有条件连接的设备用公共低压供电系统中电压变化、电压波动和闪烁的限制EN61000-3-11:2000电磁兼容性(EMC)第3-11部分:限值公共低压供电系统中电压变化,电压波动和闪烁的限制额定电流不低于75A并限于条件连接的设备EN 610004-1::2000电磁兼容(EMC)第4-1部分:试验和测量技术61000-4系列综述EN61000-4-2:2001电磁兼容(EMC)第4-2部分:试验和测量技术静电放电抗干扰试验EN61000-4-3:2002 电磁兼容(EMC)第4-3部分:试验和测量技术辐射、射频和电磁场的抗干扰度试验EN61000-4-4:2004 电磁兼容(EMC)第4-4部分:试验和测量技术电快速瞬变脉冲群抗扰度试验EN61000-4-5:2001 电磁兼容(EMC)第4-5部分:试验和测量技术浪涌(冲击)抗扰度试验EN61000-4-6:2001 电磁兼容(EMC)第4-6部分:试验和测量技术射频场感应的传导骚扰抗扰度EN61000-4-7:2002 电磁兼容(EMC)第4-7部分:试验和测量技术供电系统及所连设备诸波、谐间波的测量和测量仪器导则EN61000-4-8:2001 电磁兼容(EMC)第4-8部分:试验和测量技术工频磁场抗干扰试验EN61000-4-9:2001 电磁兼容(EMC)第4-9部分:试验和测量技术脉冲磁场抗扰度试验EN61000-4-10:2001 电磁兼容(EMC)第4-10部分:试验和测量技术阻尼振荡磁场抗扰度试验EN61000-4-11:2004 电磁兼容(EMC)第4-11部分:试验和测量技术电压暂降、短时中断和电压变化的抗扰度试验EN61000-4-12:2001 电磁兼容(EMC)第4-12部分:试验和测量技术振荡波抗干扰度试验EN61000-4-13:2002 电磁兼容(EMC)第4-13部分:试验和测量技术在交流电源端的谐波和谐间波(包括主要信号)的低频抗扰度试验EN61000-4-14:2004 电磁兼容(EMC)第4-14部分:试验和测量技术电压波动抗扰度试验EN61000-4-15/A1:2003 电磁兼容性第4部分:试验和测量技术第15节:闪烁仪功能和设计规范EN61000-4-16:1998 电磁兼容性(EMC)第4-16部分:试验和测量技术对频率在0-150kHz范围内的传导共模骚扰的抗扰试验EN61000-4-17:2004 电磁兼容(EMC)第4-17部分:试验和测量技术直流电源输入端口纹波抗扰度试验EN61000-4-20:2003 电磁兼容性(EMC)第4-20部分:试验和测量技术横电磁波(TEM)波导管中的发射和抗干扰试验EN61000-4-21:2003 电磁兼容性(EMC)第4-21部分:试验和测量技术混响实验室法EN61000-4-23:2000 电磁兼容性(EMC)第4-23部分:试验和测量技术HEMP和其他辐射干扰保护装置的试验方法EN61000-4-24:1997 电磁兼容(EMC)第4部分:试验和测量技术第24节:HEMP保护装置的试验方法基础EMC出版物EN61000-4-25:2002 电磁兼容性(EMC)第4-25部分:试验和测量技术设备和系统的HEMP抗扰性试验方法EN61000-4-27:2000 电磁兼容性(EMC)第4-27部分:试验和测量技术不平衡,抗扰性试验EN61000-4-28:2000 电磁兼容性(EMC)第4-28部分:试验和测量技术电源频率变化,抗扰性试验EN61000-4-29:2000 电磁兼容性(EMC)第4-29部分:试验和测量技术直流输入电源口电压暂降,短暂中断和电压变化的抗扰性试验EN61000-4-30:2003 电磁兼容性(EMC)第4-30部分:试验和测量技术电力质量测量方法EN61000-5-5:1996 电磁兼容性(EMC)第5部分:安装和调节指南,第5节:HEMP射导骚扰保护装置规范基础(EMC)出版物EN61000-5-7:2001 电磁兼容性(EMC)第5-7部分:安装和调试指南外壳抗电磁电磁干扰(EM码)的保护程度EN61000-6-1:2001 电磁兼容(EMC)第6-1部分:通用标准居住、商业和轻工业环境的抗扰度EN61000-6-2:2001 电磁兼容(EMC)第6-1部分:通用标准工业环境的抗扰度EN61000-6-3:2001 电磁兼容性(EMC)第6部分:通用标准第3节:住宅商业和轻工业环境用辐射标准EN61000-6-4:2001 电磁兼容(EMC)第6部分:通用标准第4节:工业环境用发射标准EN61326-1:1997 测量、控制和实验室用的电设备电磁兼容性第1部分通用要求prEN55021:1999 CISPR 21:脉冲噪声对移动无线电通信的骚扰评定其性能暂降的方法和提高性能的措施prEN55101-2:199信息技术设备的电磁兼容性要求第2部分:静电放电要求EN55014-1:2002 电磁兼容性家用电器、电动工具和类似电器的要求第1部分:发射EN55014-2:2001 电磁兼容性家用电器、电动工具和类似电器的要求第2部分:抗扰性产品系列标准EN50366:2003 家用和类似用途的电器电磁场评定和测量方法EN55022:2002 信息技术设备无线电骚扰特性测量方法与极限EN55024:2002 信息技术设备抗扰度特性测量方法和限制EN55015:2002 电照明和类似设备无线电骚扰特性的测量方法和限值。

电磁兼容试验和测量技术射频电磁场辐射抗扰度试验电磁兼容试验和测量技术是一种对设备、系统或产品在电磁环境中的抗扰度进行评估的方法。

射频电磁场辐射抗扰度试验是其中的一种重要测试,用于评估设备在射频电磁场辐射环境中的抗干扰能力。

本文将从电磁兼容试验和测量技术的理论基础、试验过程和应用前景等方面进行探讨,以期为相关领域的研究和工程应用提供一定的参考。

一、电磁兼容试验和测量技术的理论基础电磁兼容性是指设备、系统或产品在电磁环境中不受外界电磁场辐射或内部电磁干扰的影响,能够正常工作而不对周围其他设备产生干扰。

电磁兼容试验和测量技术主要包括电磁辐射抗干扰性能测试、电磁场辐射测量、电磁场防护效能检测等内容。

这些内容主要是通过一系列的试验手段,来对设备在电磁环境中的性能进行评估,并提出相应的改进措施,确保设备的正常运行和周围环境的安全。

二、射频电磁场辐射抗扰度试验的重要性射频电磁场辐射抗扰度试验是电磁兼容试验和测量技术中的一个重要环节,其重要性主要表现在以下几个方面:首先,射频电磁场辐射是目前电磁环境中最普遍和最强烈的一种电磁辐射,因此对设备在射频电磁场辐射环境中的抗干扰能力进行评估,对保障设备的正常运行有着重要的意义;其次,随着射频技术的不断发展和应用,射频电磁场辐射对设备的影响越来越大,因此射频电磁场辐射抗扰度试验的重要性也越来越凸显;最后,射频电磁场辐射抗扰度试验结果直接影响着设备的市场准入和使用范围,因此对设备进行相关试验是十分必要的。

三、射频电磁场辐射抗扰度试验的试验过程射频电磁场辐射抗扰度试验通常分为试验前准备、试验环境建立、试验参数设置、试验设备布置、试验数据采集和试验结果分析等步骤。

其中,试验前准备要求进行充分的试验方案设计和试验流程规划,以确保试验过程的合理性和有效性;试验环境建立要求在专门的试验室或试验场地内搭建符合要求的射频电磁场辐射环境;试验参数设置要求在试验过程中合理设置射频电磁场辐射的频率、功率、方向和持续时间等参数;试验设备布置要求将待测设备按照实际使用情况布置到射频电磁场辐射环境中;试验数据采集要求利用专业的测试设备对待测设备在射频电磁场辐射环境中的性能参数进行实时采集和记录;试验结果分析要求通过专业的数据处理和分析手段,对试验数据进行深入的分析和评估,得出相应的结论和建议。

电磁兼容试验和测量技术电能质量测量方法电磁兼容试验和测量技术是评估和确保电子设备在电磁环境中正常运行并与其他设备相容的一项关键技术。

而电能质量测量方法是用于评估和监测电力系统中的电能质量参数的方法。

以下是关于这两个方面的简要介绍:1. 电磁兼容试验和测量技术:电磁兼容(Electromagnetic Compatibility,EMC)试验和测量技术主要包括以下方面:-电磁辐射测试:通过测量电子设备辐射出的电磁波,评估其对周围设备的影响。

-电磁感受性测试:测量电子设备对外部电磁干扰的敏感性,以确保其正常运行。

-传导干扰测试:测量电子设备对通过电源线、信号线或地线传导的干扰的抵抗能力。

-静电放电测试:评估设备对静电放电(如人体静电放电)的敏感性。

这些测试和测量方法有助于确定设备是否符合相关的电磁兼容标准,以确保设备在电磁环境中的正常运行,并减少对其他设备造成的干扰。

2. 电能质量测量方法:电能质量(Power Quality)测量方法用于评估和监测电力系统中的电能质量参数,以确保供电系统正常运行,并满足相关的电能质量标准。

常用的电能质量参数包括:-电压稳定性:包括瞬时电压波动、瞬时电压闪变和长时间电压偏差等。

-频率稳定性:评估供电系统的频率稳定程度。

-谐波含量:测量供电系统中的谐波含量,包括电压谐波和电流谐波。

-电能质量事件:记录电力系统中的突发电压变化、短暂中断和持续中断等异常事件。

电能质量测量方法可以通过专业的电能质量仪器和传感器进行实施,获取相关的电能质量参数数据,并进行分析和评估,以确保电力系统的稳定性和可靠性。

需要指出的是,电磁兼容试验和测量技术以及电能质量测量方法都是复杂的领域,需要经验和专业知识的支持。

在进行相关测试和测量时,建议依据相关标准和规范,并寻求专业人士的指导和支持。

电磁兼容试验和测量技术电快速瞬变脉冲群抗扰度试验下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!电快速瞬变脉冲群抗扰度试验技术介绍在电磁兼容(EMC)领域中,电快速瞬变脉冲群抗扰度试验是评估电子设备抗电磁干扰能力的重要手段之一。