哈工大数字逻辑与数字电子试题

- 格式:doc

- 大小:937.00 KB

- 文档页数:11

第6章 逻辑代数基础6.2 授课的几点建议6.2.1 基本逻辑关系的描述基本逻辑关系有“与”、“或”、“非”三种,在本教材中采用文字叙述和常开触点、常闭触点的串、并联等形式来加以描述。

还有一种描述逻辑关系的图,称为文氏图(V enn diagram )。

图6.1(a)圆圈内是A ,圆圈外是A ;图6.1(b)圆圈A 与圆圈B 相交的部分是A 、B 的与逻辑,即AB ;图6.1(c)圆圈A 与圆圈B 所有的部分是A 、B 的或逻辑,即A +B 。

与逻辑AB 也称为A 与B 的交集(intersection );或逻辑A +B 也称为A 和B 的并集(union )。

(a) 单变量的文氏图 (b) 与逻辑的文氏图 (c) 图6.1 文氏图6.2.2 正逻辑和负逻辑的关系正逻辑是将双值逻辑的高电平H 定义为“1”,代表有信号;低电平L 定义为“0”,代表无信号。

负逻辑是将双值逻辑的高电平H 定义为“0”,代表无信号;低电平L 定义为“1”,代表有信号。

正逻辑和负逻辑对信号有无的定义正好相反,就好象“左”、“右”的规定一样,设正逻辑符合现在习惯的规定,而负逻辑正好反过来,把现在是“左”,定义为“右”,把现在是“右”,定义为“左”。

关于正、负逻辑的真值表,以两个变量为例,见表6.1。

表6.1由表6.1可以看出,对正逻辑的约定,表中相当是与逻辑;对负逻辑约定,则相当是或逻辑。

所以正逻辑的“与”相当负逻辑的“或”;正逻辑的“或”相当负逻辑的“与”。

正与和负或只是形式上的不同,不改变问题的实质。

6.2.3 形式定理本书介绍了17个形式定理,分成五类。

需要说明的是,许多书上对这些形式定理有各自的名称,可能是翻译上的缘故,有一些不太贴切,为此,将形式定理分成5种形式表述,更便于记忆。

所以称为形式定理,是因为这些定理在逻辑关系的形式上虽然不同,但实质上是相等的。

形式定理主要用于逻辑式的化简,或者在形式上对逻辑式进行变换,它有以下五种类型:1.变量与常量之间的关系;2.变量自身之间的关系;3.与或型的逻辑关系;4.或与型的逻辑关系;5.求反的逻辑关系——摩根(Morgan )定理。

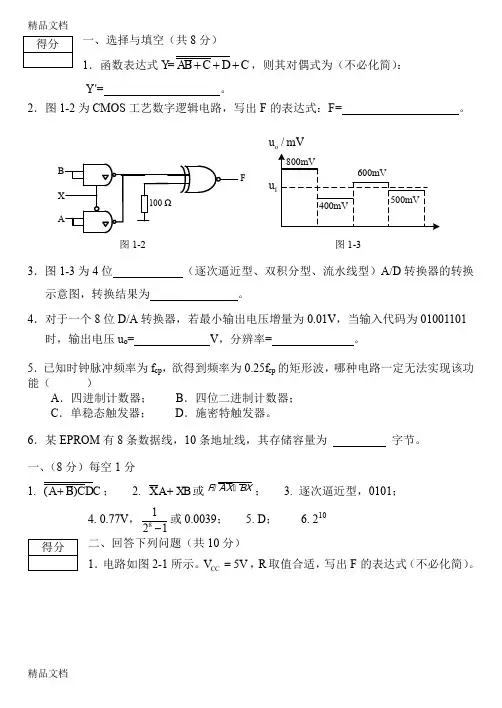

一、选择与填空(共8分)1.函数表达式Y =C D C B A +++,则其对偶式为(不必化简): Y '= 。

2.图1-2为CMOS 工艺数字逻辑电路,写出F 的表达式:F = 。

Fo /mVu u图1-2 图1-33.图1-3为4位 (逐次逼近型、双积分型、流水线型)A/D 转换器的转换示意图,转换结果为 。

4.对于一个8位D/A 转换器,若最小输出电压增量为0.01V ,当输入代码为01001101时,输出电压u o = V ,分辨率= 。

5.已知时钟脉冲频率为f cp ,欲得到频率为0.25f cp 的矩形波,哪种电路一定无法实现该功能( )A .四进制计数器;B .四位二进制计数器;C .单稳态触发器;D .施密特触发器。

6.某EPROM 有8条数据线,10条地址线,其存储容量为 字节。

一、(8分)每空1分1. ()A B CDC +;2. X A XB +或X B A F X ;3. 逐次逼近型,0101;4. 0.77V ,8121-或0.0039; 5. D ; 6. 210二、回答下列问题(共10分)1.电路如图2-1所示。

V 5CC =V ,R 取值合适,写出F 的表达式(不必化简)。

3210图2-1解: 3210F ABS ABS ABS ABS =⋅⋅⋅————————————————3分2.卡诺图化简:(),,,(0,1,2,3,5,8)P A B C D m =∑,约束条件为:0ABD BCD ABC ++= 解:AB CD000111100001111011ΦΦΦ0111001ΦΦ——————————2分P AD BD =+——————————————1分3.在图2-3中,用一片74LS160和一片74LS161,配合必要的逻辑门电路,构成128进制计数器。

要求:使用置数方式,且74LS160为低位芯片,74LS161为高位芯片。

Q D 74LS160RCO Q C Q B Q A ET EP D C B A CR LD CPQ D RCO Q C Q B Q A ET EP D C B A CR LDCP74LS161图2-3解:Q D 74LS160RCO Q C Q B Q A ET EP D C B A CR LDCPQ D RCO Q C Q B Q A ET EP D CB A CR LDCP74LS161111CP——4分三、(10分)一个保险箱有3个按键,当3个键都不按下时,保险箱关闭,不报警;当只有一个按键按下时,保险箱仍关闭,但报警;当有2个按键按下时,保险箱打开,不报警;当三个按键同时按下时,保险箱打开,但要报警。

资料范本本资料为word版本,可以直接编辑和打印,感谢您的下载数字逻辑考题及答案地点:__________________时间:__________________说明:本资料适用于约定双方经过谈判,协商而共同承认,共同遵守的责任与义务,仅供参考,文档可直接下载或修改,不需要的部分可直接删除,使用时请详细阅读内容数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8 =( 10.BC )162、(63.25) 10= ( 111111.01 )23、(FF)16= ( 255 )104、[X]原=1.1101,真值X= -0.1101,[X]补 = 1.0011。

5、[X]反=0.1111,[X]补= 0.1111。

6、-9/16的补码为1.0111,反码为1.0110 。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为1100 01018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_ 、_或__、_非_ 。

10、,其最小项之和形式为_ 。

11、RS触发器的状态方程为__,约束条件为。

12、已知、,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简(5分)答:3、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添 * ,设计出函数。

(5分)5分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解: 2分该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

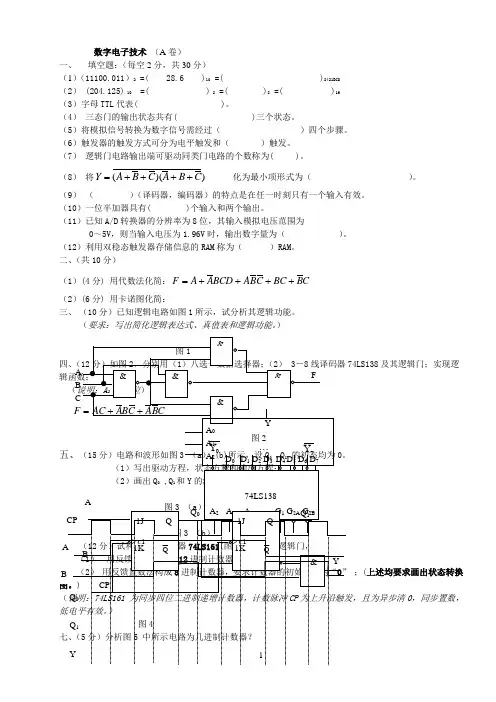

数字电子技术 (A 卷)一、 填空题:(每空2分,共30分) (1)(11100.011)2 =( 28.6 )10 =( )8421BCD (2) (204.125) 10 =( ) 2 =( )8 =( )16 (3)字母TTL 代表( )。

(4) 三态门的输出状态共有( )三个状态。

(5)将模拟信号转换为数字信号需经过( )四个步骤。

(6)触发器的触发方式可分为电平触发和( )触发。

(7) 逻辑门电路输出端可驱动同类门电路的个数称为( )。

(8) 将))((C B A C B A Y ++++= 化为最小项形式为( )。

(9) ( )(译码器,编码器)的特点是在任一时刻只有一个输入有效。

(10)一位半加器具有( )个输入和两个输出。

(11)已知A/D 转换器的分辨率为8位,其输入模拟电压范围为0~5V ,则当输入电压为1.96V 时,输出数字量为( )。

(12)利用双稳态触发器存储信息的RAM 称为( )RAM 。

二、(共10分) (1)(4分) 用代数法化简:C B BC C B A BCD A A F ++++=(2)(6分) 用卡诺图化简: 三、 (10分)已知逻辑电路如图1所示,试分析其逻辑功能。

(要求:写出简化逻辑表达式、真值表和逻辑功能。

)图1四、(12分)如图2,分别用(1)八选一数据选择器;(2) 3-8线译码器74LS138及其逻辑门;实现逻辑函数: (说明:A 2 为高位) C B A C B A AC F ++=五、(15分)电路和波形如图3 (a ),(b)所示,设Q 0 ,Q 1 的初态均为0。

(1)写出驱动方程,状态方程和输出方程;(2)画出Q 0 ,Q 1和Y 的波形(直接画在本试卷上)。

图3 (a )图3 (b )六、(12分)试利用集成计数器74LS161(图4)和必要的逻辑门, (1) 用反馈清零法构成12进制计数器; (2) 用反馈置数法构成8进制计数器,要求计数器的初始状态为“0” ;(上述均要求画出状态转换图。

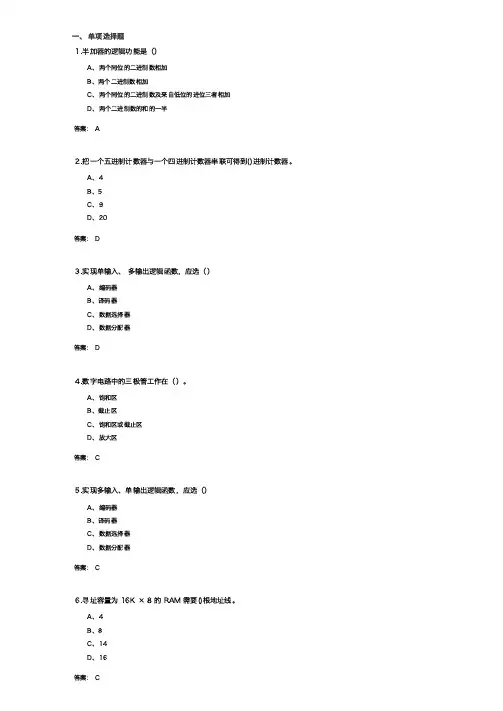

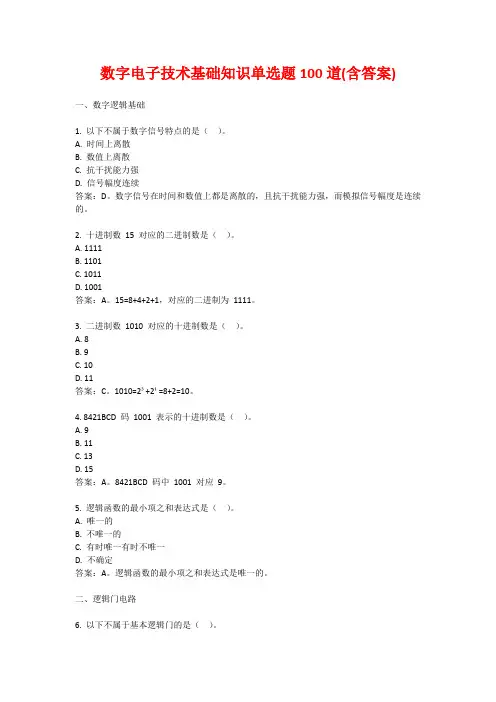

数字电子技术基础知识单选题100道(含答案)一、数字逻辑基础1. 以下不属于数字信号特点的是()。

A. 时间上离散B. 数值上离散C. 抗干扰能力强D. 信号幅度连续答案:D。

数字信号在时间和数值上都是离散的,且抗干扰能力强,而模拟信号幅度是连续的。

2. 十进制数15 对应的二进制数是()。

A. 1111B. 1101C. 1011D. 1001答案:A。

15=8+4+2+1,对应的二进制为1111。

3. 二进制数1010 对应的十进制数是()。

A. 8B. 9C. 10D. 11答案:C。

1010=2³+2¹=8+2=10。

4. 8421BCD 码1001 表示的十进制数是()。

A. 9B. 11C. 13D. 15答案:A。

8421BCD 码中1001 对应9。

5. 逻辑函数的最小项之和表达式是()。

A. 唯一的B. 不唯一的C. 有时唯一有时不唯一D. 不确定答案:A。

逻辑函数的最小项之和表达式是唯一的。

二、逻辑门电路6. 以下不属于基本逻辑门的是()。

A. 与门B. 或门C. 非门D. 与非门答案:D。

与非门是由与门和非门组合而成,不属于基本逻辑门。

7. 三输入端与门的输出为0,当且仅当()。

A. 三个输入全为0B. 三个输入全为1C. 至少一个输入为0D. 至少一个输入为1答案:A。

与门只有当所有输入都为1 时输出才为1,否则输出为0。

8. 三输入端或门的输出为1,当且仅当()。

A. 三个输入全为0B. 三个输入全为1C. 至少一个输入为0D. 至少一个输入为1答案:D。

或门只要有一个输入为1 时输出就为1。

9. 非门的逻辑功能是()。

A. 有0 出1,有1 出0B. 全0 出1,全1 出0C. 相同出0,不同出1D. 不同出0,相同出1答案:A。

非门对输入信号取反。

10. 与非门的逻辑功能是()。

A. 有0 出1,全1 出0B. 全0 出1,有1 出0C. 相同出0,不同出1D. 不同出0,相同出1答案:A。

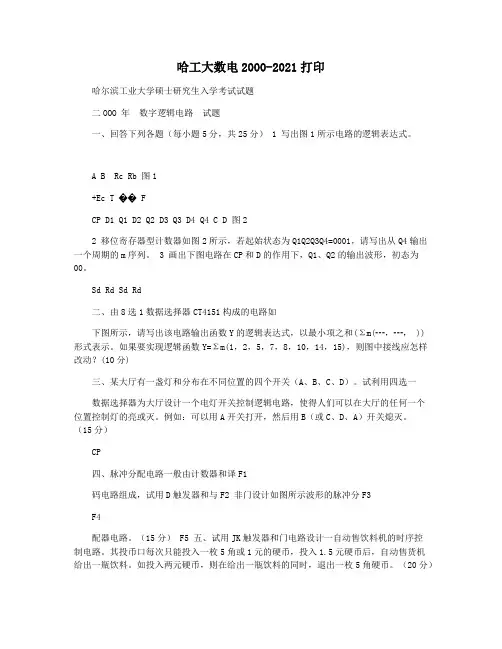

哈工大数电2000-2021打印哈尔滨工业大学硕士研究生入学考试试题二OOO 年数字逻辑电路试题一、回答下列各题(每小题5分,共25分) 1 写出图1所示电路的逻辑表达式。

A B Rc Rb 图1+Ec T �� FCP D1 Q1 D2 Q2 D3 Q3 D4 Q4 C D 图22 移位寄存器型计数器如图2所示,若起始状态为Q1Q2Q3Q4=0001,请写出从Q4输出一个周期的m序列。

3 画出下图电路在CP和D的作用下,Q1、Q2的输出波形,初态为00。

Sd Rd Sd Rd二、由8选1数据选择器CT4151构成的电路如下图所示,请写出该电路输出函数Y的逻辑表达式,以最小项之和(Σm(┅,┅, ))形式表示。

如果要实现逻辑函数Y=Σm(1,2,5,7,8,10,14,15),则图中接线应怎样改动?(10分)三、某大厅有一盏灯和分布在不同位置的四个开关(A、B、C、D)。

试利用四选一数据选择器为大厅设计一个电灯开关控制逻辑电路,使得人们可以在大厅的任何一个位置控制灯的亮或灭。

例如:可以用A开关打开,然后用B(或C、D、A)开关熄灭。

(15分)CP四、脉冲分配电路一般由计数器和译F1码电路组成,试用D触发器和与F2 非门设计如图所示波形的脉冲分F3F4配器电路。

(15分) F5 五、试用JK触发器和门电路设计一自动售饮料机的时序控制电路。

其投币口每次只能投入一枚5角或1元的硬币,投入1.5元硬币后,自动售货机给出一瓶饮料。

如投入两元硬币,则在给出一瓶饮料的同时,退出一枚5角硬币。

(20分)要求:1 状态设置合理,状态图标注清楚; 2 画出逻辑电路图;3 检验自启动。

39哈尔滨工业大学硕士研究生入学考试试题二OO一年数字逻辑电路试题一、解答下列各题(每小题5分,共25分)1. 将D触发器转换成JK触发器,画出逻辑电路图。

2. 试画出111序列检测器的状态图,当连续输入三个1时输出为1,否则输出为0。

数字逻辑设计习题册哈尔滨工业大学(威海)计算机学院体系结构教研室第2章 逻辑代数基础一、填空1.摩根定理表示为:=⋅B A _____;=+B A ______。

2. 函数表达式D C AB Y ++=,则其对偶式为='Y ________。

3.根据反演规则,若C D C B A Y +++=,则=Y ________。

4.函数式CD BC AB F ++=写成最小项之和的形式结果为()∑m ,写成最大项之积的形式结果为)(∏M。

二、 证明1.证明公式()()A BC A B A C +=++成立。

2.证明此公式B A B A A +=+成立。

3.证明此公式)()()()()(C A B A C B C A B A +⋅+=+⋅+⋅+成立。

三、 用代数法化简下列各式1.B A BC A F +=12.D C A ABD CD B A F ++=23.CD D AC ABC C A F +++=34.)()(4C B A C B A C B A F ++⋅++⋅++=5.C DE C BE CD B B A AC F ++++=56.C B A AD C B A CD AB F ++++=67.D BC A BD A BD CD B B A C A F +++++=7四、用卡诺图化简下列各式 1.C B A AB C B F ++=12.C B BC B A F ++=23.C B C B C A C A F +++=34.D C A C B A D C D C A ABD ABC F +++++=45.D B A AC C B A F ++=56.C B A AD C B A D C AB F ++++=67.D BC A BD A BD CD B B A C A F +++++=78.D B D B C A C A F +++=89.D C B A D AC D C B D C A F +++⊕=)(910.∑=mC B A P )7,6,5,2,1,0(),,(111.∑=mD C B A P )14,11,10,9,8,7,6,4,3,2,1,0(),,,(212.∑=mD C B A P )15,14,13,12,10,9,8,6,4,1,0(),,,(3五、 用卡诺图化简下列带有约束条件的逻辑函数 1.∑∑+=d mD C B A P )15,14,13,2,1,0()12,11,9,8,6,3(),,,(12.∑∑+=d mD C B A P )15,14,13,10,9,8()12,11,6,5,4,3,2,0(),,,(23.D C B A D C B A D C A P ++++=3, 约束:0=+AC AB4.CD B A CD B A P +=4, 约束:A B C D 为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1。

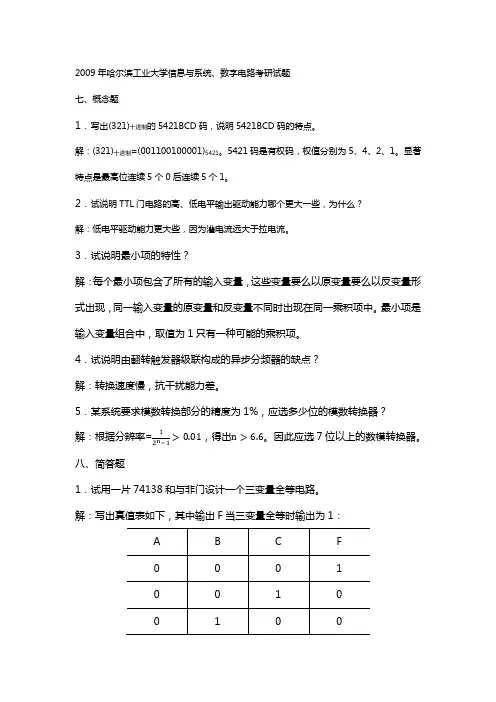

哈尔滨工业大学一九九七年硕士研究生考试试题数字逻辑电路一. (10分)1. 由双极型三极管构成放大器,在正常工作状态下测得管子三个引脚对地的电位为V1=0伏,V2=-6伏,V3=-5.3伏,问此管是什么类型管?管脚1,2,3各是什么极?2. 放大电路如图1所示。

试说明稳定静态工作点Q 的物理过程。

3. 由理想运放构成如图2电路。

其中R 1=R 4,R 2=R 3。

(1) 其增益函数表达式 A(j ω)=Vo/Vi ; (2) 其直流增益 ;(3) 求3dB 上限频率ωH 。

二. 放大电路如图3所示,已知晶体管的参数为:hfe1=hfe2=49, rbb ’=300Ω, hoe=hre=0.静态工作电流:IcQ1=IcQ2=1 mA. 电容对交流可认为短路。

求输入电阻Ri, 输出电阻R0和电压增益Av 。

(10分)R 6图1 图2三.回答下列各题(20分)1. 在下图所示电路中,M1为TTL 与非门,VoH=3.6V, 最大拉电流Ilmax=13mA, 要实现Rb 应 > ( ) Rb 应 < ( )2. 在下图所示电路中M1,M2,M3为TTL OC 门,M4为TTL 与非门,V1,V2为二只20k Ω/V 的电压表,问:S1断开 V1=( ) V2=( )S1合上 A1A2, B1B2, C1C2全为低 V1=( ) V2=( ) S1合上 A1A2为高,B1B2, C1C2为低 V1=( ) V2=( ) 3. 写出下面电路真值表及逻辑表达式。

4. 设计一个序列信号检测器用以及检测0101。

当检测到此码组时输出为1,否则输出为0。

只画出状态转换图。

F1=AB ,F2=AB四.试分别用八选一数据选择器、PLA 设计下列函数。

( 10分) F =)14,13,11,9,7,6,5,4,3(4m五.试用最少数目的与非门将下图(a),(b),(c)所示各电路合并成一个多输出端的组合网络,要求输入变量仅以原变量出现。

一、(12分)填空和选择(每空1分)(1)进制为一千的计数器至少应使用_________个触发器实现。

(2)集电极开路门使用时应注意在输出端接_______________。

(3)32选1数据选择器有____________个选择变量。

(4)函数式Y =+AB BCD ,写出其对偶式Y '=_______________________。

(5)相同供电电源的CMOS 门电路与TTL 门电路相比,_________________门的噪声容限更大;_________________门的静态功耗更低。

(6)模数转换时,要求能分辨ADC 输入满量程0.1%的变化,则至少需要使用____________位的ADC 。

若信号频率为20kHz ,则要求该ADC 采样频率至少为____________kHz 。

(7)由与非门构成的基本RS 触发器,其约束条件是__________________________。

(8)下列器件的信号一定不能和其他输出信号接在一起的是______________。

(a )RAM 的数据信号;(b )ROM 的数据信号; (c )74LS138的输出信号。

(9)下列说法正确的是____________________。

(a )输入悬空时,TTL 门电路的输入端相当于接低电平; (b )输入悬空时,CMOS 门电路的输入端相当于接低电平; (c )输入悬空时,CMOS 门电路的输入端相当于接高电平; (d )实际应用中,门电路的输入端应尽量避免悬空。

(10)用万用表测量一个标准TTL 门电路的输出信号,发现其值为1.5V ,可能的情况有(多选):______________________________________。

(a )输出端处于高阻态; (b )两输出信号短接; (c )输出为脉冲信号; (d )驱动门过载。

一、(1)10;(2)上拉电阻;(3)5;A+)B+C+D B (;(5)CMOS ,CMOS ;(6)10位,40kHz ;(7)R+S=1;(8)c ;(9)d ;(10)bcd 。

数字逻辑设计_哈尔滨工业大学中国大学mooc课后章节答案期末考试题库2023年1.十进制数28,将它表示为余3码是()答案:010110112.利用公式化简法将逻辑函数表达式AC’+ABC+ACD’+CD,化简为最简与或式的结果是()。

答案:A+CD3.利用卡诺图求逻辑函数 F(ABCD)=(A+C')(A+B)(A'+C)(B+D')(B+C')的最简或与式(和之积)为()。

答案:F = B(A'+C)(A+C')4.设计可以实现函数F(A, B, C, D) = Σm(5, 10, 11, 12, 13)的最简三级与非门电路。

下面给出的设计正确的是()。

答案:5.设计一个3变量排队电路,要求:三个输入信号A,B,C单独输入时,分别输出、、;当多个输入信号同时输入时,任一时刻只能输出优先级最高的一个信号,优先级顺序依次是A,B,C。

下面电路设计过程中有错误的是()。

答案:设计完成的逻辑图为:6.逻辑函数F = (A + C)(A′+ D′)(B′+ C′+ D),在输入变量为特定取值时,共有()处相邻的卡诺圈会产生险象。

答案:共有4处,如下图7.如图所示,当AB的值为()时,当输入变量C发生变化时,可能产生错误的“0”。

答案:118.下图是由8选1数据选择器构成的电路,当取值为01时,输出端Y的表达式为()。

答案:Y = A⊕B9.将下图中的JK触发器转换为D触发器,则红色方框中应添加的逻辑门是()。

答案:非门10.电路如下图所示,设触发器的初态为“0”,边沿触发。

给定触发器的输入波形,下面给出的结论正确的是()。

答案:输出端波形:11.利用隐含表找出下面表中所有的等价状态()。

答案:a ≡ c,b ≡ d, b ≡ e, d ≡ e12.根据给出的状态表,隐含表填写正确的是()。

答案:13.某同步时序电路的状态图如下图所示,要求使用T触发器设计实现,假设电路的初始状态为Q3Q2Q1=100。

2003春季学期数字电子期末试题(远程)

教学站 班级 姓名

一、 按要求回答下列问题: 1. 用代数法化简

(1) )()(1C B A C B A C B A P ++⋅++⋅++=

(2) P 2=AB +C B C A +

2. 对逻辑运算判断下述说法是否正确,正确者在其后( )内打对号,反之打×。

(1) 若X+Y=X+Z ,则Y=Z ;( ) (2) 若XY=XZ ,则Y=Z ;( )

(3) 若X ⊕Y=X ⊕Z ,则Y=Z ;( )

3. 函数式F=C B A ⊕⊕写成最小项之和的形式,结果应为m ∑( )。

4. 用卡诺图化简:

D C A C B A D C D C A ABD ABC F +++++=

5填空:

(1) 由TTL 门组成的电路如图1所示,已知它们的输入短路电流为I is =1.6mA ,高电平输入漏电流I iH =40μA 。

试问:当A=B=1时,G 1的(拉,灌) 电流为 mA ;A=0时,G 1的(拉,灌) 电流为 mA 。

3

G A

B

图1

(2) TTL 门电路输入端悬空时,应视为 ;(高电平,低电平,不定)此时如用万用表测量其电压,读数约为 (3.5V ,0V ,1.4V )。

(3) 集电极开路门(OC 门)在使用时须在 之间接一电阻(输出与地,输出与输入,输出与电源)。

(4)8位D/A 转换器当输入数字量只有最高位为高电平时输出电压为5V ,若只有最低位为高电平,则输出电压为 。

(5)就逐次逼近型和双积分型两种A/D 转换器而言, 抗干扰能力强; 转换速度快。

(6)半导体存储器按功能分有 和 两种。

(7)某EPROM 有8数据线,13位地址线,则其存储容量为 。

6. 由TTL 门组成的电路如图2所示,G 1和G 2为三态门,分别写出R=100Ω和R =100k Ω时输出Y 的表达式。

X

G 1

图2

二、图3是由八选一数据选择器构成的电路,试写出当G 1G 0为各种不同的取值时的输出Y 的表达式。

0 1 2 3 4 5 6 74

21

G 0

7EN

MUX

Q G1G0A

B

Y

"1"

图3

二、设计一个一灯两处控制的逻辑电路,要求当改变开关A 或B 的状态时,均可改变灯

L 的状态。

列出真值表,写出逻辑表达式,用尽量少的与非门实现该逻辑电路。

四、图4 (a)是由与非门构成的基本R-S 触发器,试画出在图(b)所示输入信号的作用下的

输出波形。

&

&

R d

S d

Q

Q

图4 (a) (b)

五、试写出图5(a)中各触发器输出的次态函数( Q n+1 ),并画出在图( b )所示CP 波形作用下的输出波形。

(各触发器的初态均为“0”)

D Q

Q

CP

D

Q

Q CP

Q Q

CP

J K

Q

Q CP

J

K

Q1

Q2

Q3Q4

图5(a)

"1""1"

(b)

六、图6(a )是由555定时器构成的单稳态触发电路。

1、计算暂稳态维持时间t w

2、画出在图(b )所示输入u i 作用下的u C 和u O 的波形。

u (ms)

(ms)(ms)

u +5V

o μF

01.

图6(a ) (b )

七、分析图7所示计数器电路,写出驱动方程,列出状态转换表,画出完整的状态转换

图。

J K

Q

Q J K

Q Q

J

K Q

Q

CP

FF1

FF2

FF3

图7

八、分析图8所示由异步清零、同步预置的2/16进制同步加法计数器74LS161构成的电路

1、画出完整的状态转换图;

2、画出Qd 相对于CP 的波形,说明是几分频,Qd 的占空比是多少。

CP

"1"

"1"

C r

D C

B

A L D

Q Q b Q c d Q a

EP ET 74LS161"1"

图8

2004春季学期数字电子期末试题答案

三、 按要求回答下列问题:(32分) 2. 用代数法化简 (1)

1()()P A B C A B C A B C A BC

=++⋅++⋅+++=

(2) P 2=AB +C B C A +=AB+C

2. 对逻辑运算判断下述说法是否正确,正确者在其后( )内打对号,反之打×。

(1) 若X+Y=X+Z ,则Y=Z ;(×) (2) 若XY=XZ ,则Y=Z ;(×)

(3) 若X ⊕Y=X ⊕Z ,则Y=Z ;(√ )

3. 函数式F=C B A ⊕⊕写成最小项之和的形式,结果应为m ∑( 1,2,4,7 )。

4. 用卡诺图化简:

D C A C B A D C D C A ABD ABC F +++++==A D +

5填空:

(1) 由TTL 门组成的电路如图1所示,已知它们的输入短路电流为I is =1.6mA ,高电平输入漏电流I iH =40μA 。

试问:当A=B=1时,G 1的(拉,灌)灌电流为 3.2 mA ;A=0时,G 1的(拉,灌) 拉 电流为0.16 mA 。

3

G A

B

图1

(2) TTL 门电路输入端悬空时,应视为 高电平 ;(高电平,低电平,不定)此时如用万用表测量其电压,读数约为 1.4V (3.5V ,0V ,1.4V )。

(3) 集电极开路门(OC 门)在使用时须在输出与电源 之间接一电阻(输出与地,输出与输入,输出与电源)。

(4)8位D/A 转换器当输入数字量只有最高位为高电平时输出电压为5V ,若只有最低位为高电平,则输出电压为 5/128 近似为40mV 左右 。

(5)就逐次逼近型和双积分型两种A/D 转换器而言, 双积分型 抗干扰能力强; 逐次逼近型 转换速度快。

(6)半导体存储器按功能分有 ROM 和 RAM 两种。

(7)某EPROM 有8数据线,13位地址线,则其存储容量为 213×8 或 64k 。

6. 由TTL 门组成的电路如图2所示,G 1和G 2为三态门,分别写出R=100Ω和R =100k Ω时输出Y 的表达式。

X

G 1

图2

(100)0(100k )

F AX BX R F R =+=Ω==Ω

二、图3是由八选一数据选择器构成的电路,试写出当G 1G 0为各种不同的取值时的输出Y 的表达式。

(10分)

0 1 2 3 4 5 6 74

21

G 0

7EN

MUX

Q G1

G0A

B

Y

"1"

图3

三、一灯两处控制的逻辑电路,要求当改变开关A 或B 的状态时,均可改变灯L 的状态。

列出真值表,写出逻辑表达式,用尽量少的与非门实现该逻辑电路。

(12分)

Y AB AB AB AB

=+=⋅

Y ABB AAB =⋅

L

B

A

四、图4 (a)是由与非门构成的基本R-S 触发器,试画出在图(b)所示输入信号的作用下的输出波形。

(8分)

R d S d Q Q

不定

五、试写出图5(a)中各触发器输出的次态函数( Q n+1 ),并画出在图( b )所示CP 波形作用下的输出波形。

(各触发器的初态均为“0”)(8分)

六、图6(a )是由555定时器构成的单稳态触发电路。

1、计算暂稳态维持时间t w

2、画出在图(b )所示输入u i 作用下的u C 和u O 的波形。

(8分)

七、(12分)分析图7所示计数器电路,写出驱动方程,列出状态转换表,画出完整的

状态转换

J K

Q

Q J K

Q Q

J

K Q

Q

CP

FF1

FF2

FF3

图7

Q1CP Q2Q3Q4

u o

u c

t t t

u i (ms)

(ms)(ms)

5 10 25 30 45 50

3.33V

暂稳态维持时间t w

=1.1RC=10ms

第11页(共11页)

分析过程略,状态转换图见下图(Q 1为高位),其功能为跳全”0”的三位扭环型计数器。

61

43

2

5

7

八、(10分)分析图8所示由异步清零、同步预置的2/16进制同步加法计数器74LS161构成的电路

1、画出完整的状态转换图;

2、画出Qd 相对于CP 的波形,说明是几分频,Qd 的占空比是多少。

CP

"1"

"1"

C r D

C

B

A L D

Q Q b Q c d Q a EP

ET

74LS161"1"

067815

14

1

5432

91312

1110

六分频,50%

图8。