组合逻辑电路的设计方法案例分析

- 格式:docx

- 大小:22.22 KB

- 文档页数:1

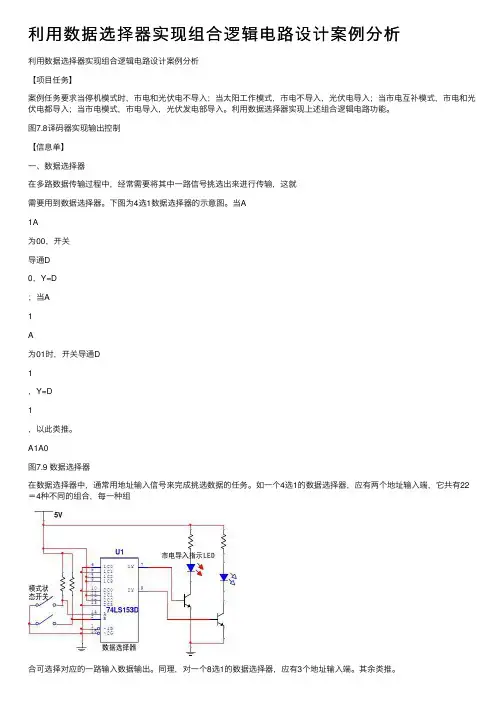

利⽤数据选择器实现组合逻辑电路设计案例分析利⽤数据选择器实现组合逻辑电路设计案例分析【项⽬任务】案例任务要求当停机模式时,市电和光伏电不导⼊;当太阳⼯作模式,市电不导⼊,光伏电导⼊;当市电互补模式,市电和光伏电都导⼊;当市电模式,市电导⼊,光伏发电部导⼊。

利⽤数据选择器实现上述组合逻辑电路功能。

图7.8译码器实现输出控制【信息单】⼀、数据选择器在多路数据传输过程中,经常需要将其中⼀路信号挑选出来进⾏传输,这就需要⽤到数据选择器。

下图为4选1数据选择器的⽰意图。

当A1A为00,开关导通D0,Y=D;当A1A为01时,开关导通D1,Y=D1,以此类推。

A1A0图7.9 数据选择器在数据选择器中,通常⽤地址输⼊信号来完成挑选数据的任务。

如⼀个4选1的数据选择器,应有两个地址输⼊端,它共有22=4种不同的组合,每⼀种组合可选择对应的⼀路输⼊数据输出。

同理,对⼀个8选1的数据选择器,应有3个地址输⼊端。

其余类推。

⼀、4选1数据选择器74LS1531、逻辑电路:D3、D2、D1、D0为数据输⼊端,A1、A0为地址信号输⼊端,Y 为数据输出端,ST 为使能端,⼜称选通端,输⼊低电平有效。

下图7.10为74LS153 管脚排列⽰意图。

该芯⽚中存在两个4选1数据选择器。

2Y92C0102C1112C2122C313A 14B 2~1G 11Y71C061C151C241C33~2G15图7.10 74LS153 管脚排列表7.5为74LS153的功能表。

当使能端G 有效时,输出等于地址信号A 、B 所选择的数据信号。

可得输出函数表达式为:3322110C m C m C m C m Y o +++=。

对于⼀个n 选1的数据选择器,其输出函数为:n n o C m C m Y ++=...0 ⼆、⽤数据选择器实现组合逻辑函数实现原理:数据选择器是⼀个逻辑函数的最⼩项输出:∑-===++=1200...n i ii n n o c m C m C m Y ⽽任何⼀个n 位变量的逻辑函数都可变换为最⼩项之和的标准式。

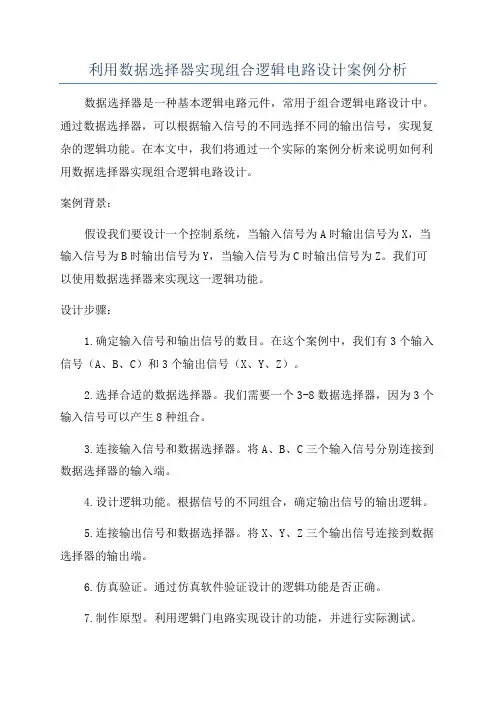

利用数据选择器实现组合逻辑电路设计案例分析数据选择器是一种基本逻辑电路元件,常用于组合逻辑电路设计中。

通过数据选择器,可以根据输入信号的不同选择不同的输出信号,实现复杂的逻辑功能。

在本文中,我们将通过一个实际的案例分析来说明如何利用数据选择器实现组合逻辑电路设计。

案例背景:假设我们要设计一个控制系统,当输入信号为A时输出信号为X,当输入信号为B时输出信号为Y,当输入信号为C时输出信号为Z。

我们可以使用数据选择器来实现这一逻辑功能。

设计步骤:1.确定输入信号和输出信号的数目。

在这个案例中,我们有3个输入信号(A、B、C)和3个输出信号(X、Y、Z)。

2.选择合适的数据选择器。

我们需要一个3-8数据选择器,因为3个输入信号可以产生8种组合。

3.连接输入信号和数据选择器。

将A、B、C三个输入信号分别连接到数据选择器的输入端。

4.设计逻辑功能。

根据信号的不同组合,确定输出信号的输出逻辑。

5.连接输出信号和数据选择器。

将X、Y、Z三个输出信号连接到数据选择器的输出端。

6.仿真验证。

通过仿真软件验证设计的逻辑功能是否正确。

7.制作原型。

利用逻辑门电路实现设计的功能,并进行实际测试。

在这个案例中,我们可以利用3-8数据选择器来实现逻辑功能。

数据选择器有三个输入引脚和八个输出引脚,根据输入信号的不同选择不同的输出信号。

通过合理的连接和设计,我们可以准确地实现控制系统的逻辑功能。

数据选择器在逻辑电路设计中有着广泛的应用,可以用来设计各种复杂的组合逻辑电路。

通过合理的选型和设计,我们可以实现各种复杂的控制功能,提高系统的性能和稳定性。

在实际应用中,数据选择器是一个非常重要的逻辑元件,掌握好其原理和设计方法对于电路设计师来说至关重要。

总的来说,数据选择器是一种非常重要的逻辑电路元件,在组合逻辑电路设计中有着广泛的应用。

通过合理的选型和设计,我们可以实现各种复杂的控制功能,提高系统的性能和稳定性。

希望通过本文的案例分析,读者对数据选择器的应用有更深入的理解,并能够在实际项目中灵活运用。

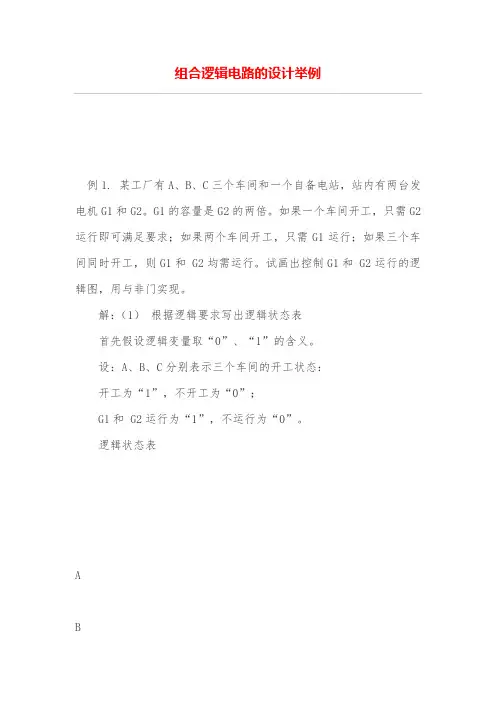

组合逻辑电路的设计举例例1. 某工厂有A、B、C三个车间和一个自备电站,站内有两台发电机G1和G2。

G1的容量是G2的两倍。

如果一个车间开工,只需G2运行即可满足要求;如果两个车间开工,只需G1运行;如果三个车间同时开工,则G1和 G2均需运行。

试画出控制G1和 G2运行的逻辑图,用与非门实现。

解:(1)根据逻辑要求写出逻辑状态表首先假设逻辑变量取“0”、“1”的含义。

设:A、B、C分别表示三个车间的开工状态:开工为“1”,不开工为“0”;G1和 G2运行为“1”,不运行为“0”。

逻辑状态表ABC G1 G2 0 0 0 00 0 0 1 0 11 0 0 1 0 11 0 1 0 0 01 0 1 1 0 11 0 1 0 1 1 111(2)由逻辑状态表写出逻辑式根据状态表写表达式的一般步骤:①在状态表上找出输出为1的行;②将这一行中所有自变量写成乘积项,当变量的取值为“1”时写为原变量,当变量的取值为“0”时写为原变量的反变量;③将所有乘积项逻辑加,便得到逻辑函数表达式。

这里的乘积项又叫最小项,在最小项里,每个变量都以它的原变量或反变量的形式在乘积项中出现,且仅出现一次。

(3)化简逻辑式(4)用“与非”门构成逻辑电路(5)画出逻辑电路图例2:设计三人表决电路(A、B、C)。

每人一个按键,如果同意则按下,不同意则不按。

结果用指示灯表示,多数同意时指示灯亮,否则不亮。

要求用与非门实现。

解:(1)根据逻辑要求列状态表首先确定逻辑变量取0、1的含义:A、B、C分别表示三人按键的状态,键按下时为“1”,不按时为“0”。

F表示指示灯的亮灭,灯亮为“1”,不亮为“0”。

逻辑要求:两个人(包括两个人)以上同意,指示灯亮。

ABCF 0 0 0 0 0 01 0 0 1 0 01 1 1 1 0 01 0 1 1 1 111111(2)由状态表写出逻辑式并化简、转换(3)实现电路。

实验一组合逻辑电路的设计组合逻辑电路是一种电子电路,由逻辑门组成,用于执行特定的逻辑功能。

在本实验中,我们将设计一个基本的组合逻辑电路以及一些常见的组合逻辑电路,包括加法器、减法器、比较器等。

首先,我们将设计一个基本的组合逻辑电路,该电路由两个输入和一个输出组成。

输入可以是0或1,输出将依据输入的值进行逻辑运算得出。

在这个基本电路中,我们将使用两个逻辑门:与门和或门。

与门的真值表如下:输入1输入2输出000010100111与门的布尔表达式是:输出=输入1AND输入2或门的真值表如下:输入1输入2输出000011101111或门的布尔表达式是:输出=输入1OR输入2基于以上真值表和布尔表达式,我们可以通过逻辑门的连接来设计一个基本的组合逻辑电路。

具体设计步骤如下:1.首先,将两个输入引线分别连接到与门和或门的输入端。

这将确保输入的值能够传递到逻辑门中。

2.将与门和或门的输出引线连接到一个输出引线上,以便能够输出最终的逻辑结果。

3.最后,将逻辑门的电源连接到电路的电源上,以确保逻辑门能正常工作。

通过以上步骤,我们就完成了一个基本的组合逻辑电路的设计。

这个电路可以根据输入产生不同的输出,实现不同的逻辑功能。

除了基本的组合逻辑电路,我们还可以设计一些常见的组合逻辑电路,如加法器、减法器和比较器。

加法器是用来执行数字加法的组合逻辑电路。

在一个二进制加法器中,输入是两个二进制数和一个进位位,输出是一个和输出和一个进位位。

加法器的设计可以通过级联多个全加器来实现。

减法器是用来执行数字减法的组合逻辑电路。

在一个二进制减法器中,输入是两个二进制数和一个借位位,输出是一个差输出和一个借位位。

减法器的设计可以通过级联多个全减法器来实现。

比较器是用来比较两个数字的大小的组合逻辑电路。

比较器的输出取决于输入的大小关系。

如果两个输入相等,则输出为0。

如果第一个输入大于第二个输入,则输出为1、如果第一个输入小于第二个输入,则输出为-1、比较器的设计可以通过使用逻辑门和触发器来实现。

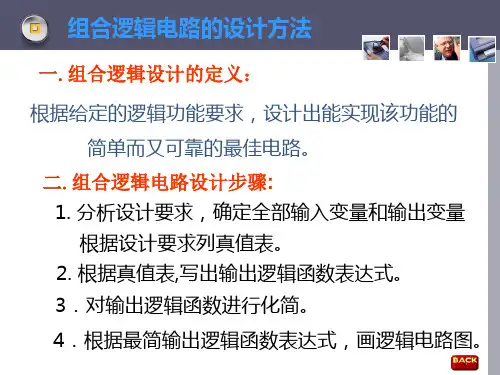

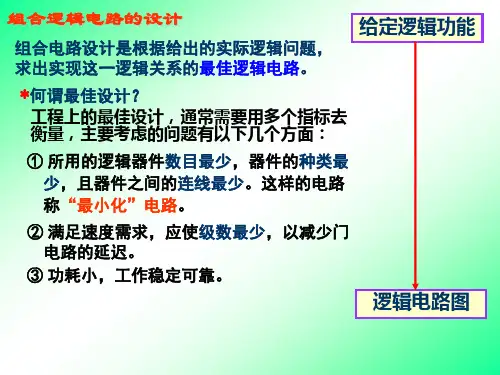

组合逻辑电路的设计

、组合逻辑电路的设计步骤:

组合逻辑电路的设计过程正好与分析过程相反,它是根据给定的逻辑功能

要求,找出用最少逻辑门实现该逻辑功能的电路。

资料个人收集整理,勿做商业用途

(1)分析给定的实际逻辑问题,根据设计的逻辑要求列出真值表。

(2)根据真值表写出组合电路的逻辑函数表达式并化简。

(3)根据集成芯片的类型变换逻辑函数表达式并画出逻辑电路图。

例:设计一个楼上、楼下开关的控制逻辑电路来控制楼梯上的路灯,使之在上楼前,用楼下开关打开电灯,上楼后,用楼上开关关灭电灯;或者在下楼前,

用楼上开关打开电灯,下楼后,用楼下开关关灭电灯。

资料个人收集整理,勿做商业用途

解:(1)分析给定的实际逻辑问题,根据设计的逻辑要求列出真值表。

设楼上开关为A,楼下开关为B,灯泡为丫。

并设A、B闭合时为1,断开时为0;灯亮时丫为1,灯灭时丫为0。

根据逻辑要求列出真值表。

资料个人收集整理,勿

做商业用途

(2)根据真值表写出逻辑函数的表达式并化简。

由可直接写出表达式:

Y = +川豆即Y= B

此式已为最简。

(3)画出逻辑电路图如图4所示。

若用与非门实现。

贝U先将函数变换为:

逻辑电路图如图下所示。

项目二、设计三人表决器

项目三、血型匹配系统的设计

项目四、交通信号灯监测电路

项目五、二楼楼梯开关控制电路 项目六、三位数据奇偶校验器

S

Y

项目设计方案:。

74LS153译码器组合逻辑电路设计案例分析74LS153是一个8-输入、4-输出译码器,常用于数字电路中的多路选择器和标识器等应用。

在设计任何电路之前,首先需要明确设计的功能和要求,并根据要求选择合适的元器件和逻辑门。

在设计74LS153译码器的组合逻辑电路时,需要考虑译码器的输入信号和输出信号之间的关系,以及适当的逻辑门的选择和连接。

设计目标:设计一个将8个输入信号(A0-A2,B0-B2)经过74LS153译码器进行解码,并输出4个选择信号(Y0-Y3)的组合逻辑电路。

设计要求:1.按照以下真值表设置输入信号和输出信号之间的关系:-A0-A2作为译码器的A输入端口-B0-B2作为译码器的B输入端口-输出信号Y0-Y3为译码器的输出端口2.根据译码器的逻辑功能表,确定输入信号和输出信号的关系,设计逻辑门的连接方式,并绘制电路图。

设计步骤:1.根据74LS153译码器的真值表确定输入和输出关系:-A0-A2:000-111,共8个输入信号-B0-B2:000-111,共8个输入信号-输出信号Y0-Y3:0000-1111,共16个输出信号2.根据真值表确定译码器的逻辑功能表,分别设计A和B输入信号的连接方式:-A输入信号的逻辑功能表表示为F(A)=Y0(A)+Y1(A)+Y2(A)+Y3(A)-B输入信号的逻辑功能表表示为F(B)=Y0(B)+Y1(B)+Y2(B)+Y3(B)3.根据逻辑功能表确定逻辑门的连接方式:-对于A输入信号,根据真值表可确定Y0(A)=1,Y1(A)=1,Y2(A)=1,Y3(A)=1,因此需要使用四个2输入的OR门连接-对于B输入信号,根据真值表可确定Y0(B)=1,Y1(B)=1,Y2(B)=1,Y3(B)=1,因此需要再使用四个2输入的OR门连接4.将A和B输入信号的连接方式和逻辑门的连接方式结合起来,绘制组合逻辑电路的电路图。

设计结果:最终的组合逻辑电路图如下所示:```A0-------\A1-------,----OR----Y0A2-------/B0-------\B1-------,----OR----Y1B2-------/A0-------\A1-------,----OR----Y2A2-------/B0-------\B1-------,----OR----Y3B2-------/```通过以上设计步骤,我们成功地设计了一个将8个输入信号通过74LS153译码器解码,并输出4个选择信号的组合逻辑电路。

组合逻辑电路分析方法案例分析数字电路根据逻辑功能的不同可分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两大类。

任一时刻电路的输出仅仅取决于该时刻的输入信号,而与电路原来的状态无关,这种电路称为组合逻辑电路。

组合逻辑电路是由门电路组合而成的,可以有一个或多个输入端,也可以有一个或多个输出端。

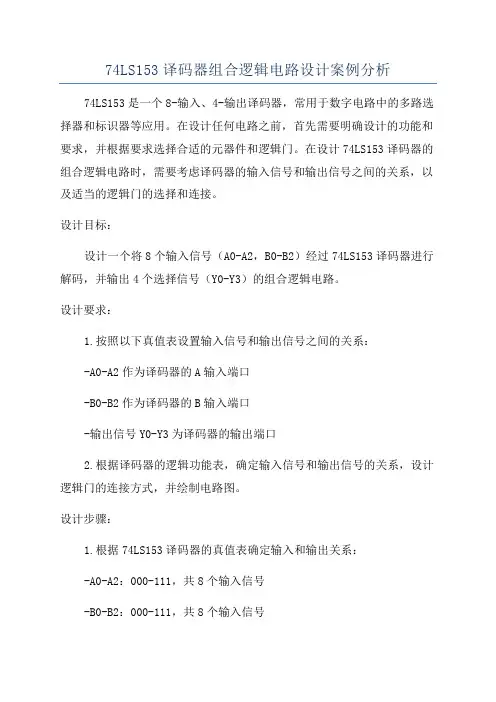

【项目任务】利用集成与非门电路74LS00设计三输入表决电路,当输入端有两个或者两个以上高电平时,输出端二极管亮,表明表决通过。

按照其真值表可到该电路的标准与或表达式为:ABC BC A C B A C AB F +++=,函数转换后为:ABC BC A C B A C AB F ⋅⋅⋅=,可得测试电路如下图6.45所示。

X12.5 V图6.45 测试电路【信息单】一、组合逻辑电路分析方法所谓组合逻辑电路的分析,就是根据给定的逻辑电路图,确定其逻辑功能。

分析组合逻辑电路的目的是确定已知电路的逻辑功能或者检查电路设计是否合理。

组合逻辑电路通常采用的分析步骤如下。

(1)根据给定逻辑电路图,写出逻辑函数表达式。

(2)根据逻辑表达式列真值表。

(3)观察真值表中输出与输入的关系,描述电路逻辑功能。

例:试分析图6.46所示组合逻辑电路的功能。

解:(1) 写出逻辑函数表达式。

C AB Y =1,C B A Y =2,BC A Y =2 所以:ABC BC A C B A C AB ABC BC A C B A C AB F +++=⋅⋅⋅=6.5。

(3) 观察真值表中输出与输入的关系,描述电路逻辑功能。

从真值表可见,该电路实现的是3路判决电路。

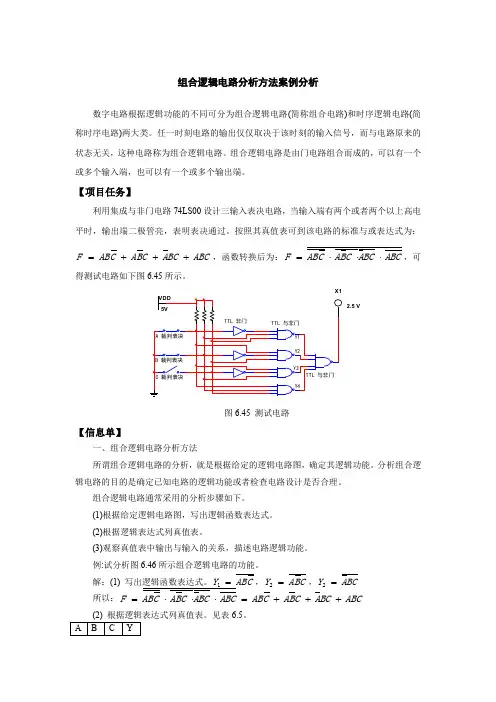

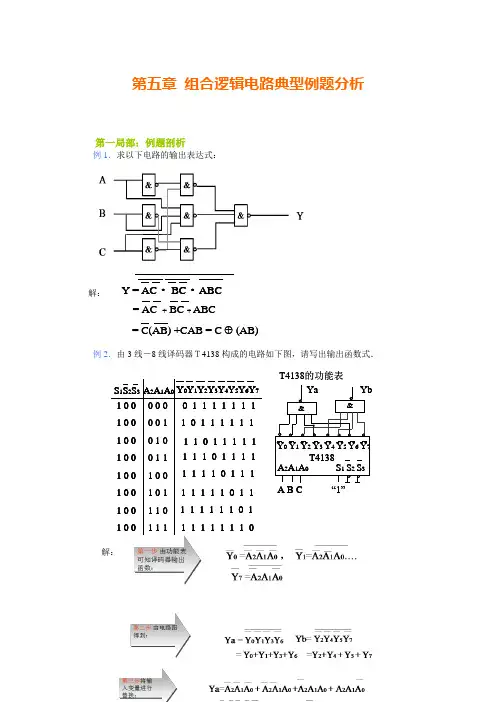

第五章 组合逻辑电路典型例题分析第一局部:例题剖析例1.求以下电路的输出表达式:解:例2.由3线-8线译码器T4138构成的电路如下图,请写出输出函数式.解:Y = AC BC ABC = AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表&&Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7“1”T4138A B CA 2A 1A 0YaYbS 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0例3.分析如图电路,写出输出函数Z的表达式。

CC4512为八选一数据选择器。

解:例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。

〔表中未出现的输入变量状态组合可作为约束项〕CC4512的功能表A ⨯DIS INH 2A 1A 0Y1 ⨯0 10 00 00 00 00 00 00 00 0⨯⨯⨯⨯⨯0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1高阻态 0D 0D 1D 2D 3D 4D 5D 6D 7ZCC4512A 0A 1A 2D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7DIS INHD1DA B C D Y 0 0 0 0 10 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 ××××10 0 1 ××AB第一步画卡诺图第三步画逻辑电路图例5.写出下面组合电路的输出表达式,分析逻辑功能。

实验1组合逻辑电路的设计与测试

一、实验目的

掌握组合逻辑电路的设计与测试方法

二、实验原理

1、组合电路的一般步骤如图

2、组合逻辑电路设计举例

用“与非”门设计一个表决电路。

当四个输入端中有三个或四个为“1”时,输出端才为“1”。

D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 1 1 1 1 0 0 0 0 1 1 1 1

A 0 0

B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Z 0 0 0 0 0 0 0 1 0 0 0 1 0 1 1 1

DA

00 01 11 10

BC

00

01 1

11 1 1 1

10 1

表5-5-2

由卡诺图得出逻辑表达式,并演化成“与非”的形式

Z=ABC+BCD+ACD+ABD

=ABC ACD BCD ABC ⋅⋅⋅

图5-5-1

表决逻辑电路

按图5-5-2接线,输入端A 、B 、C 、D 接至逻辑开关输出插口,输出端Z 接逻辑电平显示输入插口,按真值表(自拟)要求,逐次改变输入变量,测量相应的输出值,验证逻辑功能,与表5-5-1进行比较,验证所设计的逻辑电路是否符合要求。

三、实验设备与器件

1、 +5V 直流电源

2、 逻辑电平开关

3、 逻辑电平显示器

4、 直流数字电压表

5、 74LS00 74LS20 cc4070

四、实验内容

1用与非门设计半加器

2用与非和异或门设计半加器

3用与非和异或设计全加器。

组合逻辑电路的设计方法案例分析

与分析过程相反,组合逻辑电路的设计是根据给定的实际逻辑问题,求出实现其逻辑功能的最简逻辑电路。

组合逻辑电路的设计步骤如下。

(1)分析设计要求,设置输入变量和输出变量并逻辑赋值。

(2)列真值表,根据上述分析和赋值情况,将输入变量的所有取值组合和与之相对应的输出函数值列表,即得真值表。

(3)写出逻辑表达式并化简。

(4)画逻辑电路图。

例:设计一个3路判决电路,A 裁判具有否决定权。

解:(1)分析设计要求,设输入、输出变量并逻辑赋值。

输入变量:A 、B 、C 分别为3个裁判。

输出变量:Y 。

逻辑赋值:用1表示肯定,用0表示否定。

(2)列真值表,见表6.6。

(3) 由真值表写出逻辑函数表达式并化简。

C B A C AB ABC Y ++= AC AB AC AB ⋅=+= (4) 画逻辑电路图。

用与非门电路实现,如图6.46所示。

图6.46逻辑电路图

利用分立门电路搭接了具有一定逻辑功能的组合逻辑电路,需要的组合逻辑电路固然能通过刚才的方法利用门电路进行搭接,但缺点是该种电路所需的硬件多、连线多、电路复杂,从而造成功耗、重量及体积增大,同时特性较差,所以可利用现成的集成数字组合逻辑电路来搭接相应的功能电路,接下来介绍常见的集成组合逻辑电路。