集成电路第九章 测试

- 格式:ppt

- 大小:1.99 MB

- 文档页数:58

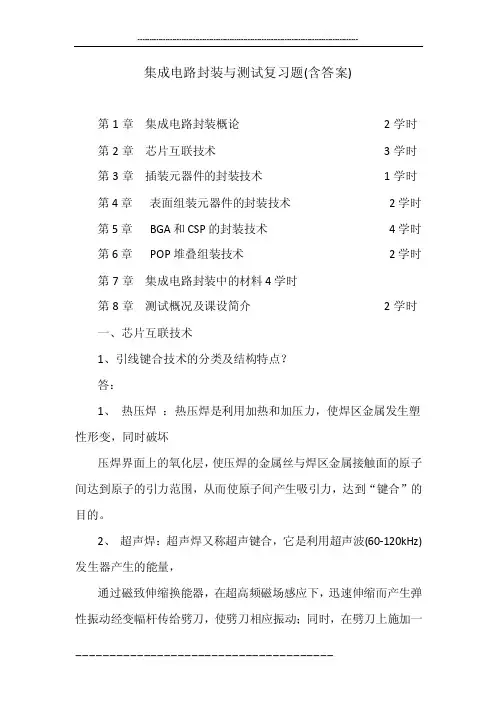

集成电路封装与测试复习题(含答案)第1章集成电路封装概论2学时第2章芯片互联技术3学时第3章插装元器件的封装技术1学时第4章表面组装元器件的封装技术2学时第5章BGA和CSP的封装技术4学时第6章POP堆叠组装技术2学时第7章集成电路封装中的材料4学时第8章测试概况及课设简介2学时一、芯片互联技术1、引线键合技术的分类及结构特点?答:1、热压焊:热压焊是利用加热和加压力,使焊区金属发生塑性形变,同时破坏压焊界面上的氧化层,使压焊的金属丝与焊区金属接触面的原子间达到原子的引力范围,从而使原子间产生吸引力,达到“键合”的目的。

2、超声焊:超声焊又称超声键合,它是利用超声波(60-120kHz)发生器产生的能量,通过磁致伸缩换能器,在超高频磁场感应下,迅速伸缩而产生弹性振动经变幅杆传给劈刀,使劈刀相应振动;同时,在劈刀上施加一定的压力。

于是,劈刀就在这两种力的共同作用下,带动Al丝在被焊区的金属化层(如Al膜)表面迅速摩擦,使Al丝和Al膜表面产生塑性形变。

这种形变也破坏了Al层界面的氧化层,使两个纯净的金属面紧密接触,达到原子间的“键合”,从而形成牢固的焊接。

3、金丝球焊:球焊在引线键合中是最具有代表性的焊接技术。

这是由于它操作方便、灵活,而且焊点牢固,压点面积大,又无方向性。

现代的金丝球焊机往往还带有超声功能,从而又具有超声焊的优点,有的也叫做热(压)(超)声焊。

可实现微机控制下的高速自动化焊接。

因此,这种球焊广泛地运用于各类IC和中、小功率晶体管的焊接。

2、载带自动焊的分类及结构特点?答:TAB按其结构和形状可分为Cu箔单层带:Cu的厚度为35-70um,Cu-PI双层带Cu-粘接剂-PI三层带Cu-PI-Cu双金属3、载带自动焊的关键技术有哪些?答:TAB的关键技术主要包括三个部分:一是芯片凸点的制作技术;二是TAB载带的制作技术;三是载带引线与芯片凸点的内引线焊接和载带外引线的焊接术。

制作芯片凸点除作为TAB内引线焊接外,还可以单独进行倒装焊(FCB)4.倒装焊芯片凸点的分类、结构特点及制作方法?答:蒸镀焊料凸点:蒸镀焊料凸点有两种方法,一种是C4 技术,整体形成焊料凸点;电镀焊料凸点:电镀焊料是一个成熟的工艺。

第9章集成电路版图设计实例【习题答案】1.版图设计关于数字地和模拟地的考虑事项是什么?答:一般的模拟集成电路中,通常既有数字信号又有模拟信号,数字信号和模拟信号之间容易发生干扰。

在版图设计过程中,还要考虑地噪声对电路的影响。

即在整体版图的设计中,需着重考虑电路噪声问题,按照尽量降低噪声的原则进行电路的整体布局。

首先,在总体版图的布局上,尽量将数字部分远离模拟部分,如果总体电路中模拟部分偏多,则在版图设计中将数字部分放在靠边的位置,而且把模拟部分中最容易被数字干扰的部分放到离数字部分最远的位置,同时在数字部分和模拟部分中间用接地的衬底接触来进行隔离,反之亦然。

其次,采用隔离环设计,对每个单元模块都用一层接地的衬底接触,一层接电源的N阱构成的隔离环来进行隔离。

对于整个模拟部分和数字也分别采用相同的隔离环隔离,数字电路的隔离环可以吸收数字电路的衬底噪声,从而可以减少通过衬底串扰到模拟电路的衬底噪声。

隔离环包的层数越多,理论上吸收衬底噪声效果越好。

但是要避免数字电路的p隔离环紧靠模拟电路的p型隔离环,因为在这种情况下数字地的噪声会串扰到模拟地。

从而使模拟地受到干扰。

最后,除了数字模块之外的其它单元模块尽量将距离缩短,这样一方面能尽量地减少互连线经过别的区域引入噪声,同时也能降低引线过长引起电压信号的衰减。

2.总结自己的版图设计技巧和经验。

3. 共质心MOS管设计时的注意事项是什么?答:低精度要求可采用一维共质心,高精度要求必须采用二维共质心。

共质心设计时需保证MO管的对称性和电流通路的对称性。

4. 静电保护的种类以及版图设计注意事项。

答:常用的二极管式的静电保护分为两种方式,一种是用MOS晶体管连接成二极管形式的静电保护,一种利用CMOS工艺中二极管的静电保护。

在MOS型静电保护版图设计中,主要考虑以下几点:●MOS管要分成多个管,叉指结构,以便形成多支路共同放电。

●因为放电瞬间流经MOS管的电流特别大,构成整个放电通路的任何导线的宽度一定要有足够保证,而且CMOS工艺对于每个接触孔能通过的电流密度还有要求,因此还要保证放电通路导线上孔的数目应尽量多。

第一章1.1、集成电路测试的概念和分析过程测试的目的是检查电路设计和制造的正确与否,为此,需要建立一套规范的描述术语和检查分析方法。

测试的一般过程:建立描述电路“好”或“坏”的模型;设计出能检验电路“好”或“坏”的测试数据;把设计好的数据加在被检验的电路上;观察被检验的电路输出结果;最后分析与理想结果是否一致。

1.2、集成电路测试按照目的分类验证测试、特性测试或设计诊断(第一次投片):用于检查设计和测试过程的正确性,确定电路是否符合所有的设计规范。

生产测试(量产):对于所有加工的芯片所做的故障测试和随机缺陷测试。

可接受测试(用户验收):也称来料检查,即用户检查所购买的芯片,以保证质量。

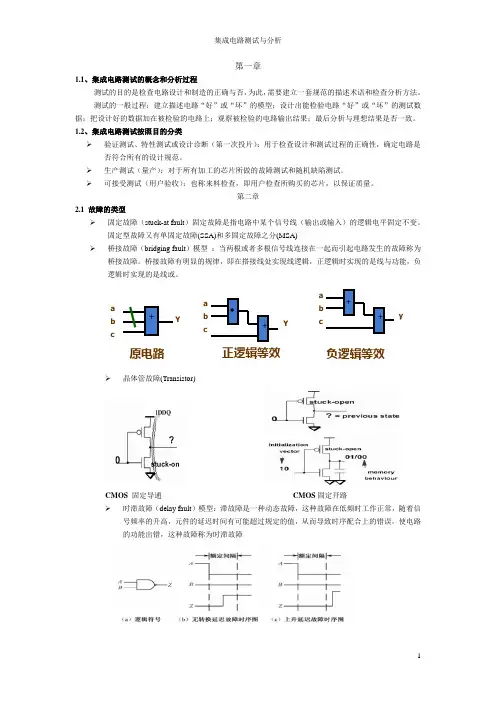

第二章2.1 故障的类型固定故障(stuck-at fault )固定故障是指电路中某个信号线(输出或输入)的逻辑电平固定不变。

固定型故障又有单固定故障(SSA)和多固定故障之分(MSA)桥接故障(bridging fault )模型 :当两根或者多根信号线连接在一起而引起电路发生的故障称为桥接故障。

桥接故障有明显的规律,即在搭接线处实现线逻辑,正逻辑时实现的是线与功能,负逻辑时实现的是线或。

晶体管故障(Transistor)CMOS 固定导通 CMOS 固定开路时滞故障(delay fault )模型:滞故障是一种动态故障,这种故障在低频时工作正常,随着信号频率的升高,元件的延迟时间有可能超过规定的值,从而导致时序配合上的错误,使电路的功能出错,这种故障称为时滞故障a b cY原电路Y正逻辑等效y负逻辑等效冗余故障:要么它是不可激活的,要么是无法检测出来,这种故障称为冗余故障。

这种故障的特点是不影响电路的逻辑功能2.2 解布尔方程法(异或法)假定n 个输入变量(x1,x2,…..xn)的电路:无故障时正常输出逻辑函数为:f(x1,x2,…..xn )有故障a 时的输出逻辑函数为:fa(x1,x2,……xn ) 若 则二者有差异故障定位测试(故障区分)一电路有a 故障的输出函数为:fa(x1,x2,……xn ) 该电路有b 故障的输出函数为:fb(x1,x2,……xn ) 解得到的测试集即为故障a 与b 的定位测试矢量 2.3 故障表法 以与门为例可见: (01) 可侦查 x1 s-a-1 故障; (00,01,10) 可侦查 y-s-a-1 故障; (00,10)可定位(区分)上述两故障;与解析法结果一样。

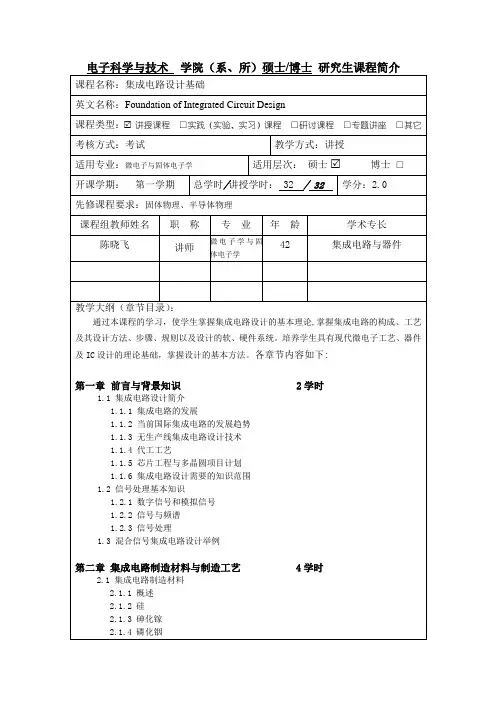

集成电路测试和可测性设计IC Testing and Design for Testability教学大纲课程名称:集成电路测试和可测性设计课程编号:M702004课程学分:3适用学科:集成电路工程、电子科学与技术一、课程性质本课程的授课对象为集成电路工程专业研究生和电子与科学技术专业研究生,课程属性为专业基础必修课(对电子与科学技术专业研究生为专业选修课)。

本课程主要讲授集成电路测试尤其是大规模集成电路测试的基本概念、基本方法,数字集成电路测试向量生成算法、可测试性设计、可测试性度量、数模混合信号电路测试方法以及测试设备和测试过程等内容。

通过基本思想、基本算法的引入、推导并配以大量的实例进行分析,使学生能够对测试相关理论有全面的理解,并能够利用所学的方法解决实际的电路测试及可测试性设计方面的问题。

二、课程教学目的学生通过本课程的学习,应能够理解集成电路测试及可测性的基本概念、基本思想;掌握重要的测试向量生成算法以及典型的可测性设计的结构;了解集成电路测试的发展趋势及面临的主要问题。

通过利用可测性设计方法构建实际的可测性方案,锻炼培养解决测试问题的实践动手能力。

同时通过对主要算法的发展历程、思想演变等的学习,培养发现问题、解决问题的能力以及创新思维。

为今后从事集成电路测试方面的工程或研究工作打下基础。

三、教学基本内容及基本要求第一章测试理论基础教学内容:1.1 引言1.2 VLSI测试过程和设备教学要求:1、掌握:集成电路测试的工作原理和工作过程。

2、理解:集成电路测试的基本概念。

3、了解:集成电路测试的特点,测试技术的发展及现状。

第二章测试经济学故障和故障模拟教学内容:2.1 测试经济学和产品质量2.2 故障模型教学要求:1、掌握:测试的经济性和故障定义。

2、理解:故障的含义和分类方法。

3、了解:测试与产品质量间的关系。

第三章逻辑与故障模型教学内容:3.1 用于设计验证的模拟3.2 用于设计评估的模拟3.3 用于模拟的模型电路3.4 用于真值模拟的算法3.5 故障模拟算法3.6 故障模拟的统计学方法教学要求:1、掌握:模型电路概念及类型,真值模拟的算法和故障模拟算法。

集成电路测试试题1、什么是验证测试(Verification Test)?简述验证测试的内容、方法及手段。

答:受EDA设计工具和设计语言的影响,在VLSI设计中,验证和测试是两个容易混淆的概念。

为了进一步明晰测试的地位和作用,我们有必要对比分析一下这两个概念:区别:1、对象不同验证-〉确认设计的正确性;测试-〉确认生产的正确性2、过程和方法不同验证-〉软件模拟、硬件仿真、形式验证;测试-〉设计、生成、应用(两个过程:测试生成测试应用)3、时机不同验证-〉生产前;测试-〉全过程4、作用不同验证-〉负责设计质量;测试-〉负责产品质量联系:一部分测试矢量可以以作为测试功能矢量。

上面的讲述后,我们对测试的角色可能还有的不太清晰,下面就对照考试模型,来条理化地总结一下:•Status / 地位:essentiality and importance•Aims / 目标:check and/or filter•Objects / 对象:manufactured chips•Contents / 内容:manufactured defects•Means / 方式:ATE•Time / 时间:from beginning to the end•Sites / 场地:testing roomVLSI测试的评价准则是coverage --- 覆盖率,即能探测到的缺陷或故障数量占总的可能存在的缺陷或故障数的百分比。

缺陷覆盖率理想的测试是能获得100%的缺陷覆盖率,即:1、探测生产过程产生的所有缺陷2、所有功能正确的器件都通过测试但实际上难以获得100%的缺陷覆盖率,这是因为:1、工艺复杂,规模庞大=〉缺陷的种类多、数量大2、面向缺陷的测试难题=〉缺乏合适的手段故障覆盖率与之相似,为解决面向缺陷的测试难题,人们根据缺陷的故障效应抽象出了各种更高层次的故障模型,相应地,测试评价准则就变为故障覆盖率。

然而,这又引出新的问题;1、缺陷和故障之间的相互映射问题;2、故障模型的完备性问题。