03实验十九 集成触发器及其应用电路设计

- 格式:doc

- 大小:315.00 KB

- 文档页数:5

电子电路试验报告

姓名:专业:班级:学号:

一、试验名称

集成触发器功能及其应用。

二、试验目的

掌握用与非门组成的基本RS触发器的特征;掌握集成JK触发器、D触发器的逻辑功能和使用方法;熟悉各种触发器的应用。

三、试验任务

用74LS73设计一个异步四进制计数器,并用双踪示波器观察输入输出波形。

四、试验任务原理

第一步:建立原始状态表和状态图。

第二步:简化状态(实际是状态合并)

第三步:状态分配(即状态编码)

第四步:选择触发器,求激励方程和状态转移方程

第五步:检查电路是否具有自启动特性

五、实现试验的电路图及其结果

试验电路图:实现的是6进制的计数器。

波形图:

六、思考题

(1)为解决主从JK触发器的一次变化问题,对CP脉冲有何要求?

答:对CP的要求是宽度较窄的正脉冲,且在CP=1期间,输入信号J,K不发生变化

七、试验心得与体会

通过这次电子电路试验,我对触发器有了了解,触发器是一种具有记忆功能的电路,可作为二进制存储单元使用。

触发器有置位端和复位端,只有当它们同时为1的时候,触发器才能正常工作,否则进行复位、置位、维持的功能,这些是我在这次试验中所学到的。

湖南工程学院课程设计课程名称集成电路原理与应用课题名称触发器设计专业电子科学与技术班级1102学号2011010402姓名德指导教师孙静2014 年12 月29 日湖南工程学院课程设计任务书课程名称集成电路原理与应用课题触发器设计专业班级电子科学与技术1102学生姓名德学号指导老师孙静审批任务书下达日期2014 年12 月22 日任务完成日期2015 年01 月02 日目录一、设计原理 (1)1.1 触发器的特点与分类 (1)1.2 D触发器原理 (1)1.3 软件介绍 (2)二、 D触发器的设计 (2)2.1 D触发器电路图设计 (2)2.1.1 反相器电路设计 (3)2.1.2 传输门电路设计 (3)2.1.3 D触发器电路图 (4)2.1.4 D触发器电路仿真 (4)2.2 D触发器版图的设计 (5)2.2.1 版图设计基本知识 (5)2.2.2 版图设计步骤 (6)2.2.3 版图的验证 (6)2.2.4 D触发器版图 (7)三、总结体会 (8)四、参考文献 (9)一、设计原理本设计是采用传输门逻辑设计一个D触发器,并利用Cadence软件对电路进行仿真;进行版图设计,并进行DRC和LVS验证。

1.1 触发器的特点与分类如下两个:1.有两个能够保持的稳定状态,分别用来表示逻辑0和逻辑1。

2.在适当输入信号作用下,可从一种状态翻转到另一种状态,在输入信号取消后,能将获得的新状态保存下来。

把触发器按触发方式分,可分为电位触发方式、主从触发方式及边沿触发方式。

按逻辑功能分,可分为R-S 触发器、D触发器、J-K触发器和T触发器。

1.2 D触发器原理锁存器是一种基本的记忆器件,它能够储存一位元的数据。

由于它是一种时序性的电路,所存器是一种基本的记忆器件,它能够储存一位元的数钟控制的记忆器件。

触发器具有一个控制输入讯号(CLOCK)。

CLOCK讯号使触发器只在特定时刻才按输入讯号改变输出状态。

若触发器只在时钟CLOCK由L到H (H到L)升沿(下降沿) 触发的。

集成触发器时序逻辑电路区别于组合逻辑电路,其任意时刻的输出值不仅与该时刻的输入变量的取值有关,而且与输入变量的前一时刻状态有关。

组成时序电路的基本单元是触发器。

K J -触发器和D 触发器是两种最基本、最常用的触发器,是构成时序逻辑电路的基本元件。

这两种触发器可以进行功能的转换;可以组成计数器、移位寄存器等常用的时序逻辑部件。

触发器的使用应注意以下几个方面:其一为触发器都有异步置位端D S 和复位端D R ,低电平有效,置位或复位后应恢复为高电平;其二为触发器的触发输入分为上升沿或下降沿触发,实验时通常用逻辑开关手动发出,按下开关(开关由断开状态0转变为接通状态1),这时发出的触发信号为上升沿脉冲,松开开关(开关由接通状态1转变为断开状态0),这时发出的触发信号为下降沿脉冲,这一点应特别引起注意,以免引起逻辑混乱。

集成D 触发器74LS74和集成K J -触发器74LS112的引脚如图4.1所示。

集成D 触发器74LS74为14引脚芯片,每片含有两片触发器,含有异步置位端D S 和异步复位端D R ,触发器的触发输入方式为上升沿触发。

在时钟的上升沿时刻,触发器输出Q 根据输入D 而改变,其余时间触发器状态保持不变。

集成K J -触发器74LS112为16引脚芯片,每片含有两片触发器,含有异步置位端D S 和异步复位端D R ,触发器的触发输入方式为下降沿触发。

D 触发器74LS74的功能表见表 4.1;K J -触发器74LS112的功能表见表 4.2。

D 触发器的特征方程为n+1Q D =;K J -触发器的特征方程为n+1n n n n Q J Q K Q =+。

CCU D DRD R CCU D R DR D DD图4.1 74LS74和74LS112引脚图表4.174LS74功能表表4.274LS112功能表。

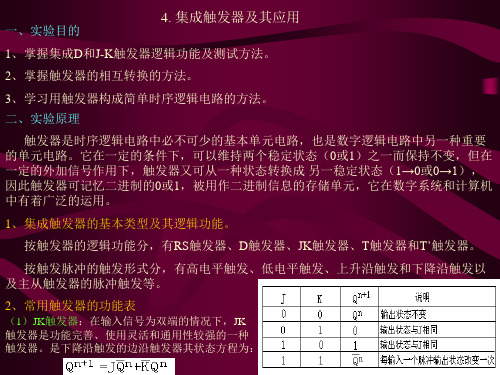

实验题目集成触发器及其应用小组合作否一、实验目的1.掌握基本RS、D和JK触发器的逻辑功能及测试方法。

2.熟悉D和JK触发器的触发方法。

3.了解触发器之间的相互转换。

二.实验环境1.数字电路实验箱1个2.集成电路与非门74LS00 1片双D触发器74LS74 1片双JK触发器74LS112 1片三、实验内容与步骤1.验证RS触发器的了解功能:按图4.1用74LS00组成基本RS触发器,并在Q端和Q’端接两只发光二极管,输入端S和R分别接了解开关。

接通+5V电源,按表4.1的要求改变S和R的状态,观察输出端的状态,并将结果填入表4.1中。

图4.1 RS触发器电路图如下:S R Q Q*0 0 0 00 0 1 10 1 0 00 1 1 01 0 0 11 0 1 11 - 0 不定1 1 1 不定表4.1 RS触发器逻辑功能2.验证D触发器的了逻辑功能将74LS74的Rd、Sd、D连接到逻辑开关,CP端接单次脉冲,Q 端和Q’端分别接两只发光二极管,接通电源,按表4.2的要求,改变Rd、Sd、D和CP的状态。

在CP从0到1跳变时,观察输出端Q*的状态,将测试结果填入表4.2中。

电路图如下:D Q Q*0 0 00 1 01 0 11 1 1表4.2 D触发器的逻辑功能3.验证JK触发器的逻辑功能将74LS112的Rd、Sd、J和K连接到逻辑开关,Q和Q’端分别接两只发光二极管,CP端接单次脉冲接通电源,按表4.3的要求,改变Rd、Sd、J和K的状态。

在CP从0到1跳变时,观察输出端Q*的状态,将测试结果填入表4.3中。

电路图如下:J K Q Q*0 0 0 00 0 1 10 1 0 00 1 1 01 0 0 11 0 1 11 1 0 11 1 1 0表4.3 JK触发器的逻辑功能四、实验过程与分析触发器是基本的逻辑单元,它具有两个稳定状态,在一定的外加信号作用下可以由一种稳定状态转换为另一种稳定状态;无外加作用信号时,将维持原状态不变。

触发器的应用实验原理实验目的•了解触发器在电子电路中的应用原理•学习触发器的基本工作方式和功能•掌握触发器在数字电路设计中的应用方法实验材料•数字电路实验板•TTL集成电路74LS74 2片•电源线、信号线•实验台•示波器实验原理触发器是一种存储和放大数字信号的电路元件。

触发器是数字系统中重要的基本存储元件之一,广泛应用于计算机、通信、控制系统等领域。

触发器能够存储一位二进制数字,并能根据输入信号的变化在指定的时刻输出存储的信息。

触发器的输出状态取决于其输入端信号以及触发器的类型。

常见的触发器有RS触发器、D 触发器、JK触发器等。

RS触发器原理RS触发器是最简单的触发器之一,由两个交叉连接的 NOR 门构成。

RS触发器有两个输入端 RS,两个输出端 Q 和Q’。

RS 触发器可以存储一位二进制数据。

RS 触发器有两种基本状态:复位状态(RESET)和设置状态(SET)。

工作原理如下: 1. 当 RS 触发器处于复位状态时,R 端输入为低电平,S 端输入为高电平,此时输出 Q 为低电平,输出Q’ 为高电平。

2. 当 RS 触发器处于设置状态时,R 端输入为高电平,S 端输入为低电平,此时输出 Q 为高电平,输出Q’ 为低电平。

D触发器原理D 触发器是一种单稳态触发器,能存储一个数据位。

D 触发器有一个数据输入端 D、一个时钟输入端 CLK 和两个输出端 Q、Q’。

工作原理如下: 1. 当时钟输入端 CLK 有信号输入时,D 触发器会在下一个时钟信号上升沿时,将 D 输入端的数值复制到输出端 Q。

2. 如果 CLK 为低电平,则 D 触发器不会改变输出状态。

JK触发器原理JK 触发器是一种带有扩展功能的 D 触发器。

JK 触发器有三个输入端 J、K、CLK 和两个输出端 Q、Q’。

工作原理如下: 1. 当时钟输入端 CLK 有信号输入时,根据 JK 触发器的输入信号,触发器会在下一个时钟信号上升沿时改变输出端 Q 的数值。

实验03 实验十九 集成触发器及其应用电路设计

(说明:CC4027 R D 、S D 接低电平)

1、验证JK 触发器逻辑功能

(1)特性方程

n

n n Q

K Q J Q

+=+1

(2)功能表(特性表) (3)器件原理图

(4)状态图

2、JK 触发器转换T 和D 触发器 (1)JK 触发器转换T 触发器 a 逻辑图

b 状态图

c 特性方程

n n n Q K Q J Q +=+1 n n n Q T Q T Q +=+1 (J =K =T )

d T 触发器特性表、转换图

JK 触发器特性表

J K ==× =0

J =1 K =1

T 触发器特性表

J K ==× =0

J =1

K =1 JK 状态图 T =0

T =1 T 状态图

(2)JK 触发器转换D 触发器

a 逻辑图

b 状态图

c 特性方程

n n n Q K Q J Q +=+1 D Q n =+1 (D J

= D K =)

d T 触发器特性表、转换图

3、JK 触发器组成二分频、四分频电路

(1)JK 触发器的特性方程、逻辑功能表

n n n Q K Q J Q +=+1

(2)电路连接原理(逻辑)图、逻辑功能表

D 触发器逻辑图

D 触发器状态图

D =1

D 触发器特性表

JK 触发器(功能)特性表

电路功能表

(3)逻辑函数式、状态图、波形图 a 逻辑函数式 n

n n n Q Q K Q J Q 000001

=+=+ (J 0=K 0=1) n

n n n n n n Q Q Q Q Q K Q J Q 101011111

1

+=+=+

b 状态图

c 波形图

4、同步3分频电路

(1)JK 触发器的特性方程、逻辑功能表

n n n Q K Q J Q +=+1

(2)状态表、状态图

J 0(K 0) Q 0n+1 CP =1kH Z Q 1n+1

J 1=K 1(Q 0)

J 0=K 0J =K =1

J 0=K 0=1 J 0=K 0=0

J 1=K 1J 1=K 1=1

J 1=K 1=0 JK 触发器(功能)特性表 × 0 1 × 1 × ×

1 ×

1

× 0 3

0 1

0 1 1 0 0

1 0 0 0

Q 1n

年 0

1

1

2 ×

×

×

1 ×

Q 0n 年 Q 1n+1年

Q 0n+1年 J 1

年 K 1 J 0

年 K 0

年 同步3分频电路状态真值表

由卡诺图得:

10Q J = 100Q Q K == 01Q J = 101Q Q K ==

n n

n Q Q Q 0111=+ n

n

n Q Q Q 011

0=+

(4)逻辑图

(5)波形图

5、可逆计数器(模4)状态真值表

(1)JK 触发器的特性方程、逻辑功能表 见4、(1)

(2)状态表、状态图

CP

(模4)状态真值表

1 × × 1 × 1 × 1 ×

1

× 0 3 0

1

1

1 1 0 0 0

1 0

0 0

Q 1n

年 0 0 1 0 2 1 × × 1 0 Q 0n 年

Q 1n+1年 Q 0n+1年

J 1

年 K 1 J 0

年 K 0

年 7

4 6

5 1 1 1

1

0 1 0 1 1 × 1 × × 1 1 × × 1 0 × 0 0 1 0 1 1 0

1

×

×

1

M Z

1 0 1 0 1 0 1

0 1 0 0 1 0 0 0

CP Q 0 Q 1 (模4)状态表 Q 1n

Q 0n

Q 1n+1 Q 0n+1/ Z

00 M =0

M =1

01

10 11

01/0 10/0 11/0 00/1

11/1 00/0 01/0 10/0

M Q M Q M Q M Q K J 000011⋅=+==

000Q K J == M Q Q M Q Q Z 0101+=

n n

n

n n n n Q M Q M Q Q M Q M Q Q 10010011)()(+++=+ M Q Q M Q Q M Q Q M Q Q n

n n n

n n n

n

01010101+++=

n

n Q Q 010=+

M Q Q M Q Q M Q Q M Q Q Z n n n

n

n n n

n

01010101=+=

(4)逻辑图

(5)波形图

Q 0

M

CP M Q 0 Q 1 0

1 2 3 4 5 6 7

Z。