ADC性能仿真

- 格式:docx

- 大小:16.94 KB

- 文档页数:1

仿真电路图,经过测试,没问题两个图是一体的。

模拟电路:设计模拟电路的原因主要有以下两点1.由于外界信号的复杂性,使得传感器直接输出的电信号可能会存在一些问题(如不稳定),这些不稳定信号如果直接送到A/D芯片进行采样,则最终结果可能使得最后的显示值来回乱跳,而无法确定待测的外界信号到底是多少。

因此,可能需要设计一套模拟电路对传感器输出的不稳定电信号进行滤波等处理,去除干扰,使得进入A/D转换芯片的电压值为一个稳定的信号。

2.每一个A/D转换芯片都有一个参考电压,只有输入的模拟电压值在这个参考电压的范围内才能进行正确的转换,例如:本试验将ADC0804芯片的参考电压设置成0V~5V,因此如果输入的电压值大于5V,则转换出的结果永远为0xFF,若输入的电压值小于0V,则转换出的结果永远为0,这样便无法正确的还原出被测信号的大小。

基于上述原因,我们可能需要设计一套模拟电路,传感器的输出电压值进行一些变换(放大,缩小),使得送到A/D转换芯片的电压值在转换芯片的参考电压范围内。

A/D转换芯片:即模拟/数字转换芯片,它将输入的模拟电压信号转换成单片机等控制处理器能够识别的数字二进制形式。

处理器芯片:处理器芯片有很多中(比如51单片机,ARM或者是PC上的奔腾处理器,AMD处理器)这些处理器虽然架构不一样,但是有个共同的特点,就是它们能够运行程序,因此它们能通过程序对A/D芯片送入的二进制形式的电压值进行处理,通过运算将其还原成待测的外界信号值,控制显示部件(如LCD,八段数码管)将这个值显示出来。

例如:假如ADC0804输出的二进制值0x80,则根据A/D转换公式可以推出ADC0804的输入电压大小为(0x80/0x100)*5V=2.5V。

假设信号经过模拟电路缩小了8倍,则可以推出传感器的输出电压为2.5V*8=20V,再根据传感器的转换公式(一般手册会给出)即可得到输入的外界信号的值。

显示:显示的作用是将计算出的待测外界信号的值展示给测量人员,显示的形式有很多种,如LCD,八段数码管,上位机软件等。

[1] 华光•电子技术基础(数字部分)(第4版)[M].北京:高等教育出版社,2000:388—416.[2] 闫石.数字电子技术基础(第4版)[M].北京:高等教育出版社,1998:456—439[3] 余集成.电子测量检测——剖析双积分AD转换器:《技术讲座》DOI:10.16589/ 11-3571/t n.2008.0913[4] 石会.逐次逼近型ADC的电路分析:解放军理工大学通信工程学院南京210007《中国电子教育》2016年第4期⑸李云•超高速高精度并行ADC系统的设计与实现1008- 0570(2008)07- 20307- 03⑹高静姚素英徐江涛史再峰•高速并行10位模数转换电路的设计文章编号0493-2137 (2010)06-0498-064.进度安排AD基本原理仿真摘要:目前,科学技术进步突飞猛进,数字系统技术被广泛应用于生活的方方面面,数字系统相对于模拟系统,显示出了其巨大的优势。

然而,由于数字系统并不能够用于模拟信号的应用处理,仅能够用于数字信号的处理,但是,人们日常生活生产当中,很多物理量都是取值连续的模拟量,如压力,温度,流量,速度,距离等等。

我们可以通过传感器将这些取值连续的物理量变成幅值或者频率连续的电压量或者电流量。

然后在经过一个模数转换电路,将模拟量转换成易于处理的数字量。

编码、量化、保持以及抽样是吧模拟信号转换成数字信号的四大步骤。

抽样通常都在特定的抽样-保持来完成,量化编码则在模数转换器(ADC中完成。

根据不同的原理,ADC也有不同的分类。

压频变换型、并行比较型以及电容阵列逐次比较型都是比较常见的类型,而逐次渐进型(逐次比较型)、双积分型也是较为常见的一种。

文章对三种常见AD转换器的原理,比如双积分型、并行比较型以及逐次渐进型进行了重点研究。

根据其原理设计三种不同的AD转换器。

并且利用Multisim 对三种不同的结构进行仿真。

对这三种结构进行性能的分析。

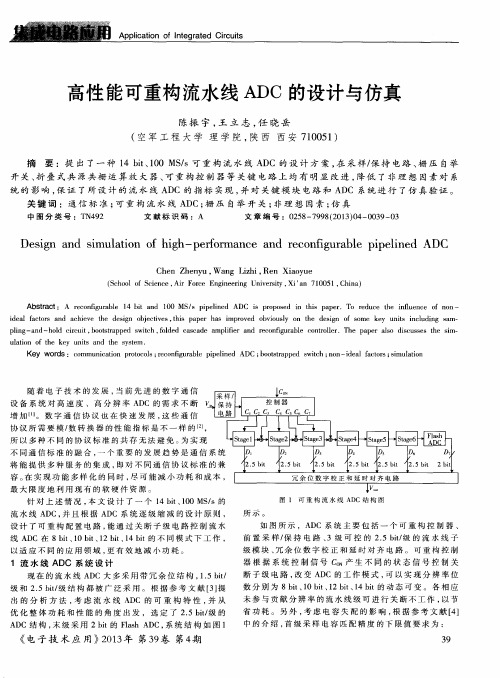

第五章 ADC性能仿真本章旨在分析ADC转换器的结构,并建立ADC的模型和仿真系统。

通过仿真检验Dither 信号、噪声、采样时钟抖动以及ADC的非线性特性对ADC性能的影响。

第一节 A/D转换器的模型ADC的作用是将一定幅度的模拟信号转换为相应的数字量,传递函数反映了它最基本的特征。

理想的ADC传递函数是一个等间距的阶梯图,如第二章图2-1-2所示。

由于实际的ADC存在非线性特性,所以它的传递函数是一个非等间距的阶梯图,如第二章图2-2-3所示。

用公式表示其传递函数如下:式(5-1-1)是理想ADC的传递函数;式(5-1-2)是实际ADC的传递函数,其中Yn是ADC的数字输出,X是模拟输入信号,LSB为最小量化电平,DNL(k)为微分非线性参数。

从式(5-1-2)中可以看出,要想模拟实际ADC的特性,必须分析其结构,得出其非线性参数。

从ADC的结构上看,有逐次比较(successive approximation)式ADC、快闪(flash)式ADC、分级快闪(subranging flash)式ADC和∑-∆式ADC等。

要实现中频或射频采样,就必须采样高速大动态范围的ADC,而目前高速大动态范围的ADC都采用分级快闪式结构。

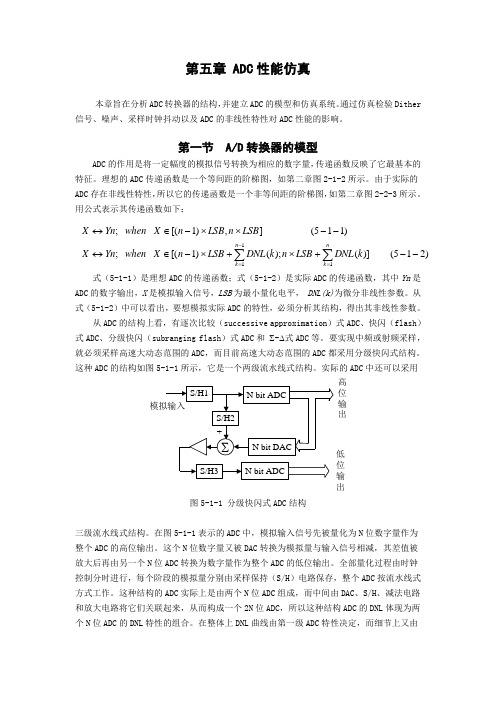

这种ADC的结构如图5-1-1所示,它是一个两级流水线式结构。

实际的ADC中还可以采用高位输出低位输出图5-1-1 分级快闪式ADC结构三级流水线式结构。

在图5-1-1表示的ADC中,模拟输入信号先被量化为N位数字量作为整个ADC的高位输出。

这个N位数字量又被DAC转换为模拟量与输入信号相减,其差值被放大后再由另一个N位ADC转换为数字量作为整个ADC的低位输出。

全部量化过程由时钟控制分时进行,每个阶段的模拟量分别由采样保持(S/H)电路保存,整个ADC按流水线式方式工作。

这种结构的ADC实际上是由两个N位ADC组成,而中间由DAC、S/H、减法电路和放大电路将它们关联起来,从而构成一个2N位ADC,所以这种结构ADC的DNL体现为两个N位ADC的DNL特性的组合。

目录一、设计任务及性能指标 (2)二、设计要求 (2)三、方案设计与论证 (2)3.1 方案设计原理 (2)3.2 方案论证 (3)四、具体设计过程 (4)4.1AD0809的工作时序图 (4)4.2 程序流程图 (5)五、测试结果 (6)5.1仿真时序图 (6)5.2RTL原理图 (7)5.3 Moore型有限状态机状态图 (7)六、附录 (8)6.1程序代码 (8)6.2 心得体会 (11)7.参考文献 (14)ADC0809的应用一、设计任务及性能指标1.利用实验箱上FPGA芯片控制ADC0809的时序,进行AD转换,然后将ADC0809转换后的数据以十六进制的数据显示出来。

2.实现时必须严格遵守ADC0809的工作时序,在编写代码时要注意。

对选定的通道输入一个模拟量,调节电位器改变输入的模拟量。

3.了解ADC0809的工作原理4.了解用扫描方式驱动七段码管显示的工作原理。

5.了解时序电路FPGA的实现。

6.学习用VHDL语言来描述时序电路的过程。

二、设计要求基本要求:1、采用状态机2、控制ADC0809的第三通道进行AD转换3、转换结果显示格式00~FF三、方案设计与论证3.1 方案设计原理ADC0809是CMOS的8位A/D转换器,片内有8路模拟开关,可控制8个模拟量中的一个进入转换器中。

ADC0809的分辨率为8位,转换时间约100us,含锁存控制的8路多路开关,输出有三态缓冲器控制,单5V电源供电。

主要控制信号说明:如图3.1所示,START是转换启动信号,高电平有效;ALE是3位通道选择地址(ADDC、ADDB、ADDA)信号的锁存信号。

当模拟量送至某一输入端(如IN1或IN2等),由3位地址信号选择,而地址信号由ALE锁存;EOC是转换情况状态信号(类似于AD574的STATUS),当启动转换约100us后,EOC产生一个负脉冲,以示转换结束;在EOC的上升沿后,若使输出使能信号OE为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线。

12位100MHz流水线型ADC行为级建模与仿真作者:王月海刘红岩来源:《电脑知识与技术》2016年第24期摘要:为了提高大规模集成电路的设计效率,该文通过Verilog-A对子ADC、MADC电路、数字校正电路等关键单元进行建模,最后得到12比特100MHZ的流水线型ADC模型,采用Cadence的Spectre仿真器进行仿真验证。

通过仿真结果验证得到SNDR为72.9465dB,SNR为72.9484dB距离理想的12比特ADC模型的SNR只差1.0516dB,ENOD为11.8155距离理想的12比特ADC的ENOD只差0.1845,以此验证了本文的ADC是高速有效的ADC模型。

关键词: Verilog-A;行为级建模;流水线型ADC中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2016)24-0236-03行为级建模的方法有很多,Matlab/Simulink建模 [1],模型通用性和可移植性差。

采用VHDL-AMS(VHDL Analog and Mixed-Signal Extensions)建模[2],但并没有创建出针对流水线的实际非理想因素进行特定的流水线结构ADC模型。

利用Pspice和Simulink进行联合仿真[3],但是普通用户无法得知系统内部详细的电路结构和参数。

基于Verilog-A对多位每级流水线ADC做行为级建模,Verilog-A可以使用电路仿真工具Spectre仿真,而且可以精确描述模拟电路中的各种性能参数,Verilog-A主要通过基尔霍夫电流定律和基尔霍夫电压定律,描述输入输出信号之间的电路行为,verilog-A可以描述时钟抖动、运放增益等非理想因素。

本文通过Verilog-A对子ADC、MADC电路、数字校正电路等关键单元进行建模,最后得到12比特100MHZ的流水线型ADC模型,采用Cadence的Spectre仿真器进行仿真验证。

如何仿真ADC的模拟器件?逐次逼近、模数转换器(SAR-ADC) 很简单直接,用户将模拟电压接在输入端上(AINP, AINN, REF),会看到一个输出数字代码,这个代码表示相对于基准的模拟输入电压。

此时,用户也许很想分析一下转换器的技术规格,来验证转换器的运行是否符合数据表中的标准。

尤其当用户发现不够快的时候,更需要确定转换器是否已经接收到内部正确的模拟信号。

用户可以通过使用仿真工具来预测发生这些问题的可能性,并解决这些问题。

ADC模拟输入级仿真的确定依赖于电压和电流的准确度。

正是在这个方面,模拟SPICE宏模型能够发挥作用。

PCB数字信号完整性取决于定时、电压-电流电平、以及寄生效应。

而数字IBIS 模型在这方面会比较有用。

我们会在下个月来谈一谈IBIS,不过让我们先解决ADC的仿真环境。

针对ADC的SPICE仿真将信号传送到ADC中的试错法是比较耗时的,并且不一定会起作用。

如果用户的模拟输入引脚在转换器正在捕捉电压信息的关键时间点上不稳定,这就不太可能获得正确的输出数据。

SPICE模型使你能够进行的第一步操作就是验证全部的模拟输入,这样的话,就不会有错误信号进入到你的转换器中了。

我们来仔细看一看一款与ADS8860相似的典型串行、伪差分SAR-ADC器件(图1)。

这款器件的TINA-TI SPICE模型使用户能够仿真进入转换器的模拟信号所产生的效果。

借助于这款模型,以及AINP、AINM、REF上合适的驱动器运算放大器模型,在用户进行实际的PCB操作之前,确定是否能够实现良好转换。

ADC宏模型的重要性在于,它能够准确地描述转换器输入端子的特性。

驱动AINP、AINN和REF的运算放大器还必须准确地模拟它们的开环输出电阻(Ro)。

我们来仔细看一看这款宏模型的工作方式。

这款转换器宏模型用55pF采样电容器对正、。

14位Single―slope ADC行为级建模与仿真摘要:单斜率型模/数转换器以其简单的结构、较高的分辨率和易于集成的优势,在红外焦平面读出电路设计中被广泛应用。

基于Matlab软件环境下的Simulink工具,建立了一个14位Single?slope ADC的系统模型。

其充分讨论Simulink工具下电路各单元模块的具体实现和信号间的时序关系,给出电路的行为级仿真结果,为Single?slope ADC的集成电路设计与实现提供参考。

关键词:单斜模/数转换器;行为级建模;红外焦平面;Simulink;集成电路设计;功能仿真中?D分类号:TN492?34 文献标识码:A 文章编号:1004?373X(2018)16?0104?04Abstract:As the single?slope ADC has the advantages of simple structure,high resolution,and easy integration,it has been widely used in the design of the infrared focal plane read?out circuit. Based on the Simulink tool in the Matlab software environment,a 14?bit single?slope ADC system model is built. The specific implementation utilizing the Simulink tool for each unit module of the circuit and the time sequence relationship among signals are fully discussed. The behavioral simulation results of the circuit are given,whichprovides a reference for the design and implementation of the single?slope ADC integrated circuit.Keywords:Single?slope ADC;behavioral modeling;infrared focal plane;Simulink;integrated circuit design;functional simulation 0 引言红外焦平面成像系统在军事、医疗扫描、空间探测、环境监控以及民用消费电子方面有着广泛的应用[1]。

1.用calculator把你的数字比特输出按不同权重做和,得到重建信号

2.对重建信号做dft,再做spectralPower,注意跑了多少点就做多少点的dft。

最好是64,128,。

但是cadence里跑一个tran很花时间,尤其是跑高精度的tran,所以你要在精度和仿真时间上做权衡

3.重建信号和延时的输入信号做差,你的tb上要有两个信号源,其中s1进adc,s2接电阻到地。

s2是s1的延时版本,s1进adc后延时多少时间才输出,s2也同样延时多少时间

4.对差信号做sample得到每个采样点的量化误差,注意sample的起始时间是s1的延时时间

5.把4中得到的信号除以LSB,做abs,再做average,得到用LSB表示的平均量化误差。

你可以用这个误差估计adc的性能,当然这个误差一定要小于0,5LSB

6.以上步骤中提到的函数在cadence里的calculator里都有,你去找找吧。

不同版本的cadence 对dft的定义似乎有差别,你可以试试

终了时间=起始时间+63*时钟周期,终了时间=起始时间+64*时钟周期,结果会有不同。

至于INL和DNL,还有ENOB,我还没想出来,不过估计是用锯齿波做输入,再把输出重建为阶梯波形,当然要在时序上对齐

嘻嘻,先把期末考试应付过去,暑假里再想想

小的最近做了一个adc,现在在做动态特性的仿真,sfdr,thd都可以从频谱中直接计算,好象sndr,snr不能直接计算,看了一些matlab的代码,有些函数不是特别理解,但根据自己的理解在计算adc的动态特性,结果感觉也比较正常,下面说一下我的理解,请高人指点一下,看我的这种理解是否合理.

1.用cadence的计算器做dft,这里不乘以20db,得到一个频谱,通常的频谱是乘以20db的结果.

2.把1得到的频谱的每个点用计算器里面的一个列表功能全列出来,然后用csv后缀进行保存,并把保存的结果从服务器导到自己用的终端上,在windows下csv后缀的文件会被转为excel格式.

3.sndr的计算:在得到的excel里,把基波处的值设为0,对其他所有项求平方和,excel 提供这个函数,然后用基波处那个值的平方除以前面得到的平方和,得到的结果再取10log10,就得到了sndr,通过sndr就可算得enob.

4.snr的计算:和上面的第一个步骤相同,在得到的excel里面,把基波处的值设为0,同时把需要考虑的偕波值也设为0,剩下的可认为是量化噪声,然后把剩下的项求平方和,用基波处的值除以前面得到的平方和再乘以10log10就得到了snr.

5.thd的计算:把上一步那些需要考虑成谐波的量求平方和,设这个值为a,然后b=a+基波处值^2,thd=10log10(a/b).

这是我对这几个参数的计算方法,不知道是否有问题,请高人指点啊.。