计算机组成原理2.2定点加减法运算

- 格式:ppt

- 大小:177.00 KB

- 文档页数:43

第二章 运算方法和运算器本章内容 2.1 数据与文字的表示方法 2.2 定点加法、减法运算 2.3 定点乘法运算 2.4 定点除法运算 2.5 定点运算器的组成 2.6 浮点运算方法和浮点运算器中山大学 信息科学与技术学院 陈 任 2010.92.3 定点乘法运算2.3.1 原码乘法1.人工算法与机器算法的同异性 运算规则:乘积的符号位由两数的符号位按异或运算得到, 乘积的数值部分则是两个正数相乘之积。

设n位被乘数和乘数用定点小数表示(定点整数也同样适用) 被乘数 [x]原=xf xn-1…x1x0 乘数 [y]原=yf yn-1…y1y0 则乘积[z]原=(xf⊕yf)+(xn-1…x1x0)(yn-1…y1y0) 式中,xf为被乘数符号,yf为乘数符号。

乘积符号的运算法则是:同号相乘为正,异号相乘为负。

由于 被乘数和乘数和符号组合只有四种情况(xfyf=00,01,10,11),因 此积的符号可按“异或”(按位加)运算得到。

数值部分的运算方法与普通的十进制小数乘法类似,不过对于 用二进制表达式的数来说,其乘法规则更为简单一些。

2 设x=1101,y=1011,先用习惯方法求其乘积,其过程如下:设x=1101,y=1011,用习惯方法求其乘积,其过程如下运算的过程与十进制乘法相似:从乘数y的最低位开始,若这一位 为“1”,则将被乘数x写下;若这一位为“0”,则写下全0。

然 后在对乘数y的高一位进行乘法运算,其规则同上,不过这一位乘 数的权与最低位乘数的权不一样,因此被乘数x要左移一位。

以 此类推,直到乘数各位乘完为止,最后将它们统统加起来,变得到最 后乘积z。

3问题:人们习惯的算法对机器并不完全适用。

原因之一:机器通常只有n位长,两个n位数相乘,乘积可能为2n位。

原因之二:只有两个操作数相加的加法器难以胜任将n个位积一次 相加起来的运算。

被乘数x=1101,乘数y=1011.早期计算机中为 了简化硬件结构,采 用串行的1位乘法方 案,即多次执行“加 法—移位”操作来 实现。

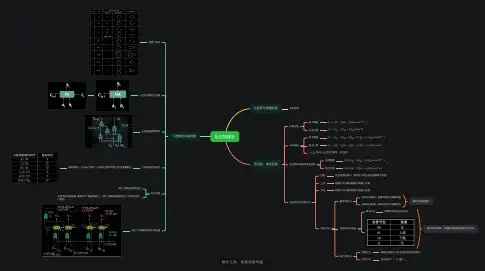

定点加减法

位运算与逻辑运算非常简单

定点加、减法运算补码加法定点整数[x +y ]=补[x ]+补[y ]

补(mod 2)n +1定点小数[x +y ]=补[x ]+补[y ]补(mod 2)

补码减法定点整数[x −y ]=补[x ]−补[y ]=补[x ]+补[−y ]补(mod 2)n +1定点小数[x −y ]=补[x ]−补[y ]=补[x ]+补[−y ]补(mod 2)

等于的各位取反,末位加1

[−y ]补[y ]补定点数补码的加减法运算定点整数[x ±y ]=补[x ]+补[±y ]补(mod 2)n +1定点小数

[x ±y ]=补[x ]+补[±y ]补(mod 2)溢出概念与检验方法溢出

在定点数机器中,数的大小超出定点数能表示范围上溢数据大于机器所能表示的最大正数

下溢数据小于机器所能表示的最小负数

检验方法直接判别法

同号补码相加,结果符号位与加数相反异号补码相减,结果符号位与减数相同

硬件实现较复杂

变形补码判别法模4补码采用双符号位表示补码硬件实现简单,只需要对结果的符号进行异或

进位判别法

判别方法

最高位的进位与符号位的进位是否相同判别公式溢出标志V =C C f ⨁n −1二进制加法减法器逻辑门符号

一位半加器和全加器

全加器的逻辑结构门电路的时间延迟通常采用一个与非门或者一个或非门的时间延迟作为度量单位补充内容

与非门具有函数完备性在使用多发射极晶 体管的TTL集成电路中,与非门需要的晶体管也少于其他任何门电路多位二进制数据加法/减法器。