Cyclone II系列FPGA配置手册

- 格式:pdf

- 大小:3.30 MB

- 文档页数:28

一、外文资料译文:Cyclone II器件系列简介关键词:cyclone II器件;特点;简介;在非常成功的第一代Cyclone器件系列之后,Altera的Cyclone II FPGA系列扩大低成本的FPGA的密度,最多达68,416个逻辑单元(LE),提供622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。

Cyclone II器件的制造基于300毫米晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术是使用低绝缘体过程以确保了快速有效性和低成本。

通过使硅片面积最小化,Cyclone II器件可以在单芯片上支持复杂的数字系统,而在成本上则可以和ASIC竞争。

不像其他用电力功耗和性能来换取低成本的FPGA卖主,Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。

低成本和优化特征使Cyclone II FPGA系列为各种各样的汽车、消费、通讯、视频处理、测试与测量、和其他最终市场提供理想的解决方案。

在参考设计、系统图,和IP,使用cyclone II FPGA系列可以帮助你迅速实现最总市场方案开发。

低成本的嵌入式解决方案Cyclone II 器件支持Nio s II 嵌入式处理器,能够自己完成自定义的嵌入式处理器。

Cyclone II器件还能够扩展各种外部存储器和I/O口或者嵌入式处理器的性能。

单个或多个NiosII嵌入式系统中嵌入式处理器也可以设计成cyclone II设备以提供一些额外的同时处理的能力或者甚至取代已经在你的系统中存在的嵌入式处理器。

使用cyclone II和nios II 能够拥有成本低和高性能处理方案的共同特点,和普通的产品相比,这个特点能够延长你的产品的生命周期,提高产品进入市场的时间。

低成本DSP方案单独使用cycloneII FPGA 系列或者或者作为数字信号处理(DSP)协处理器以提高数字信号处理(DSP)应用的性价比。

嵌入式开发笔记——MCU配置Altera-Cyclone系列FPGA作者:zzssdd2E-mail:*******************1、需求描述FPGA内部是SRAM储存结构,掉电后程序就会丢失,故需要将FPGA程序保存在掉电不丢失的储存介质中(比如FLASH、EMMC、SD卡等),在每次上电时读取程序进行配置。

2、功能分析项目中使用的FPGA型号是Altera公司(现属于Intel)的Cyclone系列。

在Altera的文档《Cyclone Device Handbook,Volume1》的第13章节讲述了该系列FPGA的几种配置方式。

FPGA'的三种配置模式模式描述AS(Active serial)模式FPGA主动配置。

该模式由FPGA主动从外部储存器读取配置数据PS(Passive serial)模式FPGA被动控制。

该模式由外部控制器对FPGA进行配置JTAG模式通过外部下载器下载到FPGA内部SRAM中FPGA选择配置模式通过MSEL0和MSEL1引脚不同的电平来选择配置方式(如果使用JTAG配置则可以忽略这些引脚配置)MSEL1 MSEL0 模式0 0 AS0 1 PSx x JTAG最终确定的方案是使用PS模式通过MCU来升级、配置FPGA。

下面主要讲使用MCU对FPGA进行PS模式下的配置过程。

PS模式配置引脚时序•发起配置请求o nCONFIG引脚拉低tCFG时间然后拉高,等待nSTATU拉低响应请求•进行配置o FPGA在DCLK引脚的上升沿采集DATA引脚Bit数据,LSB在前传输方式•配置完成o等待CONF_DONE引脚回应一个高电平表示配置完成PS配置模式时序参数3、功能实现配置FPGA用到的变量和标志static uint8_t fpga_cfg_buf[W25Q_SECTOR_SIZE]; //储存从FLASH读出数据static __IO uint8_t fpga_cfg_sta = 0x00; //记录配置状态//配置过程用到的标识enum{FPGA_CFG_ENABLE = 0x01,FPGA_CFG_START = 0x02,FPGA_CFG_DONE = 0x04,FPGA_CFG_OVER = 0x08,};MCU与FPGA连接引脚配置/**************************************************************** ******** 函数: fpga_config_init* 功能: 配置FPGA引脚* 输入: 无* 输出: 无*************************************************************** ********/void fpga_config_init(void){GPIO_InitTypeDef GPIO_InitStruct = {0};/* 引脚时钟使能 */FPGA_PIN_CLK_ENABLE();/* nCFG、DAT、CLK配置为输出 */GPIO_InitStruct.Pin = FPGA_nCFG_PIN;GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;GPIO_InitStruct.Pull = GPIO_NOPULL;GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;HAL_GPIO_Init(FPGA_nCFG_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_DAT_PIN;HAL_GPIO_Init(FPGA_DAT_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_CLK_PIN;HAL_GPIO_Init(FPGA_CLK_PORT, &GPIO_InitStruct);/* nSTA、CFG_DONE配置为输入 */GPIO_InitStruct.Pin = FPGA_nSTA_PIN;GPIO_InitStruct.Mode = GPIO_MODE_INPUT;GPIO_InitStruct.Pull = GPIO_NOPULL;HAL_GPIO_Init(FPGA_nSTA_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_CFG_DONE_PIN;HAL_GPIO_Init(FPGA_CFG_DONE_PORT, &GPIO_InitStruct);/* 配置引脚默认状态 */HAL_GPIO_WritePin(FPGA_nCFG_PORT, FPGA_nCFG_PIN, GPIO_PIN_SET);HAL_GPIO_WritePin(FPGA_DAT_PORT, FPGA_DAT_PIN, GPIO_PIN_RESET);HAL_GPIO_WritePin(FPGA_CLK_PORT, FPGA_CLK_PIN, GPIO_PIN_RESET);}MCU对FPGA配置过程/**************************************************************** ******** 函数: fpga_config_process* 功能: FPGA程序配置* 输入: _uiDataSize:FPGA配置文件大小* _uiStartAddr:FLASH储存FPGA配置文件地址* 输出: 失败:< 0; 成功:0*************************************************************** ********/int fpga_config_process(uint32_t _uiDataSize, uint32_t _uiStartAddr){UINT interrupt_save;uint16_t i, j;uint32_t uiTout, uiRdAddr, uiCnt = 0;fpga_cfg_sta = 0;uiRdAddr = _uiStartAddr;/*############## 第一阶段:发起配置请求########################*/FPGA_PinWrite(FPGA_nCFG_PORT,FPGA_nCFG_PIN,GPIO_PI N_RESET);dwt_delay_us(100);FPGA_PinWrite(FPGA_nCFG_PORT,FPGA_nCFG_PIN,GPIO_PI N_SET);dwt_delay_us(40);/* 等待FPGA回应:100ms超时 */for (uiT out = 0; uiT out < 10000; uiTout++){if (GPIO_PIN_RESET == FPGA_PinRead(FPGA_nSTA_PORT,FPGA_nSTA_PIN)){SET_BIT(fpga_cfg_sta, FPGA_CFG_START);break;}dwt_delay_us(10);}/* 是否响应? */if (!READ_BIT(fpga_cfg_sta, FPGA_CFG_START)){return -1;}/*############## 第二阶段:进行配置########################*/do{W25Q_ReadBuffer(fpga_cfg_buf, uiRdAddr, W25Q_SECTOR_SIZE);uiRdAddr += W25Q_SECTOR_SIZE;for (i = 0; i < W25Q_SECTOR_SIZE; i++){/* 按bit写入,LSB在前 */DISABLE_IRQ();for (j = 0; j < 8; j++){if (fpga_cfg_buf[i] & 0x01){FPGA_PinWrite(FPGA_DAT_PORT,FPGA_DAT_PIN,GPIO_PIN_S ET);}else{FPGA_PinWrite(FPGA_DAT_PORT,FPGA_DAT_PIN,GPIO_PIN_ RESET);}FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_R ESET); Delay(2);FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_S ET); Delay(2);FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_R ESET); Delay(2);fpga_cfg_buf[i] >>= 1;ENABLE_IRQ();/* 数据写入完毕退出 */if (++uiCnt >= _uiDataSize){SET_BIT(fpga_cfg_sta, FPGA_CFG_OVER);break;}}}while(RESET == READ_BIT(fpga_cfg_sta, FPGA_CFG_OVER));/*############## 第三阶段:等待配置完成回应########################*/for (i = 0, uiT out = 0; uiTout < 20000; uiTout++){dwt_delay_us(100);if (GPIO_PIN_SET == FPGA_PinRead(FPGA_CFG_DONE_PORT,FPGA_CFG_DONE_PIN)) {if (++i >= 10){SET_BIT(fpga_cfg_sta, FPGA_CFG_DONE);break;}}else{i = 0;}if (READ_BIT(fpga_cfg_sta, FPGA_CFG_DONE)) {return 0;}else{return -1;}}。

使用手册目 录第一章综述 (1)EP1C12核心板资源介绍 (1)FPGA开发板资源介绍 (2)第二章 系统模块功能介绍 (5)EP1C12核心板模块说明EP1C12F324C8芯片说明 (7)NOR FLASH模块说明 (8)SRAM模块说明 (9)FPGA接口I/O说明 (10)调试接口JTAG、AS说明 (11)其它功能模块 (12)EP1C12核心板使用注意事项 (15)FPGA开发平台模块说明液晶显示模块 (17)RTC实时时钟模块 (19)USB接口模块 (19)音频CODEC接口模块 (20)EEPROM存储模块 (21)数字温度传感器模块 (22)其它功能模块 (23)FPGA开发平台使用注意事项 (24)附表一核心板载资源与FPGAEP1C12I/O接口对照表 (25)附表二EP1C12与开发板硬件资源I/O接口对照表 (30)第一章综述FPGA开发来台是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板EP1C12、SOPC开发平台和扩展板构成,根据用户不同的需求配置成不同的开发系统。

EP1C12核心板EP1C12核心板为基于Altera Cyclone器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源:1主芯片采用Altera Cyclone器件EP1C12F324C82EPCS4I8配置芯片34个用户自定义按键44个用户自定义LED51个七段码LED6标准AS编程接口和JTAG调试接口750MHz高精度时钟源8三个高密度扩展接口9系统上电复位电路10支持+5V直接输入,板上电源管理模块系统主芯片采用324引脚、BGA封装的E1C12 FPGA,它拥有12060个LE,52个M4K 片上RAM(共计239616bits),2个高性能PLL以及多达249个用户自定义IO。

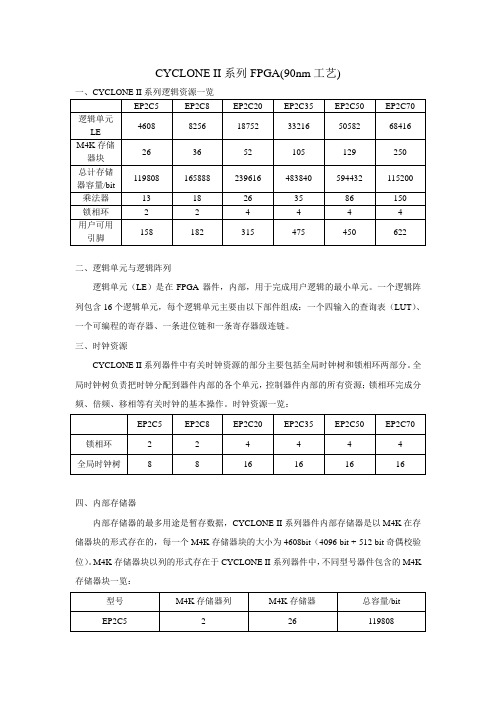

CYCLONE II系列FPGA(90nm工艺)二、逻辑单元与逻辑阵列逻辑单元(LE)是在FPGA器件,内部,用于完成用户逻辑的最小单元。

一个逻辑阵列包含16个逻辑单元,每个逻辑单元主要由以下部件组成:一个四输入的查询表(LUT)、一个可编程的寄存器、一条进位链和一条寄存器级连链。

三、时钟资源CYCLONE II系列器件中有关时钟资源的部分主要包括全局时钟树和锁相环两部分。

全局时钟树负责把时钟分配到器件内部的各个单元,控制器件内部的所有资源;锁相环完成分频、倍频、移相等有关时钟的基本操作。

时钟资源一览:四、内部存储器内部存储器的最多用途是暂存数据,CYCLONE II系列器件内部存储器是以M4K在存储器块的形式存在的,每一个M4K存储器块的大小为4608bit(4096 bit + 512 bit奇偶校验位)。

M4K存储器块以列的形式存在于CYCLONE II系列器件中,不同型号器件包含的M4K 存储器块一览:CYCLONE II 系列器件中的M4K 可以被配置为以下模式:单口模式、简单双口模式、完全双口模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

五、FPGA 芯片的配置由于CYCLONE II 系列的FPGA 是基于SRAM 工艺制造的,SRAM 属于易失性的存储媒质,因此FPGA 在每次上电时必须重新配置。

CYCLONE II 系列的FPGA 支持3种配置方式:主动串行(AS )、被动串行(PS )和JATG 模式。

CYCLONE II 器件的配置分为3个阶段:复位阶段、配置阶段和初始化阶段。

六、FPGA 内部资源的使用锁相环(PLL )配置,锁相环一般用于同步输入时钟和输入数据,以及完成时钟综合,包括分频、倍频、移相等操作。

PLL 配置需求:CYCLONE II 系列器件中的M4K 配置为以下模式:单口RAM 模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

摘要:本文主要通过介绍Cyclone 系列FPGA 器件的配置方案,主要阐述了低成本专用配置芯片的主动串行(AS )配置方案以及基于微处理器的被动串行(PS )配置方案的配置过程。

介绍了如何结合工程设计选择配置方案,改变现在的任意选择配置方案的现象。

提出一种实时解压数据减少贮存要求和配置时间的配置方案,这些方案在工程项目中具有很高的实际应用价值。

关键词:Cyclone FPGA 配置模式主动串行被动串行0引言FPGA 是英文Field -Programmable Gate Array 的缩写,即现场可编程门阵列,它是在PAL 、GAL 、CPLD 等可编程器件的基础上进一步发展的产物。

FPGA 技术广泛应用于通讯、视频、信息处理等特定领域。

FPGA 主要生产厂商有Altera 、Xilinx 、Actel 和Lattice ,对比不同的FPGA 编程技术特点,综合各个厂家不同系列器件的技术优势、逻辑资源、器件功耗、芯片速度、供货、价格和系统要求等诸多因素考虑,在很多项目设计中采用Altera 公司基于SRAM 架构Cyclone 系列器件。

Cyclone 器件与其他FPGA 器件一样是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。

这些配置数据可通过多种模式加载到FPGA 内部的SRAM 中,由于SRAM 的易失性,每次上电时,都必须对FPGA 进行重新配置。

1Cyclone FPGA 配置模式Cyclone 系列FPGA 器件配置方案主要有三种,包括使用低成本配置芯片的主动串行(AS )配置、被动串行(PS )配置以及基于JTAG 配置,实际应用时可以使用其中的一种方案配置Cyclone 系列FPGA 器件,来实现用户编程所要实现的功能。

Cyclone 系列FPGA 器件是用SRAM 单元配置数据的。

由于SRAM 掉电后容易丢失数据,配置数据必须即时地下载到上电的Cyclone 器件中。

CYCLONE II系列FPGA存储器模块○1CYCLONE II 系列FPGA支持的双口RAM 类型:●单端口RAM●简单双端口RAM●真双端口RAM【在QUARTUS II中的库模块是AltSYNCRam】●混合真双端口RAM【允许不同读写宽度】○2CYCLONE II 系列FPGA存储器模块M4K寄存器清零的三种方法:●使用【异步】清零信号aclr●上电复位器件●assert the device-wide reset signal using the DEV_CLRn option○3地址时钟使能应用于:●高速缓冲储存●地址使能默认为【低】电平●读地址时钟使能时:读地址锁存在使能时的地址上,读出的数据就是锁定的那个地址单元的数据。

如:读地址锁存在0x05地址,则读出的数据就是0x05地址里面的数据值。

●Figure 8–3 shows an address clock enable block diagram. The address register output is fedback to its input via a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal. Address latching is enabled when the addressstall signal goes high (active high). The output of the address register is then continuously fed into the input of the register until the addressstall signal goes low.●●●写地址时钟使能时:写入的数据依次写在锁定的地址上。

Altera Cyclone II FPGA的几种代码配置1、根据FPGA在配置电路中的角色,配置数据可以使用3种方式载入到目标器件中:(1) FPGA主动方式:由FPGA来主动输出控制和同步信号给FPGA的串行配置芯片(EPCS系列),配置芯片收到命令后,把配置数据发给FPGA,完成配置过程;在AS模式下,FPGA必须与AS串行配置芯片配合使用,它与FPGA的接口为四跟信号线,分别为:串行时钟输入(DCLK),AS控制信号输入 (ASDI),片选信号(nCS),串行数据输出(DATA)。

(2) FPGA被动方式:被动模式下,由系统的其他设备发起并控制配置过程,这些设备可以是配置芯片(EPC系列),或者单板的微处理器、CPLD等。

FPGA 在配置过程中完全处于被动地位,只是输出一些状态信号来配合配置过程;在PS模式下,需要配置时钟(DCLK),配置数据(DATA0),配置命令 (nCONFIG),状态信号(nSTATUS),配置完成指示(CONF_DONE)这四个信号来完成配置过程。

(3) JTAG模式:使用JTAG进行配置可以使用Altera的下载电缆,或者通过智能主机模拟JTAG的时序来进行配置;JTAG接口由四个必须的信号TDI、TDO、TMS 和TCK,以及一个可选的TRST构成。

2、若使用ByteBlasterII下载电缆,支持的配置方式有以下3种:AS方式:对AS配置芯片(ECPS系列)进行编程;PS方式:可以对FPGA进行配置;JTAG方式:可以对FPGA、CPLD以及Altera配置芯片(EPC系列)编程。

3、AS及PS模式下的注意事项PS模式:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序.只有在调试完成以后,才把程序烧在配置芯片中,然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种.这样出了问题还可以方便地调试.AS模式下: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS 方式需要电路上隔离。

Red Cyclone开发板RCII-CY1C6/12 用户手册 Ver 2.2修订历史版本 修订人 修订日期 修订内容0.1 红色飓风 2004年10月15日初始版本0.5 红色飓风 2004年10月17日建立基本框架,补充部分细节0.9 红色飓风 2004年11月02日基本完善1.1 红色飓风 2004年11月20日修订部分管脚2.1 红色飓风 2005年03月17日重新改版,增加了VGA,LCD,PS2和USB 2.1 红色飓风 2005年12月01日修改用户手册2.2 红色飓风 2008年11月修改用户手册目录RED CYCLONE (1)主开发板(RCM).................................................................................................................错误!未定义书签。

用户手册 VER 2.2.. (1)修订历史 (2)内容介绍:本手册包括以下章节 (5)CHAPTER 1主要器件及特性 (6)主要元器件介绍 (6)支持的功能扩展板 (8)开发板示意图 (8)CHAPTER 2 开关、按键与数码管 (9)拨码开关 (9)按键开关 (9)LED S (10)CHAPTER 3 VGA 接口 (12)CRT显示器的工作原理: (13)VGA信号的时序关系: (14)CHAPTER 4 PS/2 鼠标键盘接口 (16)键盘 (17)鼠标 (19)CHAPTER 5 RS-232 串口 (20)串行通信标准 (21)接收机设计 (23)发送机设计 (23)CHAPTER 6 字符型液晶显示器 (24)介绍 (24)FPGA控制原理 (26)CHAPTER 7 USB接口及芯片 (28)CHAPTER 8 用户自定义串行接口 (30)CHAPTER 9 高速异步SRAM (31)CHAPTER 10 高速同步SDRAM (33)CHAPTER 11大容量,快速FLASH (35)CHAPTER 12 扩展板接口 (37)扩展地址总线 (37)扩展数据总线 (38)扩展用户IO (39)说明 (40)CHAPTER 13 JTAG 下载与调试接口 (41)JTAG接口 (41)AS接口 (41)CHAPTER 14 电源分配 (42)CHAPTER 15 复位电路 (44)说明 (44)CHAPTER 16 时钟源 (45)EP1C6和EP1C12的区别 (47)附录A:原理图 (47)附录 B, 主要元件的相关材料 (47)内容介绍:本手册包括以下章节 • Chapter 1, “主要器件及特性”• Chapter 2, “开关、按键与数码管” • Chapter 3, “VGA 接口”• Chapter 4, “PS/2 鼠标/键盘接口” • Chapter 5, “RS-232 串口”• Chapter 6,“字符型液晶显示器接口”• Chapter 7,“USB2.0接口与芯片”Chapter 8,“用户自定义串行接口”• Chapter 9,“高速异步SRAM”• Chapter 10,“高速同步SDRAM”• Chapter 11,“大容量快速FLASH”• Chapter 12,“扩展板接口”• Chapter 13, “JTAG 下载与调试接口” • Chapter 14, “电源分配”• Chapter 15, “复位电路”• Chapter 16,“时钟源”•“EP1C6和EP1C12的区别”• 附录A, “电路板原理图”• 附录B, “主要元件的相关材料”Chapter 1主要器件及特性本手册中描述了Red Cyclone系列开发板的设计原理和使用方法,作为开发板的配套材料。