Simultaneous Absolute Timing of the Crab Pulsar at Radio and Optical Wavelengths

- 格式:pdf

- 大小:192.60 KB

- 文档页数:8

ONE、PLC overviewProgrammable controller is the first in the late 1960s in the United States, then called PLC programmable logic controller (Programmable Logic Controller) is used to replace relays. For the implementation of the logical judgment, timing, sequence number, and other control functions. The concept is presented PLC General Motors Corporation. PLC and the basic design is the computer functional improvements, flexible, generic and other advantages and relay control system simple and easy to operate, such as the advantages of cheap prices combined controller hardware is standard and overall. According to the practical application of target software in order to control the content of the user procedures memory controller, the controller and connecting the accused convenient target.In the mid-1970s, the PLC has been widely used as a central processing unit microprocessor, import export module and the external circuits are used, large-scale integrated circuits even when the PLC is no longer the only logical (IC) judgment functions also have data processing, PID conditioning and data communications functions. International Electro technical Commission (IEC) standards promulgated programmable controller for programmable controller draft made the following definition : programmable controller is a digital electronic computers operating system, specifically for applications in the industrial design environment. It used programmable memory, used to implement logic in their internal storage operations, sequence control, timing, counting and arithmetic operations, such as operating instructions, and through digital and analog input and output, the control of various types of machinery or production processes. Programmable controller and related peripherals, and industrial control systems easily linked to form a whole, to expand its functional design. Programmable controller for the user, is a non-contact equipment, the procedures can be changed to change production processes. The programmable controller has become a powerful tool for factory automation, widely popular replication. Programmable controller is user-oriented industries dedicatedcontrol computer, with many distinctive features.First, high reliability, anti-interference capability;Second programming visual, simple;Third, adaptability good;Fourth functional improvements, strong functional interface.TWO、History of PLCProgrammable Logic Controllers (PLC), a computing device invented by Richard E. Morley in 1968, have been widely used in industry including manufacturing systems, transportation systems, chemical process facilities, and many others. At that time, the PLC replaced the hardwired logic with soft-wired logic or so-called relay ladder logic (RLL), a programming language visually resembling the hardwired logic, and reduced thereby the configuration time from 6 months down to 6 days [Moody and Morley, 1999].Although PC based control has started to come into place, PLC based control will remain the technique to which the majority of industrial applications will adhere due to its higher performance, lower price, and superior reliability in harsh environments. Moreover, according to a study on the PLC market of Frost and Sullivan [1995], an increase of the annual sales volume to 15 million PLCs per year with the hardware value of more than 8 billion US dollars has been predicted, though the prices of computing hardware is steadily dropping. The inventor of the PLC, Richard E Morley, fairly considers the PLC market as a 5-billion industry at the present time.Though PLCs are widely used in industrial practice, the programming of PLC based control systems is still very much relying on trial-and-error. Alike software engineering, PLC software design is facing the software dilemma or crisis in a similar way. Morley himself emphasized this aspect most forcefully by indicating `If houses were built like software projects, a single woodpecker could destroy civilization.”Particularly, practical problems in PLC programming are to eliminate software bugs and to reduce the maintenance costs of old ladder logic programs. Thoughthe hardware costs of PLCs are dropping continuously, reducing the scan time of the ladder logic is still an issue in industry so that low-cost PLCs can be used.In general, the productivity in generating PLC is far behind compared to other domains, for instance, VLSI design, where efficient computer aided design tools are in practice. Existent software engineering methodologies are not necessarily applicable to the PLC based software design because PLC-programming requires a simultaneous consideration of hardware and software. The software design becomes, thereby, more and more the major cost driver. In many industrial design projects, more than of the manpower allocated for the control system design and installation is scheduled for testing and debugging PLC programs.In addition, current PLC based control systems are not properly designed to support the growing demand for flexibility and reconfigurability of manufacturing systems. A further problem, impelling the need for a systematic design methodology, is the increasing software complexity in large-scale projects.The objective of this thesis is to develop a systematic software design methodology for PLC operated automation systems. The design methodology involves high-level description based on state transition models that treat automation control systems as discrete event systems, a stepwise design process, and set of design rules providing guidance and measurements to achieve a successful design. The tangible outcome of this research is to find a way to reduce the uncertainty in managing the control software development process, that is, reducing programming and debugging time and their variation, increasing flexibility of the automation systems, and enabling software reusability through modularity. The goal is to overcome shortcomings of current programming strategies that are based on the experience of the individual software developer.Three、now of PLCFrom the structure is divided into fixed PLC and Module PLC, the two kinds of PLC including CPU board, I/O board, display panel, memory block, power, these elements into a do not remove overall. Module type PLC including CPU module,I/O modules, memory, the power modules, bottom or a frame, these modules can be according to certain rules combination configuration.In the user view, a detailed analysis of the CPU's internal unnecessary, but working mechanism of every part of the circuit. The CPU control works, by it reads CPU instruction, interprets the instruction and executes instructions. But the pace of work by shock signal control.Unit work under the controller command used in a digital or logic operation.In computing and storage register of computation result, it is also among the controller command and work. CPU speed and memory capacity is the important parameters for PLC , its determines the PLC speed of work, IO PLC number and software capacity, so limits to control size.Central Processing Unit (CPU) is the brain of a PLC controller. CPU itself is usually one of the microcontrollers. Aforetime these were 8-bit microcontrollers such as 8051, and now these are 16-and 32-bit microcontrollers. Unspoken rule is that you‟ll find mostly Hitachi and Fujicu microcontrollers in PLC controllers by Japanese makers, Siemens in European controllers, and Motorola microcontrollers in American ones. CPU also takes care of communication, interconnectedness among other parts of PLC controllers, program execution, memory operation, overseeing input and setting up of an output.System memory (today mostly implemented in FLASH technology) is used by a PLC for a process control system. Aside form. this operating system it also contains a user program translated forma ladder diagram to a binary form. FLASH memory contents can be changed only in case where user program is being changed. PLC controllers were used earlier instead of PLASH memory and have had EPROM memory instead of FLASH memory which had to be erased with UV lamp and programmed on programmers. With the use of FLASH technology this process was greatly shortened. Reprogramming a program memory is done through a serial cable in a program for application development.User memory is divided into blocks having special functions. Some parts of amemory are used for storing input and output status. The real status of an input is stored either as “1”or as “0”in a specific memory bit/ each input or output has one corresponding bit in memory. Other parts of memory are used to store variable contents for variables used in used program. For example, time value, or counter value would be stored in this part of the memory.PLC controller can be reprogrammed through a computer (usual way), but also through manual programmers (consoles). This practically means that each PLC controller can programmed through a computer if you have the software needed for programming. Today‟s transmission computers are ideal for reprogramming a PLC controller in factory itself. This is of great importance to industry. Once the system is corrected, it is also important to read the right program into a PLC again. It is also good to check from time to time whether program in a PLC has not changed. This helps to avoid hazardous situations in factory rooms (some automakers have established communication networks which regularly check programs in PLC controllers to ensure execution only of good programs). Almost every program for programming a PLC controller possesses various useful options such as: forced switching on and off of the system input/outputs (I/O lines), program follow up in real time as well as documenting a diagram. This documenting is necessary to understand and define failures and malfunctions. Programmer can add remarks, names of input or output devices, and comments that can be useful when finding errors, or with system maintenance. Adding comments and remarks enables any technician (and not just a person who developed the system) to understand a ladder diagram right away. Comments and remarks can even quote precisely part numbers if replacements would be needed. This would speed up a repair of any problems that come up due to bad parts. The old way was such that a person who developed a system had protection on the program, so nobody aside from this person could understand how it was done. Correctly documented ladder diagram allows any technician to understand thoroughly how system functions.Electrical supply is used in bringing electrical energy to central processing unit.Most PLC controllers work either at 24 VDC or 220 VAC. On some PLC controllers you‟ll find electrical supply as a separate module. Those are usually bigger PLC controllers, while small and medium series already contain the supply module. User has to determine how much current to take from I/O module to ensure that electrical supply provides appropriate amount of current. Different types of modules use different amounts of electrical current.This electrical supply is usually not used to start external input or output. User has to provide separate supplies in starting PLC controller inputs because then you can ensure so called “pure”supply for the PLC controller. With pure supply we mean supply where industrial environment can not affect it damagingly. Some of the smaller PLC controllers supply their inputs with voltage from a small supply source already incorporated into a PLC.Four、PLC design criteriaA systematic approach to designing PLC software can overcome deficiencies in the traditional way of programming manufacturing control systems, and can have wide ramifications in several industrial applications. Automation control systems are modeled by formal languages or, equivalently, by state machines. Formal representations provide a high-level description of the behavior of the system to be controlled. State machines can be analytically evaluated as to whether or not they meet the desired goals. Secondly, a state machine description provides a structured representation to convey the logical requirements and constraints such as detailed safety rules. Thirdly, well-defined control systems design outcomes are conducive to automatic code generation-An ability to produce control software executable on commercial distinct logic controllers can reduce programming lead-time and labor cost. In particular, the thesis is relevant with respect to the following aspects.In modern manufacturing, systems are characterized by product and process innovation, become customer-driven and thus have to respond quickly to changing system requirements. A major challenge is therefore to provide enabling technologies that can economically reconfigure automation controlsystems in response to changing needs and new opportunities. Design and operational knowledge can be reused in real-time, therefore, giving a significant competitive edge in industrial practice.Studies have shown that programming methodologies in automation systems have not been able to match rapid increase in use of computing resources. For instance, the programming of PLCs still relies on a conventional programming style with ladder logic diagrams. As a result, the delays and resources in programming are a major stumbling stone for the progress of manufacturing industry. Testing and debugging may consume over 50% of the manpower allocated for the PLC program design. Standards [IEC 60848, 1999; IEC-61131-3, 1993; IEC 61499, 1998; ISO 15745-1, 1999] have been formed to fix and disseminate state-of-the-art design methods, but they normally cannot participate in advancing the knowledge of efficient program and system design.A systematic approach will increase the level of design automation through reusing existing software components, and will provide methods to make large-scale system design manageable. Likewise, it will improve software quality and reliability and will be relevant to systems high security standards, especially those having hazardous impact on the environment such as airport control, and public railroads.The software industry is regarded as a performance destructor and complexity generator. Steadily shrinking hardware prices spoils the need for software performance in terms of code optimization and efficiency. The result is that massive and less efficient software code on one hand outpaces the gains in hardware performance on the other hand. Secondly, software proliferates into complexity of unmanageable dimensions; software redesign and maintenance-essential in modern automation systems-becomes nearly impossible. Particularly, PLC programs have evolved from a couple lines of code 25 years ago to thousands of lines of code with a similar number of 1/O points. Increased safety, for instance new policies on fire protection, and the flexibility of modern automation systems add complexity to the program design process.Consequently, the life-cycle cost of software is a permanently growing fraction of the total cost. 80-90% of these costs are going into software maintenance, debugging, adaptation and expansion to meet changing needs.Today, the primary focus of most design research is based on mechanical or electrical products. One of the by-products of this proposed research is to enhance our fundamental understanding of design theory and methodology by extending it to the field of engineering systems design. A system design theory for large-scale and complex system is not yet fully developed. Particularly, the question of how to simplify a complicated or complex design task has not been tackled in a scientific way. Furthermore, building a bridge between design theory and the latest epistemological outcomes of formal representations in computer sciences and operations research, such as discrete event system modeling, can advance future development in engineering design.From a logical perspective, PLC software design is similar to the hardware design of integrated circuits. Modern VLSI designs are extremely complex with several million parts and a product development time of 3 years [Whitney, 1996]. The design process is normally separated into a component design and a system design stage. At component design stage, single functions are designed and verified. At system design stage, components are aggregated and the whole system behavior and functionality is tested through simulation. In general, a complete verification is impossible. Hence, a systematic approach as exemplified for the PLC program design may impact the logical hardware design.Five、AK 1703 ACPFollowing the principle of our product development, AK 1703 ACP has high functionality and flexibility, through the implementation of innovative and reliable technologies, on the stable basis of a reliable product platform.For this, the system concept ACP (Automation, Control and Protection) creates the technological preconditions. Balanced functionality permits the flexible combination of automation, telecontrol and communication tasks. Complemented with the scalable performance and various redundancyconfigurations, an optimal adaptation to the respective requirements of the process is achieved.AK 1703 ACP is thus perfectly suitable for automation with integrated telecontrol technology as:•Telecontrol substation or central device•Automation unit with autonomous functional groups•Data node, station control device, front-end or gateway•With local or remote peripherals•For rear panel installation or 19 inch assembly•Branch-neutral product, therefore versatile fields of application and high productstability•Versatile communication•Easy engineering•Plug & play for spare parts•Open system architecture•Scalable redundancy•The intelligent terminal - TM 1703The Base Unit AK 1703 ACP with Peripheral Elements has one basic system element CP-2010/CPC25 (Master control element) and CP-2012/PCCE25 (Processing and communication element) ,one bus line with max. 16 peripheral elements can be connected.CP-2010/CPC25 Features and FunctionsSystem Functions:•Central element,coordinating all system servicesCentral hub function for all connected basic system elements•Time managementCentral clock of the automation unitSetting and keeping the own clock`s time with a resolution of 10ms Synchronization via serid communication via LAN or local•RedundancyVoting and change-over for redundant processing and communication elements of the own automation unitSupports voting and change-over by an external SCA-RS redundancy switch Supports applicational voting and change-over by an external system,e.g.a control system•SAT TOLLBOX|| connectionStoring firmware and parameters on a Flash CardCommunication:•Communication via installable protocol elements to any superior or subordinate automation unit•Automatic data flow routing•Priority based data transmission (priority control)•Own circular buffer and process image for each connected station(data keeping)•Redundant communication routesCommunication with redundant remote stations•Special application specific functions for dial-up trafficTest if stations are reachableProcess Peripherals:•Transmission of spontaneous information objects from and to peripheral elements, via the serial Ax 1703 peripheral busFunctions for Automation:•Open-/closed-loop control function for the execution of freely definable user programs which are created with CAEX plus according to IEC 61131-3,ing function diagram technology 512KB for user programApprox 50.000 variables and signals,2.000 of them retainedCycle of 10ms or a multiple thereofOnline testLoadable without service interruption•Redundant open-/closed-loop control functionsSynchronization via redundancy linkTransmission of periodic process information between the open-/closed-loop control function and the peripheral elements,via the serial Ax 1703 peripheral bus.Six、SIEMENS PLCSIMATIC S7-300 series PLC applied to all walks of life and various occasions in the detection, monitoring and control of automation, its power to both the independent operation of, or connected to a network able to achieve complex control.The photoelectric products with isolation, high electromagnetic compatibility; have high industrial applicability, allowing the ambient temperature of 60 ℃; has strong anti-jamming and anti-vibration and impact resistance, so in a harsh working environment has been widely Applications.I also mean freedom of communication S7-300 type PLC' s a very unique feature, which allows S7-300-PLC can deal openly with any other communications equipment, communications controller, or PLC S7-300 type can be defined by the user's own Communications protocol (of the agreement ASCII), the baud rate to 1.5 Mbit / s (adjustable). So that can greatly increase the scope of communications so that the control system configuration more flexible and convenient. Of any kind with a serial interface peripherals, such as: printers or bar code readers, Drives, a modem (Modem), the top PC-connected, and so can be used. Users can program to develop communication protocols, the exchange of data (for example: ASCII character code), RS232 interfaces with the equipment can also be used PC / PPI cable linking the free communication communications. When the PC offline, under the control of the next crew, the whole system can operate normally.PC that is by control centre, mainly by the PC and laser printer components, using SIMATIC WINCC software platform, the all-Chinese interface, friendly man-machine dialogue. Managers and operators can be observed through a PC,shown in the various kinds of information to understand the present and pion tasks.WINCC and the ice-storage operation of the automatic control system and all the parameters, and through the mouse to print equipment management and implement at software in the field of automation can be used for all the operators‟control and monitoring tasks. Can be controlled in the process of the events clearly show, and shows the current status and order records, the recorded data can show all or select summary form, or may be required for editing, printing and output statements and trends .WINCC able to control the critical situation in the early stages of the report, and the signal can be displayed on the screen, can also use sound to be felt. It supported by online help and operational guidelines to eliminate failure. WINCC a workstation can be devoted to the process control to the process so that important information not is shielded. Software-assisted operation strategy ensures that the process was not illegal to visit and to provide for non-industrial environment in the wrong operation.WINCC is MICRSOFT WINDOWS98 or WINDOWS NT4.0 operating system,running on a PC object-oriented class 32-bit applications, OLE through the window and ODBC standard mechanism, as an ideal partner to enter the communications world WINDOWS, it can be easily WINCC To integrate a company-wide data processing system.Seven、CommunicationsCommunications are vital to an individual automation cell and to the automated factory as a whole. We've heard a lot about MAP in the last few years, and a lot of companies have jumped on the band wagon. Many, however were disappointed when a fully-defined and completed MAP specification didn’t appear immediately. Says Larry Kumara:”Right now , MAP is still a moving target for the manufacturers specification that is not final. Presently, for example, people are introducing products to meet the MAP 2.1standard.Yet 2.1-basedproducts will be obsolete when the new standard for MAP,3.0 is introduced.”Because of this, many PLC vendors are holding off on full MAP implementations. Omron, for example has an ongoing MAP-compatibility program, but Frank Newborn, vice president of Omron‟s Industrial Division, reports that because of the lack of a firm definition, Omron's PLCs don't yet talk to MAP.Since it‟s unlikely that an individual PLC would talk to broadband MAP anyway, makers are concentrating n proprietary networks. According to Sal Provanzano, users fear that if they do get on board and vendors withdraw from MAP, they’ll pulse width modulation control system be the ones left holding a communications structure that‟s not supported.。

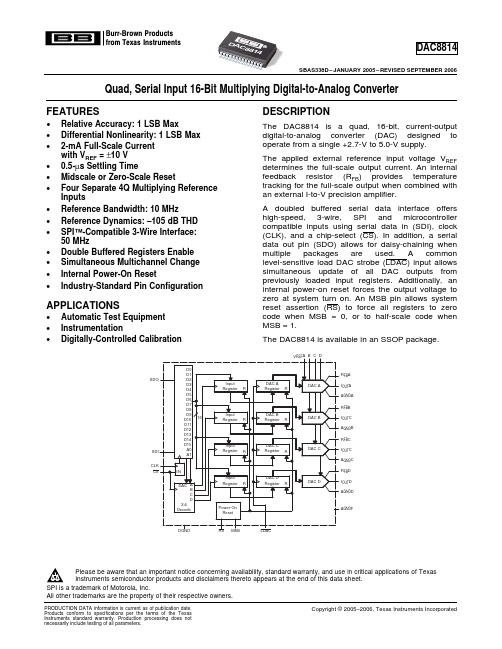

BurrĆBrown Productsfrom TexasInstrumentsFEATURES DESCRIPTIONAPPLICATIONSA GND FA GND DI OUT DR FB DA GND CI OUT CR FB CA GND BI OUT CR FB BA GND AI OUT AR FB ADAC8814SBAS338D–JANUARY2005–REVISED SEPTEMBER2006 Quad,Serial Input16-Bit Multiplying Digital-to-Analog Converter•Relative Accuracy:1LSB Max The DAC8814is a quad,16-bit,current-output •Differential Nonlinearity:1LSB Max digital-to-analog converter(DAC)designed tooperate from a single+2.7-V to5.0-V supply.•2-mA Full-Scale Currentwith V REF=±10V The applied external reference input voltage VREF •0.5-µs Settling Time determines the full-scale output current.An internalfeedback resistor(R FB)provides temperature •Midscale or Zero-Scale Resettracking for the full-scale output when combined with •Four Separate4Q Multiplying Referencean external I-to-V precision amplifier.InputsA doubled buffered serial data interface offers •Reference Bandwidth:10MHzhigh-speed,3-wire,SPI and microcontroller •Reference Dynamics:–105dB THDcompatible inputs using serial data in(SDI),clock •SPI™-Compatible3-Wire Interface:(CLK),and a chip-select(CS).In addition,a serial 50MHz data out pin(SDO)allows for daisy-chaining when •Double Buffered Registers Enable multiple packages are used.A commonlevel-sensitive load DAC strobe(LDAC)input allows •Simultaneous Multichannel Changesimultaneous update of all DAC outputs from •Internal Power-On Resetpreviously loaded input registers.Additionally,an •Industry-Standard Pin Configuration internal power-on reset forces the output voltage tozero at system turn on.An MSB pin allows systemreset assertion(RS)to force all registers to zerocode when MSB=0,or to half-scale code when •Automatic Test EquipmentMSB=1.•Instrumentation•Digitally-Controlled Calibration The DAC8814is available in an SSOP package.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.SPI is a trademark of Motorola,Inc.All other trademarks are the property of their respective owners.PRODUCTION DATA information is current as of publication date.Copyright©2005–2006,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.ABSOLUTE MAXIMUM RATINGS (1)DAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PACKAGE/ORDERING INFORMATION (1)MINIMUM RELATIVE DIFFERENTIAL SPECIFIED TRANSPORT ACCURACYNONLINEARITYTEMPERATUREPACKAGE-PACKAGE ORDERING MEDIA,PRODUCT (LSB)(LSB)RANGE LEAD DESIGNATORNUMBER QUANTITY DAC8814ICDBT Tape and Reel,250DAC8814C ±1±1–40°C to +85°C SSOP-28DB DAC8814ICDBR Tape and Reel,2500DAC8814IBDBT Tape and Reel,250DAC8814B±4±1.5–40°C to +85°CSSOP-28DBDAC8814IBDBRTape and Reel,2500(1)For the most current specifications and package information,see the Package Option Addendum located at the end of this document,or see the TI website at .DAC8814UNIT V DD to GND –0.3to +8V V REF to GND–18to +18V Logic inputs and output to GND –0.3to +8V V(I OUT )to GND –0.3to V DD +0.3V A GND X to DGND–0.3to +0.3V Input current to any pin except supplies ±50mA Package power dissipation (T J max –T A )/θJAW Thermal resistance,θJA28-Lead shrink surface-mount (RS-28)100°C/W Maximum junction temperature (T J max)150°C Operating temperature range,Model A –40to +85°C Storage temperature range –65to +150°C ESD rating,HBM 3000V ESD rating,CDM 500V(1)Stresses above those listed under absolute maximum ratings may cause permanent damage to the device.This is a stress rating only;functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.Exposure to absolute maximum conditions for extended periods may affect device reliability.2Submit Documentation FeedbackELECTRICAL CHARACTERISTICSDAC8814 SBAS338D–JANUARY2005–REVISED SEPTEMBER2006V DD =2.7V to5.5V;IOUTX=Virtual GND,AGNDX=0V,VREFA,B,C,D=10V,TA=full operating temperature range,unlessotherwise noted.DAC8814 PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNIT STATIC PERFORMANCE(1)Resolution16Bits Relative accuracy INL DAC8814B±4LSBINL DAC8814C±1LSB Differential nonlinearity DNL DAC8814B±1.5LSBDNL DAC8814C±1LSB Output leakage current I OUT X Data=0000h,T A=25°C10nAI OUT X Data=0000h,T A=T A max20nAFull-scale gain error G FSE Data=FFFFh±0.75±3mVFull-scale tempco(2)TCV FS1ppm/°C Feedback resistor R FB X V DD=5V5kΩREFERENCE INPUTV REF X Range V REF X–1515VInput resistance R REF X456kΩInput resistance match R REF X Channel-to-channel1% Input capacitance(2)C REF X5pF ANALOG OUTPUTOutput current I OUT X Data=FFFFh 1.6 2.5mA Output capacitance(2)C OUT X Code-dependent50pF LOGIC INPUTS AND OUTPUTInput low voltage V IL V DD=+2.7V0.6VV IL V DD=+5V0.8VInput high voltage V IH V DD=+2.7V 2.1VV IH V DD=+5V 2.4VInput leakage current I IL1µA Input capacitance(2)C IL10pF Logic output low voltage V OL I OL=1.6mA0.4V Logic output high voltage V OH I OH=100µA4V INTERFACE TIMING(2),(3)Clock input frequency f CLK50MHz Clock width high t CH10ns Clock width low t CL10nsCS to Clock setup t CSS0ns Clock to CS hold t CSH10ns Clock to SDO prop delay t PD220ns Load DAC pulsewidth t LDAC25ns Data setup t DS5ns Data hold t DH10ns Load setup t LDS5ns Load hold t LDH10ns (1)All static performance tests(except I OUT)are performed in a closed-loop system using an external precision OPA277I-to-V converteramplifier.The DAC8814R FB terminal is tied to the amplifier output.Typical values represent average readings measured at+25°C.(2)These parameters are specified by design and not subject to production testing.(3)All input control signals are specified with t R=t F=2.5ns(10%to90%of3V)and timed from a voltage level of1.5V.3Submit Documentation FeedbackDAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006ELECTRICAL CHARACTERISTICS (continued)V DD =2.7V to 5.5V;I OUT X =Virtual GND,A GND X =0V,V REF A,B,C,D =10V,T A =full operating temperature range,unless otherwise noted.DAC8814PARAMETERSYMBOL CONDITIONS MIN TYP MAX UNIT SUPPLY CHARACTERISTICS Power supply range V DDRANGE2.75.5V Logic inputs =0V,Positive supply currentI DD 25µA V DD =+4.5V to +5.5V Logic inputs =0V,I DD12.5µA V DD =+2.7V to +3.6V Power dissipation P DISS Logic inputs =0V 0.0275mW Power supply sensitivity P SS∆V DD =±5%0.006%AC CHARACTERISTICS (4)To ±0.1%of full-scale,Output voltage settling timet s 0.3µs Data =0000h to FFFFh to 0000h To ±0.0015%of full-scale,t s0.5µs Data =0000h to FFFFh to 0000hReference multiplying BW BW –3dBV REF X =100mV RMS ,Data =FFFFh,C FB =3pF 10MHz DAC glitch impulse QV REF X =10V,Data =7FFFh to 8000h to 7FFFh 5nV-s Feedthrough error V OUT X/V REF X Data =0000h,V REF X =100mV RMS ,f =100kHz–70dB Data =0000h,V REF B =100mV RMS ,Crosstalk error V OUT A/V REF B–100dB Adjacent channel,f =100kHzDigital feedthrough Q CS =1and f CLK =1MHz1nV-s Total harmonic distortion THD V REF =5V PP ,Data =FFFFh,f =1kHz–105dB Output spot noise voltage e nf =1kHz,BW =1Hz12nV/√Hz(4)All ac characteristic tests are performed in a closed-loop system using a THS4011I-to-V converter amplifier.4Submit Documentation FeedbackPIN CONFIGURATIONSA GND I OUT V REF R FB RS V DD CS R FB V REF I OUT A GND A GND D I OUT D V REF D R FB D DGND V SS (1)A GND F LDAC SDO NC (1)R FB C V REF C I OUT C A GND CDB Package (TOP VIEW)NOTE (1): No internal connectionDAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006PIN DESCRIPTION5Submit Documentation FeedbackTYPICAL CHARACTERISTICS:V DD =+5VChannel A819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0DAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 1.Figure 2.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 3.Figure 4.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 5.Figure 6.6Submit Documentation FeedbackChannel B819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0DAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006TYPICAL CHARACTERISTICS:V DD =+5V (continued)At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 7.Figure 8.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 9.Figure 10.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 11.Figure 12.7Submit Documentation FeedbackChannel C1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0DAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006TYPICAL CHARACTERISTICS:V DD =+5V (continued)At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 13.Figure 14.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 15.Figure 16.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 17.Figure 18.8Submit Documentation FeedbackChannel D819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0DAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006TYPICAL CHARACTERISTICS:V DD =+5V (continued)At T A =+25°C,+V DD =+5V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 19.Figure 20.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 21.Figure 22.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 23.Figure 24.9Submit Documentation Feedback18016014012010080604020000.51.01.52.02.53.03.54.04.55.0S u p p l y C u r r e n t ,I D D (µA )Logic Input Voltage (V)−−−−−−−−−−−−−−−−−−A Digital Codet t e n u a t i o n (d B )B andw idth (H z)Time (0.2µs/div)O u t p u t V o l t a g e (50m V /d i v )Time (0.1µs/div)O u t p u t V o l t a g e (5V /d i v )3210−1−2−3−40−20100E n d p o i n t E r r o r (m V )Temperature (_C)204060805.04.54.03.53.02.52.01.51.00.50Temperature (_C)−2020I D D (µA )5.0V2.7V 406080100−40DAC8814SBAS338D–JANUARY 2005–REVISED SEPTEMBER 2006TYPICAL CHARACTERISTICS:V DD =+5V (continued)At T A =+25°C,+V DD =+5V,unless otherwise noted.SUPPLY CURRENT vs LOGIC INPUT VOLTAGEREFERENCE MULTIPLYING BANDWIDTHFigure 25.Figure 26.DAC GLITCHDAC SETTLING TIMEFigure 27.Figure 28.I DD vs TEMPERATUREENDPOINT ERROR vs TEMPERATUREFigure 29.Figure 30.10Submit Documentation FeedbackTYPICAL CHARACTERISTICS:V DD =+2.7VChannel A819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0At T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 31.Figure 32.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 33.Figure 34.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 35.Figure 36.Channel B819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.01.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code819216384245763276840960491525734465535I N L (L S B )Digital InputCode 1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0DD At T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 37.Figure 38.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 39.Figure 40.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 41.Figure 42.Channel C819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0DD At T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 43.Figure 44.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 45.Figure 46.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 47.Figure 48.Channel D819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital InputCode1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535I N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0819216384245763276840960491525734465535D N L (L S B )Digital Input Code1.00.80.60.40.20−0.2−0.4−0.6−0.8−1.0DD At T A =+25°C,+V DD =+2.7V,unless otherwise noted.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 49.Figure 50.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 51.Figure 52.LINEARITY ERROR DIFFERENTIAL LINEARITY ERRORvs DIGITAL INPUT CODEvs DIGITAL INPUT CODEFigure 53.Figure 54.Time (0.2µs/div)O u t p u t V o l t a g e (50m V /d i v )3210−1−2−3−40−20100E n d p o i n t E r r o r (m V )Temperature (_C)20406080TIMING INFORMATIONSDICLKCSLDACDD At T A =+25°C,+V DD =+2.7V,unless otherwise noted.DAC GLITCHENDPOINT ERROR vs TEMPERATUREFigure 55.Figure 56.Figure 57.DAC8814Timing DiagramTHEORY OF OPERATIONCIRCUIT OPERATIOND/A ConverterV OUT +*V REFD65536(1)Digital interface connections omitted for clarity.Switches S1 and S2 are closed. V must be powered.DD DGNDV REF XFB XOUT X DD GND F GND XThe DAC8814contains four,16-bit,current-output,digital-to-analog converters (DACs)respectively.Each DAC has its own independent multiplying reference input.The DAC8814uses a 3-wire SPI-compatible serial data interface,with a configurable asynchronous RS pin for half-scale (MSB =1)or zero-scale (MSB =0)preset.In addition,an LDAC strobe enables four channel simultaneous updates for hardware-synchronized output voltage changes.The DAC8814contains four current-steering R-2R ladder DACs.Figure 58shows a typical equivalent DAC.Each DAC contains a matching feedback resistor for use with an external I-to-V converter amplifier.The R FB X pin is connected to the output of the external amplifier.The I OUT X terminal is connected to the inverting input of the external amplifier.The A GND X pin should be Kelvin-connected to the load point in the circuit requiring the full 16-bit accuracy.The DAC is designed to operate with both negative or positive reference voltages.The V DD power pin is only used by the logic to drive the DAC switches on and off.Note that a matching switch is used in series with the internal 5k Ωfeedback resistor.If users are attempting to measure the value of R FB ,power must be applied to V DD in order to achieve continuity.The DAC output voltage is determined by V REF and the digital data (D)according to Equation 1:Note that the output polarity is opposite of the V REF polarity for dc reference voltages.Figure 58.Typical Equivalent DAC ChannelThe DAC is also designed to accommodate ac reference input signals.The DAC8814accommodates input reference voltages in the range of –15V to +15V.The reference voltage inputs exhibit a constant nominal input resistance of 5k Ω,±20%.On the other hand,the DAC outputs I OUT A,B,C,D are code-dependent and produce various output resistances and capacitances.The choice of external amplifier should take into account the variation in impedance generated by the DAC8814on the amplifiers'inverting input node.The feedback resistance,in parallel with the DAC ladder resistance,dominates output voltage noise.For multiplying mode applications,an external feedback compensation capacitor (C FB )may be needed to provide a critically damped output response for step changes in reference input voltages.V REF XFigure 26shows the gain versus frequency performance at various attenuation settings using a 3pF external feedback capacitor connected across the I OUT X and R FB X terminals.In order to maintain good analog performance,power supply bypassing of 0.01µF,in parallel with 1µF,is recommended.Under these conditions,a clean power-supply with low ripple voltage capability should be used.Switching power supplies are usually not suitable for this application because of the higher ripple voltage and P SS frequency-dependent characteristics.It is best to derive the DAC88145-V supply from the system analog supply voltages.(Do not use the digital 5-V supply.)See Figure 59.Figure 59.Recommended Kelvin-Sensed HookupA GND FA GND DI OUT D R FB DA GND CI OUT C R FB CGND BI OUT C R FB BA GND AI OUT A R FB AV DD SERIAL DATA INTERFACEFigure 60.System Level Digital InterfacingThe DAC8814uses a 3-wire (CS,SDI,CLK)SPI-compatible serial data interface.Serial data of the DAC8814is clocked into the serial input register in an 18-bit data-word format.MSB bits are loaded first.Table 2defines the 18data-word bits for the DAC8814.Data is placed on the SDI pin,and clocked into the register on the positive clock edge of CLK subject to the data setup and data hold time requirements specified in the Interface Timing Specifications.Data can only be clocked in while the CS chip select pin is active low.For the DAC8814,only the last 18bits clocked into the serial register are interrogated when the CS pin returns to the logic high state.Since most microcontrollers output serial data in 8-bit bytes,three right-justified data bytes can be written to the DAC8814.Keeping the CS line low between the first,second,and third byte transfers results in a successful serial register update.Once the data is properly aligned in the shift register,the positive edge of the CS initiates the transfer of new data to the target DAC register,determined by the decoding of address bits A1and A0.For the DAC8814,Table 1,Table 2,Table 3and Figure 57define the characteristics of the software serial interface.Figure 61shows the equivalent logic interface for the key digital control pins for the DAC8814.POWER ON RESETESD Protection CircuitsV DDDGNDDigital InputsFigure 61.DAC8814Equivalent Logic InterfaceTwo additional pins RS and MSB provide hardware control over the preset function and DAC register loading.If these functions are not needed,the RS pin can be tied to logic high.The asynchronous input RS pin forces all input and DAC registers to either the zero-code state (MSB =0),or the half-scale state (MSB =1).When the V DD power supply is turned on,an internal reset strobe forces all the Input and DAC registers to the zero-code state or half-scale,depending on the MSB pin voltage.The V DD power supply should have a smooth positive ramp without drooping in order to have consistent results,especially in the region of V DD =1.5V to 2.3V.The DAC register data stays at zero or half-scale setting until a valid serial register data load takes place.All logic-input pins contain back-biased ESD protection zener diodes connected to ground (DGND)and V DD as shown in Figure 62.Figure 62.Equivalent ESD Protection CircuitsPCB LAYOUTThe DAC8814is a high-accuracy DAC that can have its performance compromised by grounding and printed circuit board(PCB)lead trace resistance.The16-bit DAC8814with a10-V full-scale range has an LSB value of 153µV.The ladder and associated reference and analog ground currents for a given channel can be as high as 2mA.With this2mA current level,a series wiring and connector resistance of only76mΩwill cause1LSB of voltage drop.The preferred PCB layout for the DAC8814is to have all A GND X pins connected directly to an analog ground plane at the unit.The non-inverting input of each channel I/V converter should also either connect directly to the analog ground plane or have an individual sense trace back to the A GND X pin connection.The feedback resistor trace to the I/V converter should also be kept short and have low resistance in order to prevent IR drops from contributing to gain error.This attention to wiring ensures the optimal performance of the DAC8814.Table1.Control Logic Truth Table(1)CS CLK LDAC RS MSB SERIAL SHIFT REGISTER INPUT REGISTER DAC REGISTERH X H H X No effect Latched LatchedL L H H X No effect Latched LatchedL↑+H H X Shift register data advanced one bit Latched LatchedL H H H X No effect Latched LatchedSelected DAC updated↑+L H H X No effect Latchedwith current SR contentsH X L H X No effect Latched TransparentH X H H X No effect Latched LatchedH X↑+H X No effect Latched LatchedH X H L0No effect Latched data=0000h Latched data=0000hH X H L H No effect Latched data=8000h Latched data=8000h(1)↑+=Positive logic transition;X=Do not careTable2.Serial Input Register Data Format,Data Loaded MSB First(1)B17B0 Bit(MSB)B16B15B14B13B12B11B10B9B8B7B6B5B4B3B2B1(LSB) Data A1A0D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0 (1)Only the last18bits of data clocked into the serial register(address+data)are inspected when the CS line positive edge returns tologic high.At this point an internally-generated load strobe transfers the serial register data contents(bits D15-D0)to the decoded DAC-input-register address determined by bits A1and A0.Any extra bits clocked into the DAC8814shift register are ignored;only the last18bits clocked in are used.If double-buffered data is not needed,the LDAC pin can be tied logic low to disable the DAC registers.Table3.Address DecodeA1A0DAC DECODE00DAC A01DAC B10DAC C11DAC D。

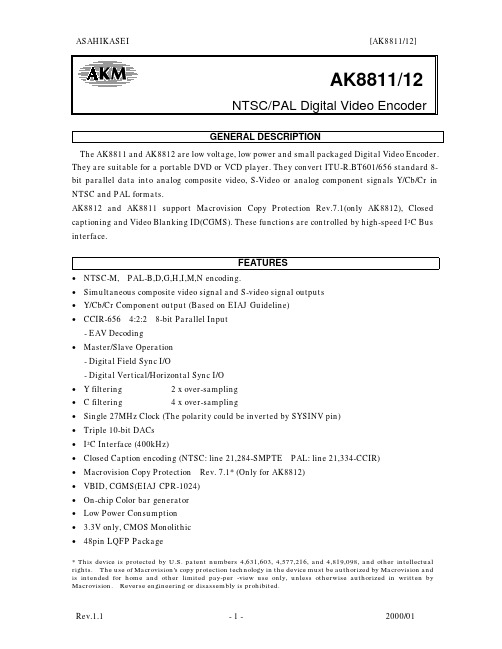

ASAHIKASEI [AK8811/12]AK8811/12NTSC/PAL Digital Video EncoderGENERAL DESCRIPTIONThe AK8811 and AK8812 are low voltage, low power and small packaged Digital Video Encoder. They are suitable for a portable DVD or VCD player. They convert ITU-R.BT601/656 standard 8-bit parallel data into analog composite video, S-Video or analog component signals Y/Cb/Cr in NTSC and PAL formats.AK8812 and AK8811 support Macrovision Copy Protection Rev.7.1(only AK8812), Closed captioning and Video Blanking ID(CGMS). These functions are controlled by high-speed I2C Bus interface.FEATURES• NTSC-M, PAL-B,D,G,H,I,M,N encoding.•Simultaneous composite video signal and S-video signal outputs•Y/Cb/Cr Component output (Based on EIAJ Guideline)• CCIR-656 4:2:2 8-bit Parallel Input- EAV Decoding• Master/Slave Operation- Digital Field Sync I/O- Digital Vertical/Horizontal Sync I/O•Y filtering 2 x over-sampling• C filtering 4 x over-sampling•Single 27MHz Clock (The polarity could be inverted by SYSINV pin)• Triple 10-bit DACs•I2C Interface (400kHz)•Closed Caption encoding (NTSC: line 21,284-SMPTE PAL: line 21,334-CCIR)•Macrovision Copy Protection Rev. 7.1* (Only for AK8812)• VBID, CGMS(EIAJ CPR-1024)•On-chip Color bar generator• Low Power Consumption• 3.3V only, CMOS Monolithic• 48pin LQFP Package* This device is protected by U.S. patent numbers 4,631,603, 4,577,216, and 4,819,098, and other intellectual rights. The use of Macrovision’s copy protection technology in the device must be authorized by Macrovision and is intended for home and other limited pay-per -view use only, unless otherwise authorized in written by Macrovision. Reverse engineering or disassembly is prohibited.PIN LAYOUT48pin LQFP48 47 46 45 44 43 42 41 40 39 38 3712345678910111213 14 15 16 17 18 19 20 21 22 23 24PD9D7D6D5D4DVDD DVSS D3D2D1D0TEST1363534333231302928272625PD4PD3PD2PD1PD0DVDD DVSS IREF VREFIN VREFOUT AVDD AVSSFID/VSYNCSYSINVDVSSHSYNC DVDDPD8DVDDSYSCLKDVSSPD7PD6PD5TEST2SELASCLSDADVSS/RESETAVSSYAVDDCHROMA / VAVSSCOMPOSITE / UAK8811/12PIN/FUNCTION No.Pin Name I/O Description2-5, 8-11D7 - D0I27MHz 8-Bit 4:2:2 multiplexed Y,Cb,Cr Data Input.For Rec.656 format, AK8811/12 decodes EAV.For non-Rec.656 format (without EAV), AK8811/12operates in Master or Slave mode.41SYSCLK I27MHz Clock Input. The polarity could be inverted by SYSINV.48SYSINV I“L “ : data is latched with rising edge.“H” : data is latched with falling edge.18/RESET I After this pin becomes “L”, AK8811/12 starts theinternal initializing sequence.After initializing sequence, AK8811/12 is set NTSC mode, Rec.656 decoding mode. All DACs Off condition.45FID/VSYNCI/O Either of FID or VSYNC selected by the register.Rec.656 decode mode :OutputMaster mode : OutputSlave mode : InputFID shows that “L” is odd field and ”H” is even field.46HSYNC I/O Rec.656 decode mode : Output Master mode : OutputSlave mode : Input15SCL I Serial interface clock 16SDA I/O Serial interface data14SELA I The slave address is set with this pin.“L”:40H “H”:42H27VREFOUT O Output of the Internal Vref. Terminate with 0.1uF or more capacitor.28VREFIN I Input of the Reference Voltage29IREF O The currents flow this pin adjusts the full-scale output current of the DAC.24COMPOSITE/U O Output of Composite Video signal or component U 22CHROMA/V O Output of the C signal or component V20Y O Output of Luminance Signal.21,26AVDD P Analog +3.3V6,31,42,44DVDD P Digital +3.3V19,23,25AVSS G Analog Ground7,17,47,40,30DVSS G Digital Ground12,13TEST1TEST2I Test pin. Ground for normal operation1, 32-39,43PD[9:0]I/O Test pin. Open for normal operationELECTRICAL CHARACTERISTICSAbsolute Maximum RatingsParameter Min Max Units-0.3 4.6V V Supply Voltage (VDD)DVDD, PVDD, AVDDInput Pin Voltage (Vin)-0.3VDD+0.3V Input Pin Current (Iin)-±10mA Analog Reference Current (IREF)-0.21mA Analog Output Current- 6.5mA Power Dissipation1000mW Storage Temperature-40125°C (Note)When all Ground pins(DVSS, AVSS) are set to 0V.Recommended Operating ConditionsParameter Min Typ.Max Units Supply Voltage (VDD) 3.0 3.3 3.6V Operating Temperature-4085°CDC Characteristics[Power Supply:3.3V Temperature:25°C] Parameter Symbol Min Max Units ConditionsDigital Input High Voltage VIH10.7VDD V Note1)Digital Input Low Voltage VIL10.3VDD V Note1)Digital Input leak Current IL±10uA Note1)Digital Output High Voltage VOH 2.4V IOH =-1mA Note 2) Digital Output Low Voltage VOL10.4V IOL = 2mA Note 2)Digital Maximum Load20pFCapacitanceI2C Input High VoltageI2C(SDA,SCL)VIH20.7VDD VI2C Input Low VoltageI2C(SDA,SCL)VIL20.3VDD VI2C(SDA) Output Voltage VOL20.4V IOL = 3mANote 1) D[9:0],FID/VSYNC, HSYNC, SYSCLK, /RESET pinNote 2) FID/VSYNC, HSYNC pinNote ) Connected Test Pin to Ground, SELA and SYSINV Pin are desired polarity.Analog Characteristics and Dissipation Current[Power Supply:3.3V Temperature:25°C] Parameter Min Typ Max Units ConditionsDAC Resolution10bitDAC Integral linearity error±0.6±2LSBDAC Differential linearity error±0.4±1LSBDAC Output Full Scale Voltage 1.21 1.28 1.38V Note1)DAC Output offset Voltage 5.0mV Note2) Unbalances between DACs±1±5%Note3)Isolation between DACs50dB1MHz Full ScaleDAC Load Capacitance30pF Note4)Internal Reference Voltage 1.17 1.235 1.33VInternal Reference Drift50ppm/°CDAC Current (Active mode)15mA Note5)DAC Current (Sleep mode)10uA Note6)Total Current5072mA Note7)Note 1) Under the condition of output load 390Ω, IREF pin with 12kΩ, using internal reference. The output full-scale current IOUT is calculated as Full scale output voltage (typ. 1.28V) /390Ω=typ. 3.3mA.Note 2) DAC output when feeding code of 0 (Decimal).Note 3) Deviation between the DAC output when feeding 1V generating code of 800(Decimal).Note 4) The value is a design target. This value is not tested.Note 5) All DACs are operating.Note 6) All DACs are turned off with no system clock.Note 7) NTSC internal color bar with 3ch DACs operation and slave mode operation. DAC output pins is connected with only 390Ω load.AC Characteristic1. SYSCLK[ 3.3V Temperature 25°C ]ParameterSymbol Min.Typ.Max Unit SYSCLKfSYSCLK 27MHz SYSCLK Pulse width H tCLKH 15nsec SYSCLK Pulse width LtCLKL15nsecVILVIH2. In case of SYSINV = L (2-1). Pixel Data InputPixel Data Input Timing[ 3.3V Temperature 25°C ]ParameterSymbol Min TypMaxUnits Data Setup Time tDS 5nsec Data Hold TimetDH8nsec(2-2). Synchronizing Signal ( FID/VSYNC, HSYNC )(2-2-1) Input Synchronizing Signal Timing[ 3.3V Temperature 25°C ]ParameterSymbol Min Typ.MaxUnits Data Setup Time tDS 5nsec Data Hold TimetDH8nsecD7 - D0VILVIH(2-2-2) Output Synchronizing Signal Timing[ 3.3V Temperature 25°C ]ParameterSymbol MinTyp.Max Units Delay from SYSCLKtDEL27nsec(2-3). Reset (Initialize)Reset Timing[ 3.3V Temperature25°C ]ParameterSymbol Min Typ.Max Units /RESET Pulse WidthpRES10SYSCLK/RESETSYSCLKSYSCLKVIH(3). In case of SYSINV = H (3-1). Pixel Data InputPixel Data Input Timing[ 3.3V Temperature 25°C ]ParameterSymbol Min TypMaxUnits Data Setup Time tDS 5nsec Data Hold TimetDH8nsec(3-2). Synchronizing Signal ( FID/VSYNC, HSYNC )(3-2-1) Input Synchronizing Signal Timing[ 3.3V Temperature 25°C ]ParameterSymbol Min Typ.MaxUnits Data Setup Time tDS 5nsec Data Hold TimetDH8nsecD7 - D0VILVIH(3-2-2) Output Synchronizing Signal Timing[ 3.3V Temperature 25°C ]ParameterSymbol MinTyp.Max Units Delay from SYSCLKtDEL27nsec(3-3). Reset (Initialize)Reset Timing[ 3.3V Temperature 25°C ]ParameterSymbol Min Typ.MaxUnits /RESET Pulse WidthpRES10SYSCLK/RESETSYSCLKSYSCLK(4). I 2C Bus (SCL 400kHz cycle mode )(4-1) I/O Timing 1[ 3.3V Temperature 25°C ]ParameterSymbol Min Max Units Bus Free TimetBUF 1.3usec Hold Time (Start Condition)tHD:STA 0.6usec Clock Pulse Low Time tLOW 1.3usecBus Signal Rise Time tR 300nsec Bus Signal Fall Time tF 300nsec Setup Time(Start Condition)tSU:STA 0.6usec Setup Time(Stop Condition)tSU:STO0.6usecAll the figures shown above list are not restricted by AK8811/12 but are restricted by I 2C Bus standard.Please see the I 2C Bus standard for further details.(4-2) I/O Timing 2[ 3.3V Temperature 25°C ]ParameterSymbol Min.Max.Unit.Data Setup Time tSU:DAT 100 (1)nsecData Hold Time tHD:DAT 0.00.9 (2)usec Clock Pulse High TimetHIGH0.6usec(1) In case of normal I 2C bus mode tSU:DAT ≥250nsec(2) Using under minimum tLOW, this value must be satisfied.SDAtSU:DATSCLFUNCTIONAL DESCRIPTION♦ ResetWhen the reset pin [ /RESET ] set to “L”, AK8811/12 is in reset state. AK8811/12 starts in the internal initializing sequence at the trailing edge of the first SYSCLK after the reset pin is “L”. All internal registers are set to be default value by this initializing sequence. AK8811/12 needs at least 10 clock counts of SYSCLK for this reset operation. After the reset operation, the video output pins are in high-impedance. AK8811/12 requires SYSCLK for the reset operation.♦ Master-ClockAK8811/12 requires 27MHz clock at SYSCLK pin for operation. Video input data (ITU-R BT.656) is sampled at the trailing edge of this 27MHz. SYSINV decides the edge direction.SYSINV = L Data is sampled at rising edge of SYSCLK.SYSINV = H Data is sampled at falling edge of SYSCLK.♦ Video Signal InterfaceAK8811/12 can interface with the video input data by the following 3 modes. The mode is set by the register [ Interface mode register(00H) ].1. ITU-R BT.656 FormatAK8811/12 decodes EAV in stream data and manages an internal synchronization.In this case, AK8811/12 outputs FID (odd : “L” even : “H”)/ VSYNC and HSYNC.CCIR-bit of [ Interface mode register (00H) ] should be set “1” .2. ITU-R BT.656 like Format (4:2:2 Y/Cb/Cr)There are Master and Slave modes, for ITU-R BT.656 like Format which does not include EAV. In this mode, CCIR-bit of [ Interface mode register(00H) ] should be set “0” .<Master Mode>AK8811/12 provides FID/VSYNC and HSYNC to an external device according to the AK8811/12 internal timing counter. AK8811/12 starts to sample the input data at the fixed value on the internal pixel counter.In this mode, following setting should be done to [Interface mode register(00H)].CCIR-bit = 0MAS-bit = 1<Slave Mode>FID/VSYNC and HSYNC are supplied by an external device. AK8811/12 samples the data as same manner of Master mode.In this mode, following setting should be done to [Interface mode register(00H)].CCIR-bit = 0MAS-bit = 0♦ Video Signal ConversionVideo reconstruction module converts the multiplexed data (ITU-R. BT601 Y/Cb/Cr) to the interlace format of NTSC-M, PAL-M, PAL-B,D,G,H,I,N and other formats (ex. NTSC-4.43 and PAL60). The video reconstruction format, the line number, the color encode way(NTSC or PAL) and the frequency of Color Sub-carrier is specified by [Video Process 1 register(01H)]. (cf. Burst Signal Table) The frequency and the phase of Color Sub-carrier are also adjustable by [Sub C. Freq. register(06H)] and [Sub C. Phase register(07H)]. The Sub-carrier has a free-running mode and a reset-mode. In the reset-mode, the Sub-carrier is reset automatically to the initial phase for every 4 fields (NTSC) or 8 fields (PAL).♦ Component Video OutputVideo output mode is set by VS-bit of [ Video Process 3 register (03H) ].AK8811/12 can output not only the set of composite video signal and S-video signal but also can output component video signals(Y/Cb/Cr). The component video signals are complied with EIAJ guideline 1998/3.VS-bit = 0 : composite video signal and S-video signal outputVS-bit = 1 : component video signal output♦ Luminance FilterLuminance signal passes through the 2x Low Pass filter Fig.1 is the characteristic of Luminance Filter.Fig. 1 Luminance Filter♦ Chroma FilterChroma signals (Cb,Cr) before Sub-carrier modulation pass through the 1.3 MHz Low pass filter shown in Fig.2. Chroma signal modulated by Sub-carrier passes through the filter shown in Fig.3.Fig. 2 Chroma-1 LPFFig. 3 Chroma-2 LPF♦ Color burst signalColor burst signal is generated by 24bits-length Digital Frequency Synthesizer. The Default frequency of the color burst is selected by [Video Process 1 Register(0x01)].Standard Sub-carrier Freq.[MHz]Video Process 1[VM1,VM0]NTSC-M 3.57954545[0,0]PAL-M 3.57561188[0,1]PAL-B,D,G,H,I 4.43361875[1,1]PAL-N(Arg.) 3.5820558[1,0]PAL-N(non-Arg.) 4.43361875[1,1]PAL60 4.43361875[1,1]NTSC-4.43 4.43361875[1,1]Burst Signal TableSub-carrier frequency 3.57561188MHz is allowed when PAL-M mode is selected.The burst frequency and initial phase resolution are as follows.Frequency resolution 0.8046HzSCH Phase resolution 360°/256♦ Video DACAK8811/12 has the three current driven 10bits-DACs at 27MHz operation. The full scale voltage of DAC is determined by the current output from IREF pin. Typical output voltage is 1.28Vo-p under the condition of VREFIN 1.235V, 12KΩ between IREF pin and Ground(AVSS) and DAC load resistance of 390Ω. This full-scale voltage should be set in the range of 1.17V to 1.33V by adjusting the resistor which terminates IREF pin. Each DAC output can be set to “active state” or to “inactive state” individually by [DAC Mode register(05H)]. When DAC is in “inactive state”, the output is Hi-impedance. When all DACs are set to “inactive state”, the analog part of AK8811/12 goes into sleep mode. In this case AK8811/12 stops outputing the reference voltage(VREF) output. When any DAC is switched over in “active state” from sleep mode, AK8811/12 starts outputing reference voltage. In this case AK8811/12 needs several milisecond for VREF wake-up time.Using internal VREF as the reference voltage, connect [VREF OUT] pin with [VREF IN] pin and [VREF OUT] pin is terminated with more than 0.1uF capacitor.♦ Use external Reference VoltageIn order to improve the accuracy of DAC output, external reference voltage may be used. In this case, VREFOUT pin still needs to be terminated with more than 0.1uF capacitor.♦ Copy ProtectionMacrovision Copy Protection Rev.7.1Information about the Macrovision encoding functions of the AK8812 is available to Macrovision licensees. Macrovision may be contacted at:Macrovision Corporation1341 Orleans DriveSunnyvale, California 94089USAAttention: ACP-PPV Technical SupportFAX: (408) 743 – 8610♦ Closed Caption and Extended DataAK8811/12 supports both Closed Captioning and Extended Data. They are controlled “ON”or ”OFF” respectively by [ Video Process 2 Register(02H) ]. Each data consists of 2 continuous bytes register( Closed Caption R (16H,17H) ), and it is recognized as the data is renewed whenthe second byte(17H register) is written in the register. After the data is renewed, AK8811/12 encodes Closed Captioning and Extended Data at the designated line. If the data isn’t renewed,AK8811/12 outputs “ASCII-NULL” code. The data is supposed as Odd Parity and 7 bit US-ASCII code. Host should provide a parity bit.*In PAL encoding mode, AK8811/12 outputs them at the same timing and same pattern as NTSC. *The line where Closed Captioning data is encoded is as follows.525/60 System (SMPTE)625/50 System (CCIR)Closed Caption21 Line default21 Line defaultExtended Data284 Line default334 Line defaultTWO 7-Bit+PARITYFig. 4 Closed Captioning Wave form♦ Video IDAK8811/12 supports Video ID (EIAJ standard, CPR-1204) encoding for the distinction of an aspect ratio, etc. Setting or Resetting the VBID-bit of [ Video Process 2 Register(02H) ], this function is switched On/Off. The data is set by using [ Video ID Data Register(1AH, 1BH) ].VBID Data Renewal Timing.Fig. 5 VBID Data renewal TimingVBID Data LayoutVBID is consists of 20 bits and its format is shown as follows.AK8811/12 generates CRC code automatically and appends it to the data. Initial value of the Polynomial is 1.Fig. 6 VBID code assignmentVBID WaveformFig. 7 VBID Wave Form525/60 system625/50 system Amplitude70 IRE490 mVEncode Line20/28320/333VBID parameter table♦AK8811/12 Interface Timing (Part 1) Master mode & ITU-R BT. 656 modeOn ITU-R BT.656 decoding mode or master mode operation, AK8811/12 outputs HSYNC and FID or VSYNC (selected by register).When AK8811/12 receives ITU-R BT. 656 signal, AK8811/12 decodes [EAV] code in the data for synchronization then outputs the HSYNC. AK8811/12 outputs HSYNC at the rising edge of SYSCLK in the timing of the 32nd/24th(NTSC/PAL) data slot, which is counted from the [EAV] starting point as below. (See also AC Characteristics 2-2[Input Synchronizing Signal])On master mode operation, the front device connected with AK8811/12 (ex. MPEG Decoder) starts to set Cb on the 276th/288th(NTSC/PAL) slot, after starting to count HSYNC falling edge as 32nd/24th(NTSC/PAL) slot.FID/VSYNC is output synchronously with HSYNC at the timing of solid line as in Fig. 10 Video Field.Fig. 8 Interface Timing (ITU-R BT.656 or Master mode)♦ AK8811/12 Interface Timing (Part 2) Slave modeOn slave mode operation, HSYNC and FID or VSYNC (Selected by register) are input to AK8811/12.AK8811/12 monitors the transition of HSYNC at the timing of the rising edge of SYSCLK.(Refer to AC Characteristic 2-1. [Input Synchronizing Signal]) After AK8811/12 recognizes HSYNC is Low-logic, AK8811/12 sets the slot number to the 32nd/24th(NTSC/PAL),internally, then AK8811/12 starts to sample the data as Cb on 276th/288th(NTSC/PAL) slot. Video field is recognized the transition timing between FID/VSYNC and HSYNC. (Fig.10.Video Field) As in the figure, there is a toreralnce of ±1/4H.FID/VSYNCHSYNCFID/VSYNCODD FieldStartEVEN Field StartFig. 10. Video Field♦ HSYNC FID/VSYNC TimingHSYNCFID VSYNCHSYNCFIDVSYNCHSYNCFID VSYNCHSYNCFID VSYNC♦ Color BarsAK8811/12 generates the Common Color Bar signal for NTSC and PAL internally. The generated Color Bar is “100% Amplitude, 100% Saturation”.The following values are code for ITU-R. BT601WHITE YELLOWCYAN GREEN MAGENTARED BLUEBLACK Cb 128161665420290240128Y 235210170145106814116Cr1281461634222240110128WHITEYELLOWCYANGREENREDBLUEBLACKLuminance♦ Component video outputThe levels of each Component video outputs are following. ( Color bar NTSC 100/0/100/0 )Magnitude is compliant to the guideline of EIAJ CPR-1024.[mV]WHITEYELLOW CYAN GREEN MAGENTARED BLUE BLACKCb 0-350118-232232-1183500Y 714632500418296213820Cr57-350-293293350-57Y Signal Level : 1.00Vpp Y ( Video Signal Level ) : 0.714VY ( Sync level ) : 0.286V Setup :None Cb/Cr Signal Level :± 0.350V714mV (100 IRE)286mV350mV-350mV350mV-350mV♦ I2C Control SequenceAK8811/12 is controlled by I2C bus. The slave address can be selected as 40H or 42H by selecting SELA pin.SELA pull-down 40HPull-up42HOperation :Write Sequence:Stp : Stop Conditionby AK8811/12R/W: 1: Read0:Write- It ignores the general callAK8811/12 REGISTER MAPSub Address Name R/W Explanation 00H Interface Mode W Setting Interface mode01H Video Process 1W Setting Standard (NTSC, PAL etc.)02H Video Process 2W Setting Closed Caption/Extended Data/VBID 03H Video Process 3W Setting Composite signal or Component SignalAdjusting chroma/Luma Delay 04H RESERVED05H DAC Mode W Each DAC On/Off Switch06H Sub C. Freq.W Adjusting Sub-carrier frequency07H Sub C. Phase W Adjusting Sub-carrier phase08H-15H RESERVED16H Closed Caption R W Closed Caption Lower byte Data17H Closed Caption R W Closed Caption Upper byte Data18H Closed Caption R W Extended Lower byte Data19H Closed Caption R W Extended Upper byte Data1AH Video ID Data W Video ID Lower byte Data1BH Video ID Data W Video ID Upper byte Data1CH-23H RESERVED24H STS Data R Status25H Device ID R Device ID26H Device REV R Revision27H-29H RESERVEDInterface Mode Register (W only default A4H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 00H BLN4BLN3BLN2BLN1BLN0FID MAS CCIR Symbol Value DescriptionBLN4 - BLN0*****Line BlankingNo.default 10100FID0Select VSYNC1Select FID default MAS0Slave mode default1Master mode When CCIR=0,it’svalidCCIR0CCIR656 non-decode default1CCIR656 decodeVideo Process 1 Register (W only default 18H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 01H Reserved CBG SETUP SCR VM3VM2VM1VM0 Symbol Value DescriptionCBG0Video Encode default1Generates color barSETUP0No Set-up17.5 IRE Set-up defaultSCR0Sub C. Phase Reset off1Standard Field Reset default VM3 – VM200525/60default01525/60 PAL (PAL-M etc.)10 Reserved11PALVM1-VM000 3.57954545 MHz default01 3.57561188 MHz(PAL-M only)10 3.5820558 MHz11 4.43361875 MHzRegister Setting of each standard is showend as following ;VM3-VM0NTSC-M 0000PAL-B,D,G,H,I 1111PAL-M 0101PAL-60 0111NTSC4.43 0011• When SCR is “ON”, the Subcarrier Phase is reset every 4 fields for NTSC, every 8 fields for PAL.• Even when SETUP is “ON”, there is no Set-up (Pedestal) during the blanking lines.Video Process 2 Register (W only default 00H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 02H Reserved Reserved Reserved Reserved Reserved CC284CC21VBID Symbol Value DescriptionCC2840Extended Data OFF default1ONCC210Closed Caption OFF default1ONVBID0Video ID OFF default1ONVideo Process 3 Register (W only default 00H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 03H Reserved VS SYD2SYD1SYD0CYD2CYD1CYD0 Symbol Value DescriptionVideo Set0Composite, S-Video setdefault1Component setSYD2 - SYD0S-Video Y Component defaultdelay no. from Chroma: 2's comp.000 CYD2 - CYD0Composite Y Component defaultdelay no. from Chroma: 2's comp.000• VS-bit selects the one of the setting of signals from the 2 signal sets (Composite, Y /Cor Y/Cb/Cr)• S video and Y component of the composite signal can be shifted for the chroma signal independently at ±3-system clock (27MHz).DAC Mode Register (W only default 00H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 05H Reserved Reserved Reserved Reserved Reserved OUTCP OUTC OUTY Symbol Value DescriptionOUTCP0Composite video signal or U signal output : OFF default1Composite video singal or U signal output : ONOUTC0Chroma signal or V signal output : OFF default1Chroma signal or V signal output : ONOUTY0Y signal output : OFF default1Y signal output : ON•Video output of AK8811/12 (DAC) can be forced “OFF” independently.The output of DAC that is forced “OFF” is Hi-impedance. When three DACs areforced “OFF”, then the internal VREF is also forced “OFF”. In this case, it takesseveral miliseconds before the internal VREF reaches the proper voltage after anyDAC becomes “ON”.SubC Freq. Register (W only default 00H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 06H SUBF7SUBF6SUBF5SUBF4SUBF3SUBF2SUBF1SUBF0 Symbol Value Descriptiondefault 0 SUBF7-SUBF0Adjustment of frequency between+127 and –128 step of 0.8Hz• AK8811/12 generates the necessary sub-carrier frequency from a system clock by DFS (Digital Frequency Synthesizer)• Frequency of default is adjustable by specifying this bit. This bit adjusts the default frequency.SubC Phase Register (W only default 00H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 07H SUBP7SUBP6SUBP5SUBP4SUBP3SUBP2SUBP1SUBP0Symbol Value descriptionSUBP7 – SUBP0Step: (360° /256°)default 0•Sub- carrier phase is adjustable by (360°/256) step.Closed Caption Register (W only default 00H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 16H CC1[7]CC1[6]CC1[5]CC1[4]CC1[3]CC1[2]CC1[1]CC1[0] 17H CC2[7]CC2[6]CC2[5]CC2[4]CC2[3]CC2[2]CC2[1]CC2[0] 18H CC3[7]CC3[6]CC3[5]CC3[4]CC3[3]CC3[2]CC3[1]CC3[0] 19H CC4[7]CC4[6]CC4[5]CC4[4]CC4[3]CC4[2]CC4[1]CC4[0] Symbol DescriptionCC1[7] – CC1[0]Line 21 –1Closed CaptionCC2[7] – CC2[0]Line 21 –2CC3[7] – CC3[0]Line 284 -1Extended DataCC4[7] – CC4[0]Line 284 -2• When the 2nd byte of Closed Caption Data and Extended Data is written in,AK8811/12 recognizes the renewed data and encodes it in the video line. When thedata is not renewed AK8811/12 outputs NULL code.Video ID Data Register (W only default 00H)Sub Add bit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 1AH Reserved Reserved bit 1bit 2bit 3bit 4bit 5bit 6 1BH bit 7bit 8bit 9bit 10bit 11bit 12bit 13bit 14• Please write value 0 at Reserved bit.• Bit numbers correspond to Fig. 5 VBID code assignment.• AK8811/12 generates CRC 6 bit data automatically.Followings are read only registerSTATUS REGISTER (R only)Sub Add bit7bit6bit5bit4bit3bit2bit1bit0 24H Reserved Reserved EN284EN21SYNC STS2STS1STS 0 Symbol Value DescriptionEN2840Wait for the appointed video line to encode.1Ready for the C.C. data input to the register.EN210Wait for the appointed video line to encode.1Ready for the C.C. data input to the register.SYNC01Missing synchronization in slave mode. Synchronization was achieved.STS2 - STS 0***Shows the processing field No.• Status Register becomes effective when SYNC bit turns to “1”. When in master mode operation, this bit is ”1”.• STS2-STS2 holds the field number of processing. Some time lag is inevitable for the I2C acquisition.• Closed caption data should be renewed after firm that the EN* flag is “1”. EN* flag bit is cleared after the second byte( Sub address 17H,19H) was accessed.• Reserved-bit is always value 0.Device ID (R only default 21H)Sub Add bit7bit6bit5bit4Bit3bit2bit1bit0 25H00010001• Represents device ID. AK8811 is assigned 11H.Sub Add bit7bit6bit5bit4Bit3bit2bit1bit0 25H00010010• Represents device ID. AK8811/12 is assigned 12H.Device REV (R only default 01H)Sub Add bit7bit6bit5bit4Bit3bit2bit1bit0 26H00000001• Represents device revision. Initial is 01H.SYSTEM CONNECTION EXAMPLEAnalog GNDDigital GNDPACKAGEPackage & Lead frame materialPackage molding compound : EpoxyLead frame material : CuLead frame surface treatment : Solder plateUnits = mm10°MARKING1) Pin #1 indication2) Date Code : XXXXXXX (7 digits)3) Marketing Code : AK8811/AK88124) Country of Origin5) Asahi Kasei LogoIMPORTANT NOTICEThese products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:(a) A hazard related device or system is one designed or intended for life support or maintenance of safety or forapplications in medicine, aerospace, unclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.(b) A critical component is one whose failure to function or perform may reasonably be expected to result, whetherdirectly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.。